数字电子技术基础简明教程第四章

数字电子技术基础-第4章--

& Q4 G4 &

Q

Q

L2

CP Q5 & G5 Q6 G6 &

C1 R 1D ∧ S RD SD

RD 和SD 不受CP和D信号的影 响,具有最高的优先级。

RD

D

SD

二、CMOS主从结构的触发器

1.电路结构:由CMOS逻辑门和CMOS传输门组成主从D触发器。

CP G1 D T G1

1

Q' G2

1

CP Q' T G3

Q 从 触 发 器

Q

G1

&

&

G2

G3

&

&

G4

Q' 主 触 发 器 G5 & &

Q' G6 1 G9

G7

&

&

G8

R

CP

S

主从RS触发器的缺点 R、S不能同时为1,即有效的输入电平 主从JK触发器可解决此问题

(二)主从JK触发器

主从RS触发器的缺点: 使用时有约束条件 RS=0。

CP G1 D T G1

1

Q' G2

1

CP Q' T G3

Q G3

1

Q G4

1

CP CP T G2 主触发器 CP 从触发器 CP

CP T G4

CP

3 .具有直接置0端RD和直接置1端SD的CMOS边沿D触发器

集成触发器

一、集成触发器举例

1.TTL主从JK触发器74LS72

Q ┌ Q Vcc S D CP K3 K2 K1 ┌

CP J K

t CPH

t CPL

数字电子技术基础第四章习题及参考答案

数字电子技术基础第四章习题及参考答案第四章习题1.分析图4-1中所示的同步时序逻辑电路,要求:(1)写出驱动方程、输出方程、状态方程;(2)画出状态转换图,并说出电路功能。

CPY图4-12.由D触发器组成的时序逻辑电路如图4-2所示,在图中所示的CP脉冲及D作用下,画出Q0、Q1的波形。

设触发器的初始状态为Q0=0,Q1=0。

D图4-23.试分析图4-3所示同步时序逻辑电路,要求:写出驱动方程、状态方程,列出状态真值表,画出状态图。

CP图4-34.一同步时序逻辑电路如图4-4所示,设各触发器的起始状态均为0态。

(1)作出电路的状态转换表;(2)画出电路的状态图;(3)画出CP作用下Q0、Q1、Q2的波形图;(4)说明电路的逻辑功能。

图4-45.试画出如图4-5所示电路在CP波形作用下的输出波形Q1及Q0,并说明它的功能(假设初态Q0Q1=00)。

CPQ1Q0CP图4-56.分析如图4-6所示同步时序逻辑电路的功能,写出分析过程。

Y图4-67.分析图4-7所示电路的逻辑功能。

(1)写出驱动方程、状态方程;(2)作出状态转移表、状态转移图;(3)指出电路的逻辑功能,并说明能否自启动;(4)画出在时钟作用下的各触发器输出波形。

CP图4-78.时序逻辑电路分析。

电路如图4-8所示:(1)列出方程式、状态表;(2)画出状态图、时序图。

并说明电路的功能。

1C图4-89.试分析图4-9下面时序逻辑电路:(1)写出该电路的驱动方程,状态方程和输出方程;(2)画出Q1Q0的状态转换图;(3)根据状态图分析其功能;1B图4-910.分析如图4-10所示同步时序逻辑电路,具体要求:写出它的激励方程组、状态方程组和输出方程,画出状态图并描述功能。

1Z图4-1011.已知某同步时序逻辑电路如图4-11所示,试:(1)分析电路的状态转移图,并要求给出详细分析过程。

(2)电路逻辑功能是什么,能否自启动?(3)若计数脉冲f CP频率等于700Hz,从Q2端输出时的脉冲频率是多少?CP图4-1112.分析图4-12所示同步时序逻辑电路,写出它的激励方程组、状态方程组,并画出状态转换图。

数字电子技术基础教材第四章答案

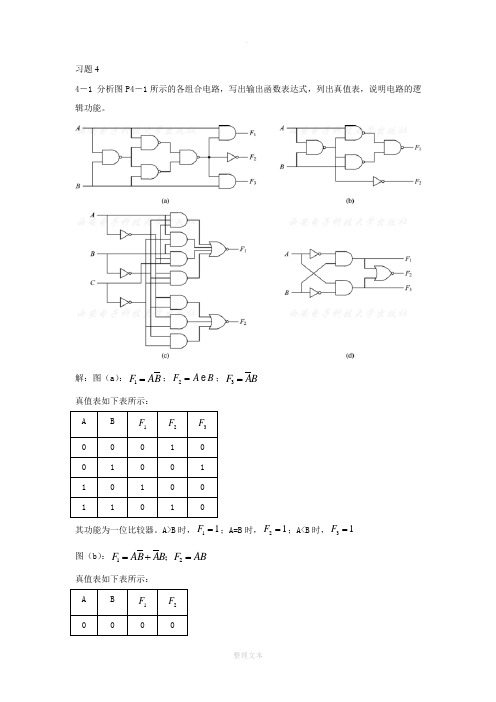

习题44-1 分析图P4-1所示得各组合电路,写出输出函数表达式,列出真值表,说明电路得逻辑功能。

解:图(a):;;真值表如下表所示:其功能为一位比较器。

A>B时,;A=B时,;A<B时,图(b):真值表如下表所示:功能:一位半加器,为本位与,为进位。

图(c):真值表如下表所示:功能:一位全加器,为本位与,为本位向高位得进位。

图(d):;;功能:为一位比较器,A<B时,=1;A=B时,=1;A>B时,=14-2 分析图P4-2所示得组合电路,写出输出函数表达式,列出真值表,指出该电路完成得逻辑功能。

解:该电路得输出逻辑函数表达式为:因此该电路就是一个四选一数据选择器,其真值表如下表所示:,当M=1时,完成4为二进制码至格雷码得转换;当M=0时,完成4为格雷码至二进制得转换。

试分别写出,,,得逻辑函数得表达式,并列出真值表,说明该电路得工作原理。

解:该电路得输入为,输出为。

真值表如下:由此可得:完成二进制至格雷码得转换。

完成格雷码至二进制得转换。

4-4 图P4-4就是一个多功能逻辑运算电路,图中,,,为控制输入端。

试列表说明电路在,,,得各种取值组合下F与A,B得逻辑关系。

解:,功能如下表所示,两个变量有四个最小项,最多可构造种不同得组合,因此该电路就是一个能产生十六种函数得多功能逻辑运算器电路。

4-5 已知某组合电路得输出波形如图P4-5所示,试用最少得或非门实现之。

解:电路图如下:4-6 用逻辑门设计一个受光,声与触摸控制得电灯开关逻辑电路,分别用A,B,C表示光,声与触摸信号,用F表示电灯。

灯亮得条件就是:无论有无光,声信号,只要有人触摸开关,灯就亮;当无人触摸开关时,只有当无关,有声音时灯才亮。

试列出真值表,写出输出函数表达式,并画出最简逻辑电路图。

解:根据题意,列出真值表如下:由真值表可以作出卡诺图,如下图:C AB 00 10 11 100 1由卡诺图得到它得逻辑表达式为: 由此得到逻辑电路为:4-7 用逻辑门设计一个多输出逻辑电路,输入为8421BCD 码,输出为3个检测信号。

数字电子技术基础第四章

&

G3

&

S=0,R=1:Qn+1=0

R

S=1,R=1:Qn+1=1(×),

CP

S

CP回到0后状态不定 输入端R、S通过与非门

作用于基精本品PPRT S触发器。

1R C1 1S R CP S

(三)同步RS触发器

2. 特征(tèzhēng)表

RS

00 01 10 11

Qn+1

Qn 1 0 1(×)

3. 特征方程

CP

电路连接的特点:第一个触发器的CP1端作为计数脉冲CP输入 端,Q1与第二个触发器的CP2端相连,依次有Qi与CPi+1相连,触发 器的输出Q4Q3Q2Q1代表四位二进制数。

精品PPT

4. 应用(yìngyòng)

二、主从(zhǔcóng)触发 器

每一个CP下降沿,都会使Q的状态变化,Q4Q3Q2Q1代表四位二进 制数,故称该电路为四位二进制计数器。

1. 逻辑(luójí)符号

输入信号:R、S(高有效) 时钟输入:CP 异步置0、置1:RD、SD

(不受CP限制,低有效) 输出信号:Q、Q

精品PPT

Q

Q

R 1R C1 1S S RD R CP S SD

2. 组成(zǔ chénɡ)及工作原理

组成:由两个同步RS触发器级联而成。

工作原理:

按照C同P步为高RS电触平发:器主的触功发能器翻输从转出触,A发、从B器 触发器时的钟状C态P不直变接,作Q用状于态主保触持。

精品PPT

3. 状态(zhuàngtài)转换图

特征表

D

Qn+1

0

0

1

1

数字电子技术基础简明教程(第三版) 4-6章

抗干扰0 能1力极0 强;异步置0

只有置1

0

1、00 置不1用0

功能异不。步允置许1

3. T 型触发器

在CP作用下,当T = 0时保持状态不变,T =1 时状态 翻转的电路,叫T 型时钟触发器。

Q

Q

1T C1

T Q n+1 功能 Q n1 T Q n TQ n

0 Q n 保持

T Qn

1 Q n 翻转 CP 下降沿时刻有效

56 引出端 功能 14

VCC

98 7

地

特性表 SD D CP RD

3.C边P 沿D0 DR触1–D 发S–1D器Q主n0+1要特点同步注置0

4 2 3 1 10 12 11 13

–SD1 CP1 – S–D2 CP2 –

D1 RD1 D2 RD2

C1P

的11上升11 沿Q1(正n 边保沿同持)步(或置无下1效降) 沿(负边沿)触发;

2. CP = 1 时跟随。 (Qn1 D) 下降沿到来时锁存 (Qn1 Qn )

三、集成同步 D 触发器

1. TTL 74LS375

Q

G1 >1

R G3 &

Q

>1 G2

S & G4

R

1 S CP

G5 D

D1 CP1、2

D2

D3 CP3、4

D4

74LS375

1 4

1D0 1LE

7 1D1

9 12

换 (2)比较上述特性方程,得出给定触发器中输入

方

信号的接法。

法 (3)画出用给定触发器实现待求触发器的电路。

1. JK D

已有

因此,令J = K = D D

数字电子技术基础教材第四章答案

习题44-1 分析图P4-1所示的各组合电路,写出输出函数表达式,列出真值表,说明电路的逻辑功能。

解:图(a ):1F AB =;2F A B =e ;3F AB = 真值表如下表所示: A B 1F2F3F0 0 0 1 0 0 1 0 0 1 1 0 1 0 0 111其功能为一位比较器。

A>B 时,11F =;A=B 时,21F =;A<B 时,31F = 图(b ):12F AB AB F AB =+=; 真值表如下表所示: A B 1F2F功能:一位半加器,1F 为本位和,2F 为进位。

图(c ):1(0,3,5,6)(1,2,4,7)F M m ==∑∏2(0,1,2,4)(3,5,6,7)F M m ==∑∏真值表如下表所示:功能:一位全加器,1F 为本位和,2F 为本位向高位的进位。

图(d ):1F AB =;2F A B =e ;3F AB =功能:为一位比较器,A<B 时,1F =1;A=B 时,2F =1;A>B 时,3F =14-2 分析图P4-2所示的组合电路,写出输出函数表达式,列出真值表,指出该电路完成的逻辑功能。

解:该电路的输出逻辑函数表达式为:100101102103F A A x A A x A A x A A x =+++因此该电路是一个四选一数据选择器,其真值表如下表所示:1A0AF0 0 0x 0 1 1x1 0 2x 1 13x4-3 图P4-3是一个受M 控制的代码转换电路,当M =1时,完成4为二进制码至格雷码的转换;当M =0时,完成4为格雷码至二进制的转换。

试分别写出0Y ,1Y ,2Y ,3Y 的逻辑函数的表达式,并列出真值表,说明该电路的工作原理。

解:该电路的输入为3x 2x 1x 0x ,输出为3Y 2Y 1Y 0Y 。

真值表如下:3x2x1x0x3Y2Y1Y0YM=10 0 0 0 0 0 0 0 0 0 0 1 0 0 0 1 0 0 1 0 0 0 1 1 0 0 1 1 0 0 1 0 0 1 0 0 0 1 1 0 0 1 0 1 0 1 1 1 0 1 1 0 0 1 0 1 01 1 0 0 1 0 0 M=0 1 0 0 0 1 1 1 1 1 0 0 1 1 1 1 0 1 0 1 0 1 1 0 0 1 0 1 1 1 1 0 1 11111 0 1 1 0 0 1 1 1 1 0 1 0 1 1 111111由此可得:1M =当时,33232121010Y x Y x x Y x x Y x x =⎧⎪=⊕⎪⎨=⊕⎪⎪=⊕⎩ 完成二进制至格雷码的转换。

数字电子技术第4章组合逻辑电路习题解答

、已知8421BCD可用7段译码器,驱动日字LED管,显示出十进制数字。指出下列变换真值表中哪一行是正确的。(注:逻辑“1”表示灯亮)

D

C

B

A

a

b

c

d

e

f

g *

0

0

0

0

0

0

0

0

0

0

0

0

4

0

1

0

0

0

1

1

0

0

1

1

7

0

1

1

(1)试分析电路,说明决议通过的情况有几种。

(2)分析A、B、C、D四个人中,谁的权利最大。

习题图

解:(1)

(2)

ABCD

L

ABCD

L

0000

0001

0010

0011

0100

0101

0110

0111

0

0

0

1

0

0

1

1

1000

1001

1010

1011

1100

1101

1110

1111

0

0

0

1

0

1

1

1

(3)根据真值表可知,四个人当中C的权利最大。

3) 用与或非门实现。

解:(1)将逻辑函数化成最简与或式并转换成最简与非式。

根据最简与非式画出用与非门实现的最简逻辑电路:电路略。

(2 )由上述卡偌图还可得到最简或与表达式:

即可用或非门实现。

(3)由上步可继续做变换:

数字电子技术基础教材第四章答案

习题44-1 分析图P4-1所示得各组合电路,写出输出函数表达式,列出真值表,说明电路得逻辑功能。

解:图(a):;;真值表如下表所示:A B0 0 0 1 00 1 0 0 11 0 1 0 01 1 0 1 0其功能为一位比较器。

A>B时,;A=B时,;A<B时,图(b):真值表如下表所示:A B0 0 0 00 1 1 0功能:一位半加器,为本位与,为进位。

图(c):真值表如下表所示:功能:一位全加器,为本位与,为本位向高位得进位。

图(d):;;功能:为一位比较器,A<B时,=1;A=B时,=1;A>B时,=14-2 分析图P4-2所示得组合电路,写出输出函数表达式,列出真值表,指出该电路完成得逻辑功能。

解:该电路得输出逻辑函数表达式为:因此该电路就是一个四选一数据选择器,其真值表如下表所示:0 00 11 01 14-3 图P4-3就是一个受M控制得代码转换电路,当M=1时,完成4为二进制码至格雷码得转换;当M=0时,完成4为格雷码至二进制得转换。

试分别写出,,,得逻辑函数得表达式,并列出真值表,说明该电路得工作原理。

解:该电路得输入为,输出为。

真值表如下:M=1 0 0 0 0 0 0 0 00 0 0 1 0 0 0 10 0 1 0 0 0 1 10 0 1 1 0 0 1 00 1 0 0 0 1 1 00 1 0 1 0 1 1 10 1 1 0 0 1 0 10 1 1 0 0 1 0 0 M=0 1 0 0 0 1 1 1 11 0 0 1 1 1 1 01 0 1 0 1 1 0 01 0 1 1 1 1 0 11 1 0 0 1 0 0 01 1 0 1 1 0 0 11 1 1 0 1 0 1 11 1 1 1 1 0 1 0由此可得:完成二进制至格雷码得转换。

完成格雷码至二进制得转换。

4-4 图P4-4就是一个多功能逻辑运算电路,图中,,,为控制输入端。

数字电子技术基础教材第四章答案

数字电子技术基础教材第四章答案习题44—1分析图P4—1所示的各组合电路,写出输出函数表达式,列出真值表,说明电路的逻辑功真值表如下表所示:其功能为一位比较器。

A>B时,F i i ;A=B时,F2 1 ;A<B 时,F3 1 图(b) : F, AB AB; F2 AB 真值表如下表所示:功能:一位半加器,F,为本位和,图(C): F, M (0,3,5,6)m(1,2,4,7)F2为进位。

F2M(0,1,2,4) m(3,5,6,7)真值表如下表所示:位的进位。

图(d) : F i AB ;F2 AeB ;F3 AB功能:为一位比较器,A<B时,F i = 1 ;A=B时,F2 = 1 ;A>B 时,F3 = 14—2分析图P4 —2所示的组合电路,写出输出函数表达式,列出真值表,指出该电路完成的逻辑功能。

^1 理0解:该电路的输出逻辑函数表达式为:A )A J X。

AA)X I AA Q X ?A 1A 0X 3如下表所示:AA 0F0 0 X O0 1 X 1 1 0 X 2 11X 30 12 3 X XX X因此该电路是一个四选一数据选择器, 其真值表4-3图P4—3是一个受M控制的代码转换电路,当M = 1时,完成4为二进制码至格雷码的转换;当M = 0时,完成4为格雷码至二进制的转换。

试分别写出Y°,Y,Y2,Y3的逻辑函数的表达式,并列出真值表,说明该电路的工作原理。

表如下:0 1 0 0 0 1 1 00 1 0 1 0 1 1 10 1 1 0 0 1 0 10 1 1 0 0 1 0 0 M=0 1 0 0 0 1 1 1 11 0 0 1 1 1 1 01 0 1 0 1 1 0 01 0 1 1 1 1 0 11 1 0 0 1 0 0 01 1 0 1 1 0 0 11 1 1 0 1 0 1 11 1 1 1 1 0 1 0丫3 30时,X3X3X3X3X2X2X2X i 丫2X i X o £Y完成格雷码至二进制的转换4— 4图P4— 4是一个多功能逻辑运算电路,图 中S 3,S 2, S i, S o为控制输入端。

数字电子技术基础简明教程课件第4章_触发器

数字电子技术基础简明教程课件第4章_触发器第4章触发器概述4.1基本触发器4.1.1用与非门组成的基本触发器4.1.2用或非门组成的基本触发器4.1.3集成基本触发器4.2同步触发器1、时钟电平控制,无约束问题在CP=1期间,若D=1,则Qn+1=1;若D=0,则Qn+1=0,即根据输入信号D取值不同,触发器既可以置1,也可以置0。

由于电路是在同步RS触发器基础上经过改进得到的,所以约束问题不存在。

2、CP=1时跟随,下降沿到来时才锁存 CP=1期间,输出端随输入端的变化而变化;只有当CP脉冲下降沿到来时才锁存,锁存的内容是CP下降沿瞬间D的值。

集成同步D 触发器引脚图4.3.1边沿D触发器一、电路组成及工作原理二、集成边沿D触发器1、D的逻辑表达式二、集成边沿JK触发器三、边沿JK 触发器的主要特点1、CP边沿(上升沿或下降沿)触发在CP脉冲上升沿(或下降沿)时刻,触发器按照特性方程的规定转换状态,其他时间里,J、K不起作用。

2、抗干扰能力强因为只在触发沿甚短的时间内触发,其他时间输入信号对触发器不起作用,保证信号的可靠接收。

3、功能齐全,使用灵活方便具有置1、置0、保持、翻转四种功能。

二、主要特点三、集成同步D触发器 1.TTL:74LS375CPDQG1QG3R&&SG2G41>1>1G5RS+VCC74LS3751D0 1LE1D12D02LE2D11Q01Q01Q11Q12Q02Q02Q12Q1147912152 36510111413Q1Q1Q2Q2Q3Q3Q4Q4––––D1CP1、2D2D3CP3、4D48162.CMOS:CC4042CDG1QG3G2G41TGQTG111CG5G6CP11=1POL0CPCPCP CP1CPCPCP=1?保持CP=0?DCP=1?DCP=0?保持POL=1时,CP=1有效,锁存的内容是CP下降沿时刻D的值;POL=0时,CP=0有效,锁存的内容是CP上升沿时刻D的值。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1

1

1

0

10 1 0 1 1 0 不用

Q n+1= S + RQ n

1 1 1 不用

特性方程 RS 0 约束条件 5

[例]

R

S

Q Q

R

S

Q

Q

6

4.1.2 由或非门组成

一、电路及符号

Q

G1 >1

Q

>1 G2

QQ RS

二、工作原理

RS0

R

S

RS

Qn1Qn,Qn1Qn “保持”

R0,S1 Qn1 1,Qn1 0 “置 1”

第四章 触发器

一、基本要求

1. 有两个稳定的状态(0、1),以表示存储内容; 2. 能够接收、保存和输出信号。 二、现态和次态

1. 现态: Q n 触发器接收输入信号之前的状态。 2. 次态: Q n1 触发器接收输入信号之后的状态。

三、分类

1. 按电路结构和工作特点:基本、同步、边沿。

2. 按逻辑功能分:RS、JK、D 和 T(T )。

基本 RS 触发器:S — 直接置位端; (不受 CP 控制) R — 直接复位端。

同步触发器: 同步 RS 触发器 同步 D 触发器

11

一、电路组成及工作原理

1. 电路及逻辑符号

Q

Q

Q

Q

Q

Q

G1 & S

G3 &

& G2

R & G4

S CP R S CP R

S C1 R S CP R

S CP R

2. 工作原理

1

EN

+VCC

R三RSSRSRSSRS0011––––––––––11233412341212态S0101111111235610245RES01111N锁1112233344RSSRSRSSRS存ABAB74Q不17触Q10LZ64n用2S发n+7219器79高1234特保不QQQQ置置注阻性允1479持10态3表许

8

Q1 Q2 Q3 Q4

内含 4 个基本 RS 触发器

2. 由或非门组成:CC4043(略)

9

二、TTL 集成基本触发器

74279、74LS279

Q

&

&

S

R

Q

&

&

RSSRSRSSRS––––––––––11233412341212

1 2 3 5 6 10 11 12 14 15

S1 S2

R

+VCC 16

1R

4

1SA

1Q

1SB 2R

74279

2Q

7

233SRSA74LS2793Q 9

3SB 4R

4Q 13

4S

8

Q1 Q2 Q3 Q4

10

4.2 同步触发器

4.2.1 同步 RS 触发器 同步触发器:触发器的工作状态不仅受输入端 (R、S)

控制,而且还受时钟脉冲(CP) 的控制。 CP (Clock Pulse): 等周期、等幅的脉冲串。

R1,S0 RS1

Qn1 0,Qn1 1 “置 0”

Qn1、 Qn1均为 UL “不允许”

若高电平同时撤消,则状态不定。

7

Q

G1 >1

Q 波S

>1 G2

形 图

R

Q

R

S

Q

三、特性表和特性方程 四、基本 RS 触发器主

R S Q n+1

要特点

0 0 Q n 保持 1. 优点:结构简单,

0 1 1 置 1 具有置 0、置 1、保持功能。

Q=1

“置 0”或“复位” (Reset)

S 0, R 1 Q = 1 1 态

Q=0

“置 1”或“置位” (Set)

Q SQ S R1

Q RQ S R 0 Q和Q 均为UH

R 先撤消: 1 态

Q= Q

S 先撤消: 0 态

“保持” 信号同时撤消:状态不定

(随机)3

简化波形图

状态翻转过程需要一定的延迟时间, Q

当 CP = 0 SR1

曾用符号

Qn1 Qn

国标符号

保持

当 CP = 1 SCP S1S RCP R1R

与基本 RS 触发器功能相同

12

特性表:

特性方程:

CP R S 0

100 100 101 101 110 1 10 111 111

Q n Q n+1 注

Q n 保持

0 1

0 1

保持

01 1 1 置1

Q

如 1 0,延迟时间为 tPHL;

0 1,延迟时间为 tPLH 。 由于实际中翻转延迟时间相对于脉

G1 &

&

信信号号同不时同撤时消撤,出

冲的宽度和周期很小,故可视为0。 现消S不,确状定态状确R态定 设触发器初始状态为0:

S

S

R

R

Q

Q

Q

Q

4

三、现态、次态、特性表和特性方程

1. 现态和次态

现态Qn:触发器接收输入信号之前的状态。

00 1 0 置0

0 1

不用 不用

不许

Qn1SRQn

RS0 约束条件

CP = 1期间有效 二、主要特点

1. 时钟电平控制 CP = 1 期间接受输入信号; CP = 0 期间输出保持不变。 (抗干扰能力有所增强)

2. RS 之间有约束

13

4.2.2 同步 D 触发器

一、电路组成及工作原理

Q

Q

SD,RD

3. 其他: TTL 和 CMOS,分立和集成。

1

4.1 基本触发器

4.1.1 由与非门组成

一、电路及符号

Q

01

G1 &

10

S

Q 01

& G2

R 10

QQ SR SR

Q=0 0态

Q=1

Q=1 1态

Q=0

2

二、工作原理

Q

01

G1 &

10

S

Q 01

&

G2

R 10

S 1, R 0 Q = 0 0 态

Qn1SRQn

D DQn D

(CP = 1期间有效) 简化电路:省掉反相器。

二、主要特点

G1 & S

& G2 R

G3 & 时钟电平控制,无约束问题; 2. CP = 1 时跟随。 (Qn1 D) 下降沿到来时锁存 (Qn1 Qn)

14

三、集成同步 D 触发器

1. TTL 74LS375

次态Qn:触发器接收输入信号之后的新状态。

2. 特性表和特性方程

特性表

R S Qn 00 0 00 1 01 0 01 1 10 0

Q n+1

0 1 1 1 0

简化特性表

Q n+1

RS 00

Q n+1 Q n 保持

RS Qn 00

01

11

10

0 1 1 置1 0 0 1

0

10 11

0 置0

不用 不允许

1 0 0 置0 1 1 不用 不许 2. 问题:输入电平直接控制输

Q n+1= S + RQ n

RS 0 约束条件

出状态,使用不便,抗干扰能 力差;R、S 之间有约束。

8

4.1.3 集成基本触发器

一、CMOS 集成基本触发器

1. 由与非门组成:CC4044

EN

R&

1

TG Q

EN

&

S

EN

EN 1

Q

G1 >1

R G3 &

Q

>1 G2

S & G4

R

1 S CP

G5 D

D1 CP1、2

D2

D3 CP3、4

D4

74LS375

1 4

1D0 1LE

7 1D1

9 12

2D0 2LE

15 2D1

+VCC

16

1Q0 1Q0 1Q1 1Q1 2Q0 2Q0 2Q1 2Q1