两级运算放大器的仿真验证

两级放大电路multisim仿真试验报告

两级放大电路multisim仿真试验报告两级放大电路multisim仿真试验报告一、实验介绍本实验主要用MultiSim软件编辑和仿真一个两级放大电路。

放大电路包括一级预处理部分(当前缓冲器+电容式滤波器)和一级功率部分(管式功率放大器TDA2110)。

两级放大电路也称直接放大,它使用一个预处理放大部分和一个功率放大部分来放大从源收到的信号。

预处理由电容式滤波器和当前缓冲器组成,用于消除输入信号中的干扰,提高信号增益。

功率放大部分主要由放大芯片TDA2110组成,以提高信号电平,使输出信号能够给拓扑分配足够的功率。

1. 首先,用Multisim软件编辑电路图。

先拖出当前缓冲器、电容式滤波器、放大芯片TDA2110等元件,按照原理设计图将各节点连接起来,并进行相应的仿真参数设置,如阻抗等。

2. 然后,设置激励信号,这里设置为正弦信号,频率为1kHz,高低电平分别为5V、-5V,且给激励信号的输入点添加滤波电容。

3.最后,设置输入电压为5v,根据实验要求,观察TDA2110功率放大芯片的输出信号,检查其电压分量的幅值,即前后放大的效果。

四、实验过程1.首先,拖出所需元器件,连接好各节点,并设置元器件的仿真参数,最终实现仿真所需电路图。

五、实验结果运行仿真,将输出信号电压调整为500mV,调压后输出信号获得明显放大,相对于输入信号来说,由5V放大至500mV(即放大100倍)。

如下图所示:六、结论通过实验,可以看出,两级放大电路在实验中正常工作,基本达到将输入信号由5V放大至500mV(即放大100倍)的效果。

两级放大电路分析仿真实验报告

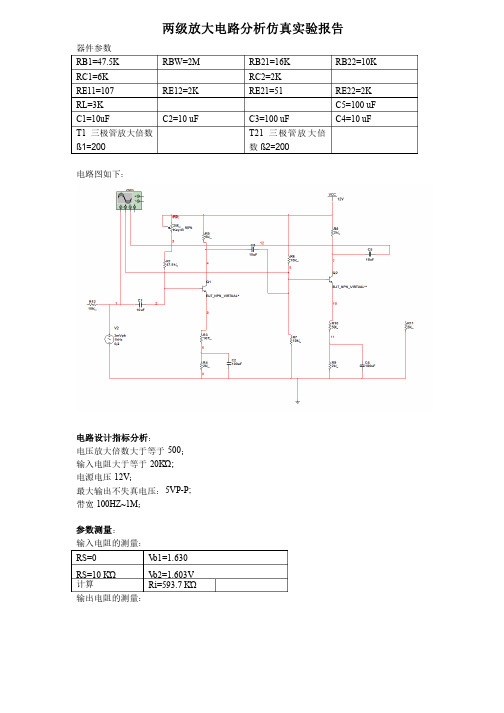

两级放大电路分析仿真实验报告器件参数器件参数 RB1=47.5K RBW=2M RB21=16K RB22=10K RC1=6K RC2=2K RE11=107 RE12=2K RE21=51 RE22=2K RL=3K C5=100 uF C1=10uFC2=10 uF C3=100 uF C4=10 uF T1三极管放大倍数ß1=200T21三极管放大倍数ß2=200电路图如下:电路图如下:电路设计指标分析:电压放大倍数大于等于500; 输入电阻大于等于20K Ώ; 电源电压12V ;最大输出不失真电压:5VP-P; 带宽100HZ~1M ;参数测量:输入电阻的测量:输入电阻的测量: RS=0 V o1=1.630 RS=10 K Ώ V o2=1.603V计算计算Ri=593.7 K Ώ输出电阻的测量:输出电阻的测量:RL 为开路为开路 V oo=1.643vRL=3K Ώ V ol=989.720mv计算计算 R0=1.99k Ώ电压放大倍数的测量:电压放大倍数的测量: 测试条件测试条件第一级放大输出第一级放大输出 第二级放大输出第二级放大输出 RL 为开路,为开路, RS=0,VI=3mVppV o1pp=48.427mV V o21pp=1.383V RL=3 K Ώ V o1pp=5.237 mVV o2=1.708Vp波形如下:波形如下:未加入负载RL 时仿真波形时仿真波形加入负载RL 时仿真波形时仿真波形带宽测量带宽测量静态工作点的测量:静态工作点的测量: VB1=4.013V VC1=4.378V VE1=3.228V VRE1=162.927 V VB2=4.743 V VC2=8.164 V VE2=3.953V VRE2=98.285 m V T1三极管放大倍数ß1=200T21三极管放大倍数ß2=200连接万用表电路如下:连接万用表电路如下:。

实验三 两级运放原理图设计及仿真

• 参考过程:

(1)选取电路结构; (2)确定工作点:由功耗、增益等要求选取各支路的工作电流; 如参考电路2:

g m 2 Cox (W / L ) I DS / 2 1 1 ro go I DS

压摆率:SR = M1过驱动电压 × 单位增益带宽 (3)确定MOS尺寸

(4)仿真验证

静态功耗≤5mW 电源电压:|1.8V|±10%; 工作温度范围 -20~80℃; 工艺:SMIC 0.18um CMOS

输出摆幅≥ ±1V;

失调≤ ±10mV; 噪声≤ 200(1kHz时);

参考电路1:

VDD M3 x iref vin1 M1 Vn Id5 M8 3 M5 M2 vin2 CL M7 y M4 M6

实验报告: 描述设计仿真过程;

描述参数估算过程; 描述性能参数仿真过程及结果,并进行分析;

• 设计指标要求:

开环增益≥60dB; 单位增益带宽≥50MHz; 摆率(Slew Rate)≥ 5V/us; 相位裕度≥50 ICMR ≥ ±0.8V; CMRR ≥50dB; PSRR ≥50dB;

实验三 两级CMOS运放的原理图设计及仿真

Hale Waihona Puke 验目的: 掌握采用cadence实现模拟IC原理图设计的方法; 掌握集成运算放大器设计的参数估算方法; 掌握集成运算放大器主要参数的仿真方法;

两级运算放大器

两级运算放大器实验报告一、实验名称:两级运算放大器二、实验目的:1.熟悉掌握Orcad captureCIS的使用方法以及常见的仿真方法和参数设置。

2.利用Orcad captureCIS设计两级运算放大器,并完成要求功能。

3.掌握运算放大器中的增益、带宽、输出摆幅、压摆率、速率、噪声等各个参数之间的折中调试。

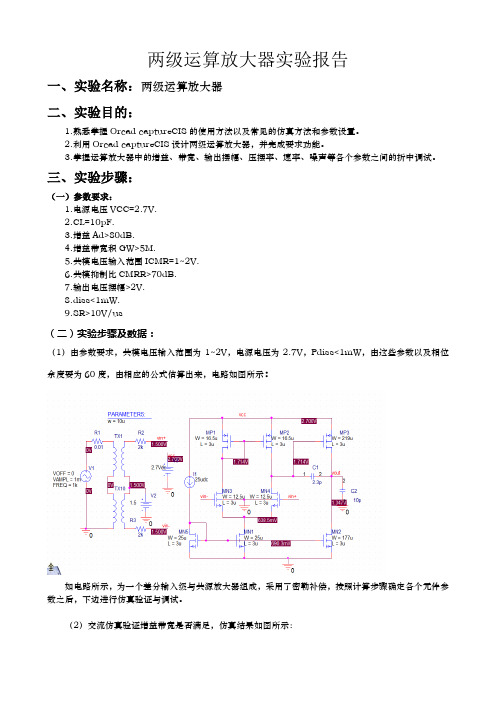

三、实验步骤:(一)参数要求:1.电源电压VCC=2.7V.2.CL=10pF.3.增益Ad>80dB.4.增益带宽积GW>5M.5.共模电压输入范围ICMR=1~2V.6.共模抑制比CMRR>70dB.7.输出电压摆幅>2V.8.diss<1mW.9.SR>10V/us(二)实验步骤及数据:(1)由参数要求,共模电压输入范围为1~2V,电源电压为2.7V,Pdiss<1mW,由这些参数以及相位余度要为60度,由相应的公式估算出来,电路如图所示:如电路所示,为一个差分输入级与共源放大器组成,采用了密勒补偿,按照计算步骤确定各个元件参数之后,下边进行仿真验证与调试。

(2)交流仿真验证增益带宽是否满足,仿真结果如图所示:如图结果,增益Av=82dB,增益带宽积GW=6.6M,相位裕度有42度,满足要求,并且还有一定的余量。

(3)交流仿真验证共模电压输入范围ICMR与共模抑制比CMRR是否满足要求,仿真电路如图所示:1、在仿真验证CMRR之前,先做了一个增益随共模输入电压的变化曲线,大致了解共模电压输入范围,结果如图所示:如图所示,增益在大于80dB时,共模电压输入范围为0.96V~2.66V,能达到要求,且还有余量。

2、现在仿真验证一下CMRR随共模电压的变化曲线,需要更改仿真电路图,更改的电路图如图所示:如图所示,由于要同时产生差模放大与共模放大,所以复制一个电路出来用以产生共模放大输出,仿真结果如图所示:由仿真结果可以看出,在增益大于80dB时,共模电压输入范围为0.56V~2.65V,由此得出的参数满足要求,且有一定余量。

两级运放设计与仿真报告

两级运放设计与仿真报告引言两级运放是一种常用的电路配置,具有在放大信号时增益稳定、频率响应宽、噪声低等特点。

本报告将介绍两级运放的设计与仿真过程,包括电路设计原理、参数选择、电路模拟与性能评估等内容。

设计原理两级运放主要由两个级联的运放组成,第一级运放作为输入级,主要负责增益放大和输入阻抗匹配;第二级运放作为输出级,主要负责提供电流放大和输出阻抗匹配。

通过合理选择运放参数和电阻分压比,可以实现所需的放大倍数和频率响应。

参数选择在设计过程中,首先需要确定所需的放大倍数和频率响应范围。

然后根据运放的特性参数,如增益带宽积、输入输出阻抗等,选择合适的运放器件。

通常使用的运放器件有型号为LM741、LT1001等。

电路设计根据参数选择,可以开始进行电路设计。

首先确定输入电阻,选择合适的电阻值以使得输入阻抗满足要求。

然后计算电阻分压比,以确定电压放大倍数。

接下来选择适当的电容值以确保频率响应满足要求。

电路仿真一般使用电路设计软件进行仿真。

根据电路设计原理和参数选择,输入正确的电路图和器件参数,进行仿真分析。

通过观察波形、频率响应曲线等结果,评估电路性能和稳定性。

性能评估通过仿真结果,可以评估电路的性能和稳定性。

主要包括增益稳定性、频率响应范围、失调电压、失调电流等指标。

根据仿真结果,可以对电路参数做出调整,以改善电路性能。

结论通过两级运放设计与仿真,我们可以实现对输入信号的放大和频率响应的控制。

通过选择合适的运放器件、参数以及电阻分压比和电容值,可以实现所需的放大倍数和频率响应范围。

通过仿真分析,可以评估电路性能和稳定性,并进行参数调整以改善电路性能。

[1] Sedra, A. S., & Smith, K. C. (2004). Microelectronic circuits. New York: Oxford University Press.[2] Razavi, B. (2024). Design of analog CMOS integrated circuits. McGraw-Hill Education.[3] Haigh, P. A., & Gác, P. (2024). Practical amplifier diagrams. New York: Springer.。

【免费下载】二阶运算放大器设计与仿真

目录第一章绪论 (1)1.1、模拟集成电路概述 (1)1.1.1、模拟集成电路的设计特点 (1)1.2、模拟集成电路设计流程 (1)第二章二阶运算放大器 (3)2.1、运算放大器概述 (3)2.1.1、运算放大器的工作原理 (3)2.2、运算放大器的分类 (5)2.2.1、运算放大器的主要参数 (5)第三章二阶运算放大器仿真分析 (6)3.1、画电路图 (6)3.2、二阶运算放大器仿真分析 (7)第四章实训总结 (12)参考文献 (13)第一章绪论1.1、模拟集成电路概述集成电路是一种将“管”和“路”紧密结合的器件,它以半导体单晶硅为芯片,采用专门的制造工艺,把晶体管、场效应管、二极管、电阻和电容等元件及它们之间的连线所组成的完整电路制作在一起,使之具有特定的功能。

集成放大电路最初多用于各种模拟信号的运算(如比例、求和、求差、积分、微分……)上,故被称为运算放大电路,简称集成运放。

集成运放广泛用于模拟信号的处理和产生电路之中,因其高性价能地价位,在大多数情况下,已经取代了分立元件放大电路。

1.1.1、模拟集成电路的设计特点几何尺寸是设计的重要部分;通常涉及模数混合电路;模拟占20%、数字占80%的芯片面积;模拟需要80%的设计时间;模拟设计主要在电路级;成功的设计:2/3取决于模拟,1/3取决于数字。

1.2、模拟集成电路设计流程设计输入:以电路图或HDL语言的形式形成电路文件;输入的文件经过编译后,可以形成对电路逻辑模型的标准描述。

逻辑仿真(功能仿真):对如上形成的逻辑描述加入输入测试信号,检查输出信号师傅哦满足设计要求;再此没有考虑任何时间关系,只是检测逻辑是否有错。

系统分割(设计综合):采用特定的设计方法分解实现电路模型,得到电路实际采用的逻辑单元及其相互连接形式;在GA设计时,电路会分割为2-3输入的逻辑单元,在FPGA设计中,分割为4输入逻辑单元,而采用CPLD设计时,则分割为更大的逻辑单元。

基本两级运放分析与仿真

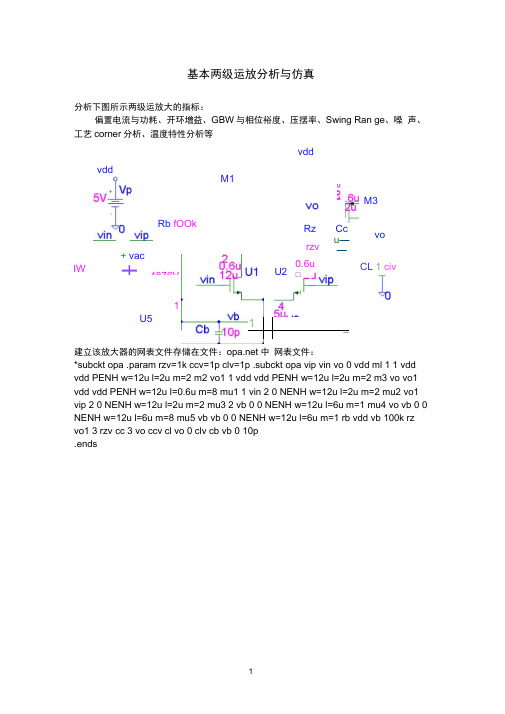

基本两级运放分析与仿真分析下图所示两级运放大的指标:偏置电流与功耗、开环增益、GBW 与相位裕度、压摆率、Swing Ran ge 、噪 声、工艺corner 分析、温度特性分析等vdd建立该放大器的网表文件存储在文件: 中 网表文件:*subckt opa .param rzv=1k ccv=1p clv=1p .subckt opa vip vin vo 0 vdd ml 1 1 vdd vdd PENH w=12u l=2u m=2 m2 vo1 1 vdd vdd PENH w=12u l=2u m=2 m3 vo vo1 vdd vdd PENH w=12u l=0.6u m=8 mu1 1 vin 2 0 NENH w=12u l=2u m=2 mu2 vo1 vip 2 0 NENH w=12u l=2u m=2 mu3 2 vb 0 0 NENH w=12u l=6u m=1 mu4 vo vb 0 0 NENH w=12u l=6u m=8 mu5 vb vb 0 0 NENH w=12u l=6u m=1 rb vdd vb 100k rz vo1 3 rzv cc 3 vo ccv cl vo 0 clv cb vb 0 10p .endsIWU5M1Rz 801rzv0.6u □ 2uCc u —— ccvM3 vo CL 1 civ1—Rb fOOkvdd1+ vac士 .4876VU21. 工作点分析由仿真结果查得电路的功耗是多少?各个 mos 管的工作区域,以及 MOS f的漏极电流为多少?该放大器的偏置电流为多少?网表如下:*opa fivea.sp .optio ns post=2.lib 7home/fzu/hspice/models/cz6h_v28.lib' TT .in clude "/home/fzu/example/zuoye/opa. net" xa1 vip vin vo 0 vdd opa vdd vdd 0 5vin1 vin 0 dc 2.4876vip1 vip 0 dc 2.4876 ac 1 0 .op .end(1)电路的功耗:电路功耗为1.7896mW(2)各个mos 管的工作区域,MOS 管的漏极电流,以及放大器的偏置电流:aubcktxalxalxal xalelement 1 :ml 11 :m3 1 :mul 1 :mu2 1 :rau3 model 0:penh0 :penh 0 :penhO :nenh 0:nenh 0 :nenhregion Sarurati Sarurati Sarurati Sarurati Saturati Saturati id -17.2O45U -17.2O45U -?S8.8356u17.2O45U 17.2O45U 34.4089Usubcktxal xalelementl:mu4 1;model 0:nenh 0: nenliregionSaturati Saturatiid2S0.8355U34,6021u2. 直流分析仿真该运放的输入输出特性曲线,求小信号增益、输出摆幅( output swing range ) 网表如下:*opa fiveb.sp .optio ns post=2.lib 7home/fzu/hspice/models/cz6h_v28.lib' TT .in eludesubck t element 0 :vdd 0:vinl0:viplvol t 吕 5.0000 2.4876 2.4S76 current -357.9266u 0.0. power1.7&96m 0. 0.■st 蓝盍盖T/cilt:age sourcestotal voltage source power dissipation=watts"/home/fzu/example/zuoye/opa .n et" xa1 vip vin vo 0 vdd opavdd vdd 0 5vin1 vin 0 dc 2.4876vip1 vip 0 dc 2.4876 ac 1 0.dc vip1 2.484 2.491 0.0001.end(1)输入输出特性曲线、小信号增益(2)输出摆幅由输入输出特性曲线图可得输出摆幅为: 4.9112V-0.01057V=4.90063V3. 交流分析(调整管子尺寸使运放的增益大于60dB,调整补偿电容使相位裕度大于60)①在没有补偿电阻(Rz),补偿电容(Cc)为1pf的条件下求该放大器单位增益带宽(GW/B相位裕度;网表如下:*opa fivec.sp.optio ns post=2.lib 7home/fzu/hspice/models/cz6h_v28.lib' TT.in clude "/home/fzu/example/zuoye/opa. net".param rzv=0xa1 vip vin vo 0 vdd opa vdd vdd 0 5vin1 vin 0 dc 2.4876vip1 vip 0 dc 2.4876 ac 1 0.ac dec 100 100 200meg.print ac vdb(vo) vp(vo).endSHCF FxpIfflFr ^n-Kinn 7HC-. I Cn^iljhi "z 呼n I nr. P^ip^nal hi■叭yTags ia r:nfis ssss(,仇•”:ma■M"S- HWViH J? «I*^|HW 的HMWIM 3S i I : I--Fi* *J M¥T**iR +1 "iLI! : I'M*!* <? WYV^iM +] >I MPW3*I> *A , WV^jlH *E 壬,b«Vr>iW 4? VVWi* 国tawjR[d£d E<J■- ] cimril hrtm:* | . J R, jhmuhMnJrrij 讥■皿摯>| 呼SR 匚 E Ev 加百Vim ns 2DC 序呼List文件截图:23.44229x2・9183m -110.3815由上图有,该放大器单位增益带宽(GWB为:23.44229MHz,相位裕度为:180-110.3815=79.6185②分析没有补偿电阻,补偿电容在(0~5pf)变化的时候对GWB口相位裕度的影响;网表如下:*opa fivec.sp.optio ns post=2.lib 7home/fzu/hspice/models/cz6h_v28.lib' TT.in clude "/home/fzu/example/zuoye/opa. net".param rzv=0xa1 vip vin vo 0 vdd opavdd vdd 0 5vin1 vin 0 dc 2.4876vip1 vip 0 dc 2.4876 ac 1 0.ac dec 100 10 200meg sweep ccv 0 5p 0.5p.print ac vdb(vo) vp(vo).end:* | 在“口.巾w章他卫hui.、j B? SF1 C£ Exdni V rn』母hu "List文件截图:ccv=0pf ccv=0.5pf165.958693(48.2706m161.8799|42.65795X93-S095m-122.3574 ccv=1pf ccv=1.5pf23.44229X 1.1939m-1 10.3fi2715.84893x8jD. 7018m-105.5736 ccv=2pf ccv=2.5pf12 022fi4K«5.9371m-IDS.19339.5499SX175.8782m-101.5&22 ccv=3pf ccv=3.5pf&.12831X20.4489m-100.S029 6.91&31X102.5128m-99.9992 ccv=4pf ccv=4.5pf6.0256QX155.0402m-99.4129 5.37032X144.4577m-99.015S ccv=5pf4.B9779x37.0887m-98.7967由上知随着电容增大,单位增益带宽减小,相位裕度增大③ 分析补偿电阻在(0~2K变化,补偿电容为1pf的时候对GWB口相位裕度的影响。

两级运放仿真结果

1.共模输入范围ICMR的仿真利用单位增益结构来测量共模输入范围ICMR,仿真电路图如下:仿真网表如下:*AMP_ICMR *** 共模输入范围测试***X1 VDD VSS VINP VOUT VOUT AMP ***调用子网表,端口对应相连,注意****VOUT与VINN 是相连的*** .GLOBAL VDD ***定义全局VDD****VDD VDD 0 5 ***VDD输入5V电压***VSS VSS 0 0 ***VSS为0V***VINP VINP 0 3 ***运放正端VINP输入3V**.OP ***直流分析***.DC VINP 0 5 0.01 ***直流扫描,从0 ~ 5V,间隔0.01V**.PROBE DC V(VOUT) ***打印输出直流电压VOUT***.PROBE DC I1(M5) ***打印输出直流尾电流I5**.lib'sm0351.lib' TT ***调用工艺库***.OPTIONS INGOLD=2 CSDF=2 ***选择设置INGOLD=2 CSDF=2*** .END ***电路描述结束***分析:仿真时,VINP从0扫描到5V 。

当VINP较小时,刚刚进入共模输入范围时,运放的尾电流I5进入饱和区,达到静态值,将此作为ICMR的起点,当VINP较大时,离开共模输入范围时,输出电压VOUT不再跟随VINP线性变化,将此作为终点。

仿真得到的波形如下:(输出VOUT)(运放尾电流I5)结果分析:从波形可以看出,当尾电流I5进入饱和区时,输出电压为1.5V,当输出电压不再跟随输入VINP线性变化时,输出电压值为4.6V。

满足设计要求。

2.输出电压范围的仿真在单位增益中,传输曲线的线性受到ICMR的限制,在高增益下结构下,输出曲线的线性部分与放大器的输出电压范围一致,下面采用增益为10的结构电路图仿真:仿真网表如下:*AMP_AMP_OUTPUT **输出摆幅测试**X1 VDD VSS VINP VINN VOUT AMP ***调用子网表,端口与子网对应相连*** R1 VINN 0 10K ***在运放负输入端和地之间接10K电阻** R2 VOUT VINN 90K ***运放输出端和负输入端接90K电阻** .GLOBAL VDD ***定义全局VDD****VDD VDD 0 5 ***VDD输入5V电压***VSS VSS 0 0 ***VSS为0V***VINP VINP 0 2 ***运放正端VINP输入2V**.OP ***直流分析***.DC VINP 0 5 0.01 ***直流扫描,从0 ~ 5V,间隔0.01V**.PROBE V(VOUT) ***打印输出电压VOUT***.lib'sm0351.lib' TT ***调用工艺库***.OPTIONS INGOLD=2 CSDF=2 ***选择设置INGOLD=2 CSDF=2***.END ***电路描述结束***分析:当直流电压VINP从0扫面到5V时,得到输出电压的波形如下:结果分析:个从仿真结果大致可以看出,输出电压范围与曲线中增益为10的线性范围一致的条件下得到输出电压范围在500mVd到4.8V之间,基本满足设计要求。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验一、两级运算放大器的仿真验证

一、实验目的

1、学习集成运算电路单元的设计参数的仿真、测试、验证。

2、学习采用Cadence工具实现IC电路设计的基本操作和方法,包括电路图的编辑以及仿真调试过程。

二、实验内容

本实验通过设计一个两级运算放大器电路学习Cadence工具下电路的设计和仿真方法。

实验内容包括:

1.熟悉Cadence界面及基本的建立新的cell文件等基本过程;

2.完成两级运算放大器电路的设计;

3.利用Cadence的仿真环境得到波形,分析仿真结果。

该电路设计采用上华CSMC0.5umCMOS工艺设计,工作电压5V。

三、实验原理

运算放大器是一个能将两个输入电压之差放大并输出的集成电路。

运算放大器是模拟电子技术中最常见的电路,在某种程度上,可以把它看成一个类似于BJT或FET 的电子器件。

它是许多模拟系统和混合信号系统中的重要组成部分。

它的主要参数包括:开环增益、单位增益带宽、相位阈度、输入阻抗、输入偏流、失调电压、漂移、噪声、输入共模与差模范围、输出驱动能力、建立时间与压摆率、CMRR、PSRR以及功耗等主要包括四部分:第一级输入级放大电路、第二级放大电路、偏置电路和相位补偿电路。

1.共模抑制比:差分放大电路抑制共模信号及放大差模信号的能力,常用

共模抑制比作为一项技术指标来衡量,其定义为放大器对差模信号的电

压放大倍数Aud与对共模信号的电压放大倍数Auc之比,称为共模抑制

比,英文全称是Common Mode Rejection Ratio,因此一般用简写CMRR

来表示,符号为Kcmr,单位是分贝db。

2.共模输入范围:是指在差分放大电路中,二个输入端所加的是大小相

等,极性相同的输入信号叫共模信号,此信号的范围叫共模输入信号范

围。

3.电源抑制比:是输入电源变化量(以伏为单位)与转换器输出变化量

(以伏为单位)的比值(PSRR),常用分贝表示。

通常把满量程电压变化

的百分数与电源电压变化的百分数之比称为电源抑制比。

4.输出摆幅:指的是,当输出信号为电压的时候,外部量的变化引起的输

出电压变化。

对于无源器件,这个变化通常是从某个负电压到某个正电

压。

而对于有源器件,这个变化是相对于某个固定电压,做一定幅度的

上下偏移。

(无源器件也可以看作是相对电压0做偏移)。

四、实验步骤

1、登陆到UNIX系统。

在登陆界面,输入用户名stu01和密码123456。

2、Cadence的启动。

登录进去之后,点击Terminal出现窗口,输入icfb命令,启动Cadence软件。

3、根据设计指标及电路结构,估算电路参数。

4、利用Candence原理图的输入。

(1)Composer的启动。

在CIW窗口新建一个单元的Schematic视图。

(2)添加器件。

在comparator schematic窗口点击Add-Instance或者直

接点i,就可以选择所需的器件。

(3)添加连线。

执行Add-Wire,将需要连接的部分用线连接起来。

(4)添加管脚。

执行Add-Pin和直接点p,弹出添加管脚界面。

(5)添加线名。

为设计中某些连线添加有意义的名称有助于在波形显示窗口中显出该条线的信号名称,也可以帮助检查电路错误。

点击Add-Wire Name,弹出新窗口,为输入输出线添加名称。

为四端的MOS器件的衬底添加名称vdd!或gnd!,其中!表示全局变量。

(6)添加电源信号,根据不同的仿真电路设置不同的电源参数。

(7)保存并检查。

点击schematic窗口上的Check and Save按钮,察看是否有警告或者错误。

如果有,察看CIW窗口的提示。

5、电路仿真。

(1)启动模拟仿真环境。

在comparator schematic窗口,选择Tools-Analog Environment,弹出模拟仿真环境界面。

(2)设置模型库。

(3)设置分析类型。

在仿真窗口,点击Choose Analyses按钮,弹出Choose Analyses窗口,该窗口中列出了各种仿真类型,依次进行各种仿真,如ac、dc、tran,进行交流仿真、直流仿真、瞬态仿真。

(4)设置波形显示工具。

Cadence中有两种波形显示工具:AWD和wavescane,在仿真窗口选择Session-assign,在弹出的窗口中可以选择波形显示工具为AWD 或wavescane。

(5)选择输出结果显示信号。

在Results中选择Main ,在电路图中点击输出确定输出波形信号。

(6)进行仿真。

选择Simulation-Run,或者直接点击仿真窗口右下角的Run 按钮来启动仿真,仿真开始过程中,在CIW窗口会出现一系列仿真信息,另外会弹出一个Spectre输出窗口。

仿真结束会自动弹出波形显示窗口。

(7)观察波形,看是否满足设计要求。

五、实验结果

1.两级运放的实验过程及基本仿真

(1)电路图

(2)仿真参数设置

(3)仿真结果

①波形

②参数

2. 两级运放的实验过程及共模抑制比(CMRR)仿真(1)电路图

(2)仿真参数设置

(3)仿真结果

3.两级运放的实验过程及输入共模范围(ICMR)仿真(1)电路图

(2)仿真参数设置

(3)仿真结果

4.两级运放的实验过程及电源抑制比(PSRR)仿真(1)电路图

(2)仿真参数设置

(3)仿真结果

5.两级运放的实验过程及输出摆幅仿真(1)电路图

(2)仿真参数设置

(3)仿真结果

六、实验总结

在两级运算放大器的仿真实验中,学会了CAD软件Cadence的基本操作和快捷键的使用方法,实现了在Cadence中的电路图的设计流程以及仿真方法。

熟

悉了两级运算放大器的结构,了解了其参数的仿真。

学会了如何在Cadence中对两级运算放大器进行交流仿真、共模抑制比、输入共模范围、电源抑制比、输出摆幅的仿真,对于书本上的理论,有了进一步的理解。