CMOS二级运算放大器设计

模拟CMOS集成电路设计优质课程设计实验报告二级放大器的设计

模拟CMOS集成电路设计课程设计报告--------二级运算放大器旳设计信息科学技术学院电子与科学技术系一、概述:运算放大器是一种能将两个输入电压之差放大并输出旳集成电路。

运算放大器是模拟电子技术中最常用旳电路,在某种限度上,可以把它当作一种类似于BJT 或FET 旳电子器件。

它是许多模拟系统和混合信号系统中旳重要构成部分。

它旳重要参数涉及:开环增益、单位增益带宽、相位阈度、输入阻抗、输入偏流、失调电压、漂移、噪声、输入共模与差模范畴、输出驱动能力、建立时间与压摆率、CMRR、PSRR以及功耗等。

二、设计任务:设计一种二级运算放大器,使其满足下列设计指标:三、电路分析:1.电路构造:最基本旳二级运算放大器如下图所示,重要涉及四部分:第一级放大电路、第二级放大电路、偏置电路和相位补偿电路。

2.电路描述:输入级放大电路由PM2、PM0、PM1和NM0、NM1构成。

PM0和PM1构成差分输入对,使用差分对可以有效地克制共模信号干扰;NM0和NM1构成电流镜作为有源负载;PM2作为恒流源为放大器第一级提供恒定旳偏置电流。

第二级放大电路由NM2和PM3构成。

NM2为共源放大器;PM3为恒流源作负载。

相位补偿电路由电阻R0和电容C0构成,跨接在第二级输入输出之间,构成RC米勒补偿。

此外从电流电压转换角度来看,PM0和PM1为第一级差分跨导级,将差分输入电压转换为差分电流。

NM0和NM1为第一级负载,将差模电流恢复为差模电压。

NM2为第二级跨导级,将差分电压信号转换为电流,而PM3再次将电流信号转换成电压信号输出。

偏置电压由V0和V2给出。

3.静态特性对第一级放大电路:构成差分对旳PM0和PM1完全对称,故有G m1=g mp0=g mp1 (1)第一级输出电阻R out1=r op1||r on1 (2)则第一级电压增益A1=G m1Rout1=g mp0,1(r op1||r on1) (3) 对第二级放大电路:电压增益A2=G m2R out2= -g mn2(r on2||r op3) (4) 故总旳直流开环电压增益A0=A1A2= -g mp0,1g mn2(r op1||r on1)(r on2||r op3) (5) 由于所有旳管子都工作在饱和区,因此对于gm我们可以用公式g m =D I L W )/(Cox 2μ (6) 进行计算;而电阻r o 可由下式计算 r o =DI 1λ (7)其中λ为沟道长度调制系数且λ∝1/L 。

全差分CMOS运算放大器的设计毕业设计

CMOS运算放大器的设计毕业设计(论文)原创性声明和使用授权说明原创性声明本人郑重承诺:所呈交的毕业设计(论文),是我个人在指导教师的指导下进行的研究工作及取得的成果。

尽我所知,除文中特别加以标注和致谢的地方外,不包含其他人或组织已经发表或公布过的研究成果,也不包含我为获得及其它教育机构的学位或学历而使用过的材料。

对本研究提供过帮助和做出过贡献的个人或集体,均已在文中作了明确的说明并表示了谢意。

作者签名:日期:指导教师签名:日期:使用授权说明本人完全了解大学关于收集、保存、使用毕业设计(论文)的规定,即:按照学校要求提交毕业设计(论文)的印刷本和电子版本;学校有权保存毕业设计(论文)的印刷本和电子版,并提供目录检索与阅览服务;学校可以采用影印、缩印、数字化或其它复制手段保存论文;在不以赢利为目的前提下,学校可以公布论文的部分或全部内容。

作者签名:日期:学位论文原创性声明本人郑重声明:所呈交的论文是本人在导师的指导下独立进行研究所取得的研究成果。

除了文中特别加以标注引用的内容外,本论文不包含任何其他个人或集体已经发表或撰写的成果作品。

对本文的研究做出重要贡献的个人和集体,均已在文中以明确方式标明。

本人完全意识到本声明的法律后果由本人承担。

作者签名:日期:年月日学位论文版权使用授权书本学位论文作者完全了解学校有关保留、使用学位论文的规定,同意学校保留并向国家有关部门或机构送交论文的复印件和电子版,允许论文被查阅和借阅。

本人授权大学可以将本学位论文的全部或部分内容编入有关数据库进行检索,可以采用影印、缩印或扫描等复制手段保存和汇编本学位论文。

涉密论文按学校规定处理。

作者签名:日期:年月日导师签名:日期:年月日目录第一章绪论 (7)1.1设计平台及软件介绍 (7)1.1.1PSPICE简介 (7)1.1.2 L-Edit简介 (7)1.1.3 Cadence OrCAD Capture简介 (7)1.2 设计方法 (8)1.2.1CMOS运算放大器设计方法 (8)1.2.2运算放大器的性能优化 (8)第二章全差分运算放大器基础 (10)2.1 MOS器件基本特性 (11)2.1.1 MOSFET的结构和大信号特性 (11)2.1.2 MOSFET的小信号模型 (12)2.2运算放大器概述 (13)2.3全差分运算放大器特点 (14)第三章CMOS模拟运放设计 (16)3.1设计目标 (16)3.2电路结构分析 (16)3.3.1 输入级设计 (18)3.3.2电流镜电路 (18)3.3.3偏置电路 (19)3.3.4 输出级 (20)3.3.5 整体电路 (20)第四章运放参数的模拟与测量 (22)4.1瞬态分析 (22)4.2 温度特性 (23)4.3输出阻抗 (24)4.4交流特性分析 (25)5.1版图设计基础 (26)5.1.1设计流程 (26)5.1.2 L-edit中的版图设计 (27)5.2 版图设计 (28)5.3版图参数的提取并仿真 (29)5.3.1版图参数的提取和修改 (29)5.3.2电路仿真 (29)第六章总结 (31)【参考资料】 (32)附录: (33)一、Pspice仿真代码: (33)1、原理层次仿真代码(偏置电压由直流电压直接替代) (33)2、MOS分压电路中MOS宽长比确定电路 (35)3、最终Pspice仿真代码 (35)二、版图生成代码 (37)三、版图修改代码 (40)第一章绪论1.1设计平台及软件介绍1.1.1 PSPICE简介PSPICE是由SPICE(Simulation Program with Intergrated Circuit Emphasis)发展而来的用于微机系列的通用电路分析程序。

两级运算放大器设计文档-20150116

点,使补偿后的运放只有一个极点。这就要求:

fZ

1

2

CC

(

g

m

1 6

RZ

)

gm6

2 CL

RZ

CC CL gm6 CC

(b) 消去零点。即将零点移至无穷远处。这就要求

gm6Rz 1

(c) 将零点移到左半平面略大于 GBW 的位置。一般为 1.2 倍 GBW 处(why?), 原因:1,2GBW 处的零点既不影响幅度特性,又能很好地贡献相位裕度。

=

������������ ������������

=

������������1 2������������������

=

������������1 ������������1

������������1

1 2������������������

(5)

B 相位补偿分析:

如图 1 电路,加入一个与 Cc 的串联电阻之后,电路的零点变为:

第六章 仿真

6.1 直流增益、带宽和相位裕度

结果说明

A1 A2 增益 3dB带宽 增益带宽积 相位裕度

16.64 20.8 50.8dB 4.2MHZ 1.88GHZ 62deg

仿真结果图示

6.2 偏置电路设计:

注:此电路没有做输入偏置,后续工作应做一个 342mv 的偏置供输入。

放大器 symbol 测试

W 502.392u 502.392u 155.416u 155.416u 342.083u 104.154u 849.32u 306.99u

5.4 计算&仿真参数

DC参数 Vout Vp Vgs1 Vgs2 id1 id2

cmos两级级联运算放大器电路

CMOS两阶段的级联操作放大器电路就像集成电路(IC)技术的超级

英雄。

由于其放大和冷却的金属—氧化—半导体(CMOS)技术的双重阶段,这个电路用高增益和增加带宽来打包一拳。

这就像瑞士军队

的刀模拟信号处理,准备应对任何挑战的方式。

无论是放大音频信

号还是在传感器中压缩数字这个电路都是你用来模拟一切的下一次

你需要信号助推,只要呼叫CMOS两级级级的操作放大器电路, IC

世界的无声英雄!

这个CMOS两阶段操作放大器的第一部分有几台晶体管,它们一起工作来提升输入信号,然后还有这个电流镜的东西可以帮助负载。

这个

第一阶段基本上为第二部分铺设了舞台。

第二阶段类似于encore,它能增加更多的收益,并有助于提升输出电压。

很酷的是,第一阶段的

输出只是直接插入第二阶段的输入,所以它就像这种双功率提升的配置。

CMOS两阶段的级联操作放大器电路具有重大优点,包括收益高、输

入阻力高以及铁路对铁路输出摇摆。

它适合需要大量扩展的应用程序,特别是在数据获取系统、传感器接口和音频信号处理领域。

电路的配

制和加强涉及仔细考虑晶体管的尺寸、偏差和计费技术,所有这些技

术都是为了达到所期望的性能指标。

两级CMOS运算放大器设计

从CC和GB的表达式来确定输入晶体管的跨导,可以用下面方程来计算跨导gm2

gm2 GB CC

从而可直接求得输入晶体管M2的宽长比

W L2

gm22 K2` I5

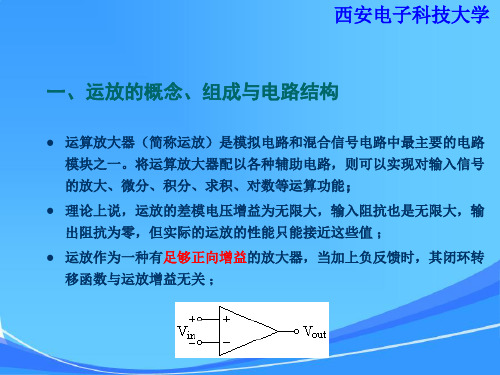

西安电子科技大学

两级CMOS运算放大器的设计步骤(3)

下面利用共模电压范围(低电平)计算M5的饱和电压:

VDS5 Vin(min)I51VT1(max) 若VDS5<100mV,则可能会使(W/L)5过大,这是不可接受的。若VDS5<0V,则 说明所确定的共模范围CMR的技术规范太严了。为此,我们可以减小I5或增加 (W/L)1。注意,应考虑条件改变后对前面设计步骤的影呐。这样反复迭代,直 到获得满意的结果。由求得的VDS5及(W/L)5为

↓1/2

↑1/2

↑

L

W/L

↑

↑1/2

M7 补偿电容 CC

L

↑

增大GB

↑1/2

↑1/2

↓

增大RHP零点

↑1/2

↑1/2

↓

增大SR

↑

↓

增大 CL

↑

在完成以上计算和设计后,可以采用Spice仿真软件进行仿真验证。

西安电子科技大学

四、两级运放的仿真和测试

仿真是对设计的细化和验证,对精度的提高,对 性能的优化,是一个主次逼近理想值的过程。

运放平衡时有:I5=I6=I7,因此可得:

W L7

WL5

I6 I5

最后检查运放的总增益和运放功耗:

AV I522g3m 2Ig6m 667

如果增益太低,许多参数还可再做调整。

西安电子科技大学

运放的性能与器件、电流之间的关系

漏极电流

M1和M2 M3和M4 M6

两级全差动运算放大器的设计

两级全差动运算放大器的设计华中科技大学IC课程设计两级全差动运算放大器的设计年级:学号:姓名:专业:指导老师:二零一一年十二月摘要应用0.18umCMOS工艺,设计了一个放大倍数为86dB、单位增益带宽为360MHz、负载为1pF的两级全差动运算放大器。

可以满足一定的高速度、高精度的指标。

两级分别由一个差分的共源放大器和一个折叠式放大器组成。

通过运用差动输出代替普通两级运算放大器的单端输出,从而提高了输入动态范围、抑制共模信号和噪声的能力等性能。

因此,优于一些传统的两级运算放大器。

关键词:全差动运算放大器;共源放大器;折叠式放大器AbstractA fully differential operational amplifier with a DC-gain of 86dB and a gain-bandwidth of 360 MHz has been implemented in a 0.18um CMOS process.It can satisfy the index of high speed and high precision.And the two level is respectively made up of a common-source amplifier and a Folding amplifier.Therefore,it is better than some of the traditional operational amplifier.Keywords:fully differential operational amplifier; common-source amplifier; Folding amplifier目录摘要 (1)Abstract (2)1.引言 (4)2. 两级全差动运算放大器设计要求 (4)3. 电路分析与设计 (4)3.1.第一级运算放大器设计 (5)3.1.1第一级差模电压增益 (6)3.1.2.共模电压输入范围 (6)3.1.3.第一级增益带宽积GBW (7)3.1.4.第一级MOS管宽长比 (7)3.1.5.第一级仿真结果 (7)3.2.第二级运算放大器设计 (8)3.2.1.第二级差模电压增益 (9)3.2.2.偏置电压与偏值电流 (9)3.2.3.增益带宽积与负载电容 (9)3.2.4.第二级MOS管宽长比 (9)3.2.5.第二级仿真结果 (10)3.3.两级联仿 (10)3.3.1.差分压摆率 (11)3.3.2.静态功耗 (11)3.3.3.等效输入参考噪声 (11)3.3.4.相角裕度 (12)3.3.5.两级联仿结果 (13)4. 结论 (13)致谢 (14)参考文献 (14)心得体会 (15)1.引言随着模拟集成电路技术的发展,高速、高精度运算放大器得到广泛应用。

CMOS高性能运算放大器研究与设计

CMOS高性能运算放大器探究与设计引言:随着科技的不息进步和应用的广泛推广,运算放大器(Operational Amplifier,简称Op-Amp)作为一种重要的模拟电路器件,得到了广泛的关注和应用。

CMOS (Complementary Metal-Oxide-Semiconductor)技术由于其功耗低、集成度高等优势,被广泛应用于运算放大器的探究和设计中。

本文将介绍CMOS高性能运算放大器的探究与设计,主要包括运算放大器的基本原理、运算放大器的基本电路结构、CMOS技术的特点和优势、CMOS高性能运算放大器的设计方法和优化技术等方面。

一、运算放大器的基本原理运算放大器是一种特殊的差动放大器,它能够实现电压放大、电流放大、功率放大等功能。

运算放大器有两个输入端,一个非反相输入端和一个反相输入端;有一个输出端和一个电源端,电源端一般有正电源和负电源两个。

在抱负状况下,运算放大器具有无限的增益、无限的输入阻抗和零的输出阻抗。

但实际状况下,由于运算放大器的内部结构等因素的限制,无法完全满足抱负的条件。

因此,在运算放大器的设计中,需要思量如何提高增益、输入阻抗和输出阻抗等性能指标。

二、运算放大器的基本电路结构运算放大器的基本电路结构由差动放大器、电压放大器和输出级组成。

差动放大器用于实现输入信号的差分放大,电压放大器用于实现信号的放大,输出级用于驱动负载电阻。

差动放大器由两个晶体管组成,一个晶体管作为非反相输入端,另一个晶体管作为反相输入端。

通过调整两个晶体管的尺寸比例,可以实现不同的放大倍数。

电压放大器由级联的共源放大器组成,通过逐级放大,实现信号的放大。

输出级由差分放大器和输出级筛选电路组成,通过差分放大器将信号转化为可驱动负载电阻的电流信号,再经过输出级筛选电路,将电流信号转化为电压信号。

三、CMOS技术的特点和优势CMOS技术是一种基于金属-氧化物-半导体(MOS)结构的半导体制造技术。

与传统的bipolar技术相比,CMOS技术具有以下特点和优势:(1)功耗低:CMOS电路在静态状态下几乎不消耗电流,功耗分外低,适合于低功耗应用的场合。

二级密勒补偿运算放大器设计(西安邮电大学)

一、二级运放的结构及设计指标计算1.题目:二级密勒补偿运算放大器设计2.小组成员:3.设计思路设计要求在阅读复旦大学设计资料后,对之间学习过的带隙基准电路总结对比,寻找不同的结构的作用。

最基本的COMS二级密勒补偿运算跨导放大器的结构如图所示。

主要包括四部分:第一级输入级放大电路、第二级放大电路、偏置电路和相位补偿电路。

主要的任务如下:计算相应的设计指标、设计相应参数、绘制cadence核心原理图、绘制Smybol,搭建仿真测试电路、测试并仿真基本指标。

对比仿真结果,优化各项性能最后进行版图绘制,了解并生成版图。

提取参数并进行仿真,对比各项指标。

1.输出级放大电路由M6、M7组成。

M6为共源放大器。

M7为其提供恒定偏置电流同时作为第二级输出负载。

M14和Cc构成相位补偿电路。

因为M14工作在线性区,通过m14的直流电流为0,所以M14可等效为一个电阻,m14与电容Cc构成RC密勒补偿2.输出级放大电路由M6、M7组成。

M6为共源放大器。

M7为其提供恒定偏置电流同时作为第二级输出负载。

M14和Cc构成相位补偿电路。

因为M14工作在线性区,通过m14的直流电流为0,所以M14可等效为一个电阻,m14与电容Cc构成RC密勒补偿3.偏置电路由M8~M13和RB组成。

M8和M9宽长比相同。

M12与M13相比,源极加入了电阻RB,组成微电流源,产生电流IB。

对称的M11和M12构成共源共栅结构,减小沟道长度调制效应造成的电流误差。

在提供偏置电流的同时,还为M14栅极提供偏置电压。

M1和M2为第一级差分输入跨导级,将差分输入电压转换为差分电流;M3和M4为第一级负载,将差模电流恢复为差模电压;M6为第二级跨导级,将差分电压信号转换为电流;M7再将此电流信号转换为电压输出。

4.等效电路图5.静态功耗一旦电源电压确定,静态功耗取决于各支路静态电流总和。

考察各路电路,可以知道,此运放的静态功耗为6.单位增益带宽单位增益带宽是运放最重要的指标之一,它定义为当运放增益为1时,所加输入信号的频率,7.共模抑制比共模抑制比的定义为其中Adm是差模增益,Acm是共模增益。

一种CMOS二级密勒补偿运放的设计

一种CMOS二级密勒补偿运放的设计一个实际的运放电路包含很多极点,为了使运放可以正常工作必须对其进行频率补偿。

所谓“补偿”就是对运放的开环传输函数进行修正,这样就可以得到稳定的闭环电路,而且获得良好的时间响应性能。

两级运放的频率补偿存在一个问题。

我们的补偿原理是使其中一个主极点向原点靠拢,目的是使增益交点低于相位交点。

然而这样就需要一个很大的补偿电容。

大电容在集成电路中是很难制作而且不经济的。

实践证明,通过密勒效应可以以一个中等的电容器的值实现单独利用大电容才可以做到的补偿效果。

这种补偿方法就是“密勒补偿”。

一种CMOS 二级密勒补偿运放的设计,主要有第一级差分放大,第二级共源级放大,电流偏置电路以及密勒补偿电路四部分组成。

首先,手动计算各项参数,分析各项参数与性能之间的相互制约关系。

然后,利用电路EDA仿真软件对电路进行仿真,对参数进行一些微调以满足运放的设计指标。

因为数字集成电路的规律性和离散性,计算机辅助设计方法学在数字集成电路的设计中已经具有很高的自动化。

但是由于模拟电路设计的一些不确定性,一般来说,手工进行参数的预算是不能缺少的一个环节。

运算放大器(简称运放)是许多模拟系统和混合信号系统中的一个完整部分。

各种电路系统中都离不开运放:从直流偏置的产生到高速放大或滤波。

运算放大器的设计基本上是分为两个部分。

第一是选择电路结构,第二是电路的各项参数的确定。

比如静态工作电流,每个管子的尺寸等参数。

这个步骤包含了电路设计的绝大部分工作。

很多参数的确定需要不断地权衡来满足性能。

该设计第二章分析电路的原理开始,第三章接着介绍对运放的各个指标做介绍和分析。

第四章以具体的指标要求为例,分析约束条件,进行手算。

之后使用HSPICE 进行电路仿真。

2电路分析2.1 电路结构选定的 COMS 二级密勒补偿运算跨导放大器的结构如图 2.1 所示。

主要包括四部分:第一级输入级放大电路、第二级放大电路、偏置电路和相位补偿电路。

两级CMOS运算放大器设计

两级CMOS运算放大器设计引言CMOS运算放大器是现代电路设计中的重要组成部分,它在模拟电路中扮演着关键的角色。

CMOS运算放大器由于其低功耗、高增益和较低的失调电压而备受青睐。

本文将介绍两级CMOS运算放大器的设计方法,包括电路结构、工作原理以及性能指标。

电路结构两级CMOS运算放大器由两个级联的CMOS差动放大器组成,它们的输出分别连接在第二级差动放大器的输入上。

这种结构能够提供更高的增益和更好的线性度。

差动放大器差动放大器是CMOS运算放大器的关键组成部分,它用于将输入信号转换为差模信号,并放大差模信号以提供一个具有高增益的输出。

CMOS差动放大器由一对输入端和一对输出端组成,每个输入端都连接了一个NMOS和一个PMOS管,这样可以实现单端输入和差分输入。

工作原理两级CMOS运算放大器的工作原理如下:1.输入信号被差动放大器的第一级转换为差模信号,并经过第一级放大。

第一级放大的输出信号被传递给第二级放大器。

2.第二级差动放大器放大差模信号,然后将其转换为单端输出信号。

3.输出信号经过一个输出级,通过一个负反馈回路被注入到第二级差动放大器的输入上。

设计步骤下面是设计两级CMOS运算放大器的一般步骤:1.确定电路的性能指标,例如增益、带宽以及失调电压等。

2.根据给定的性能指标选择差动放大器和输出级的电路结构。

3.根据选择的电路结构计算电路的参数,例如电阻、电容和晶体管的尺寸等。

4.使用电路模拟工具,例如SPICE,对电路进行仿真和优化。

5.布局电路,并进行布线。

6.进行电路的后仿真和测试。

性能指标两级CMOS运算放大器的性能指标通常包括以下几个方面:1.增益:运算放大器的增益是指输出信号相对于输入信号的放大程度。

在设计过程中,需要根据实际应用需求确定所需的增益。

2.带宽:带宽是指运算放大器能够输出一个相对稳定的放大信号的频率范围。

一般来说,带宽越大,运算放大器的性能越好。

3.失调电压:失调电压是指实际输入和理论输入之间的偏差。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

CMOS二级运算放大器设计

(东南大学集成电路学院)

一.运算放大器概述

运算放大器是一个能将两个输入电压之差放大并输出的集成电路。

运算放大器是模拟电子技术中最常见的电路,在某种程度上,可以把它看成一个类似于BJT 或FET 的电子器件。

它是许多模拟系统和混合信号系统中的重要组成部分。

它的主要参数包括:开环增益、单位增益带宽、相位阈度、输入阻抗、输入偏流、失调电压、漂移、噪声、输入共模与差模范围、输出驱动能力、建立时间与压摆率、CMRR、PSRR以及功耗等。

二.设计目标

1.电路结构

最基本的COMS二级密勒补偿运算跨导放大器的结构如图所示。

主要包括四部分:第一级输入级放大电路、第二级放大电路、偏置电路和相位补偿电路。

图两级运放电路图

2.电路描述

电路由两级放大器组成,M1~M4构成有源负载的差分放大器,M5提供该放大器的工作电流。

M6、M7管构成共源放大电路,作为运放的输出级。

M6 提供给M7 的工作电流。

M8~M13组成的偏置电路,提供整个放大器的工作电流。

相位补偿电路由M14和Cc构成。

M14工作在线性区,可等效为一个电阻,与电容Cc一起跨接在第二级输入输出之间,构成RC密勒补偿。

3.设计指标

两级运放的相关设计指标如表1。

表1 两级运放设计指标

三.电路设计

第一级的电压增益:

)||(422111o o m m r r g R G A ==

第二级电压增益:

)||(766222o o m m r r g R G A =-= 所以直流开环电压增益:

)||)(||(76426221o o o o m m o r r r r g g A A A -==

单位增益带宽:

c

m O C g A GBW π2f 1

d == 偏置电流:

2

13

122121)/()/()/(2⎪⎪⎭

⎫ ⎝⎛-=L W L W R L W KP I B n B

根据系统失调电压:

7

5

6463)/()/(21)/()/()/()/(L W L W L W L W L W L W ==

转换速率:

⎭

⎬⎫

⎩⎨⎧-=L DS DS C DS C I I C I SR 575,min

相位补偿:

12.1)/()/()/()/(1

61311

146

6+==

m m m C g g L W L W L W L W g R

以上公式推导过程简略,具体过程可参考相关专业书籍。

根据这些公式关系,经过手算得到一个大致的器件参数如表2。

表2 二级运放器件参数

四.HSPICE仿真

根据已经计算好的器件参数,写成电路网表。

.title test

.lib E:\ tt

vdd vdd 0 5

vss vss 0 0

.subckt opamp vn vp out vdd vss

m1 2 vn 1 1 mp w=120u l=1u

m2 3 vp 1 1 mp w=120u l=1u

m3 2 2 vss vss mn w=40u l=1u

m4 3 2 vss vss mn w=40u l=1u

m5 1 6 vdd vdd mp w=16u l=1u

m6 out 3 vss vss mn w=160u l=1u

m7 out 6 vdd vdd mp w=32u l=1u

* bias circuit

m8 6 6 vdd vdd mp w= l=1u

m9 7 6 vdd vdd mp w= l=1u

m10 6 7 8 vss mn w=6u l=1u

m11 7 7 9 vss mn w=6u l=1u

m12 8 9 10 vss mn w=24u l=1u

m13 9 9 vss vss mn w=6u l=1u

rb 10 vss 6k

* miller

cc 4 out

cl out vss 3p

m14 4 7 3 vss mn w=20u l=1u

.ends

x1 vn vp out vdd vss opamp *ADM

x2 vp vp out1 vdd vss opamp *ACM

x3 out2 vi out2 vdd vss opamp *SR

x4 vn vn out3 vdc vss opamp *pPSRR

x5 vn vn out4 vdd vsc opamp *nPSRR

vp vp 0 dc ac 1

vn vn 0 dc

vi vi 0 pulse(2 3 20ns 200ns 400ns)

vdc vdc 0 dc=5 ac=1v

vsc vsc 0 ac=1v

.ac dec 10 1k 100meg

.trans 1n 400n

.ptint ac v(vout) v(3)

.print trans v(out2)

.print ac vdb(out) vp(out)

.print ac vdb(out1)

.print ac vdb(out3)

.print ac vdb(out4)

.measure ac GBW when vdb(out)=0

.measure ac VPW when vp(out)=-120

.op

.end

1.直流增益、带宽和相位裕度

把ac信号全部放在一个输入端(或正端或负端),使用Hspice分析输出增益和相位裕度。

差模放大测试电路如图。

图差模增益测试电路图

对应的网表是:

x1 vn vp out vdd vss opamp *ADM

.print ac vdb(out) vp(out)

将vac=1V,这样得到的输出电压值就是增益值,方便观察。

仿真得到的差模增益和相位裕度如图所示。

分别扫描了100Mhz和1Ghz情况下的波形如图和。

图100Mhz带宽扫描差模增益和相位波形

图1Ghz带宽扫描差模增益和相位波形

为了得到准确的直流增益值,单位增益带宽和相位裕度值,通过以下两条语句:

.measure ac GBW when vdb(out)=0

.measure ac VPW when vp(out)=-120

观察.lis文件,发现直流增益为,单位增益带宽为,相位裕度为65degree。

共模放大测试电路如图。

图共模增益测试电路图

对应的网表是:

x2 vp vp out1 vdd vss opamp *ACM

.print ac vdb(out1)

共模增益波形如图。

图共模增益频谱图

共模增益在0dB以下说明具有较好的共模抑制。

共模抑制比如图:

图共模抑制比频谱图

共模抑制比达到83dB。

2.电源抑制比

图为电源和地到输出增益的测试电路图,用差模增益除以电源增益即得电源抑制比。

图为仿真得到的正、负电源抑制比,从图中可知,低频时正电源抑制比为98dB,负电源抑制比为89dB。

图电源增益测试电路图

图仿真的电源抑制比

3.压摆率

将运放接成单位增益负反馈形式,如图所示。

对输入施加正负阶跃信号,得到阶跃特性如图所示,给输出负载充电时的压摆率为μs,放电时的压摆率大约为V/μs。

对应的网表:

x3 out2 vi out2 vdd vss opamp *SR

vi vi 0 pulse(2 3 20ns 200ns 400ns)

.trans 1n 400n

.print trans v(out2)

图压摆率测试电路图

图仿真的瞬态建立特性

通过比较设计指标与实际值,满足系统要求的设计要求。

五.总结

进行模拟IC设计的第一步是根据要求确定需要的电路结构,第二步是掌握这种结构的原理和参数之间的联系,第三步根据指标手算电路参数,这个参数只是初步仿真值,可能无法达到系统指标,然后需要手工调整相关参数。

如果始终无法满足,就需要重新考虑电路结构是否合适,初始参数设置是否合适。

通过这些调整最终满足要求。

参考文献

[1] 钟文耀.CMOS电路模拟与设计-基于Hspice[M]. 北京: 科学出版社, 2007.

[2] 尹睿.二级密勒补偿运算放大器设计教程[M].上海:复旦大学出版社,2007。