CMOS两级运算放大器_设计报告

毕业设计CMOS运算放大器版图设计

摘要集成电路掩膜版图设计是实现电路制造所必不可少的设计环节,它不仅关系到集成电路的功能是不是正确,而且也会极大程度地阻碍集成电路的性能、本钱与功耗。

本文依据大体CMOS集成运算放大电路的设计指标及电路特点,绘制了大体电路图,通过Spectre进行仿真分析,得出性能指标与格元器件参数之间的关系,据此设计出各元件的版图几何尺寸和工艺参数,成立出从性能指标到版图设计的优化途径。

运算放大器的版图设计,是模拟集成电路版图设计的典型,利用Spectre对设计初稿加以模拟,然后对不符合设计目标的参数加以修改,重复这一进程,最终取得优化设计方案。

最后依照参数尺寸等完成了放大器的版图设计和版图的DRC、LVS验证。

关键词:集成电路,运算放大器,版图设计,仿真ABSTRACTIntegrated circuit layout design is an essential design part to realize circuit mask manufacturing, it is not only related to the integrated circuit to function correctly, but also can greatly affect the performance of the integrated circuit, the cost and the power consumption.Based on the basic CMOS integrated operational amplifier circuit characteristic and design target, we have rendered the basic circuit diagram, and simulation by Spectre, the simulated results are derived parameters and their relationship between determining factors, thereby defining a line with the design target domain size and processing parameters, finally we builded an optimization from the performance index to layout design .Operational amplifier IC layout design, is the design model of analog integrated circuit layout . Here we used Spectre to design draft which should be simulated, then modified which do not comply with the design goals of the parameters , repeat the process, and finally get the optimization design scheme. Finally, according to the parameters such as size finished the amplifier layout design and the DRC, LVS verification.KET WORDS: Integrated circuit, Operational amplifier, layout design, Simulation毕业设计(论文)原创性声明和利用授权说明原创性声明本人郑重许诺:所呈交的毕业设计(论文),是我个人在指导教师的指导下进行的研究工作及取得的功效。

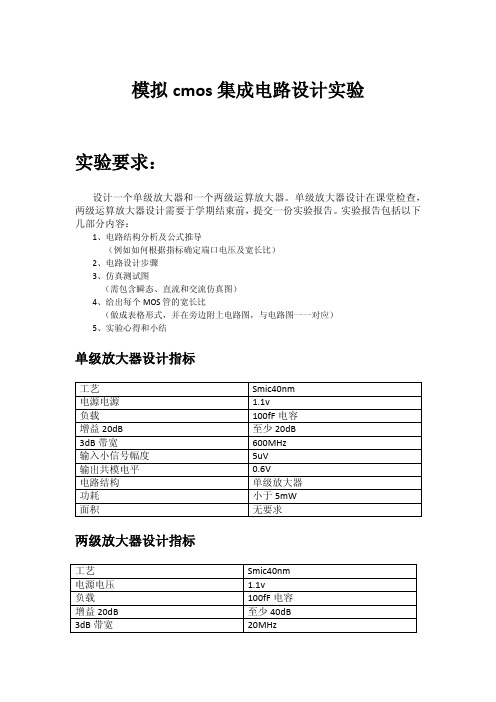

模拟cmos集成电路设计实验

模拟cmos集成电路设计实验实验要求:设计一个单级放大器和一个两级运算放大器。

单级放大器设计在课堂检查,两级运算放大器设计需要于学期结束前,提交一份实验报告。

实验报告包括以下几部分内容:1、电路结构分析及公式推导(例如如何根据指标确定端口电压及宽长比)2、电路设计步骤3、仿真测试图(需包含瞬态、直流和交流仿真图)4、给出每个MOS管的宽长比(做成表格形式,并在旁边附上电路图,与电路图一一对应)5、实验心得和小结单级放大器设计指标两级放大器设计指标实验操作步骤:a.安装Xmanagerb.打开Xmanager中的Xstartc.在Xstart中输入服务器地址、账号和密码Host:202.38.81.119Protocol: SSHUsername/password: 学号(大写)/ 学号@567& (大写)Command : Linux type 2然后点击run运行。

会弹出xterm窗口。

修改密码输入passwd,先输入当前密码,然后再输入两遍新密码。

注意密码不会显示出来。

d.设置服务器节点用浏览器登陆http://202.38.81.119/ganglia/,查看机器负载情况,尽量选择负载轻的机器登陆,(注:mgt和rack01不要选取)选择节点,在xterm中输入 ssh –X c01n?? (X为大写,??为节点名)如选择13号节点,则输入ssh –X c01n13e.文件夹管理通常在主目录中,不同工艺库建立相应的文件夹,便于管理。

本实验采用SMIC40nm工艺,所以在主目录新建SMIC40文件夹。

在xterm中,输入mkdir SMIC40然后进入新建的SMIC40文件夹,在xterm中,输入cd SMIC40.f.关联SMIC40nm 工艺库在xterm窗口中,输入gedit&,(gedit为文档编辑命令)将以下内容拷贝到新文档中。

SOFTINCLUDE /soft1/cadence/IC5141/share/cdssetup/dfII/cds.lib SOFTINCLUDE /soft1/cadence/IC5141/share/cdssetup/hdl/cds.lib SOFTINCLUDE /soft1/cadence/IC5141/share/cdssetup/pic/cds.lib SOFTINCLUDE /soft1/cadence/IC5141/share/cdssetup/sg/cds.libDEFINE smic40llrf /soft2/eda/tech/smic040/pdk/SPDK40LLRF_1125_2TM_CDS_V1.4/smic40llrf_1 125_2tm_cds_1P8M_2012_10_30_v1.4/smic40llrf保存为cds.lib 。

7两级CMOS运算放大器设计分析

1 RII C II

西安电子科技大学

有补偿两级运放的小信号模型

相位裕度(Phase Margin)

失调电压(Offset Voltage) 建立时间(Setting Time)

45< PM< 75

VOS<20mV TSET<1us

电源抑制比(PSRR)

共模抑制比(CMRR)

>60dB

>60dB

输出电压摆幅(Output Voltage Swing) >1.5V(Rail-to-Rail:0~3.3V)

11

西安电子科技大学

两级CMOS运放的稳定性分析

也就是说,稳定性是由单位开环增益的相位值决定的,即由相位裕度决定。 所以系统稳定性的重要体现就是运放的相位裕度较大,一般运放的相位裕度 要求在60o左右。

12

西安电子科技大学

无补偿两级运放的小信号模型

无补偿运放的二阶模型,为使结果通用,用角标I表示第一级的元件,角标II代

芯片面积(Silicon Die Area)

6

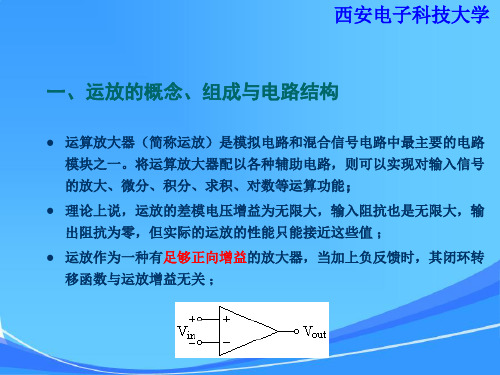

西安电子科技大学

两级CMOS运算放大器的基本结构

(a) 无补偿运放

(b)有补偿运放

M1和M2的宽长比相等,M3和M4的宽长比相等; 两级运放的电路具有两个高阻节点A和B,这就是说电路存在两个主极 点,因而降低了运放的相位裕度; 为了使运放稳定工作,通常在两级运放的第一级和第二级之间中加入 补偿电容,即在A点和B点之间加入补偿电容Cc(Miller电容),通过

导与输出阻抗的乘积来决定,因而一般都无法达到高的增益 ;

共源共栅结构虽然在一定程度上提高了电路增益,但是却限制了电路 的输出摆幅 ;

两级CMOS运算放大器设计

从CC和GB的表达式来确定输入晶体管的跨导,可以用下面方程来计算跨导gm2

gm2 GB CC

从而可直接求得输入晶体管M2的宽长比

W L2

gm22 K2` I5

西安电子科技大学

两级CMOS运算放大器的设计步骤(3)

下面利用共模电压范围(低电平)计算M5的饱和电压:

VDS5 Vin(min)I51VT1(max) 若VDS5<100mV,则可能会使(W/L)5过大,这是不可接受的。若VDS5<0V,则 说明所确定的共模范围CMR的技术规范太严了。为此,我们可以减小I5或增加 (W/L)1。注意,应考虑条件改变后对前面设计步骤的影呐。这样反复迭代,直 到获得满意的结果。由求得的VDS5及(W/L)5为

↓1/2

↑1/2

↑

L

W/L

↑

↑1/2

M7 补偿电容 CC

L

↑

增大GB

↑1/2

↑1/2

↓

增大RHP零点

↑1/2

↑1/2

↓

增大SR

↑

↓

增大 CL

↑

在完成以上计算和设计后,可以采用Spice仿真软件进行仿真验证。

西安电子科技大学

四、两级运放的仿真和测试

仿真是对设计的细化和验证,对精度的提高,对 性能的优化,是一个主次逼近理想值的过程。

运放平衡时有:I5=I6=I7,因此可得:

W L7

WL5

I6 I5

最后检查运放的总增益和运放功耗:

AV I522g3m 2Ig6m 667

如果增益太低,许多参数还可再做调整。

西安电子科技大学

运放的性能与器件、电流之间的关系

漏极电流

M1和M2 M3和M4 M6

CMOS 两级运算放大器设计

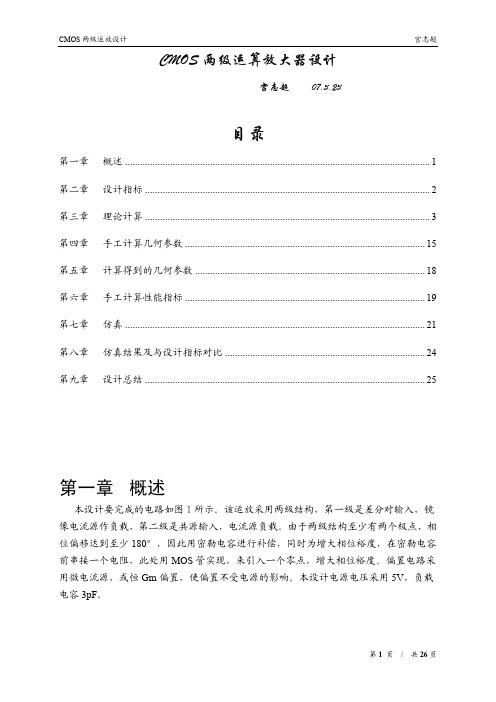

第一章 概述

本设计要完成的电路如图 1 所示。该运放采用两级结构,第一级是差分对输入,镜 像电流源作负载,第二级是共源输入,电流源负载。由于两级结构至少有两个极点,相 位偏移达到至少 180°,因此用密勒电容进行补偿,同时为增大相位裕度,在密勒电容 前串接一个电阻,此处用 MOS 管实现,来引入一个零点,增大相位裕度。偏置电路采 用微电流源,或恒 Gm 偏置,使偏置不受电源的影响。本设计电源电压采用 5V,负载 电容 3pF。

1

M1 VN

M2 VP

2

3

M3

M4

GND 图 3 第一级等效电路

图 4 第一级小信号等效电路

由图 4 得第一级共模增益

− 1 || ro3,4

Acm1 ≈

2gm3,4 2

1 2 g m1,2

+

ro5

≈− 1

gm1,2

1 + 2gm1,2ro5 gm3,4

两级运放的 CMRR 与第一级的 CMRR 相等,故

0.9(VDD-VSS)]

静态功耗 开环直流增益 单位增益带宽

≤ 2mW ≥ 80 dB Maximize

相位裕量 转换速率 共模抑制比 负电源抑制比 等效输入噪声

≥ 60 degree ≥ 30 V/us ≥ 60dB ≥ 80dB ≤ 300 nV/rt Hz@1KHz

第 2 页 / 共 26 页

+ RO (Cc

+ CL )⎤⎦ +1

其中 ξ = CECc + CECL + CcCL

在 CE << Cc ,CL 时,两个极点分别为

( )( ) ( ) ( ) ( ) ϖ p1 = RS

(完整word版)CMOS二级密勒补偿运算放大器的设计

课程设计报告设计课题:CMOS二级密勒补偿运算放大器的设计姓名:XXX专业:集成电路设计与集成系统学号:1115103004日期2015年1月17日指导教XXX师:国立华侨大学信息科学与工程学院一:CMOS二级密勒补偿运算放大器的设计1:电路结构最基本的CMOS二级密勒补偿运算跨导放大器的结构如下图,主要包括四部分:第一级PMOS输入对管差分放大电路,第二级共源放大电路,偏置电路和相位补偿电路.2:电路描述:输入级放大电路由M1~M5组成。

M1和M2组成PMOS差分输入对管,差分输入与单端输入相比可以有效抑制共模信号干扰;M3和M4为电流镜有源负载;M5为第一级放大电路提供恒定偏置电流.输出级放大电路由M6和M7组成,M6为共源放大器,M7为其提供恒定偏置电流同时作为第二级输出负载。

偏置电路由M8~M13和Rb组成,这是一个共源共栅电流源,M8和M9宽长比相同.M12和M13相比,源级加入了电阻Rb,组成微电流源,产生电流Ib。

对称的M11和M12构成共源共栅结构,减少了沟道长度调制效应造成的电流误差。

在提供偏置电流的同时,还为M14栅极提供偏置电压。

相位补偿电路由M14和Cc组成,M14工作在线性区,可等效为一个电阻,与电容Cc一起跨接在第二级输入输出之间,构成RC密勒补偿。

3:两级运放主体电路设计由于第一级差分输入对管M1与M2相同,有R1表示第一级输出电阻,其值为则第一级的电压增益对第二级,有第二级的电压增益故总的直流开环电压增益为所以4:偏置电路设计偏置电路由M8~M13 构成,其中包括两个故意失配的晶体管M12 和M13,电阻RB 串联在M12 的源极,它决定着偏置电流和gm12,所以一般为片外电阻以保证其精确稳定。

为了最大程度的降低M12 的沟道长度调制效应,采用了Cascode 连接的M10以及用与其匹配的二极管连接的M11 来提供M10 的偏置电压。

最后,由匹配的PMOS器件M8 和M9 构成的镜像电流源将电流IB 复制到M11 和M13,同时也为M5 和M7提供偏置。

CMOS二级运算放大器设计

CMOS二级运算放大器设计(东南大学集成电路学院)一.运算放大器概述运算放大器是一个能将两个输入电压之差放大并输出的集成电路。

运算放大器是模拟电子技术中最常见的电路,在某种程度上,可以把它看成一个类似于BJT 或 FET 的电子器件。

它是许多模拟系统和混合信号系统中的重要组成部分。

它的主要参数包括:开环增益、单位增益带宽、相位阈度、输入阻抗、输入偏流、失调电压、漂移、噪声、输入共模与差模围、输出驱动能力、建立时间与压摆率、CMRR、PSRR以及功耗等。

二.设计目标1.电路结构最基本的COMS二级密勒补偿运算跨导放大器的结构如图1.1所示。

主要包括四部分:第一级输入级放大电路、第二级放大电路、偏置电路和相位补偿电路。

图1.1 两级运放电路图2.电路描述电路由两级放大器组成,M1~M4构成有源负载的差分放大器,M5提供该放大器的工作电流。

M6、M7管构成共源放大电路,作为运放的输出级。

M6 提供给 M7 的工作电流。

M8~M13组成的偏置电路,提供整个放大器的工作电流。

相位补偿电路由M14和Cc 构成。

M14工作在线性区,可等效为一个电阻,与电容Cc 一起跨接在第二级输入输出之间,构成RC 密勒补偿。

3.设计指标两级运放的相关设计指标如表1。

表1 两级运放设计指标三.电路设计第一级的电压增益:)||(422111o o m m r r g R G A == (3.1) 第二级电压增益:)||(766222o o m m r r g R G A =-=(3.2)所以直流开环电压增益:)||)(||(76426221o o o o m m o r r r r g g A A A -== (3.3) 单位增益带宽:cm O C g A GBW π2f 1d == (3.4)偏置电流:213122121)/()/()/(2⎪⎪⎭⎫ ⎝⎛-=L W L W R L W KP I B n B (3.5) 根据系统失调电压:756463)/()/(21)/()/()/()/(L W L W L W L W L W L W == (3.6)转换速率:⎭⎬⎫⎩⎨⎧-=L DS DS C DS C I I C I SR 575,min (3.7)相位补偿:12.1)/()/()/()/(1613111466+==m m m C g g L W L W L W L W g R (3.8)以上公式推导过程简略,具体过程可参考相关专业书籍。

《2024年CMOS高性能运算放大器研究与设计》范文

《CMOS高性能运算放大器研究与设计》篇一一、引言随着微电子技术的快速发展,CMOS(互补金属氧化物半导体)技术已成为现代集成电路设计的主流技术。

运算放大器(Op-Amp)作为电子系统中的关键组件,其性能的优劣直接影响到整个系统的性能。

因此,对CMOS高性能运算放大器的研究与设计具有重要的实际应用价值。

本文将重点研究CMOS高性能运算放大器的设计原理、性能优化以及实际应用。

二、CMOS运算放大器的基本原理CMOS运算放大器是一种利用CMOS工艺制造的模拟电路器件,具有高精度、低噪声、低功耗等优点。

其基本原理是通过差分输入、差分输出以及电压增益等方式实现信号的放大和处理。

CMOS运算放大器的核心部分是差分对管和反馈网络,通过合理的电路设计和参数优化,可以实现高性能的运算放大器。

三、CMOS高性能运算放大器的设计1. 电路结构设计:CMOS高性能运算放大器的电路结构设计是关键。

在设计中,需要考虑差分对管的匹配性、反馈网络的稳定性以及噪声的抑制等因素。

常用的电路结构包括折叠式共源共栅结构、套筒式结构等。

这些结构在实现高电压增益的同时,还需要考虑功耗、噪声等性能指标的优化。

2. 参数优化:在CMOS高性能运算放大器的设计中,参数优化是必不可少的环节。

通过对差分对管的尺寸、偏置电流、反馈网络的电阻值等参数进行优化,可以提高运算放大器的性能。

此外,还需要考虑电路的匹配性、温度稳定性等因素,以确保运算放大器在不同条件下的性能稳定性。

3. 工艺选择:CMOS工艺的选择对运算放大器的性能有着重要影响。

在设计中,需要根据实际需求选择合适的工艺,如特征尺寸、阈值电压等。

同时,还需要考虑工艺的成熟度、生产成本等因素。

四、性能优化1. 增益与带宽:为了提高CMOS高性能运算放大器的性能,需要优化其增益和带宽。

通过合理的电路设计和参数优化,可以提高运算放大器的增益,同时保证足够的带宽以满足实际应用需求。

2. 噪声抑制:噪声是影响CMOS运算放大器性能的重要因素之一。

折叠式共源共栅CMOS运算放大器的设计

折叠式共源共栅CMOS运算放大器的设计该电路由两级放大器组成,第一级为共源放大器,第二级为共栅放大器。

下面将详细介绍各个部分的设计步骤和注意事项。

1.设计共源放大器:共源放大器的设计旨在实现高电压增益、宽带宽和稳定的工作点。

主要的设计步骤如下:-根据所需的增益和带宽确定工作点的直流电压和电流。

一般而言,直流电压应足够大,以提供足够的电压增益;而直流电流应适中,以保持功耗的合理范围。

-选择合适的晶体管尺寸和W/L比例,以满足所需的增益和带宽要求。

通常情况下,尺寸越大,增益越高,但同时也会增加功耗。

-设计偏置电路,用以稳定工作点,并提供所需的电流。

常见的偏置电路包括电流镜和电流源。

2.设计共栅放大器:共栅放大器的设计目标是进一步提高增益和带宽,并提供合适的输出电压。

以下是一些重要的设计考虑因素:-通过选择适当的晶体管尺寸和W/L比例,以满足所需的功率增益和输出电压范围。

与共源放大器类似,通常情况下尺寸越大,输出电压范围越大。

-需要设计合适的负载电路,以提供合适的输出电压和输出电流。

常见的负载电路包括电流镜和电流源。

3.总体电路优化:在设计过程中,需要进行一系列的优化步骤,以满足设计要求。

以下是一些常见的优化技术:-频率补偿:通过选择合适的补偿电容和电阻,提高电路的带宽和稳定性。

-去耦电容:通过添加适当的去耦电容,提高电路的低频响应和直流工作点稳定性。

-噪声优化:通过减小晶体管尺寸、优化偏置电路等措施,减小电路的噪声。

综上所述,折叠式共源共栅CMOS运算放大器的设计需要考虑多个方面,包括增益、带宽、工作点、输出电压范围等。

通过合理选择晶体管尺寸和W/L比例、设计合适的负载电路和偏置电路,以及进行适当的优化,可以实现高性能的运算放大器设计。

最后,需要进行电路的仿真和验证,以确保设计的性能符合预期要求。

两级CMOS运算放大器设计

两级CMOS运算放大器设计引言CMOS运算放大器是现代电路设计中的重要组成部分,它在模拟电路中扮演着关键的角色。

CMOS运算放大器由于其低功耗、高增益和较低的失调电压而备受青睐。

本文将介绍两级CMOS运算放大器的设计方法,包括电路结构、工作原理以及性能指标。

电路结构两级CMOS运算放大器由两个级联的CMOS差动放大器组成,它们的输出分别连接在第二级差动放大器的输入上。

这种结构能够提供更高的增益和更好的线性度。

差动放大器差动放大器是CMOS运算放大器的关键组成部分,它用于将输入信号转换为差模信号,并放大差模信号以提供一个具有高增益的输出。

CMOS差动放大器由一对输入端和一对输出端组成,每个输入端都连接了一个NMOS和一个PMOS管,这样可以实现单端输入和差分输入。

工作原理两级CMOS运算放大器的工作原理如下:1.输入信号被差动放大器的第一级转换为差模信号,并经过第一级放大。

第一级放大的输出信号被传递给第二级放大器。

2.第二级差动放大器放大差模信号,然后将其转换为单端输出信号。

3.输出信号经过一个输出级,通过一个负反馈回路被注入到第二级差动放大器的输入上。

设计步骤下面是设计两级CMOS运算放大器的一般步骤:1.确定电路的性能指标,例如增益、带宽以及失调电压等。

2.根据给定的性能指标选择差动放大器和输出级的电路结构。

3.根据选择的电路结构计算电路的参数,例如电阻、电容和晶体管的尺寸等。

4.使用电路模拟工具,例如SPICE,对电路进行仿真和优化。

5.布局电路,并进行布线。

6.进行电路的后仿真和测试。

性能指标两级CMOS运算放大器的性能指标通常包括以下几个方面:1.增益:运算放大器的增益是指输出信号相对于输入信号的放大程度。

在设计过程中,需要根据实际应用需求确定所需的增益。

2.带宽:带宽是指运算放大器能够输出一个相对稳定的放大信号的频率范围。

一般来说,带宽越大,运算放大器的性能越好。

3.失调电压:失调电压是指实际输入和理论输入之间的偏差。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

CMOS两级运算放大器设计及仿真

实验报告

班级:

学号:

姓名:

日期:

一、运算放大器设计简介

运算放大器是许多模拟及数模混合信号系统中一个十分重要的部分。

各种不同复杂程度的运放被用来实现各种功能:从直流偏置的产生到高速放大或滤波。

运算放大器的设计可分为两个步骤。

第一步是选择或搭建运放的基本结构,绘出电路结构草图。

确定好的电路结构不能轻易修改。

运算放大器的电路结构确定之后需要选择直流电流,手工设计管子尺寸,以及设计补偿电容等关键参数。

为了满足运放的交流和直流需要,所有管子必须设计出合适尺寸。

在手工计算的基础上,运用CandenceVirtuoso电路设计软件进行图形绘制,参数赋值,仿真分析。

在分析仿真结果的基础上判断电路是否符合设计要求。

若不符合,再回到手工计算,调试电路。

二、设计目标

电路参数要求:

(1)直流或低频时的小信号差模电压增益

Avd = 4000V/V(72dB)

(2)增益带宽积

GBW = 10MHz

(3)输入共模电压范围

Vcm,min = 0.4V,Vcm,max = 1.5V

(4)输出电压摆幅

0.2V < Vout < 1.5V

(5)相位裕度

PM = 60

(6)负载电容

CL = 1pF

(7)电源电压

VDD = 1.8V

使用CMOS-90nm工艺库。

三、电路设计

1.电路结构

最基本的CMOS二级密勒补偿运算跨导放大器的结构如下图所示。

主要包括四大部分:第一级双端输入单端输出差分放大级、第二级共源放大级、直流偏置电路及密勒补偿电路。

2.电路描述

输入级放大电路由PM0、PM2、NM1、NM3组成,其中PM0与PM2组成电流源偏置电路,NM1与NM3组成差分放大电路,输入端分别为IN1和IN2,单端输出。

如下图所示。

输出级放大电路由PM1和NM4组成,其中PM1为共源放大级电路,NM4为电流源偏置电路。

如下图所示。

电流源偏置电路由NM0、NM2与NM4组成,其中NM0接偏置电流源,电流源电流为30uA。

如下图所示。

选取电源电压为1.8V。

共模输入电压设为500mV,差模输入电压设IN1、IN2为5uV交流小信号,方向相反。

如下图所示。

3.参数估计

第一级放大电路的电压增益:

第二级放大电路的电压增益:

两级放大电路总增益:

增益带宽积:

设置直流工作点:

对单个nmos管进行gm/Id、Id/w与Vgs图形仿真,如下图所示。

取gm/Id为10,Vgs为0.3V,可得差动放大级单边电路偏置电流为15uA。

根据镜像电流源的特性可设置Iref为30uA。

设置第二级共源放大级直流偏置电流为34.3uA。

宽长比计算如下:

偏置电路:

NM0 4.5

NM2 4.5

NM4 5.15

差分放大电路:

PM0 1.875

PM2 1.875

NM1 15

NM3 15

共源放大级:

PM1 4.7

密勒补偿电路参数配置

Rc 10K

Cc 3pF

四、仿真调试

测试环境搭建。

tran为扫频时间,设置输入信号频率为1KHz,因此tran值设置为10ms。

扫频范围为1至100GHz。

并保存直流工作点信息。

如下图所示。

测试第一级差动放大级的放大倍数。

如下图所示。

放大倍数大约为250倍,红色线条为第一级输出。

相当于本征放大增益的平方。

测试两级放大电路的放大倍数。

如下图所示。

四条波形线分别为差动输出级、IN1、IN2、OUT。

便于观察放大倍数,将放大倍数及带宽截图如下。

放大倍数约为11000倍,带宽为1KHz。

因此增益带宽积大于10 MHz。

相位与放大倍数的关系如下图所示。

在增益降为0dB的时候,相位降幅大约为110度,即相位裕度大约为70度。

五、实验结果

电路仿真参数:

(1)直流或低频时的小信号差模电压增益

Avd = 11000V/V(80dB)

(2)增益带宽积

GBW = 11MHz

(3)输入共模电压

Vcm = 0.5V

(4)输出电压

1.3V < Vout < 1.4V

(5)相位裕度

PM = 70度

(6)负载电容

CL = 1pF

(7)电源电压

VDD = 1.8V

(8)密勒补偿电容及电阻

Rc = 10K

Cc = 3pF

仿真参数满足设计要求。