基于FPGA的VGA图像显示控制器设计

基于FPGA的VGA接口显示的设计与实现

编号基于FPGA的VGA接口显示的设计与实现Design and implementation of VGAinterface based on FPGA display学生姓名王雪专业控制科学与工程学号S120400520指导教师杨晓慧学院电子信息工程学院二〇一三年六月摘要利用现场可编程逻辑器件FPGA产生VGA时序信号和彩条图像信号,并将其作为信号源,应用于彩色等离子显示器的电路开发,方便彩色等离子显示器驱动控制电路的调试。

FPGA芯片具有可靠性高、编程灵活、体积小等优点,实验经过软硬件调试,最终在显示器上显示彩条正确图像。

利用此原理,可以设计更多的彩色图像,且可将采集的图像进行实时显示,将此作为信号源,应用于显示器电路的开发或某些嵌入式系统中,进行视频设备的调试与性能分析或系统中信号处理模块的调试与性能分析等。

关键词:FPGA VGA接口时序控制彩条信号AbstractVGA-timing signals and color strip image were obtained by using FPGA.The signals were used as sources when developing the circuits of color plasma display panel, and it took great convenience to the debugging of the driving and controlling circuit of color plasma display panel.The FPGA chip has the advantages of high reliability, small volume, flexible programming,just because of this,the test could achieve the desired results,display scree displays color bar signals.According to this principle, we can design color image more, and make the image real-time display, such as the signal source, used in display circuit development or some embedded systems, video equipment debugging and performance analysis of the system signal processing module debugging and performance analysis.Keywords:FPGA, VGA interface,timing control, color bar signals目录摘要 (1)Abstract (2)第一章引言 (4)第二章VGA显示接口的方案设计和原理 (5)2.1 VGA接口 (5)2.2 VGA显示原理 (5)2.3 VGA信号时序 (6)2.4 VGA显示方案实现 (7)第三章系统模块设计 (8)3.1系统模块原理图 (8)3.2 分频模块 (8)3.3 VGA彩条信号产生模块 (8)3.4 实验结果 (12)第四章结论 (13)致谢 (14)参考文献 (15)第一章引言视频图形阵列(VGA)作为一种标准的显示接口已经得到广泛的应用。

基于FPGA-CPLD的VGA显示系统设计

基于FPGA/CPLD的VGA显示系统设计和数据的存储。

用FPGA 对图像进行存储和整理,并产生驱动电路需要的各种控制波形由视频控制器对颜色缓冲器进行扫描,其中视频控制器可以读取像素颜色,用这些颜色来控制输出设备的亮度。

VGA 时序发生器模块产生显示器所需的时序,这是完成设计的关键,时序稍有偏差,显示必然不正常,甚至会损坏彩色显示器。

3、VGA 时序分析显示器采用光栅扫描方式,即轰击荧光屏的电子束在CRT(阴极射线管)屏幕上从左到右(受水平同步信号HSYNC 控制)、从上到下(受垂直同步信号VSYNC 控制)做有规律的移动。

光栅扫描又分逐行扫描和隔行扫描。

隔行扫描指电子束在扫描时每隔一行扫一线,完成一屏后再返回来扫描剩下的线,与电视机的原理一样。

隔行扫描的显示器扫描闪烁的比较厉害,会让使用者的眼睛疲劳。

目前微机所用显示器几乎都是逐行扫描。

逐行扫描是指扫描从屏幕左上角一点开始,从左向右逐点进行扫描,每扫描完一行,电子束回到屏幕的左边下一行的起始位置,在这期间,CRT 对电子束进行消隐,每行结束时,用行同步信号进行行同步;当扫描完所有行,形成一帧时,用场同步信号进行场同步,并使扫描回到屏幕的左上方,同时进行行场消隐,开始下一帧的扫描。

完成一行扫描所需时间称为水平扫描时间,其倒数称为行频率;完成一帧(整屏)扫描所需的时间称为垂直扫描时间,其倒数为垂直扫描频率,又称刷新频率,即刷新一屏的频率。

常见的有60Hz、75Hz 等。

VGA 显示器要正确显示图像关键还是如何实现VGA 时序。

视频电子标准协会( VESA, Video Electronics Standards Association)对显示器时序进行了规范。

VGA 的标准参考显示时序如图2、图 3 所示。

行时序和场时序都需要产。

基于FPGA的VGA显示控制器设计 (2)

页眉内容课程设计开课学期:第六学期课程名称:FPGA课程设计学院:专业:班级:学号:姓名:任课教师:2015 年7 月20日基于FPGA的VGA显示控制器设计一、设计方案1.设计的主要内容此设计要求实现某一分辨率下(如640*480@60Hz)的VGA显示驱动,能简单显示彩条和图像等。

能够熟悉VGA接口协议、工作时序及VGA工作原理,并计算出合适的时序,对原始时钟进行分频处理以获取符合时序要求的各率,此外须要显示的图像等可存储于外部存储器,运行时,从外部存储器读取显示数据。

将图像控制模块分为这样几部分;二分频电路、地址发生器、VGA时序控制模块、图像数据存储器读出模块.如图1-1所示:图1-1VGA显示控制系统框图2.设计原理显示控制器是一个较大的数字系统,采用模块化设计原则、借鉴自顶向下的程序设计思想,进行功能分离并按层次设计。

利用VHDL硬件描述语言对每个功能模块进行描述,并逐一对每个功能模块进行编译仿真,使顶层VGA显示控制器的模块实体仿真综合得以顺利通过。

其中二分频把50MHZ实在频率分成25Mhz并提供给其它模块作为时钟;VGA时序控制模块用于产生640X480显示范围,并控制显示范围和消隐范围以及产生水平同步时序信号HS和垂直同步时序信号VS的值;存储器读出模块提供给SRAM地址并按地址读出八位数据(灰度值Y),然后得到R、G、B的值(若Y>中间值,则R=G=B=1;否则R=G=B=0),并把R、G、B的值通过VGA接口传送给VRT显示器[9]。

地址发生器接收所要显示的数据读取控制信号,产生与图像数据ROM模块对应得地址,根据VGA显示的像素分布,确定读取对应数据的地址,由于所显示的图形每行需256个像素,而ROM 中每个地址存储的数据时64位,故每4个地址取出的数据用于一行的显示。

VGA显示控制模块:主要分为时序信号和数据颜色的控制,imgrom模块即图像数据ROM模块,在这一模块中需要解决的是图像数据BMP位图文件的来源及转换成HEX文件,利用Image2lcd 对本次设计图片处理得到BMP文件,最终在QuartusII得到HEX文件,在已设置LPM_ROM 进行加载图像数据。

基于FPGA的VGA图形控制器

基于FPGA的VGA图形控制器设计引言VGA(视频图形阵列)作为一种标准的显示接口得到广泛的应用。

利用FPGA 芯片和EDA 设计方法,可以因地制宜,根据用户的特定需要,设计出针对性强的VGA 显示控制器,不仅能够大大降低成本,还可以满足生产实践中不断变化的用户需要,产品的升级换代方便迅速。

在本设计中采用了Altera 公司的EDA 软件工具Quartus II ,并以ACEX系列FPGA 的器件为主实现硬件平台的设计。

1 基于FPGA 的VGA 图形控制器系统框图根据自顶向下的程序设计思想,采用模块化设计,我们对VGA 图形控制器进行功能分离并按层次设计。

利用VHDL 硬件描述语言逐一对每个功能模块进行描述,并逐个通过编译仿真,最后下载到硬件平台调试。

本设计的VGA 控制器主要由以下模块组成:VGA 时序控制模块、分频模块、汉字显示模块、图像控制模块、ROM读取模块等,如图1 所示。

图1 基于FPGA 的VGA 图形控制系统框图2 主要功能模块设计2. 1 VGA 时序控制模块VGA 时序控制模块是整个显示控制器的关键部分,最终的输出信号行、场同步信号必须严格按照VGA 时序标准产生相应的脉冲信号。

对于普通的VGA 显示器,其引出线共含5 个信号: G,R ,B (3 基色信号) ,HS (行同步信号) ,VS(场同步信号)。

在5个信号时序驱动时,VGA 显示器要严格遵循“VGA工业标准”,即640 Hz ×480 Hz ×60Hz 模式。

对于VGA 显示器,每个像素点的输出频率为25. 175MHz ,因此采用50MHz 的时钟信号,经过二分频模块,得到25MHz 的输入时钟脉冲。

依据VGA 时序标准,行同步信号HS ,行周期为31. 78μs ,每显示行包括800 点,其中640 点为有效显示区,160 点为行消隐区,每行有一个脉冲,该脉冲的低电平宽度为3. 81μs (即96 个脉冲) ; 场同步信号VS ,场周期为16.683ms ,每场有525 行,其中480 行为有效显示行,45 行为场消隐区,每场有一个脉冲,该脉冲的低电平宽度为63μs (2 行)。

基于FPGA的VGA图形控制器设计

i mp l e me n t t h e h o r i z o n t a l s t r i p e,v e r t i c a l s t r i p e ,l a t t i c e b o a r d a n d S O o n w i t h 8 b i t c o l o r g r a p h i c d i s p l a y .

逻 辑描 述 语 言 . 在 X i l i n x的 开 发 板 N e x y s 2上 完 成 了设 计 的 功 能 。 通 过 按 动 开 发 板 上 的 按 键 可 切 换 显 示 屏 显 示 的 图形 , 可 实现 横 条 纹 、 竖条纹、 方格 棋 盘 等 8 h i t 彩 色图形 的 显 示 。

Ke y wo r d s: VGA;F P GA; g r a p h i c s c o n t r o l l e r ;8 b i t c o l o r g r a p h

随 着 电 子 技 术 的 进 步 和 数 字 图 像 处 理 应 用 领 域 的

过 软件进 行 的, 通用性 和灵 活性极 强 。 在产 品升级 时 , 不

关 键 词 :VG A; F P G A; 图形控 制 器 ; 8 b i t彩 色 图 形

中 图 分 类 号 :T P 3 3 4 . 7 文 献 标 识 码 :A 文 章 编 号 :1 6 7 4 — 7 7 2 0( 2 0 1 3) 1 5 — 0 0 2 2 — 0 3

De s i g n o f VGA g r a ph i c s c o n t r o l l e r ba s e d o n FPGA

需 要额 外 改变 原有 的硬 件 电路 , 只需 修 改程 序 , 大 大 宿 短 了 系 统 设 计 周 期 。N e x y s 2作 为 一 款 比 较 经 典 的 F P GA

基于FPGA进行VGA控制器设置实现显示器条纹显示

基于FPGA进行VGA控制器设置实现显示器条纹显示实验目的与要求:VGA控制器设计实现显示器条纹显示要求:通过FPGA板的VGA接口在显示器上显示一幅640*480由六条不同颜色的条纹组成的图像。

实验内容:VGA简介VGA彩色显示器,彩色是由R、G、B(红、绿、蓝)三基色组成,CRT用逐行扫描方式实现图像显示,由VGA控制模块产生的水平同步信号(HS)和垂直同步信号(VS)控制阴极射线枪产生的电子束,打在涂有荧光粉的荧光屏上,产生R、G、B三基色,合成一个彩色像素。

扫描从屏幕的左上方开始,由左至右,由上到下,逐行进行扫描,每扫完一行,电子束回到屏幕下一行的起始位置,在回扫期间,CRT对电子束进行消隐,每行结束是用行同步信号HS进行行同步;扫描完所有行,再由场同步信号VS进行场同步,并使扫描回到屏幕的左上方,同时进行场消隐,预备下一场的扫描。

显示需要R,G,B,Hsync(行同步),Vsync(帧同步)五个信号输出到显示器,本设计按照VGA工业标准输出640*480@60Hz.对应的时序如下:图1 VGA接口信号基本时序图图2 FPGA板上的VGA接口图3 VGA(640*480@60Hz)时序图VGA显示的设计模块为:hsclkvsVGA显示模r块grst_nb说明:设计中FPGA板的VGA接口将R,G,B分别设为定义为2位,3位,3位,例如显示红色RGB可以输出为11000000,绿色输出为00111000,蓝色输出为00000111.表1 25MHz 640*480@60Hz模式下VGA的时序规格说明1. 像素时钟配置为25Mhz。

2. 编写代码时,需要用到的常数参考表一。

3. 输出到显示器上的条纹为从上到下依次为R G B R G B,640*80,。

4. 本实验使用FPGA板:Sparant3EXC3S500E,建project时,需要选择板的型号,。

实验方法、步骤:1、基本设计思想如下图所示:分为这四个模块,产生Hsync(行同步),Vsync(帧同步)以及RGB色彩的输出。

基于FPGA的VGA图像显示系统的设计

基于FPGA的VGA图像显示系统的设计杜宗展;王振河;冯迎春【期刊名称】《现代电子技术》【年(卷),期】2015(38)16【摘要】As a standard display interface,VGA(video graphics array)has been widely used. According to the principles of VGA and FPGA(field programmable gate array),the designed VGA interface based on FPGA can send the data to the dis-play directly,and grayscale of the output image was added to this design. Compared to the traditional design,there is no com-puter processing procedure in the design,which can save the expense of hardware and enhance the speed of data processing. It is widely used to the domain of video display.%VGA(视频图形阵列)是一种标准的显示接口,被广泛应用.根据VGA,FPGA(现场可编程门阵列)的作用原理,设计的基于FPGA的VGA 接口可以直接将数据送至显示器,同时增添了关于输出图像灰度等级的设计.与传统设计相比,该设计没有计算机的处理过程,可节省硬件成本,加快数据处理速度,被广泛应用到视频显示领域.【总页数】5页(P95-99)【作者】杜宗展;王振河;冯迎春【作者单位】山东大学电气工程学院,山东济南 250061;山东电力集团公司检修公司,山东济南 250061;山东电力集团公司检修公司,山东济南 250061【正文语种】中文【中图分类】TN919-34;TP391.8【相关文献】1.基于FPGA的VGA图像显示系统的设计与实现 [J], 周卓然;徐道连;吕凤飞;付少华2.基于FPGA的VGA图像显示控制的设计和实现 [J], 李云;刘桂华3.基于FPGA的VGA图像显示及控制系统的设计与实现 [J], 李营;吕兆承;陈帅;权循忠4.基于FPGA的VGA图像显示设计 [J], 桂淮濛5.基于FPGA的UART控制VGA图像显示器设计 [J], 李营; 范静静; 权循忠; 吕兆承; 陈帅因版权原因,仅展示原文概要,查看原文内容请购买。

课程设计基于FPGA的VGA图像汉字显示及-PS-2键盘控制设计与应用 精品

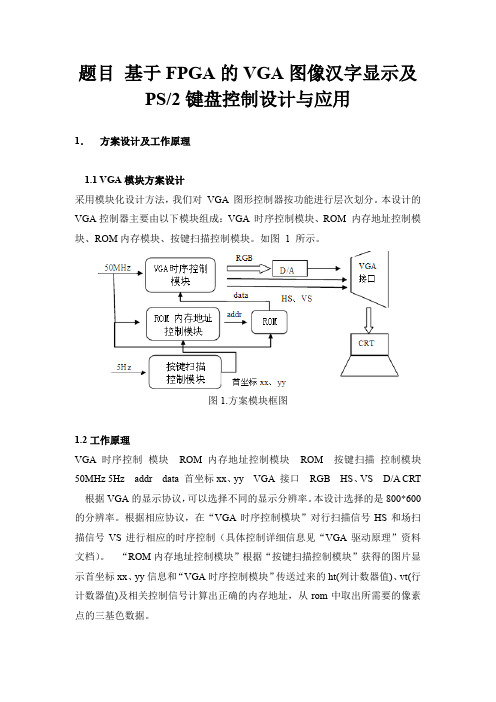

题目基于FPGA的VGA图像汉字显示及PS/2键盘控制设计与应用1.方案设计及工作原理1.1 VGA模块方案设计采用模块化设计方法,我们对VGA 图形控制器按功能进行层次划分。

本设计的VGA控制器主要由以下模块组成:VGA 时序控制模块、ROM 内存地址控制模块、ROM内存模块、按键扫描控制模块。

如图 1 所示。

图1.方案模块框图1.2工作原理VGA时序控制模块ROM内存地址控制模块ROM 按键扫描控制模块50MHz 5Hz addr data 首坐标xx、yy VGA 接口RGB HS、VS D/A CRT 根据VGA的显示协议,可以选择不同的显示分辨率。

本设计选择的是800*600的分辨率。

根据相应协议,在“VGA时序控制模块”对行扫描信号HS和场扫描信号VS进行相应的时序控制(具体控制详细信息见“VGA驱动原理”资料文档)。

“ROM内存地址控制模块”根据“按键扫描控制模块”获得的图片显示首坐标xx、yy信息和“VGA时序控制模块”传送过来的ht(列计数器值)、vt(行计数器值)及相关控制信号计算出正确的内存地址,从rom中取出所需要的像素点的三基色数据。

1.3 PS/2接口电路的工作原理PS/2协议和接口最初是IBM公司开发并推广使用的一种应用于键盘/鼠标的协议和接口,PS/2键盘按键接口是6芯的插头与PC机的键盘相连接,插头、插座定义如图所示。

键盘/鼠标接口的数据线和时钟线采用集电极开路结构,平时都是高电平当这些设备等待发送数据时,它首先检查clock是否为高。

如果为低,则认为PC抑制了通讯,此时它缓冲数据直到获得总线的控制权。

如果clock为高电平,设备则开始向PC发送数据。

一般都是由ps2设备产生时钟信号。

发送按帧格式。

数据位在clock为高电平时准备好,在clock下降沿被PC读入。

图3所示是按下Q 键的时序图“Q”键的扫描码从键盘发送到计算机(通道A是时钟信号,通道B 是数据信号)。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

四川师范大学成都学院本科毕业设计基于FPGA的VGA图像显示控制器设计学生姓名郑旺明学号**********所在系电子工程系专业名称电子信息工程(工民电)班级2008级2班指导教师胡迎刚四川师范大学成都学院二○一二年五月摘要本文介绍了一种利用可编程逻辑器件实现VGA图像显示控制的方法,阐述了VGA 图像显示控制器中VGA显像的基本原理以及功能演示,利用可编程器件FPGA设计VGA 图像显示控制的VHDL设计方案,并在Altera公司的QuartusII软件环境下完成VGA模块的设计。

而且给出了VGA模块的设计思路和顶层逻辑框图。

最终实现VGA图像显示控制器,VGA图像控制器是一个较大的数字系统,传统的图像显示的方法是在图像数据传输到计算机,并通过显示屏显示出在传输过程中,将图像数据的CPU需要不断的信号控制,所以造成CPU的资源浪费,系统还需要依靠计算机,从而减少了系统的灵活性。

FPGA 芯片和EDA设计方法的使用,可根据用户的需求,为设计提供了有针对性的VGA显示控制器,不需要依靠计算机,它可以大大降低成本,并可以满足生产实践中不断改变的需要,产品的升级换代和方便迅速。

关键词:可编程逻辑器件 VGA 图像控制器AbstractThis paper introduces a kind of make use of the programmable logic devices realize VGA images show control method, and expounds the VGA images show controller VGA imaging the basic principle and the demo function, using the programmable device FPGA design VGA images show the control design VHDL, Altera company in the QuartusII software environment complete VGA module design. Given the VGA module, the design idea and top logic diagram. Finally realize the VGA image display controller, VGA image controller is a larger number system, the traditional image shows the method is in the image data transmission to the computer, and through the screen shows in the transmission process, the image data CPU requires constant signal control, therefore creates CPU resources waste, the system also need to rely on the computer, thus reducing the flexibility of the system. FPGA chip and EDA design method of use, can according to customer demand, designed to provide targeted VGA display controller, don't need to rely on the computer, it can greatly reduce the cost, and can satisfy the production practice changing needs, product upgrading and convenient quickly.Keywords:Programmable logic devices VGA Image controller目录前言 (1)第1章 VGA概述 (2)1.1 VGA显示技术的发展概况 (2)1.2 VGA显示接口 (3)1.3 VGA显示原理 (4)1.4 VGA时序 (6)第2章 FPGA简介及设计流程 (8)2.1 FPGA简介 (8)2.2 FPGA设计流程 (9)2.3 VHDL简介 (11)2.4 Quartus II简介 (12)第3章设计方案 (13)3.1 设计的主要内容 (13)3.2 设计原理 (13)第4章系统实现 (14)4.1 VGA显示控制模块 (14)4.2 imgrom(图像数据ROM) (17)4.2.1 图像原理 (17)4.2.2 具体实现步骤 (18)4.3 二分频模块 (21)4.4 地址发生器模块 (22)4.5 顶层设计 (22)4.6 设计结果 (23)第5章结束语 (24)附录 (26)显示扫描模块代码 (26)二分频器模块代码 (27)地址发生器模块代码 (28)参考文献 (28)前言现在社会,以计算机技术为核心的信息技术飞速发展,以及信息的爆炸式增长,人们获得很大一部分的视觉信息是从各种电子显示设备上获得的,为此对电子显示设备的要求也越来越高,在这些因素影响下,显示技术也取得了快速发展。

1987年IBM推出了一种高分辨率的视频传输标准即VGA(视频图形阵列),其具备显示速度快,分辨率高,和丰富的颜色等特点。

被广泛使用于彩色显示领域。

使用VGA显示控制器的FPGA设计有着高度的灵活性,并能够根据不同类型,规模,和不同的适用场合,尤其是工业产品,做一些特殊的设计,用最低的价格,满足系统的要求,并能解决一般显示控制器本身固有的一些点。

VGA图像控制器是一个较大的数字系统,传统的图像显示的方法是将图像数据传输到计算机,并通过显示屏显示出在传输过程中,在图像数据中的芯片需要不断的信号控制,所以造成芯片的资源浪费,系统还需要依靠计算机,从而减少了系统的灵活性。

采用FPGA芯片和EDA设计方法,可根据用户的需求,为设计提供了有针对性的VGA显示控制器,不需要依靠计算机,它可以大大降低成本,并可以满足生产实践中不断改变的需要,产品的升级换代和方便迅速。

第1章VGA概述伴随着市场上液晶显示器的出现,越来越多的数字产品开始使用液晶作为显示终端,不过基于VGA标准的显示器仍是目前普及率最高的显示器。

如果想要驱动此类显示器,必须得有很高的扫描频率,以及极短的处理时间,综合诸多特点需要,所以选用FPGA 来实现对VGA显示器的驱动。

本次毕业设计即选用FPGA来实现VGA的显示。

现在,基于FPGA的设计方案越来越被用于更多的嵌入式系统,在基于FPGA的大规模嵌入式系统设计中,为了更好的实现VGA显示功能,既能使用专用的VGA接口芯SPX7111A 等,又可以设计和使用基于FPGA的VGA接口软核,其优点在于能使用VGA专用芯片具有更稳定的VGA时序和更多的显示模式可供选择。

此外设计和使用VGA接口软核更具有以下几点优势:◆使用芯片更少,节省板上资源,布线难度大大减少。

◆当高速数据进行传输时,减少高频噪声干扰。

◆采用FPGA(现场可编程门阵列)设计的VGA接口可以将要显示的数据直接传送到显示器,跳过计算机的处理过程,加快了数据的处理速度,从而有利的节约硬件成本。

◆整体设计费用降低,产品更具有价格优势。

现代EDA软件发展迅速,设计、仿真更容易实现,量化设计中各个环节,使得设计周期日益缩短。

1.1 VGA显示技术的发展概况VGA接口,它是一种被广泛使用的标准显示接口,大多数的显卡和显示器之间,以及二色等离子的电视输入图像模数的转换上使用了VGA接口。

它同样还被用于LCD的液晶显示设备,随着微电子制造工艺的发展,可编程逻辑器件也取得了长久的进步,早期的元器件只可以存储很少的数据,逻辑功能实现更为简单,然而发展至今,其完成的逻辑功能相对复杂,规模更大,速度更快,功耗更低!现阶段可编程逻辑器件主要有两大类,现场可编程逻辑器件(FPGA)和复杂可编程逻辑器件(CPLD)。

FPGA的运行速度快,管脚资源更加丰富,大规模的系统设计的实现相对简单,大量软核可供使用用,有利于二次开发使用,不仅如此,而且FPGA具备可重构的能力,抗看等特点。

因此,工业控制及其他领域也更加重视使用FPGA,利用FPG完成VGA显示控制,可以使图像的显示脱离PC机的控制,形成体积小、功耗低的格式嵌入式系统(便携式设备或手持设备),使用地面勘测,性能检测等方面,具有重要的现实意义[1]。

本设计在FPGA开发板上使用VGA接口的显示器显示彩条及简单的图形,可以成为整个采集系统的参考设计,实用价值良好。

1.2 VGA显示接口VGA接口是一种D型接口,上面共有15针孔,分成三排,每排五个。

其中,除了2根NC(Not Connect)信号、3根显示数据总线和5个GND信号,比较重要的是3根RGB彩色分量信号和2根扫描同步信号HSYNC和VSYNC针[2]。

VGA接口是显卡上使用最为广泛的接口类型,多数的显卡都带有此种接口。

其排列及接口定义如图1.2-1所示:图1.2-1 VGA接口图在基于FPGA的VGA控制中,只需要考虑行场同步信号(Vs)、同步信号(Hs)、蓝基色(R)、红基色(B)、绿基色(G)这5个信号。

一旦能够从FPGA发出这5个信号到VGA接口,就表示可以实现对VGA的控制。

1.3 VGA显示原理VGA显示的图像原理:常见之彩色显示器,一般由CRT(即:阴极射线管)构成。

彩色则由R,G,B(红:RED,绿:GREEN,蓝:BLUE这三基色够成。

显示则采取逐行扫描得方式解决,使得从阴极射线枪中发出的电子束得以打在具有荧光粉得荧光屏上,产生R,G,三基色的彩色像素。

扫描随即开始从屏幕的左上方进行,从左到右,从上到下,进行扫描,每扫完了一行,电子束则返回于屏幕左边下面一行的初始位置,在这期间,CRT把电子束消隐了,每行完成结束时,行同步则采用行同步信号进行,扫描完所有行;场同步则采用场同步信号进行,并使扫描回到屏幕的左上方,同时场消隐进行,准备下一场的扫描。

它的行、场扫描时序示意图如图1.3-1所示。

现拿正极性分析,说明CRT 的全工作过程:R,G,B呈现正极性的信号,即视为高电平是有效的。

当VS=O、HS=O 时,CRT的内容被显示为亮的过程,即是正向扫描的过程大致为26s,当一行被扫描完成后,行同步HS=I,约需6s;其间,CRT的扫描会产生消隐,电子束即回到CRT的左边的下一行得起始位置(X=O,Y=I),当扫描完成了480行以后,场同步VS=I,场同步的产生使扫描线回到CRT得第一行第一列(X=O,Y=O处,大约两个行周期)。