74HC74PW中文资料

74HC74管脚排列中文资料

74HC74管脚排列

74HC74 概述

74HC74是一款高速CMOS器件,74HC74引脚兼容低功耗肖特基TTL (LSTTL)系列。

74HC74遵循JEDEC标准no.7A。

74HC74是双路D 型上升沿触发器,带独立的数据(D)输入、时钟(CP)输入、设置(SD)和复位(RD)输入、以及互补的Q和Q输出。

设置和复位为异步低电平有效,且不依赖于时钟输入。

74HC74数据输入口的信息在时钟脉冲的上升沿传输到Q口。

为了获得预想中的结果,D输入必须在时钟脉冲上升沿来临之前,保持稳定一段就绪时间。

74HC74时钟输入的施密特触发功能使得电路对于缓慢的脉冲上升和下降具备更高的容差性。

74HC74 特性

工作电压范围:2.0~6.0 V

对称输出阻抗

高抗扰

低功耗

ESD保护

HBM EIA/JESD22-A114-A超过2000 V

MM EIA/JESD22-A115-A超过200 V

74HC74 参数

74HC74 基本参数

电压 2.0~6.0V

驱动电流+/-5.2 mA

传输延迟14 ns@5V

74HC74 其他特性

逻辑电平CMOS

功耗考量低功耗或电池供电应用74HC74 封装与引脚

SO14, SSOP14, DIP14, TSSOP14。

74HC系列芯片资料

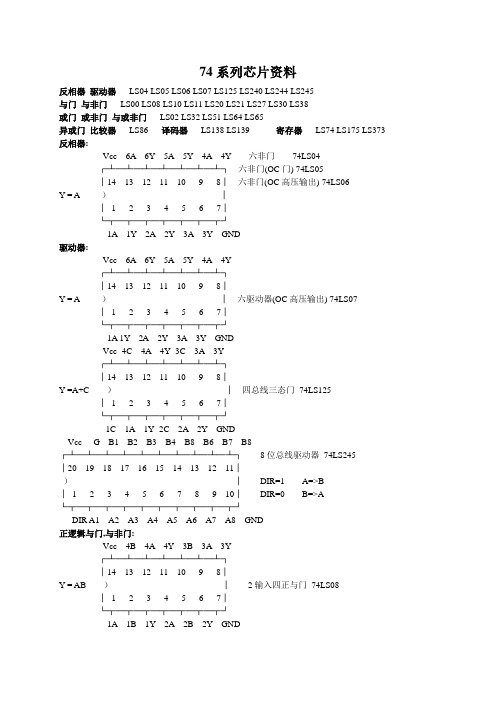

7474HC4052 74HC4053 74HC4060 74HC4066 74HC4075 74HC42 74HC423A 74HC4514 74HC4538A 74HC4543 74HC51 74HC521 74HC533 74HC534 74HC540 74HC541 74HC58 74HC589 74HC594 74HC595 74HC597 74HC620 74HC623 74HC640 74HC643 74HC646 74HC648 74HC688 74HC7266 74HC73 74HC74A 74HC75 74HC76 74HC85 74HC86 74HC942 74HC943 74LS00 74LS02 74LS03 74LS04 74LS05 74LS08 74LS09 74LS10 74LS109 74LS11 74LS112 74LS113 74LS114 74LS122 74LS123 74LS125 74LS160 74LS136 74LS138 74LS139 74LS14 74HC147 74HC148 74HC149 74LS151 74LS153 74LS155 74LS156 74LS157 74LS158 74LS160A 74LS161A 74LS162A 74LS163A 74LS164 74LS168 74LS169 74LS173 74LS174 74LS175 74LS190 74LS191 74LS192 74LS193 74LS194A 74LS195A 74LS20 74LS21 74LS240 74LS244 74LS245 74LS253 74LS256 74LS257 74LS258 74LS27 74LS279 74LS28 74LS283 74LS30 74LS32 74LS352 74LS367 74LS368A 74LS373 74LS76 74LS379 74LS38 74LS390 74LS393 74LS42 74LS48 74LS49 74LS51 74LS540 74LS541 74LS74 74LS682 74LS684 74LS75 74LS83A 74LS85 74LS86 74LS90 74LS95B 74LS688 74LS136 74LS651 74LS653 74LS670 74LS73A 74、74HC、74LS系列芯片资料2006-9-22 23:06系列 电平 典型传输延迟ns 最大驱动电流(-Ioh/Lol)mA AHC CMOS 8.5 -8/8AHCT COMS/TTL 8.5 -8/8HC COMS 25 -8/8HCT COMS/TTL 25 -8/8ACT COMS/TTL 10 -24/24F TTL 6.5 -15/64ALS TTL 10 -15/64LS TTL 18 -15/24注:同型号的74系列、74HC系列、74LS系列芯片,逻辑功能上是一样的。

74HC74中文资料_数据手册_参数

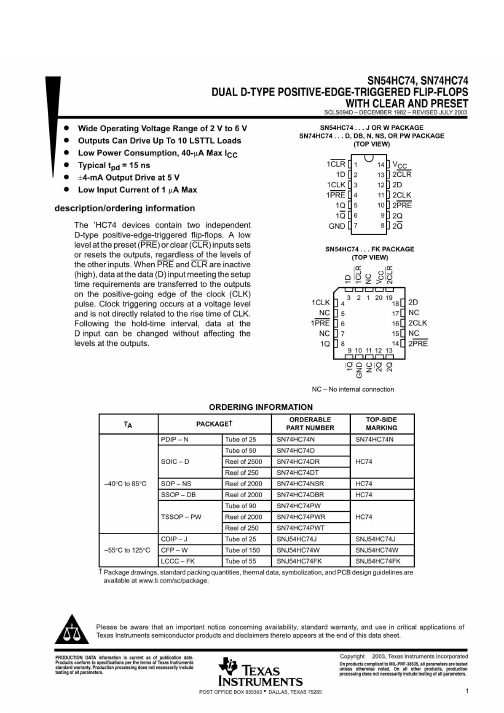

74HC74宽工作电压范围2 V 6 VD输出可以开车10 LSTTL LoadsD低功耗,40-µA马克斯ICCD典型信息= 15 nsD±4-mA输出驱动VD低输入电 流的5点1µA Maxdescription /订购informationThe HC74设备包含两个independentD-type positive-edge-triggered拖鞋。74HC74在预置(PRE)或 清除(CLR)输入设置或重置输出的低电平,而不考虑其他输入的电平。当PRE和CLR处于非活动状态(高)时,满足setuptime要求的数据 (D)输入处的数据被传输到时钟(CLK)脉冲正向边缘的输出端。时钟触发发生在电压水平,与CLK的上升时间没有直接关系。在保持时间 间隔之后,可以在不影响输出电平的情况下更改输入端的数据。订购包图纸,标准包装数量,74HC74热数据,符号,和PCB设计指南超 过“绝对最大额定值”下列出的应力可能对设备造成永久性损坏。这些只是应力等级,设备在这些或任何其他条件下的功能运行,超 出“推荐操作条件”的指示,是不受限制的。长时间暴露在绝对最大额定条件下可能会影响设备的可靠性。如果观察输入和输出电流额 定值,可能会超过输入和输出电压额定值。封装热阻抗按JESD 5计算环保(RoHS &没有某人/ Br): TI定义“绿色”意味着“Pb-Free”,此 外,使用包装材料,不含卤素,包括溴(Br)或锑(某人)总数的0.1%以上产品的重量。(3)实验室,峰值温度。湿度敏感性级别评级根据 JEDECindustry标准分类和soldertemperature峰值。重要信息和免责声明:本页所提供的信息代表德州仪器自提供之日起的知识和信念。TI 的知识和信念基于第三方提供的信息,对于这些信息的准确性不作任何陈述或保证。74HC74目前正在努力更好地整合来自第三方的信 息。TI已采取并将继续采取合理措施,提供具有代表性和准确的信息,但可能未对来料和化学品进行破坏性测试或化学分析。TI和TI供 应商认为某些信息是专有的,因此CAS号码和其他有限的信息可能无法发布。在任何情况下,TI因该等信息而产生的责任都不应超过 TIto客户在本文件中每年销售的TI部件的采购总价

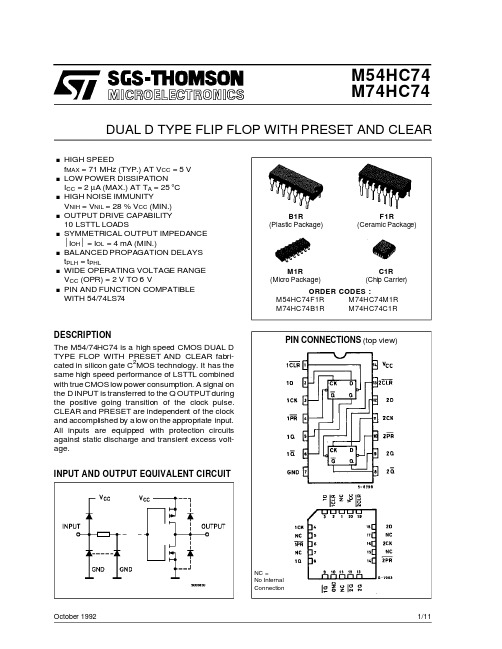

M74HC74B1中文资料

IEC LOGIC SYMBOL

4, 10 5, 9 6, 8 7 14

1PR, 2PR 1Q, 2Q 1Q, 2Q GND V CC

LOGIC DIAGRAM

2/11

元器件交易网

M54/M74HC74

ABSOLUTE MAXIMUM RATINGS

Symbol VCC VI VO IIK IOK IO ICC or IGND PD Tstg TL Supply Voltage DC Input Voltage DC Output Voltage DC Input Diode Current DC Output Diode Current DC Output Source Sink Current Per Output Pin DC VCC or Ground Current Power Dissipation Storage Temperature Lead Temperature (10 sec) Parameter Value -0.5 to +7 -0.5 to VCC + 0.5 -0.5 to VCC + 0.5 ± 20 ± 20 ± 25 ± 50 500 (*) -65 to +150 300 Unit V V V mA mA mA mA mW

VIH

High Level Input Voltage Low Level Input Voltage

V IL

4/11

元器件交易网

M54/M74HC74

AC ELECTRICAL CHARACTERISTICS (C L = 50 pF, Input t r = tf = 6 ns)

o

Value -40 to 85 oC -55 to 125 oC 74HC 54HC Min. Max. Min. Max. 95 19 16 190 38 32 190 38 32 4.2 21 25 110 22 19 110 22 19 110 22 19 0 0 0 35 7 6 10 pF pF ns ns ns ns MHz 110 22 19 225 45 38 225 45 38 ns ns ns Unit

74HCT7404N资料

GENERAL DESCRIPTION

The 74HC/HCT7404 are high-speed Si-gate CMOS devices specified in compliance with JEDEC standard no.7A.

The “7404” is an expandable, First-In First-Out (FIFO) memory organized as 64 words by 5 bits. A guaranteed 15 MHz data-rate makes it ideal for high-speed applications. A higher data-rate can be obtained in applications where the status flags are not used (burst-mode).

Fig.5 Functional diagram.

September 1993

4

Philips Semiconductors

5-Bit x 64-word FIFO register; 3-state

full pagewidth

September 1993

R (1)

R FP

S

Q

DOR

MR

SO

61 x

MGA670

handbook, halfpage

OE 1

DIR 2

SI 3

n.c. 4

D0 5 D1 6 D2 7 D3 8 D4 9 GND 10

20 VCC 19 SO 18 DOR

17 n.c.

7404

16 Q0 15 Q1 14 Q2 13 Q3 12 Q4 11 MR

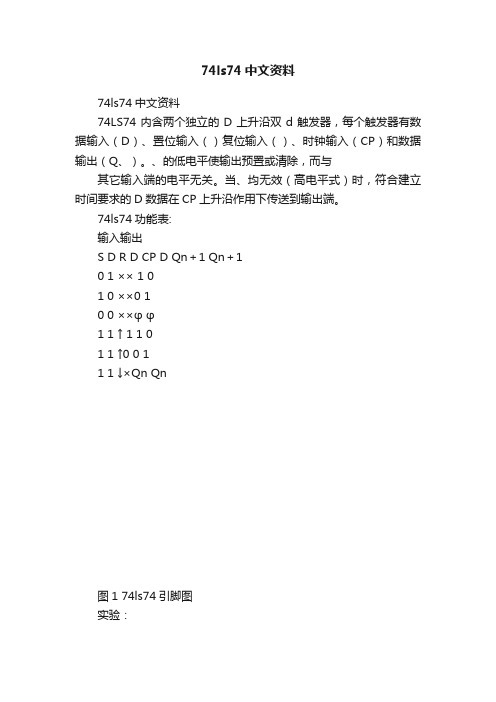

74ls74中文资料

74ls74中文资料74ls74中文资料74LS74内含两个独立的D上升沿双d触发器,每个触发器有数据输入(D)、置位输入()复位输入()、时钟输入(CP)和数据输出(Q、)。

、的低电平使输出预置或清除,而与其它输入端的电平无关。

当、均无效(高电平式)时,符合建立时间要求的D数据在CP上升沿作用下传送到输出端。

74ls74功能表:输入输出S D R D CP D Qn+1 Qn+10 1 ×× 1 01 0 ××0 10 0 ××φ φ1 1 ↑ 1 1 01 1 ↑0 0 11 1 ↓×Qn Qn图1 74ls74引脚图实验:用74LS74构成4位寄存器一个D触发器可实现一位二进数的存储,因此应采用4个D触发器实现4位寄存器。

由于要实现移位寄存,4个D触发器之间应相互联接。

(1)首先在图2中完成相应的联线,构成可实现并入并出、串入串出、并入串出、串入并出的多功能移位寄存。

按图接好电路。

(2) D3 D2 D1 D0分别接逻辑开关,Q3 Q2 Q1 Q0接发光二极管;(3) 先清零;(4) 按下列要求,实现相应功能,观察结果,并描述工作过程。

并入并出:使数据输入端D3D2D1D0=1011,给CP端输入一个正单脉冲,观察Q3Q2Q1Q0发光二极管的状态,、将结果填入表中。

并入串出:使数据输入端D3D2D1D0=1011,给CP端输入4个正单脉冲,观察Q3端发光二极管的状态,将结果填入表6中。

串入并出:使数据输入端D0分别为1011,同时通过给CP端输入正单脉冲将D0端的4 个数据送入寄存器。

观察Q3Q2Q1Q0端发光二极管的状态,将结果填入表中。

串入串出:使数据输入端D0分别为1011,同时通过给CP端输入正单脉冲,将D0端的4 个数据送入寄存器。

在CP端输完8个脉冲后,观察Q3端发光二极管的状态,将结果填入表2中。

并入并出:D3D2D1D0=10111个CP脉冲Q3Q2Q1Q0=结论:并入串出D3D2D1D0=10114个CP脉冲Q3=结论串入并出D3=10114个CP脉冲Q3Q2Q1Q0=结论串入串出D3=10118个CP脉冲Q3=结论图274ls153芯片管脚图引脚逻辑功能以及封装2007年12月17日 23:53 本站原创作者:本站用户评论()关键字:74ls153管脚图逻辑功能图封装:74LS163引脚功能表及管脚定义图(带时序波形图)发布:2011-08-30 | 作者: | 来源: huangjiapeng| 查看:2620次 | 用户关注:定时器由与系统秒脉冲(由时钟脉冲产生器提供)同步的计数器构成,要求计数器在状态信号ST作用下,首先清零,然后在时钟脉冲上升沿作用下,计数器从零开始进行增1计数,向控制器提供模5的定时信号TY和模25的定时信号TL。

74系列中文资料(超级全)

┌┴─┴─┴─┴─┴─┴─┴┐ 双 D 触发器 74LS74

│14 13 12 11 10 9 8 │

)

│

│ 1 2 3 4 5 6 7│

└┬─┬─┬─┬─┬─┬─┬┘

1Cr 1D 1Ck 1St 1Q -1Q GND

Vcc 8Q 8D 7D 7Q 6Q 6D 5D 5Q ALE

┌┴─┴─┴─┴─┴─┴─┴─┴─┴─┴┐ 8 位锁存器 74LS373

Vcc -G B1 B2 B3 B4 B8 B6 B7 B8

┌┴─┴─┴─┴─┴─┴─┴─┴─┴─┴┐ 8 位总线驱动器 74LS245

│20 19 18 17 16 15 14 13 12 11│

)

│ DIR=1 A=>B

│ 1 2 3 4 5 6 7 8 9 10│ DIR=0 B=>A

└┬─┬─┬─┬─┬─┬─┬─┬─┬─┬┘

___

)

│ Y = A+B

│ 1 2 3 4 5 6 7│

└┬─┬─┬─┬─┬─┬─┬┘

1Y 1A 1B 2Y 2A 2B GND

Vcc 2Y 2B 2A 2D 2E 1F

┌┴─┴─┴─┴─┴─┴─┴┐ 双与或非门 74S51

│14 13 12 11 10 9 8│

_____

)

│ 2Y = AB+DE

DIR A1 A2 A3 A4 A5 A6 A7 A8 GND

正逻辑与门,与非门:

Vcc 4B 4A 4Y 3B 3A 3Y

┌┴─┴─┴─┴─┴─┴─┴┐

│14 13 12 11 10 9 8│

Y = AB )

│ 2 输入四正与门 74LS08

│ 1 2 3 4 5 6 7│

74HC74管脚排列中文资料

74HC74管脚排列

74HC74 概述

74HC74是一款高速CMOS器件,74HC74引脚兼容低功耗肖特基TTL (LSTTL)系列。

74HC74遵循JEDEC标准no.7A。

74HC74是双路D 型上升沿触发器,带独立的数据(D)输入、时钟(CP)输入、设置(SD)和复位(RD)输入、以及互补的Q和Q输出。

设置和复位为异步低电平有效,且不依赖于时钟输入。

74HC74数据输入口的信息在时钟脉冲的上升沿传输到Q口。

为了获得预想中的结果,D输入必须在时钟脉冲上升沿来临之前,保持稳定一段就绪时间。

74HC74时钟输入的施密特触发功能使得电路对于缓慢的脉冲上升和下降具备更高的容差性。

74HC74 特性

工作电压范围:2.0~6.0 V

对称输出阻抗

高抗扰

低功耗

ESD保护

HBM EIA/JESD22-A114-A超过2000 V

MM EIA/JESD22-A115-A超过200 V

74HC74 参数

74HC74 基本参数

电压 2.0~6.0V

驱动电流+/-5.2 mA

传输延迟14 ns@5V

74HC74 其他特性

逻辑电平CMOS

功耗考量低功耗或电池供电应用74HC74 封装与引脚

SO14, SSOP14, DIP14, TSSOP14。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

74HC74; 74HCT74

handbook, halfpage handbook, halfpage

1RD 1

VCC 14 13 12 2RD 2D 2CP 2SD 2Q

1RD 1D 1CP 1SD 1Q 1Q GND

1 2 3 4 5 6 7

MNA417

14 VCC 13 2RD 12 2D

1D 1CP 1SD 1Q

Fig.1

Pin configuration DIP14, SO14 and (T)SSOP14.

Fig.2 Pin configuration DHVQFN14.

2003 Jul 10

4

元器件交易网

Philips Semiconductors

Product specification

元器件交易网

INTEGRATED CIRCUITS

DATA SHEET

74HC74; 74HCT74 Dual D-type flip-flop with set and reset; positive-edge trigger

Product specification Supersedes data of 1998 Feb 23 2003 Jul 10

2003 Jul 10

2

元器件交易网

Philips Semiconductors

Product specification

Dual D-type flip-flop with set and reset; positive-edge trigger

FUNCTION TABLES Table 1 See note 1 INPUT SD L H L Table 2 See note 1 INPUT SD H H Note 1. H = HIGH voltage level; L = LOW voltage level; X = don’t care; ↑ = LOW-to-HIGH CP transition; Qn+1 = state after the next LOW-to-HIGH CP transition. ORDERING INFORMATION PACKAGE TYPE NUMBER 74HC74N 74HCT74N 74HC74D 74HCT74D 74HC74DB 74HCT74DB 74HC74PW 74HCT74PW 74HC74BQ 74HCT74BQ TEMPERATURE RANGE −40 to +125 °C −40 to +125 °C −40 to +125 °C −40 to +125 °C −40 to +125 °C −40 to +125 °C −40 to +125 °C −40 to +125 °C −40 to +125 °C −40 to +125 °C PINS 14 14 14 14 14 14 14 14 14 14 PACKAGE DIP14 DIP14 SO14 SO14 SSOP14 SSOP14 TSSOP14 TSSOP14 DHVQFN14 DHVQFN14 RD H H CP ↑ ↑ D L H RD H L L CP X X X D X X X

74HC74; 74HCT74

GENERAL DESCRIPTION The 74HC/HCT74 is a high-speed Si-gate CMOS device and is pin compatible with low power Schottky TTL (LSTTL). They are specified in compliance with JEDEC standard no. 7A. The 74HC/HCT74 are dual positive-edge triggered, D-type flip-flops with individual data (D) inputs, clock (CP) inputs, set (SD) and reset (RD) inputs; also complementary Q and Q outputs. The set and reset are asynchronous active LOW inputs and operate independently of the clock input. Information on the data input is transferred to the Q output on the LOW-to-HIGH transition of the clock pulse. The D inputs must be stable one set-up time prior to the LOW-to-HIGH clock transition for predictable operation. Schmitt-trigger action in the clock input makes the circuit highly tolerant to slower clock rise and fall times.

74HC74; 74HCT74

OUTPUT Q H L H Q L H H

OUTPUT Qn+1 L H Qn+1 H L

MATERIAL plastic plastic plastic plastic plastic plastic plastic plastic plastic plastic

CODE SOT27-1 SOT27-1 SOT108-1 SOT108-1 SOT337-1 SOT337-1 SOT402-1 SOT402-1 SOT762-1 SOT762-1

MNA418

handbook, halfpage

4 3 2

S C1 1D R

5

5 9

1

6

6 8

10 11 12 13

S C1 1D R

MNA419

9

8

Fig.3 Logic symbol.

Fig.4 IEC logic symbol.

handbook, halfpage

4

Hale Waihona Puke 1SD SD D CP FF Q RD 1Q 6 Q

Dual D-type flip-flop with set and reset; positive-edge trigger

74HC74; 74HCT74

handbook, halfpage

4 10 1SD 2SD 2 12 3 11 SD 1Q 1D Q D 2D 2Q 1CP CP 2CP FF 1Q Q 2Q RD 1RD 2RD 1 13

Product specification

Dual D-type flip-flop with set and reset; positive-edge trigger

2 3

1D 1CP

1Q

5

1 10

1RD 2SD SD D CP FF Q RD 2Q 8 Q

12 11

2D 2CP

2Q

9

13

2RD

MNA420

Fig.5 Functional diagram.

2003 Jul 10

5

元器件交易网

Philips Semiconductors

QUICK REFERENCE DATA GND = 0 V; Tamb = 25 °C; tr = tf = 6 ns TYPICAL SYMBOL tPHL/tPLH PARAMETER propagation delay nCP to nQ, nQ nSD to nQ, nQ nRD to nQ, nQ fmax CI CPD Notes 1. CPD is used to determine the dynamic power dissipation (PD in µW). PD = CPD × VCC2 × fi × N + Σ(CL × VCC2 × fo) where: fi = input frequency in MHz; fo = output frequency in MHz; CL = output load capacitance in pF; VCC = supply voltage in Volts; N = total load switching outputs; Σ(CL × VCC2 × fo) = sum of the outputs. 2. For 74HC74 the condition is VI = GND to VCC. For 74HCT74 the condition is VI = GND to VCC − 1.5 V. maximum clock frequency input capacitance power dissipation capacitance per flip-flop notes 1 and 2 CONDITIONS HC CL = 15 pF; VCC = 5 V 14 15 16 76 3.5 24 15 18 18 59 3.5 29 ns ns ns MHz pF pF HCT UNIT

元器件交易网

Philips Semiconductors

Product specification

Dual D-type flip-flop with set and reset; positive-edge trigger

FEATURES • Wide supply voltage range from 2.0 to 6.0 V • Symmetrical output impedance • High noise immunity • Low power dissipation • Balanced propagation delays • ESD protection: HBM EIA/JESD22-A114-A exceeds 2000 V MM EIA/JESD22-A115-A exceeds 200 V.