16路8位A/D转换器ADC0816原理及应用

ADC0809芯片的原理及应用

目录引言 (1)1 ADC0809的逻辑结构 (1)1.1 ADC0809引脚结构 (1)1.2 ADC0809的主要性能指标 (3)1.3 ADC0809的内部逻辑结构 (3)1.4 ADC0809的时序 (4)2 ADC0809与MCS-51单片机的接口电路 (5)2.1 0809与51单片机的第一种连接方式 (7)2.2 0809与51单片机的第二种连接方式 (9)2.3 0809与51单片机的第三种连接方式 (10)3 ADC0809与单片机制作的数字电压表 (11)总结 (16)参考文献 (16)英文翻译 (17)ADC0809芯片的原理及应用摘要:ADC0809是8位逐次逼近型A/D转换器,是目前应用比较广泛、典型的A/D转换芯片之一。

本文主要介绍ADC0809芯片的内部逻辑结构、引脚分布,并详细阐述了其工作原理。

在此基础上设计了两种相关应用电路——ADC0809与单片机的接口电路及数字电压表,并对这两种应用电路的可行性进行了讨论。

通过对ADC0809应用电路的探究,能更全面的提高对应用系统的分析、设计能力,对实践具有重要的指导意义。

关键词:ADC0809;模数转换;单片机引言A/D转换器是模拟信号源与计算机或其它数字系统之间联系的桥梁,它的任务是将连续变化的模拟信号转换为数字信号,以便计算机等数字系统进行处理、存储、控制和显示。

在工业控制和数据采集及许多其它领域中,A/D转换器是不可缺少的重要组成部分,它的应用已经相当普遍。

目前用软件的方法虽然可以实现高精度的A/D转换,但占用CPU时间长,限制了应用。

8位A/D转换器ADC0809作为典型的A/D转换芯片,具有转换速度快、价格低廉及与微型计算机接口简便等一系列优点,目前在8位单片机系统中得到了广泛的应用。

1 ADC0809的逻辑结构ADC0809是带有8位A/D转换器、8路模拟开关以及微处理机兼容的控制逻辑的CMOS组件。

它是逐次逼近式A/D转换器,是目前应用比较广泛的A/D转换芯片之一,主要适用于对精度和采样速率要求不高的场合或一般的工业控制领域,可以和单片机直接相连。

ADC0808功能及简介

11.2.4 典型的集成ADC 芯片为了满足多种需要,目前国内外各半导体器件生产厂家设计并生产出了多种多样的ADC 芯片。

仅美国AD 公司的ADC 产品就有几十个系列、近百种型号之多。

从性能上讲,它们有的精度高、速度快,有的则价格低廉。

从功能上讲,有的不仅具有A/D 转换的基本功能,还包括内部放大器和三态输出锁存器;有的甚至还包括多路开关、采样保持器等,已发展为一个单片的小型数据采集系统。

尽管ADC 芯片的品种、型号很多,其内部功能强弱、转换速度快慢、转换精度高低有很大差别,但从用户最关心的外特性看,无论哪种芯片,都必不可少地要包括以下四种基本信号引脚端:模拟信号输入端(单极性或双极性);数字量输出端(并行或串行);转换启动信号输入端;转换结束信号输出端。

除此之外,各种不同型号的芯片可能还会有一些其他各不相同的控制信号端。

选用ADC 芯片时,除了必须考虑各种技术要求外,通常还需了解芯片以下两方面的特性。

(1)数字输出的方式是否有可控三态输出。

有可控三态输出的ADC 芯片允许输出线与微机系统的数据总线直接相连,并在转换结束后利用读数信号RD 选通三态门,将转换结果送上总线。

没有可控三态输出(包括内部根本没有输出三态门和虽有三态门、但外部不可控两种情况)的ADC 芯片则不允许数据输出线与系统的数据总线直接相连,而必须通过I/O 接口与MPU 交换信息。

(2)启动转换的控制方式是脉冲控制式还是电平控制式。

对脉冲启动转换的ADC 芯片,只要在其启动转换引脚上施加一个宽度符合芯片要求的脉冲信号,就能启动转换并自动完成。

一般能和MPU 配套使用的芯片,MPU 的I/O 写脉冲都能满足ADC 芯片对启动脉冲的要求。

对电平启动转换的ADC 芯片,在转换过程中启动信号必须保持规定的电平不变,否则,如中途撤消规定的电平,就会停止转换而可能得到错误的结果。

为此,必须用D 触发器或可编程并行I/O 接口芯片的某一位来锁存这个电平,或用单稳等电路来对启动信号进行定时变换。

ADC0808ADC0809 MP兼容的8位AD转换8通道多路复用器

外文资料译文ADC0808/ADC0809 MP兼容的8位A/D转换8通道多路复用器一.总体描述ADC0808,ADC0809的数据采集组件是一个8位模拟 - 数字转换器的单片CMOS器件,8通道多路复用器和微处理器兼容控制逻辑。

8位A / D 转换使用连续逼近作为转换技术。

该转换器具有高阻抗斩波稳定比较器,1模拟开关树和连续256R分压器逼近寄存器。

8通道多路复用直接访问的8路单端模拟信号。

该器件无需外部零点和满刻度的需要调整。

轻松连接到微处理器提供多路复用地址锁存和解码输入和锁存TTL三STATEÉ输出。

ADC0808,ADC0809的设计已优化通过结合几个A/ D转换的最可取的方面,转换技术。

ADC0808,ADC0809的提供高速度快,精度高,最低温度的依赖,优秀的长期精度和可重复性,并消耗最小的功率。

这些特点使该设备适合的应用程序,过程和机器控制消费电子和汽车应用。

16-与常见的输出通道多路复用器(采样/保持端口)看到ADC0816数据表。

(更多信息请参见AN-247。

)二.特点简易所有微处理器的接口5VDC或模拟跨度调整后的电压基准无零或全面调整需要8通道多路复用地址与逻辑0V至5V单电源5V输入范围输出符合TTL电平规格之标准密封或成型28引脚DIP封装28引脚型芯片载体封装ADC0808相当于以MM74C949ADC0809的相当于MM74C949-1三.主要技术指标垂直分辨率8位单电源:5 VDC低功耗15毫瓦转换时间100毫秒四.框图图1框图绝对最大额定值(注1及2)如果指定的军事/航空设备是必需的,请联系美国国家半导体的销售办公室/分销商的可用性和规格。

电源电压(VCC)(注3)6.5V在任何引脚-0.3V电压至(VCC+0.3V)除了控制输入电压控制输入-0.3V到+15V(START,OE时钟,ALE地址,补充B,添加C)存储温度范围-65℃至+150℃875毫瓦TA=25℃封装耗散导致温度。

《常用ADC芯片简介》

常用ADC 芯片简介各种类型的单片集成ADC 有很多种,读者可根据自己的要求参阅手册进行选择。

这里主要介绍两种集成ADC 和一个应用实例。

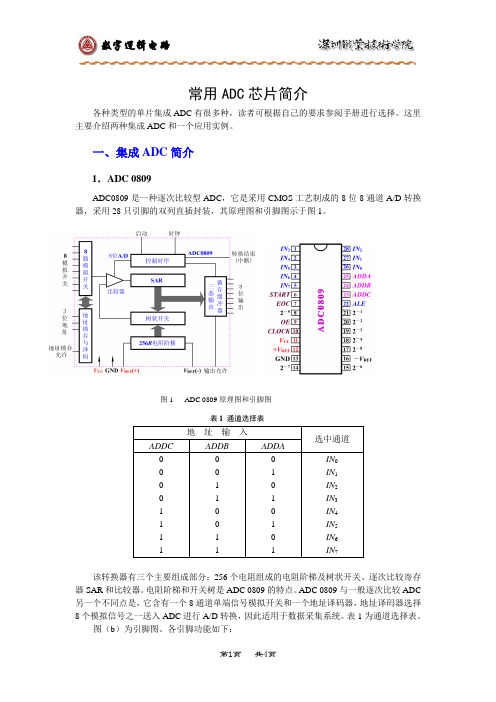

一、集成ADC 简介1.ADC 0809ADC0809是一种逐次比较型ADC ,它是采用CMOS 工艺制成的8位8通道A/D 转换器,采用28只引脚的双列直插封装,其原理图和引脚图示于图1。

表1 通道选择表该转换器有三个主要组成部分:256个电阻组成的电阻阶梯及树状开关、逐次比较寄存器SAR 和比较器。

电阻阶梯和开关树是ADC 0809的特点。

ADC 0809与一般逐次比较ADC 另一个不同点是,它含有一个8通道单端信号模拟开关和一个地址译码器,地址译码器选择8个模拟信号之一送入ADC 进行A/D 转换,因此适用于数据采集系统。

表1为通道选择表。

图(b )为引脚图。

各引脚功能如下:图1 ADC 0809原理图和引脚图(1)IN 0 ~ IN 7是8路模拟输入信号; (1) A DDA 、ADDB 、ADDC 为地址选择端; (2) 2-1~2-8为变换后的数据输出端; (3) S TART (6脚)是启动输入端,输入启动脉冲的下降沿使ADC 开始转换。

脉冲宽度要求大于100ns ;(4) A LE (22脚)是通道地址锁存输入端。

当ALE 上升沿来到时,地址锁存器可对ADDA 、ADDB 、ADDC 锁定,为了稳定锁存地址,即在ADC 转换周期内模拟多路器稳定地接通在某一通道,ALE 脉冲宽度应大于100ns 。

下一个ALE 上升沿允许通道地址更新。

实际使用中,要求ADC 开始转换之前地址就应锁存,所以通常将ALE 和START 连在一起,使用同一个脉冲信号,上升沿锁存地址,下降沿启动转换。

(5) O E (9脚)为输出允许端,它控制ADC 内部三态输出缓冲器。

当OE = 0时,输出端为高阻态,当OE =1时,允许缓冲器中的数据输出。

(6) E OC (7脚)是转换结束信号,由ADC 内部控制逻辑电路产生。

单片机最小系统

1.4单片机最小系统设计单片机加上适当的外围器件和应用程序,构成的应用系统称为最小系统;是组成单片机系统最基本的部分。

最小系统硬件组成:单片机芯片、电源电路、时钟电路、复位电路。

1)单片机芯片AT89S51/52系列单片机是比较流行的51单片机之一,它支持ISP在线编程功能(改写单片机存储器内的程序不需要把芯片从工作环境中脱离)。

AT89S52单片机芯片及IC座如图1-4所示。

实验过程中,单片机芯片最好插在IC座上,注意芯片的方向。

焊接的时候单片机不要插在IC座上,先焊好IC 座,当电路全部完成后再上芯片。

图1-4 单片机芯片及IC座2)电源电路Vcc(40脚), GND(20脚)AT89S* 系列单片机工作电源范围宽达4~5.5V。

单片机的供电有两种方式:①集成稳压电源方式;②USB供电。

①集成稳压电源方式;利用变压器、整流、滤波、稳压自制电源,如图1-5所示。

图1-5 稳压电源电路图1-8 电源适配器稳压电路焊接效果图2)时钟电路产生一个工作时序,其工作需要时钟电路提供一个工作频率。

时钟电路原理图如图1-10所示。

1)振荡频率范围:1.2MHz~12MHz。

2)电容C1和C2选择:10~30pF图1-10时钟电路原理图注意:晶体和电容应尽可能安装在单片机芯片附近,以减少寄生电容,保证振荡器稳定和可靠工作。

电容是为了更好地提高晶振电路的时钟精度。

3)复位电路复位使单片机进入某种确定的初始状态。

退出处于节电工作方式的停顿状态、退出一切程序进程、退出程序的死循环,从头开始。

上电+按钮复位电路如图1-11所示。

注意:电解电容器的极性,长脚为正。

图1-11 复位电路根据上面原理设计的单片机最小系统如图1-12所示。

图1-12单片机最小系统注意:①如果不扩展外部ROM,使用单片机内部的ROM,31脚/EA需接电源(+5V)。

3.1单片机最小系统设计3.1.1 AT89S52简介本设计采用ATMEL公司的8位单片机AT89S52,AT89S52片内含8k字节的可反复擦写的只读Flash程序存储器和256字节的随机存取数据存储器(RAM)。

AD0809

ADC0808 ADC0809版权归三毛电子 不得盗版传播 /8位uP 兼容A/D 转换器,8通道复用ADC0808/ADC0809一般描述:ADC0808,ADC0809数据获取器件集成了一个8位的模/数转换器,8通道复用器以及微处理器兼容控制逻辑。

这个8位的A/D 转换器采用了连续逼近的转换技术。

这个转换器具有一个高阻抗稳定的断续比较器,以及一个带有模拟开关树的256欧的分压器,一个连续逼近电阻。

8通道的复用器能直接获取8个单一模拟信号的任何一个。

这个器件不需要外部的0和全量程调节。

依靠锁存和解码复用器地址输入以及锁存TTL 三态输出,这个器件提供与微处理器很方便的接口。

ADC0808和ADC0809采用了几种A/D 转换技术的各自最大优点来优化的。

ADC0808和ADC0809提供了高速,高精度,低温漂,优秀的长期精度和可重复性,低功耗特性。

这些特性使得这个器件对于消费者处理和控制机器以及汽车电子应用上十分理想的选择。

对于具有相同输出(采样/保持端口)的16通道复用器的器件,请参考ADC0816的数据手册。

特性:×跟所有微处理器接口很容易×比例制的操作或带有5V DC 或者可调节参考电压范围的模拟范围×不需要调节0和全量程×用地址逻辑来区分的8通道复用×单电源5V 供电,0V ~5V 输入范围×输出符合TTL 电压声明×标准密封或浇注的28脚DIP 封装×ADC0808跟MM74C949可替换×ADC0809跟MM74C949-1可替换关键说明:×精度 8位×完全不可调节误差 ±1/2LSB 和±1LSB ×单电源供电 5V DC×低功耗 15mW×转换时间 100us方框图:ADC0808 ADC0809版权归三毛电子 不得盗版传播 /管脚分布:定购信息:ADC0808 ADC0809版权归三毛电子 不得盗版传播 /最大绝对值范围(注释1,2):假如军用或航空应用,需要特别的说明,请自己联系国家半导体公司销售部。

AD转换器的基本概念及基本结构DA转换器的工作原理及其

➢D/A、A/D转换器的基本概念及基本结构 ➢D/A转换器的工作原理及其特点 ➢A/D转换器的工作原理

实用文档

1

第10章

模拟量输入/输出接口技术

10.1 典型D/A转换器芯片

控制系统中传感器所检测的信号如温度、压力、流 量、速度、湿度等物理量都是随着时间连续变化的模拟 量,为了能用计算机对模拟量进行采集、加工和输出, 就需要把模拟量转换成便于计算机存储和加工的数字量 (称为A/D转换);同样经过计算机处理后的数字量必须 转换成模拟量(称为D/A转换)才能控制外部设备。

实用文档

6

第10章

模拟量输入/输出接口技术

10.1.2 DAC0832及其应用 DAC0832是8位分辨率的D/A转换集成芯片,其明显特

点是与微机连接简单、转换控制方便、价格低廉,在微 机系统中得到了广泛的应用。D/A转换器的输出一般都要 接运算放大器,微小信号经放大后才能驱动执行机构的 部件。

AC0832的主要技术指标有:分辨率为8位;转换速度 约为1μs;非线性误差为 0.20%FSR;温度系数为2×106/℃;工作方式为双缓冲、单缓冲和直通方式;逻辑输 入与TTL电平兼容;功耗为20mW;单电源供电。

模拟量输入/输出接口技术

(2)梯形电阻 D/A转换器:如图 10-2所示,该电阻 网络中仅有R和2R 两种电阻,切换开 关的工作原理与二 进制加权电阻网络 D/A转换工作原理 相同。

2R

d n 1

2R

K1

Rf

R

d n2

2R

K2

d1

+

2R

R 2R

VREF

K -2 梯形电阻D/A转换器的结构

实用文档

总结-8位串行ADC

8位串行ADC概述

8位串行ADC是一种模数转换器,其 将模拟信号转换为8位(即256个等级) 的数字信号。

8位串行ADC的转换速率通常较低, 但足以满足大多数低速应用的需求。

8位串行ADC通常具有低功耗、小尺寸和低 成本等优点,因此在许多应用中得到广泛应 用,如传感器接口、音频处理和电池供电设 备等。

总结-8位串行ADC

目录

CONTENTS

• 引言 • 8位串行ADC工作原理 • 8位串行ADC性能指标 • 8位串行ADC的应用场景 • 8位串行ADC的选型指南 • 8位串行ADC的未来发展趋势 • 结论

01 引言

ADC简介

ADC,即模数转换器,是一种将模拟 信号转换为数字信号的电子元件。它 广泛应用于各种领域,如通信、音频 处理、图像处理等。

功耗

总结:功耗是指ADC在工作时所消耗的电能,通常以毫瓦 (mW)或瓦(W)表示。

功耗是评估ADC能效的重要指标,低功耗的ADC有助于降低 系统整体能耗和散热需求。8位串行ADC的功耗取决于其工作 模式和工艺实现,一般在几十毫瓦至几百毫瓦之间。

04 8位串行ADC的应用场景

数据采集系统

实时数据采集

VS

转换时间

考虑ADC的转换时间,确保在所需采样 速率下,ADC能够及时完成转换。

功耗和尺寸限制

功耗

根据系统功耗预算和便携性要求,选择低功 耗或优化功耗的ADC。

尺寸

考虑PCB板空间和集成度要求,选择合适尺 寸的ADC以适应系统布局和布线需求。

06 8位串行ADC的未来发展 趋势

提高分辨率和精度

对未来研究和应用的建议

adc0809工作原理

adc0809工作原理A/D转换器是模拟信号源与计算机或其它数字系统之间联系的桥梁,其任务是将连续变化的模拟信号转换为数字信号,以便计算机等数字系统进行处理、存储、控制和显示;在工业控制和数据采集及许多其它领域中,它是不可缺少的重要组成部分。

目前用软件的方法虽然可以实现高精度的A/D转换,但占用CPU时间长,限制了应用。

而作为典型的A/D转换芯片ADC0809,具有转换速度快、价格低廉及与微型计算机接口简便等一系列优点,目前在8位单片机系统中得到了广泛的应用。

下面将介绍其的原理:1.主要特性(1)具有转换起停控制端;(2)转换时间为100μs;(3)单个+5V电源供电;(4)低功耗,约15mW;(5)8路8位A/D转换器,即分辨率8位;(6)工作温度范围为-40~+85摄氏度;(7)模拟输入电压范围0~+5V,不需零点和满刻度校准。

2.内部逻辑结构ADC0809的内部逻辑结构如图1所示,它主要由三部分组成。

第一部分:模拟输入选择部分,包括一个8路模拟开关、一个地址锁存译码电路。

输入的3位通道地址信号由锁存器锁存,经译码电路后控制模拟开关选择相应的模拟输入。

第二部分:转换器部分,主要包括比较器,8位A/D转换器,逐次逼近寄存器SAR,电阻网络以及控制逻辑电路等。

第三部分:输出部分,包括一个8位三态输出缓冲器,可直接与CPU数据总线接口。

图1 ADC0809内部逻辑结构图由于芯片性能特点是一个逐次逼近型的A/D 转换器,外部供给基准电压;分辨率为8位,带有三态输出锁存器,转换结束时,可由CPU打开三态门,读出8位的转换结果;有8个模拟量的输入端,可引入8路待转换的模拟量。

ADC0809的数据输出结构是内部有可控的三态缓冲器,所以它的数字量输出信号线可以与系统的数据总线直接相连。

内部的三态缓冲器由OE控制,当OE为高电平时,三态缓冲器打开,将转换结果送出;当OE为低电平时,三态缓冲器处于阻断状态,内部数据对外部的数据总线没有影响。

ADC0816中文资料

ADC0816/ADC08178-Bit µP Compatible A/D Converters with 16-Channel MultiplexerGeneral DescriptionThe ADC0816,ADC0817data acquisition component is a monolithic CMOS device with an 8-bit analog-to-digital con-verter,16-channel multiplexer and microprocessor compat-ible control logic.The 8-bit A/D converter uses successive approximation as the conversion technique.The converter features a high impedance chopper stabilized comparator,a 256R voltage divider with analog switch tree and a succes-sive approximation register.The 16-channel multiplexer can directly access any one of 16-single-ended analog signals,and provides the logic for additional channel expansion.Sig-nal conditioning of any analog input signal is eased by direct access to the multiplexer output,and to the input of the 8-bit A/D converter.The device eliminates the need for external zero and full-scale adjustments.Easy interfacing to microprocessors is provided by the latched and decoded multiplexer address inputs and latched TTL TRI-STATE ®outputs.The design of the ADC0816,ADC0817has been optimized by incorporating the most desirable aspects of several A/D conversion techniques.The ADC0816,ADC0817offers high speed,high accuracy,minimal temperature dependence,ex-cellent long-term accuracy and repeatability,and consumes minimal power.These features make this device ideally suited to applications from process and machine control to consumer and automotive applications.For similar perfor-mance in an 8-channel,28-pin,8-bit A/D converter,see the ADC0808,ADC0809data sheet.(See AN-258for more in-formation.)Featuresn Easy interface to all microprocessorsn Operates ratiometrically or with 5V DC or analog span adjusted voltage referencen 16-channel multiplexer with latched control logic n Outputs meet TTL voltage level specificationsn 0V to 5V analog input voltage range with single 5V supplyn No zero or full-scale adjust requiredn Standard hermetic or molded 40-pin DIP packagen Temperature range −40˚C to +85˚C or −55˚C to +125˚C n Latched TRI-STATE outputn Direct access to “comparator in”and “multiplexer out”for signal conditioningn ADC0816equivalent to MM74C948n ADC0817equivalent to MM74C948-1Key Specificationsn Resolution8Bitsn Total Unadjusted Error ±1⁄2LSB and ±1LSBn Single Supply 5V DC n Low Power15mW nConversion Time100µsBlock DiagramTRI-STATE ®is a registered trademark of National Semiconductor Corporation.DS005277-1June 1999ADC0816/ADC08178-Bit µP Compatible A/D Converters with 16-Channel Multiplexer©1999National Semiconductor Corporation Connection DiagramOrdering InformationTEMPERATURE RANGE−40˚C to +85˚CError±1⁄2Bit Unadjusted ADC0816CCN ADC0816CCJ±1Bit UnadjustedADC0817CCN Package OutlineN40A Molded DIPJ40A Hermetic DIP Dual-In-Line PackageDS005277-6Order Number ADC0816CCN or ADC0817CCNSee NS Package Number N40A 2Absolute Maximum Ratings(Notes1,2) If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.Supply Voltage(V CC)(Note3) 6.5V Voltage at Any Pin−0.3V to(V CC+0.3V) Except Control InputsVoltage at Control Inputs−0.3V to15V (START,OE,CLOCK,ALE,EXPANSION CONTROL,ADD A,ADD B,ADD C,ADD D)Storage Temperature Range−65˚C to+150˚C Package Dissipation at T A=25˚C875mW Lead Temp.(Soldering,10seconds)Dual-In-Line Package(Plastic)260˚C Molded Chip Carrier PackageVapor Phase(60seconds)215˚C Infrared(15seconds)220˚C ESD Susceptibility(Note9)400VOperating Conditions(Notes1,2) Temperature Range(Note1)T MIN≤T A≤T MAX ADC0816CCN,ADC0817CCN−40˚C≤T A≤+85˚C Range of V CC(Note1) 4.5V DC to6.0V DC Voltage at Any Pin0V to V CC Except Control InputsVoltage at Control Inputs0V to15V (START,OE,CLOCK,ALE,EXPANSION CONTROL, ADD A,ADD B,ADD C,ADD D)Electrical CharacteristicsConverter Specifications:V CC=5V DC=V REF(+),V REF(−)=GND,V IN=V COMPARATOR IN,T MIN≤T MAX and f CLK=640kHz unless otherwise stated.Symbol Parameter Conditions Min Typ Max Units ADC0816Total Unadjusted Error25˚C±1⁄2LSB(Note5)T MIN to T MAX±3⁄4LSBADC0817Total Unadjusted Error0˚C to70˚C±1LSB(Note5)T MIN to T MAX±11⁄4LSBInput Resistance From Ref(+)to Ref(−) 1.0 4.5kΩAnalog Input Voltage Range(Note4)V(+)or V(−)GND−0.10V CC+0.10V DCV REF(+)Voltage,Top of Ladder Measured at Ref(+)V CC V CC+0.1V Voltage,Center of Ladder V CC/2−0.1V CC/2V CC/2+0.1VV REF(−)Voltage,Bottom of Ladder Measured at Ref(−)−0.10V Comparator Input Current f c=640kHz,(Note6)−2±0.52µAElectrical CharacteristicsDigital Levels and DC Specifications:ADC0816CCN,ADC0817CCN—4.75V≤V CC≤5.25V,−40˚C≤T A≤+85˚C unless other-wise noted.Symbol Parameter Conditions Min Typ Max Units ANALOG MULTIPLEXERR ON Analog Multiplexer ON(Any Selected Channel)Resistance T A=25˚C,R L=10k 1.53kΩT A=85˚C6kΩT A=125˚C9kΩ∆R ON∆ON Resistance Between Any(Any Selected Channel)75Ω2Channels R L=10kI OFF+OFF Channel Leakage Current V CC=5V,V IN=5V,T A=25˚C10200nAT MIN to T MAX 1.0µAI OFF(−)OFF Channel Leakage Current V CC=5V,V IN=0,T A=25˚C−200nAT MIN to T Max−1.0µA3Electrical Characteristics(Continued)Digital Levels and DC Specifications:ADC0816CCN,ADC0817CCN—4.75V≤V CC≤5.25V,−40˚C≤T A≤+85˚C unless other-wise noted.Symbol Parameter Conditions Min Typ Max Units CONTROL INPUTSV IN(1)Logical“1”Input Voltage V CC−1.5VV IN(0)Logical“0”Input Voltage 1.5VI IN(1)Logical“1”Input Current V IN=15V 1.0µA(The Control Inputs)I IN(0)Logical“0”Input Current V IN=0−1.0µA(The Control Inputs)I CC Supply Current f CLK=640kHz0.3 3.0mADATA OUTPUTS AND EOC(INTERRUPT)V OUT(1)Logical“1”Output Voltage I O=−360µA,T A=85˚C V CC−0.4VI O=−300µA,T A=125˚CV OUT(0)Logical“0”Output Voltage I O=1.6mA0.45VV OUT(0)Logical“0”Output Voltage EOC I O=1.2mA0.45VI OUT TRI-STATE Output Current V O=V CC 3.0µAV O=0−3.0µA Electrical CharacteristicsTiming Specifications:V CC=V REF(+)=5V,V REF(−)=GND,t r=t f=20ns and T A=25˚C unless otherwise noted.Symbol Parameter Conditions Min Typ Max Units t WS Minimum Start Pulse Width(Figure5)(Note7)100200nst WALE Minimum ALE Pulse Width(Figure5)100200nst s Minimum Address Set-Up Time(Figure5)2550nsT H Minimum Address Hold Time(Figure5)2550nst D Analog MUX Delay Time R S=OΩ(Figure5)1 2.5µs from ALEt H1,t H0OE Control to Q Logic State C L=50pF,R L=10k(Figure8)125250nst1H,t0H OE Control to Hi-Z C L=10pF,R L=10k(Figure8)125250nst C Conversion Time f c=640kHz,(Figure5)(Note8)90100116µsf c Clock Frequency106401280kHz t EOC EOC Delay Time(Figure5)08+2µs ClockPeriods C IN Input Capacitance At Control Inputs1015pFC OUT TRI-STATE Output At TRI-STATE Outputs(Note8)1015pFCapacitanceNote1:Absolute Maximum Ratings indicate limits beyond which damage to the device may occur.DC and AC electrical specifications do not apply when operating the device beyond its specified operating conditions.Note2:All voltages are measured with respect to GND,unless otherwise specified.Note3:A zener diode exists,internally,from V CC to GND and has a typical breakdown voltage of7V DC.Note4:Two on-chip diodes are tied to each analog input which will forward conduct for analog input voltages one diode drop below ground or one diode drop greater than the V CC supply.The spec allows100mV forward bias of either diode.This means that as long as the analog V IN does not exceed the supply voltage by more than100mV,the output code will be correct.To achieve an absolute0V DC to5V DC input voltage range will therefore require a minimum supply voltage of4.900 V DC over temperature variations,initial tolerance and loading.Note5:Total unadjusted error includes offset,full-scale,and linearity errors.See Figure3.None of these A/Ds requires a zero or full-scale adjust.However,if an all zero code is desired for an analog input other than0.0V,or if a narrow full-scale span exists(for example:0.5V to4.5V full-scale)the reference voltages can be adjusted to achieve this.See Figure13.Note6:Comparator input current is a bias current into or out of the chopper stabilized comparator.The bias current varies directly with clock frequency and has little temperature dependence(Figure6).See paragraph4.0.Note7:If start pulse is asynchronous with converter clock or if f c>640kHz,the minimum start pulse width is8clock periods plus2µs.For synchronous operation at f c≤640kHz take start high within100ns of clock going low.Note8:The outputs of the data register are updated one clock cycle before the rising edge of EOC.Note9:Human body model,100pF discharged through a1.5kΩresistor.4Functional DescriptionMultiplexer:The device contains a16-channel single-ended analog signal multiplexer.A particular input channel is se-lected by using the address decoder.Table1shows the input states for the address line and the expansion control line to select any channel.The address is latched into the decoder on the low-to-high transition of the address latch enable sig-nal.TABLE1.Selected Address Line Expansion Analog Channel D C B A Control IN0L L L L HIN1L L L H HIN2L L H L HIN3L L H H HIN4L H L L HIN5L H L H HIN6L H H L HIN7L H H H HIN8H L L L HIN9H L L H HIN10H L H L HIN11H L H H HIN12H H L L HIN13H H L H HIN14H H H L HIN15H H H H HAll Channels OFF X X X X LX=don’t care Additional single-ended analog signals can be multiplexed to the A/D converter by disabling all the multiplexer inputs using the expansion control.The additional external signals are connected to the comparator input and the device ground. Additional signal conditioning(i.e.,prescaling,sample and hold,instrumentation amplification,etc.)may also be added between the analog input signal and the comparator input.CONVERTER CHARACTERISTICSThe ConverterThe heart of this single chip data acquisition system is its 8-bit analog-to-digital converter.The converter is designed to give fast,accurate,and repeatable conversions over a wide range of temperatures.The converter is partitioned into3 major sections:the256R ladder network,the successive ap-proximation register,and the comparator.The converter’s digital outputs are positive true.The256R ladder network approach Figure1was chosen over the conventional R/2R ladder because of its inherent monotonicity,which guarantees no missing digital codes. Monotonicity is particularly important in closed loop feedback control systems.A non-monotonic relationship can cause os-cillations that will be catastrophic for the system.Additionally, the256R network does not cause load variations on the ref-erence voltage.The bottom resistor and the top resistor of the ladder net-work in Figure1are not the same value as the remainder of the network.The difference in these resistors causes the output characteristic to be symmetrical with the zero and full-scale points of the transfer curve.The first output transi-tion occurs when the analog signal has reached+1⁄2LSB and succeeding output transitions occur every1LSB later up to full-scale.DS005277-2FIGURE1.Resistor Ladder and Switch Tree5Functional Description(Continued)Timing DiagramDS005277-3FIGURE2.3-Bit A/D Transfer CurveDS005277-4FIGURE3.3-Bit A/D Absolute Accuracy CurveDS005277-5FIGURE4.Typical Error CurveDS005277-7FIGURE5.6Timing Diagram(Continued)The successive approximation register(SAR)performs8it-erations to approximate the input voltage.For any SAR typeconverter,n-iterations are required for an n-bit converter.Figure2shows a typical example of a3-bit converter.In theADC0816,ADC0817,the approximation technique is ex-tended to8bits using the256R network.The A/D converter’s successive approximation register(SAR)is reset on the positive edge of the start conversion(SC)pulse.The conversion is begun on the falling edge ofthe start conversion pulse.A conversion in process will be in-terrupted by receipt of a new start conversion pulse.Con-tinuous conversion may be accomplished by tying theend-of-conversion(EOC)output to the SC input.If used inthis mode,an external start conversion pulse should be ap-plied after power up.End-of-conversion will go low between0and8clock pulses after the rising edge of start conversion.The most important section of the A/D converter is the com-parator.It is this section which is responsible for the ulimateaccuracy of the entire converter.It is also the comparatordrift which has the greatest influence on the repeatability ofthe device.A chopper-stabilized comparator provides themost effective method of satisfying all the converter require-ments.The chopper-stabilized comparator converts the DC inputsignal into an AC signal.This signal is then fed through ahigh gain AC amplifier and has the DC level restored.Thistechnique limits the drift component of the amplifier since thedrift is a DC component which is not passed by the AC am-plifier.This makes the entire A/D converter extremely insen-sitive to temperature,long term drift and input offset errors.Figure4shows a typical error curve for the ADC0816asmeasured using the procedures outlined in AN-179.7Typical Performance CharacteristicsTRI-STATE Test Circuits and Timing DiagramsApplications InformationOPERATION1.0RATIOMETRIC CONVERSIONThe ADC0816,ADC0817is designed as a complete Data Acquisition System (DAS)for ratiometric conversion sys-tems.In ratiometric systems,the physical variable being measured is expressed as a percentage of full-scale which is not necessarily related to an absolute standard.The voltage input to the ADC0816is expressed by the equation(1)V IN =Input voltage into the ADC0816V fs =Full-scale voltage V Z =Zero voltageD X =Data point being measured D MAX =Maximum data limit D MIN =Minimum data limitDS005277-18FIGURE parator I IN vs V IN(V CC =V REF =5V)DS005277-19FIGURE 7.Multiplexer R ON vs V IN(V CC =V REF =5V)DS005277-9DS005277-10FIGURE 8. 8Applications Information(Continued)A good example of a ratiometric transducer is a potentiom-eter used as a position sensor.The position of the wiper is di-rectly proportional to the output voltage which is a ratio of the full-scale voltage across it.Since the data is represented as a proportion of full-scale,reference requirements are greatly reduced,eliminating a large source of error and cost for many applications.A major advantage of the ADC0816, ADC0817is that the input voltage range is equal to the sup-ply range so the transducers can be connected directly across the supply and their outputs connected directly into the multiplexer inputs,(Figure9).Ratiometric transducers such as potentiometers,strain gauges,thermistor bridges,pressure transducers,etc.,are suitable for measuring proportional relationships;however, many types of measurements must be referred to an abso-lute standard such as voltage or current.This means a sys-tem reference must be used which relates the full-scale volt-age to the standard volt.For example,if V CC=V REF= 5.12V,then the full-scale range is divided into256standard steps.The smallest standard step is1LSB which is then20 mV.2.0RESISTOR LADDER LIMITATIONSThe voltages from the resistor ladder are compared to the selected input8times in a conversion.These voltages are coupled to the comparator via an analog switch tree which is referenced to the supply.The voltages at the top,center and bottom of the ladder must be controlled to maintain proper operation.The top of the ladder,Ref(+),should not be more positive than the supply,and the bottom of the ladder,Ref(−),should not be more negative than ground.The center of the ladder voltage must also be near the center of the supply because the analog switch tree changes from N-channel switches to P-channel switches.These limitations are automaticaly sat-isfied in ratiometric systems and can be easily met in ground referenced systems.Figure10shows a ground referenced system with a sepa-rate supply and reference.In this system,the supply must be trimmed to match the reference voltage.For instance,if a 5.12V reference is used,the supply should be adjusted to the same voltage within0.1V.The ADC0816needs less than a milliamp of supply current so developing the supply from the reference is readily ac-complished.In Figure11a ground references system is shown which generates the supply from the reference.The buffer shown can be an op amp of sufficient drive to supply the millliamp of supply current and the desired bus drive,or if a capacitive bus is driven by the outputs a large capacitor will supply the transient supply current as seen in Figure12. The LM301is overcompensated to insure stability when loaded by the10µF output capacitor.The top and bottom ladder voltages cannot exceed V CC and ground,respectively,but they can be symmetrically less than V CC and greater than ground.The center of the ladder volt-age should always be near the center of the supply.The sen-sitivity of the converter can be increased,(i.e.,size of the LSB steps decreased)by using a symmetrical reference sys-tem.In Figure13,a2.5V reference is symmetrically cen-tered about V CC/2since the same current flows in identical resistors.This system with a2.5V reference allows the LSB to be half the size of the LSB in a5V reference system.DS005277-11FIGURE9.Ratiometric Conversion System9Applications Information(Continued)DS005277-12FIGURE10.Ground ReferencedConversion System Using Trimmed SupplyDS005277-13FIGURE11.Ground Referenced Conversion System withReference Generating V CC SupplyDS005277-14FIGURE12.Typical Reference and Supply Circuit10Applications Information(Continued)3.0CONVERTER EQUATIONSThe transition between adjacent codes N and N +1is given by:(2)The center of an output code N is given by:(3)The output code N for an arbitrary input are the integers within the range:(4)where:V IN =Voltage at comparator input V REF =Voltage at Ref(+)V REF =Voltage at Ref(−)V TUE =Total unadjusted error voltage (typicallyV REF (+)÷512)4.0ANALOG COMPARATOR INPUTSThe dynamic comparator input current is caused by the pe-riodic switching of on-chip stray capacitances These are connected alternately to the output of the resistor ladder/switch tree network and to the comparator input as part of the operation of the chopper stabilized comparator.The average value of the comparator input current varies di-rectly with clock frequency and with V IN as shown in Figure 6.If no filter capacitors are used at the analog or comparator in-puts and the signal source impedances are low,the com-parator input current should not introduce converter errors,as the transient created by the capacitance discharge will die out before the comparator output is strobed.If input filter capacitors are desired for noise reduction and signal conditioning they will tend to average out the dynamic comparator input current.It will then take on the characteris-tics of a DC bias current whose effect can be predicted con-ventionally.See AN-258for further discussion.DS005277-15FIGURE 13.Symmetrically Centered Reference11Typical ApplicationMicroprocessor Interface TablePROCESSOR READ WRITE INTERRUPT (COMMENT)8080MEMRMEMWINTR (Thru RST Circuit)8085RD WR INTR (Thru RST Circuit)Z-80RD WR INT (Thru RST Circuit,Mode 0)SC/MP NRDS NWDS SA (Thru Sense A)6800VMA •φ2•R/WVMA •Q 2•R/WIRQA or IRQB (Thru PIA)DS005277-16*Address latches needed for 8085and SC/MP interfacing the ADC0816,17to a microprocessor 12Physical Dimensionsinches (millimeters)unless otherwise notedLIFE SUPPORT POLICYNATIONAL’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION.As used herein:1.Life support devices or systems are devices or systems which,(a)are intended for surgical implant into the body,or (b)support or sustain life,and whose failure to perform when properly used in accordance with instructions for use provided in the labeling,can be reasonably expected to result in a significant injury to the user.2.A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system,or to affect its safety or effectiveness.National Semiconductor Corporation AmericasTel:1-800-272-9959Fax:1-800-737-7018Email:support@National Semiconductor EuropeFax:+49(0)180-5308586Email:europe.support@Deutsch Tel:+49(0)180-5308585English Tel:+49(0)180-5327832Français Tel:+49(0)180-5329358Italiano Tel:+49(0)180-5341680National Semiconductor Asia Pacific Customer Response Group Tel:65-2544466Fax:65-2504466Email:sea.support@National Semiconductor Japan Ltd.Tel:81-3-5639-7560Fax:81-3-5639-7507Molded Dual-In-Line Package (N)NS Package Number N40AADC0816/ADC08178-Bit µP Compatible A/D Converters with 16-Channel MultiplexerNational does not assume any responsibility for use of any circuitry described,no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.。