谈谈四层板和33欧电阻

请问大家地址线串22欧姆是为了什么

3.假如你是作硬件,每个厂家基本上都有针对该芯片的DEMO板原理图。先将原理图消化。这样你以后做设计时,对资源的分配心中有数。器件的DATSHEET一定要好好消化。

4.仔细研究你所用的芯片的资料,尽管ARM在内核上兼容,但每家芯片都有自己的特色,编写程序时必须考虑这些问题。尤其是女孩子,在这儿千万别有依靠心理,总想拿别人的示例程序修改,却越改越乱。

5.多看一些操作系统程序,在ARM的应用开放源代码的程序很多,要想提高自己,就要多看别人的程序,linux,uc/os-II等等这些都是很好的原码。

6.假如做软件最好对操作系统的机理要有所了解。当然这对软件工程师来说是小菜一碟。但假如是硬件出身的就有点费劲。

问:做最小系统板是2层还是4层好?

答:只有AT91可以用两层板,其他的最少4层;44b0的地和电源处理好也可用两层板;

3.列读写,当行有效后,选择需要的列进行读或写操作,CAS有效,RAS无效,地址线上为列地址,WE信号决定了究竟是读还是写操作。

SDRAM中的一些重要知识:

1.tRCD,RAS到CAS的延迟,也就是说当行有效后不能在下一个时钟周期就进行读写操作,而是要等待一定的时间,这个时间就是tRCD,一般为2个或3个时钟周期。

SDRAM工作过程:

1.上电稳定后经过8个刷新周期,进入模式寄存器设置(MRS),确定芯片的工作模式,CL,BL,突发传输方式。

阻抗与叠层说明

用SI9000计算阻抗一.几个概念:阻抗的定义:在某一频率下,电子器件传输信号线中,相对某一参考层,其高频信号或电磁波在传播过程中所受的阻力称之为特性阻抗,它是电阻抗,电感抗,电容抗等的一个矢量总和。

阻抗匹配:是为了保证能量传输损耗最小,匹配就是上一级电路的内电阻要等于下一级电路的输入电阻。

当电路实现阻抗匹配时,将获得最大的功率传输,反之,当电路阻抗失配时,不但得不到最大功率传输,还可能对电路产生损害。

目前常见阻抗分类:单端(线)阻抗、差分(动)阻抗、共面阻抗三种情况。

目前我司要考虑阻抗匹配的线有:USB差分线90欧,网口线差分100欧,RF输入信号单端75欧;二.实例:1).首先了解一下几个参数的含义:1.H1:外层到VCC/GND间的介质厚度;2.W1: 阻抗线线底宽度;3.Er1: 介质层介电常数;4.CEr: 阻抗介电常数;5.C2:线面阻焊厚度;6.W2:阻抗线线面宽度;7.S1:差动阻抗线间隙;8.T1:线路铜厚,包括基板铜厚+电镀铜厚;9.C1: 基材阻焊厚度;10.C3:差动阻抗线间阻焊厚度;2).二层板,板厚1.6的两个模型(共面阻抗):a. USB差分线90欧可参考如下:计算结果:线宽W1:10mil、走线间距S1:5mil;b.差分线100欧姆阻抗参考:c. RF输入信号单端75欧、50欧可参考如下(隔层参考):d.说明:以下是凯歌给出的参考值:参数H1=57.677 ER1=4.5 T1=1.7 W1-W2= 1 C1(绿油)=0.4 C2=0.5 C3=0.4 CEr=3.5根据layout实际情况,可根据以上模型选用适合自己的W1,D1,S1的宽度。

瑞华给出的参数参数H1=57.677 ER1=4.3 T1=1.42 W1-W2=0.5 C(绿油)=0.591博敏给出的参数参数H1=57.677 ER1=4.5 T1=1.7 W1-W2=1 C1(绿油)=0.6 C2=0.5 C3=0.5 Cer=3.5各个厂家给出的参数有些差别,但算出来的结果偏差不大,大家可以按凯歌给出的参数计算即可,再者,这个计算出来的值也是理论值,发板时一定要注明这些线要求做阻抗,并标出阻抗值,可以参考以下标注:厂家会根据实际做些细微的调整,以满足阻抗的要求,厂家也只能保证阻抗值±10%;三、叠层名词定义:SI个,信号层;GND,地层;PWR,电源层电路板的叠层安排是对PCB整个系统设计的基础,叠层设计如有缺陷,将影响到整机的EMC性能。

关于输出变压器的绕制

关于输出变压器的绕制(单端)一、输出牛电感量的计算:——一般设计变压器时都取其胆内阻的3-5倍——是频响的下限M= 是下限频率相对应于中频的滚降,一般取2~3db时,M约为二、初级匝数L1B= 取决于磁通量是变压器的磁路长,是变压器的铁芯截面积三、次级阻抗与匝数L2输出变压器的简易设计胆机输出牛的快速设计设计胆机的输出变压器的资料已经不少,本文结合自己近期要制作的4P1S牛输出耳放,对如何抓住要点进行快速设计作一探讨,以供大家参考并期望抛砖引玉:输出变压器的设计要点:负载阻抗初级电感铁芯截面绕组参数绕制工艺具备了这五个要点,就可以刻画出一头输出牛的基本“脾气”了。

一、负载阻抗很多常用的电子管都可以从厂家的技术参数中查到推荐的典型应用阻抗值,但是往往DIYER 要做的电路不一定都是所谓的“典型应用”,用胆管做耳放就是一个明显的例子。

所以从电子管的特性曲线上去寻求一个符合自己特定应用条件负载阻抗,才是正途。

图一是4P1S的特性曲线图,为了求得最佳的负载阻抗,我们选择了图上过ABC三点的负载线,负载线确定的原则是:尽可能地利用最大屏耗允许线(图中往下弯的那条曲线)下的有效面积,这样才能发挥管子的最大潜力。

图中A点是栅偏压为0的点,在这里达到了屏流的上限(横坐标:Imax=73mA),同时也是屏压的下限(纵坐标:Umin=75V);B点是我们的静态工作点,无信号时管子的屏流I0=40mA,屏压为170V;C点是屏压的上限:265V同时也是屏流的下限:3mA.通过这些数据,我们就可以计算出对应于这条负载线的输出阻抗:Rp=(Umax-Umin)/(Imax-Imin)=(265-75)/(0.073-0.003)=2714取:2700(欧姆)二、初级电感Lp=Rp/6.28*f0*根号M2-1其中,f0是我们设计的下限频率,这里取20Hz;M2(2表示是M的平方,下同,在这里写公式真费劲!),M是该下限频率相对应于中频的滚降,通常取2-3(db);我们取3(实践证明:输出变压器的低端滚降并非越小越好,电感过大将会使得分布电容难以控制,从而成为高频响应的“瓶颈”)。

常用电子元件图解

1.★电磁式有源蜂鸣器

★ 有源蜂鸣器是有极 性的,在安装时要 注意它的方向

2.★扬声器(喇叭)

★ 扬声器,俗称“喇叭”他 是一种将电能转换为声能的 电声器件。

★ 扬声器是有极性的元件 ★ 用阻抗(Ω)/功率(W)来标称参数

3 .★传声器(咪头)

★ 传声器声电转换的效率。用dB表示 ★ 传声器是指驻极体电容传声器,即俗称的咪头。 ★ 咪头内部有一个场效应三极管,其作用是 阻抗转换和信号放大,所以咪头工作必须要 加一个直流电压,可在1.5--6v之间选择。

一般二极管的负极用白色、红色或黑色色环标识,发光二极管 一般用引脚长度不同来区分极性,较短的引脚为负极。

C)二极管的变形体:整流块电路、数码发光管、双色发光管

晶体三极管管脚的判别

用万用表判别三极管管脚的根据是:NPN型三极管基极到 发射极和基极到集电极均为PN结的正向;而PNP型三极管 基极到发射极和基极到集电极均为PN结反向。根据二极管 正向电阻小、反向电阻大的特点,判断出三极管的基极,进 而确定集电极与发射极。

在真空中加热合金,合金蒸发,使瓷棒表面形成一 层导电金属膜。刻槽和改变金属膜厚度可以控制阻 值。这种电阻和碳膜电阻相比,体积小、噪声低、 稳定性好,但成本较高。

用康铜或者镍铬合金电阻丝,在陶瓷骨架上绕制而 成。这种电阻分固定和可变两种。它的特点是工作 稳定,耐热性能好,误差范围小,适用于大功率的 场合,额定功率一般在1瓦以上。

实物图片

电阻的参数

1、额定功率

电阻器功率的表示

2、标称阻值与误差允许范围的标识方法

直标法 :如4.7KΩ±10%。 文字符号法:如:2K7表示2.7KΩ 色环标注法:

(1)普通电阻器用四环色带表示阻值与误差

SDRAM布线规则

SDRAM布线规则一:SDRAM 类高速器件布线规则通用基本法则:(1)DDR和主控芯片尽量靠近(2)高速约束中设置所有信号、时钟线等长(最多允许50mil的冗余),所有信号、时钟线长度不超过1000mil (3)尽量0过孔,元件层下面一定要有一个接地良好的地层,所有走线不能跨过地的分割槽,即从元件层透视地层看不到与信号线交叉的地层分割线。

这样的话200M的DDR基本上是没有太大问题。

其它的一些3W 20H法则能做到就尽量做到吧时钟信号:以地平面为参考,给整个时钟回路的走线提供一个完整的地平面,给回路电流提供一个低阻抗的路径。

由于是差分时钟信号,在走线前应预先设计好线宽线距,计算好差分阻抗,再按照这种约束来进行布线。

所有的DDR差分时钟信号都必须在关键平面上走线,尽量避免层到层的转换。

线宽和差分间距需要参考DDR控制器的实施细则,信号线的单线阻抗应控制在50~60 Ω,差分阻抗控制在100~120 Ω。

时钟信号到其他信号应保持在20mil以上的距离来防止对其他信号的干扰。

蛇形走线的间距不应小于20 mil。

串联终端电阻RS值在15~33Ω,可选的并联终端电阻RT 值在25~68 Ω,具体设定的阻值还是应该依据信号完整性仿真的结果。

数据信号组:以地平面为参考,给信号回路提供完整的地平面。

特征阻抗控制在50~60 Ω。

线宽要求参考实施细则。

与其他非DDR 信号间距至少隔离20 mil。

长度匹配按字节通道为单位进行设置,每字节通道内数据信号DQ、数据选通DQS和数据屏蔽信号DM长度差应控制在±25 mil内(非常重要),不同字节通道的信号长度差应控制在1 000 mil内。

与相匹配的DM和DQS串联匹配电阻RS值为0~33 Ω,并联匹配终端电阻RT值为25~68Ω。

如果使用电阻排的方式匹配,则数据电阻排内不应有其他DDR信号。

地址和命令信号组:保持完整的地和电源平面。

特征阻抗控制在50~60 Ω。

关于SDRAM阻抗匹配

【摘】请教关于SDRAM阻抗匹配的问题分类:layout相关2014-05-23 10:07 380人阅读评论(0) 收藏举报现在正在做4755与SDRAM连接,SDRAM的频率为166M,手册上说是需要阻抗匹配的,大概是60欧。

参考君正给的参考设计发现其在SDRAM的地址线源端串联了一个33欧电阻。

显然,这33欧电阻是用来做阻抗匹配的。

问:参考设计所说的60欧的阻抗包不包括这33欧电阻呢?答:这个60欧的阻抗应该是传输线的特征阻抗,不包括33欧姆电阻。

那个电阻是去振铃的,但振铃就是阻抗不匹配造成的,匹配了就没振铃了。

问:用串联电阻做阻抗匹配的话,还需不需要计算走线的阻抗?还是说两者都需要?答:DRAM Layout时第一就要保证走线的阻抗,例如 DDR的数据线保证特征阻抗为50-60欧姆,差分信号线为100-120欧姆。

如果不加串联电阻,其实大多数情况下,也可以正常跑起来。

但是,为了可靠性来讲,并不建议这样做。

如果在在DRAM的端口串联一个电阻,可以使DRAM端口的输出阻抗加上这个串联电阻阻抗等于传输线的特征阻抗,简单的说这样可以有效的避免信号反射,提高可靠性。

问:如果我用POLAR计算得传输线的阻抗为87欧,DRAM端口的输出阻抗为22欧,是不是说我只要串联一个65欧的就行?如果这样的话,那么很多书上写的:传输线阻抗为50欧是什么意思呢?是的,加入电阻式串行匹配的一种方式。

传输线阻抗为50欧是这个意思:在信号的传输过程中,在信号沿到达的地方,信号线和参考平面(电源平面或地平面)之间由于电场的建立,就会产生一个瞬间的电流,如果传输线是各向同性的,那么只要信号在传输,就会始终存在一个电流I,而如果信号的输出电平为V,则在信号传输过程中(注意是传输过程中),传输线就会等效成一个电阻,大小为V/I,我们把这个等效的电阻称为传输线的特征阻抗Z。

要格外注意的是,这个特征阻抗是对交流(AC)信号而言的,对直流(DC)信号,传输线的电阻并不是Z,而是远小于这个值。

常用规格电阻一览电阻基本知识检测方法参数对应表

本文档为整理搜集网络中关于电阻的一些基本知识,仅供参考学习使用。

本文大致包含以下内容;1;常用阻值表2;电阻基础知识3;电阻基本检测方法常用阻值表;此表罗列的5% 1%常用阻值表,规格参数适用于大部分贴片电阻于色环电阻5%精度阻值表单位欧姆(Ω)(E24)1.0 5.6 33 160 820 3.9K 20K 10 0K 510K2.7M1.1 6.2 36 180 910 4.3K 22K 11 0K 560K 3M1.2 6.8 39 200 1K 4.7K 24K 1 20K 620K 3.3M1.3 7.5 43 220 1.1K 5.1K 27K 130 K 680K 3.6M1.5 8.2 47 240 1.2K 5.6K 30K 150 K 750K 3.9M1.6 9.1 51 270 1.3K 6.2K 33K 160 K 820K 4.3M1.8 10 56 300 1.5K 6.6K 36K 18 0K 910K 4.7M2.0 11 62 330 1.6K 7.5K 39K 20 0K 1M 5.1M2.2 12 68 360 1.8K 8.2K 43K 22 0K 1.1M 5.6M2.4 13 75 390 2K 9.1K 47K240K 1.2M 6.2M2.7 15 82 430 2.2K 10K 51K 2 70K 1.3M 6.8M3.0 16 91 470 2.4K 11K 56K 3 00K 1.5M 7.5M3.3 18 100 510 2.7K 12K 62K 33 0K 1.6M 8.2M3.6 20 110 560 3K 13K 68K360K 1.8M 9.1M3.9 22 120 620 3.2K 15K 75K 39 0K 2M 10M4.3 24 130 680 3.3K 16K 82K 43 0K 2.2M 15M4.7 27 150 750 3.6K 18K 91K 47 0K 2.4M 22M5.1 30备注;15M 22M属于高阻,相对价格比其他略贵些1%精度阻值表单位欧姆(Ω)(E96)10 33 100 332 1K 3.32K 10.5K34K 107K 357K10.2 33.2 102 340 1.02K 3.4K 10.7K 34.8K110K 360K10.5 34 105 348 1.05K 3.48K 11K 35 .7K 113K 365K10.7 34.8 107 350 1.07K 3.57K 11.3K 36K115K 374K11 35.7 110 357 1.1K 3.6K 11.5K 36 .5K 118K 383K11.3 36 113 360 1.13K 3.65K 11.8K 37.4 K 120K 390K11.5 36.5 115 365 1.15K 3.74K 12K 38.3 K 121K 392K11.8 37.4 118 374 1.18K 3.83K 12.1K 39K124K 402K12 38.3 120 383 1.2K 3.9K 12.4K 39 .2K 127K 412K12.1 39 121 390 1.21K 3.92K 12.7K 40.2 K 130K 422K12.4 39.2 124 392 1.24K 4.02K 13K 41.2 K 133K 430K12.7 40.2 127 402 1.27K 4.12K 13.3K 42.2K137K 432K13 41.2 130 412 1.3K 4.22K 13.7K 43K140K 442K13.3 42.2 133 422 1.33K 4.32K 14K 43.2 K 143K 453K13.7 43 137 430 1.37K 4.42K 14.3K 44.2 K 147K 464K14 43.2 140 432 1.4K 4.53K 14.7K 45. 3K 150K 470K14.3 44.2 143 442 1.43K 4.64K 15K 46.4 K 154K 475K14.7 45.3 147 453 1.47K 4.7K 15.4K 47K158K 487K15 46.4 150 464 1.5K 4.75K 15.8K 47. 5K 160K 499K15.4 47 154 470 1.54K 4.87K 16K 48 .7K 162K 511K15.8 47.5 158 475 1.58K 4.99K 16.2K 49.9K16 48.7 160 487 1.6K 5.1K 16.5K 51 K 169K 536K16.2 49.9 162 499 1.62K 5.11K 16.9K 51.1K174K 549K16.5 51 165 510 1.65K 5.23K 17.4K 52.3 K 178K 560K16.9 51.1 169 511 1.69K 5.36K 17.8K 53.6K180K 562K17.4 52.3 174 523 1.74K 5.49K 18K 54.9 K 182K 576K17.8 53.6 178 536 1.78K 5.6K 18.2K 56K187K 590K18 54.9 180 549 1.8K 5.62K 18.7K 56. 2K 191K 604K18.2 56 182 560 1.82K 5.76K 19.1K 57.6 K 196K 619K18.7 56.2 187 562 1.87K 5.9K 19.6K 59K200K 620K19.1 57.6 191 565 1.91K 6.04K 20K 60.4 K 205K 634K19.6 59 196 578 1.96K 6.19K 20.5K 61.9 K 210K 649K20 60.4 200 590 2K 6.2K 21K62K 215K 665K20.5 61.9 205 604 2.05K 6.34K 21.5K 63.4K220K 680K21 62 210 619 2.1K 6.49K 22K64.9K 221K 681K21.5 63.4 215 620 2.15K 6.65K 22.1K 66.5K226K 698K22 64.9 220 634 2.2K 6.8K 22.6K 68 K 232K 715K22.1 66.5 221 649 2.21K 6.81K 23.2K 68.1K237K 732K22.6 68 226 665 2.26K 6.98K 23.7K 69.8 K 240K 750K23.2 68.1 232 680 2.32K 7.15K 24K 71.5 K 243K 768K23.7 69.8 237 681 2.37 7.32K 24.3K 73.2K249K 787K24 71.5 240 698 2.4K 7.5K 24.9K 75 K 255K 806K24.3 73.2 243 715 2.43K 7.68K 25.5K 76.8K24.7 75 249 732 2.49K 7.87K 26.1K 78.7 K 267K 825K24.9 75.5 255 750 2.55K 8.06K 26.7K 80.6K270K 845K25.5 76.8 261 768 2.61K 8.2K 27K 82K274K 866K26.1 78.7 267 787 2.67K 8.25K 27.4K 82.5K280K 887K26.7 80.6 270 806 2.7K 8.45K 28K 84. 5K 287K 909K27 82 274 820 2.74K 8.66K 28.7K 86 .6K 294K 910K27.4 82.5 280 825 2.8K 8.8K 29.4K 88.7 K 300K 931K28 84.5 287 845 2.87K 8.87K 30K 90 .9K 301K 953K28.7 86.6 294 866 2.94K 9.09K 30.1K 91K309K 976K29.4 88.7 300 887 3.0K 9.1K 30.9K 93.1 K 316K 1.0M30 90.9 301 909 3.01K 9.31K 31.6K 95.3 K 324K 1.5M30.1 91 309 910 3.09K 9.53K 32.4K 97.6 K 330K 2.2M30.9 93.1 316 931 3.16K 9.76K 33K 100K332K31.6 95.3 324 953 3.24K 10K 33.2K 102K340K32.4 97.6 330 976 3.3K 10.2K 33.6K 105K348K备注;1M 1.5M 2.2M属于高阻相对价格比其他略贵些电阻基础知识;电阻器是电路元件中应用最广泛的一种,在电子设备中约占元件总数的30%以上,其质量的好坏对电路工作的稳定性有极大影响。

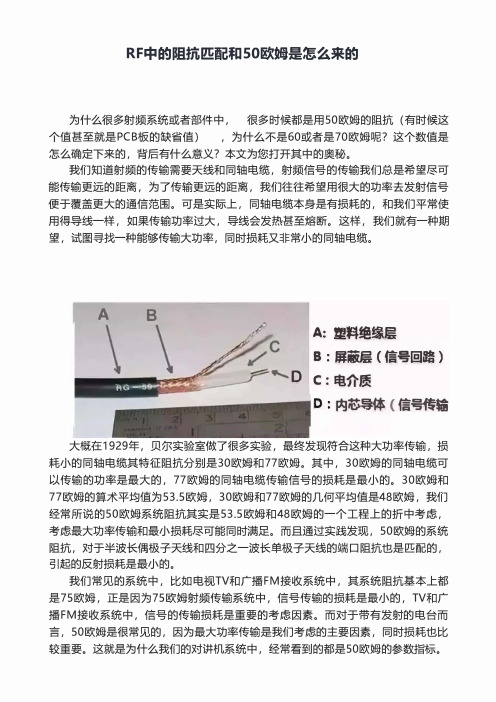

RF中的阻抗匹配和50欧姆是怎么来的

文二)射频美:

so 你可以从基本的物理学来证明 欧姆是最好的, 电缆的趋肤效应损耗L (以 zo 分贝做单位)和总的趋肤效应电阻R (单位长度)除以特性阻抗 成正比。 总的

趋肤效应电阻R是屏蔽层和中间导体电阻之和。 屏蔽层的趋肤效应电阻在高频时, 和它的直径d2成反比。 同轴电缆内部导体的趋肤效应电阻在高频时, 和他的直径 d1成反比。 总共的串联电阻R, 因此和(1/d2+1/d1)成正比。 综合这些因素, 给 定d2和相应的隔离材料的介电常数ER, 你可以用以下公式来减少 趋肤效应损 耗。

i

1 (1·迅/dl)

60 d2 ln(生也上

公式3 分离出常数项(/60)*(1/d2),有效的项((1 +d2/d1)/ln(d2/d1))确定最

小点。仔细查看公式三公式的最小值点仅由d2/d1控制,和ER 以及固定值 d2 无

关。以d2/d1为参数,为L做图,显示 d2/d1 =3.5911 时(注:解一个超越方

但

L8

在 任 何I

E R ctw 主 注鳍

0 =忘_06

+ dl 2

t 上

磁 层

1)

1 -

-

1

旺0 晌

工蛔

微 介

波 电

的 常

基 数

石出

)

书 的

中 函

数,

你都可以找到

z。

是

d 2 , d 1 禾E

。

) 伈

n 1

dI

l

II

厮拫 手

把公式2带入公式1中,分子分母同时乘以d2,整理得到:

忘 — , L 文

外径电缆(博主注:d2) /除了提高强度外,更主要的原因是,外径越大,内径也

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

谈谈四层板和33欧电阻

选用四层板不仅是电源和地的问题,高速数字电路对走线的阻抗有要求,二层板不好控制阻抗。

33欧电阻一般加在驱动器端,也是起阻抗匹配作用的;布线时要先布数据地址线,和需要保证的高速线;

在高频的时候,PCB板上的走线都要看成传输线。

传输线有其特征阻抗,学过传输线理论的都知道,当传输线上某处出现阻抗突变(不匹配)时,信号通过就会发生反射,反射对原信号造成干扰,严重时就会影响电路的正常工作。

采用四层板时,通常外层走信号线,中间两层分别为电源和地平面,这样一方面隔离了两个信号层,更重要的是外层的走线与它们所靠近的平面形成称为“微带”(microstrip) 的传输线,它的阻抗比较固定,而且可以计算。

对于两层板就比较难以做到这样。

这种传输线阻抗主要于走线的宽度、到参考平面的距离、敷铜的厚度以及介电材料的特性有关,有许多现成的公式和程序可供计算。

33欧电阻通常串连放在驱动的一端(其实不一定33欧,从几欧到五、六十欧都有,视电路具体情况) ,其作用是与发送器的输出阻抗串连后与走线的阻抗匹配,使反射回来(假设解收端阻抗没有匹配) 的信号不会再次反射回去(吸收掉),这样接收端的信号就不会受到影响。

接收端也可以作匹配,例如采用电阻并联,但在数字系统比较少用,因为比较麻烦,而且很多时候是一发多收,如地址总线,不如源端匹配易做。

这里所说的高频,不一定是时钟频率很高的电路,是不是高频不止看频率,更重要是看信号的上升下降时间。

通常可以用上升(或下降) 时间估计电路的频率,一般取上升时间倒数的一半,比如如果上升时间是1ns,那么它的倒数是1000MHz,也就是说在设计电路是要按500MHz的频带来考虑。

有时候要故意减慢边缘时间,许多高速IC其驱动器的输出斜率是可调的。