cadence元件封装总结

(完整word版)cadence封装中各层的区别作用

silkscreen top:是字符层,一般称顶层字符或元件面字符,为各元器件的外框及名称标识等,都用此层进行布局,个人认为最好与place_bound_top相同,且带有1脚标识.assemly top:是装配层,就是元器件的实际大小,用来产生元器件的装配图.也可以使用此层进行布局;外框尺寸应该为元件除焊盘外的部分(body size);place_bound_top:是元器件封装实际大小,用来防止两个元器件叠加在一起不报错。

外框尺寸需要包括焊盘在内.1.关于焊盘的准确尺寸,大家可以去网上下载软件LP Viewer ,我装的是LP Viewer 10。

2,也许现在有更高的版本,这里有国际标准的封装及尺寸,画元器件焊盘及封装的时候,可以参考这个软件。

2。

2。

1 Regular Pad:具体尺寸更具实际封装的大小,可以参考LP Viewr 里面的尺寸。

2。

2 Thermal relief:热涨缩间隙,常用于相同 NetList 的填充铜薄与PAD 的间隙。

通常比Pad 直径大 20mil(0。

5mm),如果 Pad 直径小于40mil,根据需要适当减小。

2。

3 Anti Pad:抗电边距,常用于不同 NetList 的填充铜薄与 PAD的间隙。

通常比 Pad直径大 20mil(0。

5mm),如果 Pad 直径小于 40mil,根据需要适当减小。

2。

4 SolderMask:通常比规则焊盘大4mil(0.1mm)。

2。

5 Pastemask:通常和规则焊盘大小相仿.2。

6 Filmmask:应用比较少,用户自己设定。

再次归纳:1.贴片焊盘要有SolderMask_TOP和Pastemask_TOP.通孔要有SolderMask_TOP和SolderMask_BOTTOM,因为两边都要露在外面。

盲孔要有SolderMask_TOP,因为一边露在外面。

埋孔焊盘不需要SolderMask和Pastemask,因为都在里面。

Cadence spb16.3学习笔记3__封装

Cadence学习笔记3__封装IPC软件计算后导出下面是STM32F103RCT6(64脚QFP封装)数据手册的封装尺寸:STM32F103xC, STM32F103xD, STM32F103xE Package characteristicsFigure 71. LQFP64 – 10 x 10 mm 64 pin low-profile Figure 72. Recommended footprintTable 72. LQFP64 – 10 x 10 mm 64 pin low-profile quad flat package mechanical data然后打开IPC,在Calculate中打开SMD Calculator,选择QFP封装,双击或者点击ok,出现计算界面,如下图:此时在左侧窗口填上相应的数据,然后光标停在任意一个数据中回车,就可以计算出其余的尺寸了。

注意到这里的单位是毫米Millimeters,所以应该对应数据手册中的毫米而不是英尺。

Pitch(P)在图中是引脚中心的间距,对应于数据手册中的e,值为0.5。

A和B分别是两个方向上的引脚数量,都是16,下面给出了提示,如果是矩形芯片的话,A应该小于B。

Pin Count(for search)是引脚总数,填64。

L1和L2表示包括引脚的芯片宽度和长度,对应芯片手册的D和E,最小值是11.8,最大值是12.2。

T是引脚长度,对应于数据手册中的L,最小值为0.45,最大值为0.75。

W表示焊盘的宽度,对应于数据手册中的b,最小值为0.17,最大值为0.27。

A和B表示不包括引脚的芯片宽度和长度,对应芯片手册的D1和E1,最小值为9.8,最大值为10.2。

H表示芯片的高度,对应于芯片手册中的A,最大值为1.6,不用填最小值。

K表示芯片离PCB板的高度,对应于芯片手册中的A1,最小值为0.05,不用填最大值。

填完之后光标放在任意一个框中回车,就可以计算出其余的数据了。

cadence封装学习笔记(含实例)

Cadence封装制作实例这是因为本人现在在学习PCB layout,而网上没有很多的实例来讲解,如果有大师愿意教我那有多好啊,嘿嘿!这里本人把学习cadence封装后的方法通过实例给其他的初学者更好的理解,因为本人也是初学者,不足或错误的地方请包涵,谢谢!一. M12_8芯航空插座封装制作1.阅读M12_8芯航空插座的Datasheet了解相关参数;根据Datasheet可知:a.航空插座的通孔焊盘Drill尺寸为1.2mm≈50mil,我们可以设计其焊盘为P65C50(焊盘设计会涉及到);b.航空插座的直径为5.5mm=216.53mil,以5.5/2mm为半径;2.根据参数设计该航空插座的焊盘;a.已知钻孔直径Drill_size≈50mil可知:Regular Pad=Drill_size+16mil通孔焊盘尺寸计算规则:设元器件直插引脚直径为M,则1)钻孔直径Drill_size=M+12mil,M≤40=M+16mil,40<M≤80=M+20mil,M>802)规则焊盘Regular Pad=Drill_size+16mil,Drill_size<50mil=Drill_size+30mil,Drill_size≥50mil=Drill_size+40mil,Drill_size为矩形或椭圆形3)阻焊盘Anti-Pad=Regular Pad+20mil4)热风焊盘Drill_size<10mil,内径ID=Drill_size+10mil,外径OD=Drill_size+20mil;Drill_size>10mil,内径ID= Drill_size+20mil外径OD= Regular Pad+20mil= Drill_size+36mil,Drill_size<50mil= Drill_size+50mil,Drill_size≥50mil= Drill_size+60mil,Drill_size为矩形或椭圆b.按照通孔焊盘计算方式我们命名为P65C50,打开Pad_Designer;File\NEW,点击Browse,选择文件所放路径,新建P65C50.pad文件新建好文件后,设置相关参数:点击File\Save,保存此文件,通孔焊盘完成。

cadence总结

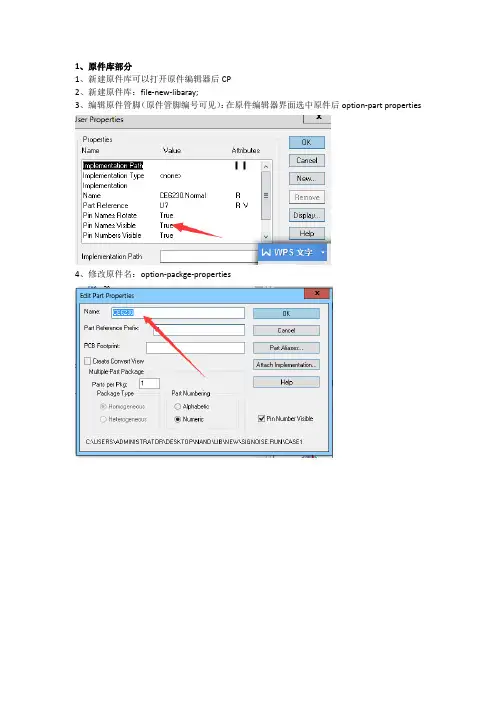

1、原件库部分1、新建原件库可以打开原件编辑器后CP2、新建原件库:file-new-libaray;3、编辑原件管脚(原件管脚编号可见):在原件编辑器界面选中原件后option-part properties4、修改原件名:option-packge-properties5、新建多罗辑器件点击原件后右击新建原件5.1多罗辑切换到下个罗辑用快捷键ctrl+N;ctor+b;返回修改。

5.2 Drill diameter 比Regular pad小0.5mm。

新建焊盘通孔焊盘Mm设置精度4个小数点。

Padmeters layers 设置标贴Soldermask比其他层次大5MIL(阻焊层比焊盘大5MIL)。

焊盘命名方式(SMD/DIP)+(焊盘形状缩写)+(孔径大小)。

Anti pad 比regular pad 大0.254(10MIL)。

3、新建元器件封装3.1设置图纸大小3.2设置删格大小3.3添加pin脚3.4添加丝印外框Add/LINE/silkscreen-top3.5添加装配层丝印外框Add/line/packge Geometry/assembly_Top3.6添加place_Bound_TOPShape/选择形状/package Geometry/place_Bound_Top/框选器件(防止原件重叠)3.7添加原件高度Setup/areas/packge height/点中原件3.8添加丝印位号添silkreen _top位号:layout/Lables/refdes添ASsmbly_top位号:layout/Lables/refdes新建PCBFile -new -Board1、导入DXFFile-import-DXF (一般设置DXF Units设置单位为MM)设置为mm导入后设置编辑页面大小2、同一大类子类的切换Edit -change后面选择需要切换到的子类(首先界面是要被切换的界面)。

cadence元件封装总结

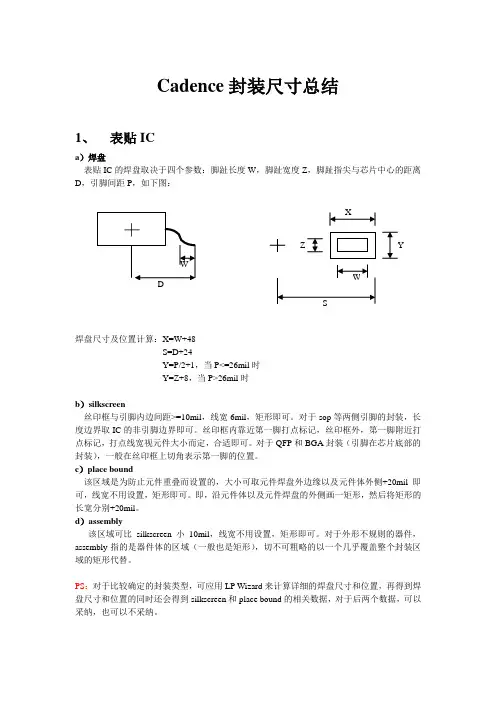

Cadence 封装尺寸总结1、 表贴ICa )焊盘表贴IC 的焊盘取决于四个参数:脚趾长度W ,脚趾宽度Z ,脚趾指尖与芯片中心的距离D ,引脚间距P ,如下图:焊盘尺寸及位置计算:X=W+48S=D+24 Y=P/2+1,当P<=26mil 时 Y=Z+8,当P>26mil 时b )silkscreen丝印框与引脚内边间距>=10mil ,线宽6mil ,矩形即可。

对于sop 等两侧引脚的封装,长度边界取IC 的非引脚边界即可。

丝印框内靠近第一脚打点标记,丝印框外,第一脚附近打点标记,打点线宽视元件大小而定,合适即可。

对于QFP 和BGA 封装(引脚在芯片底部的封装),一般在丝印框上切角表示第一脚的位置。

c )place bound该区域是为防止元件重叠而设置的,大小可取元件焊盘外边缘以及元件体外侧+20mil 即可,线宽不用设置,矩形即可。

即,沿元件体以及元件焊盘的外侧画一矩形,然后将矩形的长宽分别+20mil 。

d )assembly该区域可比silkscreen 小10mil ,线宽不用设置,矩形即可。

对于外形不规则的器件,assembly 指的是器件体的区域(一般也是矩形),切不可粗略的以一个几乎覆盖整个封装区域的矩形代替。

PS :对于比较确定的封装类型,可应用LP Wizard 来计算详细的焊盘尺寸和位置,再得到焊盘尺寸和位置的同时还会得到silkscreen 和place bound 的相关数据,对于后两个数据,可以采纳,也可以不采纳。

2、通孔ICa)焊盘对于通孔元件,需要设置常规焊盘,热焊盘,阻焊盘,最好把begin层,internal层,bottom 层都设置好上述三种焊盘。

因为顶层和底层也可能是阴片,也可能被作为内层使用。

通孔直径:比针脚直径大8-20mil,通常可取10mil。

常规焊盘直径:一般要求常规焊盘宽度不得小于10mil,通常可取比通孔直径大20mil (此时常规焊盘的大小正好和花焊盘的内径相同)。

Cadence_Allegro元件封装制作流程含实例

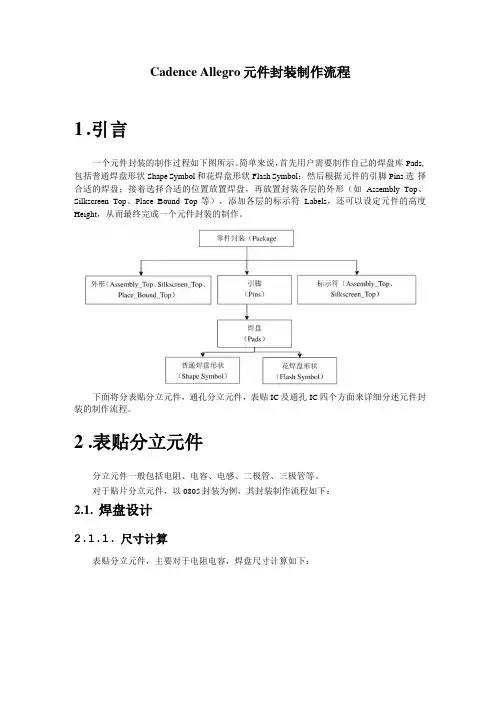

Cadence Allegro元件封装制作流程1.引言一个元件封装的制作过程如下图所示。

简单来说,首先用户需要制作自己的焊盘库Pads, 包括普通焊盘形状Shape Symbol和花焊盘形状Flash Symbol;然后根据元件的引脚Pins选择合适的焊盘;接着选择合适的位置放置焊盘,再放置封装各层的外形(如Assembly_Top、Silkscreen_Top、Place_Bound_Top等),添加各层的标示符Labels,还可以设定元件的高度Height,从而最终完成一个元件封装的制作。

下面将分表贴分立元件,通孔分立元件,表贴IC及通孔IC四个方面来详细分述元件封装的制作流程。

2.表贴分立元件分立元件一般包括电阻、电容、电感、二极管、三极管等。

对于贴片分立元件,以0805封装为例,其封装制作流程如下:2.1.焊盘设计2.1.1.尺寸计算表贴分立元件,主要对于电阻电容,焊盘尺寸计算如下:其中,K 为元件引脚宽度,H 为元件引脚高度,W 为引脚长度,P 为两引脚之间距离(边 距离,非中心距离),L 为元件长度。

X 为焊盘长度,Y 为焊盘宽度,R 为焊盘间边距离,G 为封装总长度。

则封装的各尺寸可按下述规则:1) X=Wmax+2/3*Hmax+8 mil2) Y=L ,当 L<50 mil ; Y=L+ (6~10) mil ,当 L>=50 mil 时3) R=P-8=L-2*Wmax-8 mil ;或者G=L+X 。

这两条选一个即可。

个人觉得后者更容易理解,相当于元件引脚外边沿处于焊盘中点,这在元件尺寸较小时很适合(尤其是当 Wmax 标得不准时,第一个原则对封装影响很大),但若元件尺寸较大(比如说钽电容 的封装)则会使得焊盘间距过大,不利于机器焊接,这时候就可以选用第一条原则。

本文介绍中统一使用第二个。

注:实际选择尺寸时多选用整数值,如果手工焊接,尺寸多或少几个mil 影响均不大, 可视具体情况自由选择;若是机器焊接,最好联系工厂得到其推荐的尺寸。

cadence 元件封装制作

元件封装制作一、制作焊盘1、打开焊盘制作软件Pad Designer:2、设置参数(parameters):Type:选择焊盘类型:过孔,盲孔/埋孔,表贴;Internal layers:选择内层结构:一般选择optional,盘片设置好后,内层可以更改。

Units:单位选择,精度一般选择3位即可;Multiple:焊盘上打多个小孔,一般用于固定孔;3设置层(layers):padstack layers设置:begin layer:default internal:end layer:soldermask:阻焊层设置:按照标准,一般只需要比正常的焊盘大0.1mm即可;pastemask:助焊层设置:可以在设置好其中某些项后用鼠标右键点击左边的按钮,选择复制操作。

设置完成后存档即完成焊盘制作工程。

二、封装制作1、打开软件窗口打开ORCAD PCB Editor软件,选择ORCAD PCB Dsigner,在File New 菜单中选择package symbol文件文件类型新建工程。

2、设置图纸参数栅格点设置:选择Setup >Design Parameters打开如下对话框在右下勾中Grids on,然后点击Setup Grids按钮,弹出如下对话框,将栅格设置成1mil。

设置图纸大小(仅为制作元件封装时操作方便):3、放置焊盘选择菜单Layout > Pin,然后在窗口右侧选择option,如下图所示:选中Connect表示表示有电器连接,在Padstack中选择需要放置的焊盘,然后在X:和Y:中分别设置焊盘的数量,间距,排放顺序,接着在Pin#:中设置当前焊盘标号,在Inc:设置递增量。

Text block设置标号字体大小。

Offset设置字体相对焊盘中心偏移。

4、画装配线在菜单中选择ADD > Line,然后在右边option对话框中进行如下配置,配置完成后画线。

装配线如下所示,即为元件轮廓线:5、画丝印层在菜单中选择ADD > Line,然后在右边option对话框中进行如下配置,配置完成后画线。

Cadence常见问题总结

Cadence常见问题总结Cadence常见问题总结一、封装库路径设置Setup →user preferences Editor →Paths →library →Padpath/psmpath设置到库所在位置二、创建焊盘放置pad时报错:cannot be placed outside the drawing extents原因:操作窗口过小,设置大一些Setup →Design Parameters →Design/extents 将变量设大一些三、原理图和Pcb Layout交互运用设置(按模块摆件)在原理图界面,选中.dsn →Options →Preferences/Miscellaneous勾选Enable Intertool Communication(Orcad和Pcb editor 联系的纽带)选中要摆放的模块,拖到layout界面(在layout界面保持Place Manual功能)五,PCB 设计过程中实时查看layout进度Display →Status六、将两个相同属性的shape合在一起Shape →Merge shape →分别点击两个shape七、Via设置成空心的Setup →Design Parameters →Display/勾选Display plated holes八、实时显示走线的长度Setup →user Preferences →Route/Connect/勾选allegro etch length on九、更新部品封装的pad信息打开layout界面,T ools →Padstack →Modify Design Padstack,右侧options 选择要更改的pad →Edit,修改完之后→File →Updateto Design and Exit十、铺铜的两种方式1、shape →polygon, 右侧options里class选etch,sub-class 选择要铺铜的layer,单击鼠标右键→assign net →点击器件的pin →开始画形状2、先画shape,然后选择shape →select shape or void点击sh ape →鼠标右键assign net →点击器件的pin十一、在allegro里把PCB板整个旋转90度选中Move命令,在Options/Point选择User Pick,在Find里全部勾选,右击选中Temp Group,框选整个板子,右击选中Complete,击一点作为User Pick ,然后Rotate十二、对整个原理图重新编号选中.dsn文件→Tools →Annotate →勾选update entire design、Reset part reference to ?(将部品位号全部恢复到?)选中.dsn文件→T ools →Annotate →勾选Refdes control required在右侧相应位置输入起始位号,则可以按page编号十三、allegro 如何设置route keepin,package keepin1、setup →area →route keepin,package keepin →画框2、edit →z-copy →options →package keepin/route keepin →Contract/offset 0.3->点击outline (outline必须是一个封闭的图形)十四、Z-copy失灵首先检查被操作的对象是不是一个封闭的的图形,如果不是,那么就需要把若干segments合成一个整体,shape →compose shape,右侧active class →Board Geometry/outline,框选图中segments,生成shape之后,进行Z-copy,再删掉shape十五、在地平面上加via选择要添加的via →copy,右侧options可以设置via间距和数量十六、快速切换layer设置打开layout界面,Display →Color/Visbility,打开想要显示的内容,View →Color View Save →设置路径,勾选complete →save,将生成文件放到工程allegro目录下即可应用十七、刚安装完软件,手势需要同时按Ctrl+鼠标右键Setup →user preferences Editor →Ui/input →勾选no_dragup →ok经过该设置,画手势只用右键就行十八、设置快捷键Cadence/SPB_16.6/share/pcb/text/env打开env文件(以写字板方式打开)然后进行编辑十九、在原理图赋予器件封装信息双击原理图上元件,弹出对话框,在footprint处输入对应的封装信息,选中Footprint右击Display →勾选value only →apply二十、生成netlist选中.dsn →T ools →create netlist(net名字过长时,系统会自动Rename)如果生成过程中报错,则检查部品封装信息或者device有没有问题。

【Cadence17.2】PCBEditor绘制元器件封装

【Cadence17.2】PCBEditor绘制元器件封装【Cadence17.2】PCB Editor绘制元器件封装•LP Viewer计算元器件封装•PCB Editor绘制元器件封装•o准备工作o放置焊盘o绘制丝印层o绘制装配层o绘制禁止摆放区域o添加参考编号LP Viewer计算元器件封装在使用LP Viewer计算元器件封装尺寸之前,我们首先需要找到该元器件的数据手册,获取它的尺寸信息。

如上图所示,本文以AD627为例进行讲解,由此图可知该芯片的各种尺寸并且其封装为SOIC。

准备好数据手册之后,打开LP Viewer,依次点击Calculate->SMD Calculator,在弹出的窗口中选择对应的封装形式,即Small Outline Package(SOP),该选项包括SOIC封装。

选择好之后点击OK即可。

下一步,只需按照数据手册上的数据将元器件尺寸输入软件的表格中后点击OK即可生成该器件的封装,这里注意要正确选择单位。

之后点击Land Pattern可以看到封装中焊盘的尺寸、位置,以及丝印层、禁止摆放区域的尺寸信息。

中间的十字为坐标原点,在之后的封装绘制过程中,参照这个数据即可。

如果数据手册中已经给出了推荐的焊盘尺寸和封装信息,按照那个画也可以。

PCB Editor绘制元器件封装准备工作首先点击File->New,选择Package symbol,设置好路径(最好是一个专门放置封装的文件夹)并命名好封装的名字(最好不要用大写字母)。

之后点击Set->Design Parameters,设置单位为mm,画布大小设置为100x100mm(这个尺寸基本画所有封装都能满足了),左下角坐标设置为-50,-50(也就是说画布的原点是0,0)。

点击Setup->Grids,设置栅格点间距,全部设置为0.0254mm 即可。

在正式开始绘制封装之前,还需点击Setup->User Preference,找到Path中的Library,确保将存放焊盘文件的路径添加到padpath 中,因为之后绘制封装的时候要放置焊盘,如果不添加这个路径的话会找不到我们准备好的焊盘。

Cadence Allegro封装总结

Cad ence Allegro 封装尺寸总结1、 表贴ICa )焊盘表贴IC 的焊盘取决于四个参数:脚趾长度W ,脚趾宽度Z ,脚趾指尖与芯片中心的距离D ,引脚间距P ,如下图:焊盘尺寸及位置计算:X=W+48 S=D+24 Y=P/2+1,当P<=26mil 时 Y=Z+8,当P>26mil 时b )silkscreen丝印框与引脚内边间距>=10mil ,线宽6mil ,矩形即可。

对于sop 等两侧引脚的封装,长度边界取IC 的非引脚边界即可。

丝印框内靠近第一脚打点标记,丝印框外,第一脚附近打点标记,打点线宽视元件大小而定,合适即可。

对于QFP 和BGA 封装(引脚在芯片底部的封装),一般在丝印框上切角表示第一脚的位置。

c )place bound该区域是为防止元件重叠而设置的,大小可取元件焊盘外边缘以及元件体外侧+20mil 即可,线宽不用设置,矩形即可。

即,沿元件体以及元件焊盘的外侧画一矩形,然后将矩形的长宽分别+20mil 。

d )assembly该区域可比silkscreen 小10mil ,线宽不用设置,矩形即可。

对于外形不规则的器件,assembly 指的是器件体的区域(一般也是矩形),切不可粗略的以一个几乎覆盖整个封装区域的矩形代替。

PS :对于比较确定的封装类型,可应用LP Wizard 来计算详细的焊盘尺寸和位置,再得到焊盘尺寸和位置的同时还会得到silkscreen 和place bound 的相关数据,对于后两个数据,可以采纳,也可以不采纳。

2、通孔ICa)焊盘对于通孔元件,需要设置常规焊盘,热焊盘,阻焊盘,最好把begin层,internal层,bottom 层都设置好上述三种焊盘。

因为顶层和底层也可能是阴片,也可能被作为内层使用。

通孔直径:比针脚直径大8-20mil,通常可取10mil。

常规焊盘直径:一般要求常规焊盘宽度不得小于10mil,通常可取比通孔直径大20mil (此时常规焊盘的大小正好和花焊盘的内径相同)。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Cadence 封装尺寸总结

1、 表贴IC

a )焊盘

表贴IC 的焊盘取决于四个参数:脚趾长度W ,脚趾宽度Z ,脚趾指尖与芯片中心的距离D ,引脚间距P ,如下图:

焊盘尺寸及位置计算:X=W+48

S=D+24 Y=P/2+1,当P<=26mil 时 Y=Z+8,当P>26mil 时

b )silkscreen

丝印框与引脚内边间距>=10mil ,线宽6mil ,矩形即可。

对于sop 等两侧引脚的封装,长度边界取IC 的非引脚边界即可。

丝印框内靠近第一脚打点标记,丝印框外,第一脚附近打点标记,打点线宽视元件大小而定,合适即可。

对于QFP 和BGA 封装(引脚在芯片底部的封装),一般在丝印框上切角表示第一脚的位置。

c )place bound

该区域是为防止元件重叠而设置的,大小可取元件焊盘外边缘以及元件体外侧+20mil 即可,线宽不用设置,矩形即可。

即,沿元件体以及元件焊盘的外侧画一矩形,然后将矩形的长宽分别+20mil 。

d )assembly

该区域可比silkscreen 小10mil ,线宽不用设置,矩形即可。

对于外形不规则的器件,assembly 指的是器件体的区域(一般也是矩形),切不可粗略的以一个几乎覆盖整个封装区域的矩形代替。

PS :对于比较确定的封装类型,可应用LP Wizard 来计算详细的焊盘尺寸和位置,再得到焊盘尺寸和位置的同时还会得到silkscreen 和place bound 的相关数据,对于后两个数据,可以采纳,也可以不采纳。

2、通孔IC

a)焊盘

对于通孔元件,需要设置常规焊盘,热焊盘,阻焊盘,最好把begin层,internal层,bottom 层都设置好上述三种焊盘。

因为顶层和底层也可能是阴片,也可能被作为内层使用。

通孔直径:比针脚直径大8-20mil,通常可取10mil。

常规焊盘直径:一般要求常规焊盘宽度不得小于10mil,通常可取比通孔直径大20mil (此时常规焊盘的大小正好和花焊盘的内径相同)。

这个数值可变,通孔大则大些,比如+20mil,通孔小则小些,比如+12mil。

花焊盘直径:花焊盘内径一般比通孔直径大20mil。

花焊盘外径一般比常规焊盘大20mil (如果常规焊盘取比通孔大20mil,则花焊盘外径比花焊盘内径大20mil)。

这两个数值也是可以变化的,依据通孔大小灵活选择,通孔小时可取+10-12mil。

阻焊盘直径:一般比常规焊盘大20mil,即应该与花焊盘外径一致。

这个数值也可以根据通孔大小调整为+10-12mil。

注意需要与花盘外径一致。

对于插件IC,第一引脚的TOP(begin)焊盘需要设置成方形。

b) Silkscreen

与表贴IC的画法相同。

c) Place bound

与表贴IC的画法相同。

d) Assembly

与表贴IC的画法相同。

3、表贴分立元件

分立元件一般包括电阻、电容、电感、二极管、三极管等。

对于贴片分立元件,封装规则如下:

a)焊盘

表贴分立元件,主要对于电阻电容,焊盘尺寸计算如下:

X=W+2/3*Hmax+8

Y=L ,一般这个数值应该比L 稍微大些,比如+6-8mil 。

R=P-8,该数值用来确定焊盘的位置。

一般也可以通过LP Wizard 来获得符合IPC 标准的焊盘数据。

b ) Place bound

与表贴IC 相同。

即元件体以及焊盘的外边缘矩形+20mil ,线宽不用设置,矩形即可。

c ) silkscreen

一般选择比place bound 略小的矩形框代替,比如-4mil ,线宽6mil 即可。

对于有极性的分立元件,需要在丝印框上显示出来,比如正极的丝印框线条稍微粗一点,比如8mil ,也可在正极画双线表示。

对于表贴三极管丝印层如下图:

d ) assembly

比丝印框稍微小一点,比如-4mil ,线宽不用设置,矩形即可。

但是对于不规则的封装,比如TO 或者SOT ,assembly 区域指的是元件体的区域(一般也是矩形),切不可以一个几乎覆盖全部区域的矩形代替,否则贴片时将出现贴片位置不准的大问题。

PS :由于分立元件尺寸都比较小,因此线宽的选择可以稍微细些。

4、 直插分立元件

比如插针,按钮等。

侧视图

底视图

焊盘底视图

L

丝印框(长度和位置合适即可,线宽可以去4mil )。

对于这些元件,焊盘的参数与上面通孔IC的焊盘参数计算方法相同。

Place bound,assembly,silkscreen与表贴分立元件相应的参数基本相同。

总结:元件的封装,对于焊盘的要求比较严格,如果能够使用LP Wizard计算,最好采用LP Wizard得出的焊盘参数。

Assembly也是比较严格的,最起码,元件体的中心要与所画的assembly中心重合,这样才能使表贴的位置有保证。

焊盘类别解释:

常规焊盘:即用于阳片的焊盘,通过布线与其他资源连接在一起,主要用于信号层。

热风焊盘:也称为花焊盘,主要用于阴片,作用是为了防止热量散失产生虚焊等,主要用于电源层以及地层,即在地层或者电源层,通过花焊盘与地层或者电源层取得连接。

阻焊盘:主要用于阴片,即断开该过孔与相应内层(比如电源或者地层)的电气连接。

总之,常规焊盘用于阳片的电气连接,花焊盘用于阴片的电气连接,阻焊盘用于阴片的电气隔离。