南京理工大学电子线路课程设计(优秀)

南理工 _电力电子课程设计分析

电力电子技术课程设计报告学院:自动化学院专业:电气工程及其自动化指导老师:学生:学号1010190136目录1 设计目的––––––––––––––––––––––32 电路的工作原理及实验步骤––––––––––––––3①不可逆PWM变换器–––––––––––––––3②有制动的不可逆PWM变换器电路–––––––––4不可逆PWM变换器电路中的一般电动状态–––––5不可逆PWM变换器电路中的制动状态–––––––6③桥式可逆PWM变换器–––––––––––––7桥式可逆PWM变换器电路中电机正向运行–––––8桥式可逆PWM变换器电路中电机反向运行–––––9双极式控制可逆PWM变换器的分析––––––10桥式可逆PWM变换器的性能评价––––––14 3 实验总结–––––––––––––––––––––15一设计目的通过斩波电路来实现的直流脉宽调速电路,此斩波电路由基本的降压型变换器和升压型变换器相组合,选用全控型器件IGBT,当此变换器对直流电动机供电时,只要对IGBT进行实时的PWM 控制,就可实现电机的四象限运行。

二电路的工作原理及实验步骤1 我们首先先了解一下简单的不可逆PWM变换器,简单的不可逆PWM 变换器-直流电动机系统主电路原理图如下图所示:在Matlab中的电路图如下:在一个开关周期内,当0 ≤ t < ton 时,Ug 为正,IGBT 导通,电源电压通过IGBT 加到电动机电枢两端,当ton ≤ t < T 时, Ug 为负,IGBT 关断,电枢失去电源,经VD 续流。

在Matlab 中的仿真图中,触发电路的参数如下:电机运行时的波形如下:电机两端得到的平均电压为s s on d U U Tt U ρ==式中 ρ 为 PWM 波形的占空比,改变ρ(10≤≤ρ)既可以调节电机的转速。

2 有制动的不可逆PWM 变换器电路在简单的不可逆电路中电流不能反向,因而没有制动能力,只能作单象限运行。

南京理工大学电子线路课程设计(优秀)

南京理工大学电子线路课程设计实验报告摘要本次实验利用QuartusII7.0软件并采用DDS技术、FPGA芯片和D/A转换器,设计了一个直接数字频率信号合成器,具有频率控制、相位控制、测频、显示多种波形等功能。

并利用QuartusII7.0软件对电路进行了详细的仿真,同时通过SMART SOPC 实验箱和示波器对电路的实验结果进行验证。

报告分析了整个电路的工作原理,还分别说明了设计各子模块的方案和编辑、以及仿真的过程。

并且介绍了如何将各子模块联系起来,合并为总电路。

最后对实验过程中产生的问题提出自己的解决方法。

并叙述了本次实验的实验感受与收获。

关键词数字频率信号合成器频率控制相位控制测频示波器AbstractThis experient introduces using QuartusII7.0software, DDS technology,FPGA chip and D/A converter to design a multi—output waveform signal generator in which the frequency and phase are controllable and test frequency,display waveform.It also make the use of software QuartusII7.0 a detailed circuit simulation, and verify the circuit experimental results through SMART SOPC experiment box and the oscilloscope.The report analyzes the electric circuit principle of work,and also illustrates the design of each module and editing, simulation, and the process of using the waveform to testing each Sub module. Meanwhile,it describes how the modules together, combined for a total circuit. Finally theexperimental problems arising in the process of present their solutions. And describes the experience and result of this experiment.Keywords multi—output waveform signal- generator frequency controllable phase controllable test frequency oscilloscope目录一、实验目的与要求 (4)二、电路工作原理 (4)三、子模块设计原理 (8)3.1 分频电路 (8)3.2频率预置和调节电路 (11)3.3累加寄存电路 (13)3.4相位控制电路 (15)3.5波形存储电路 (15)3.6测频电路 (18)3.7译码显示电路 (20)3.8波形选择电路 (22)3.9 节省ROM的设计 (23)3.10总电路 (25)3.11AM调制 (25)四、调试 (29)五、编程下载 (29)六、波形结果 (29)七、结论 (32)八、实验小结 (32)参考文献 (33)一.实验目的与要求本实验使用DDS的方法设计一个任意频率的正弦信号发生器,要求具有频率控制、相位控制、测频、切换波形,动态显示以及使能开关等功能。

南理工电子信息课程设计

南理工电子信息课程设计一、课程目标知识目标:1. 理解并掌握电子信息工程基本概念,包括信号与系统、数字信号处理等;2. 学习并掌握基础的电子电路原理,如放大器、滤波器等;3. 掌握基础的编程知识,如C语言、Python语言等,并能应用于简单的电子信息处理;4. 理解现代通信系统的基本原理,如数字通信、无线通信等。

技能目标:1. 能够运用所学知识设计简单的电子信息系统,具备初步的电路分析和调试能力;2. 能够运用编程语言编写简单的程序,实现对电子信息进行处理和分析;3. 能够运用所学知识解决实际问题,具备一定的创新能力和实践能力。

情感态度价值观目标:1. 培养学生对电子信息工程的兴趣,激发学生主动探索科学技术的热情;2. 培养学生的团队协作精神,提高沟通与交流能力;3. 增强学生的国家意识,认识到电子信息工程在国家科技发展中的重要性,培养学生的责任感。

课程性质:本课程为电子信息工程专业的基础课程,旨在让学生掌握电子信息领域的基本知识和技能,为后续专业课程打下坚实基础。

学生特点:学生为南理工电子信息工程专业大一或大二学生,具备一定的物理和数学基础,对电子信息工程有一定了解,但实践经验不足。

教学要求:结合学生特点和课程性质,注重理论与实践相结合,强化实践操作环节,培养学生动手能力和创新能力。

通过本课程的学习,使学生能够达到上述课程目标,为未来从事电子信息工程领域工作奠定基础。

二、教学内容1. 电子信息工程基本概念:包括信号的分类、特性和处理方法,系统的性质和分类,数字信号处理的基础知识等。

对应教材第一章内容。

2. 基本电子电路:讲解放大器、滤波器、振荡器等基本电路的原理、设计和应用。

对应教材第二章内容。

3. 编程语言基础:介绍C语言、Python语言的基本语法、数据结构、控制语句等,并结合电子信息处理实例进行讲解。

对应教材第三章内容。

4. 数字通信原理:包括数字通信系统的基本组成、调制解调技术、误码纠正等。

南京理工大学eda实验一 单极放大电路的设计与仿真

实验一单极放大电路的设计与仿真一、实验内容1.设计一个分压偏置的单管电压放大电路,要求信号源频率5kHz(幅度1mV) ,负载电阻5.1kΩ,电压增益大于50。

2. 调节电路静态工作点(调节电位计),观察电路出现饱和失真和截止失真的输出信号波形,并测试对应的静态工作点值。

3. 加入信号源频率5kHz(幅度1mV) ,调节电路使输出不失真,测试此时的静态工作点值。

测电路的输入电阻、输出电阻和电压增益4. 测电路的频率响应曲线和f L、f H值。

二、实验报告要求1.给出单级放大电路原理图。

2.给出电路饱和失真、截止失真、和不失真时的输出信号波形图,并给出三种状态下电路静态工作点值。

3.给出测量输入电阻、输出电阻和电压增益的实验图,给出测试结果并和看理论计算值进行比较。

4.给出电路的幅频和相频特性曲线,并给出电路的f L、f H值。

5.分析实验结果三、实验步骤1实验原理图2电路饱和失真截止失真最大不失真<1>饱和失真时的波形描述:此时滑动变阻器调为10%其静态工作点:由图得 I(BQ)=172.52300u I(CQ)=883.65600uU(BEQ)=U5-U7=0.63257V U(CEQ)=U3-U7=0.05327V<2>截止失真时的波形在描述:此时滑动变阻器滑到47%其静态工作点为由图得 I(BQ)=2.92160uA I(CQ)=615.90300uAU(BEQ)=U5-U7=0.61423V U(CEQ)=U3-U7=4.22668V<3>最大不失真波形描述:此时电压为 8MV 滑动变阻器滑到28%其静态工作点为:由图得 I(BQ)=4.26490uA I(CQ)=875.44100uAuU(BEQ)=U5-U7=0.62422V U(CEQ)=U3-U7=0.98933V可得100*28%+5=32KΩ3 1mv不失真情况下输入电阻、输出电阻和电压增益电路图静态工作点<1>输入电阻表的读数输入电阻为测量值是999.972ⅹ1000÷237.431=4.211kΩ理论值为 Ri=RB//(hie+(1+β)RE)=13.037*6.296/(13.037+6.296)=83.081/19.333=4.2456 kΩHie=200+26mv/IB=200+6096=6296=6.296kΩRB=32ⅹ22/(32+22)=13.037K Ωβ=IC÷IB=205.266相对误差(4.2456-4.211)/4.2456=0.8%误差分析:器件存在误差,存在0.8%的误差是在允许范围内<2>输出电阻表的示数是输出电阻测量值是999.972ⅹ1000÷135.143=7.4kΩ理论值是R2=7.9KΩ相对误差(7.9-7.4)÷7.9=6.3%误差分析:理论值是近似等于RC的所以存在误差,再加上实际器件存在百分之几的误差。

南京理工大学电工电子实验1

南京理⼯⼤学电⼯电⼦实验1电⼯电⼦综合实验论⽂班级:学号:姓名:⾮线性电阻电路的应⽤---混沌电路⼀、摘要:蔡式电路是美国贝莱克⼤学的蔡少堂教授设计的能产⽣混沌⾏为的最为简洁的⼀种⾃治电路,该型电路并不唯⼀,在⾮线性系统及混沌研究中,占有极为重要的地位。

该电路结构简单,但却出现双涡卷奇怪引⼦和及其丰富的混沌动⼒学⾏为。

本实验研究⾮线性电阻的特性和混沌电路。

试验中利⽤两个运算放⼤器模拟⾮线性电阻,并⽤列表法测量做出其伏安特性曲线,并利⽤⽰波器观察其伏安特性曲线。

同样利⽤两个运算放⼤器,实现混沌现象,并研究其图像的规律。

⼆、关键词:⾮线性负电阻,混沌电路,三、引⾔:混沌(Chaos)是20世纪物理学的重⼤事件。

混沌研究最先起源于洛伦兹研究天⽓预报时⽤到的三个动⼒学⽅程。

后来的研究表明,⽆论时复杂的系统,如⽓象系统、太阳系,还是简单系统,如滴⽔龙头等,皆因存在着内在随机性⽽出现类似⽆轨,但实际是⾮周期有序运动,即混沌现象。

现在混沌研究涉及的领域包括数学、物理学、⽣物学、化学、天⽂学、经济学及⼯程技术的众多学科,并对这些学科的发展产⽣了重要影响,混沌包含的物理内容⾮常⼴泛,研究这些内容更需要⽐较深⼊的数学理论,如微分动⼒学⽅程、拓补学、分形⼏何学等。

⽬前混沌的研究重点已转向多维动⼒学系统中的混沌、量⼦及时空混沌、混沌的同步及控制等⽅⾯。

本实验借助⾮线性电阻电路,从实验上对这⼀现象进⾏了探索。

四、正⽂:1.实验材料与设备装置。

⽰波器,可变电阻,定值电阻,直流电源,电流表,TL082CD运算放⼤器,线性电感,电容。

2.实验过程。

(1)实验电路图。

这是由两个线性电容C1、C2,⼀个线性电感L,和⼀个可变性电阻R0,⼀个⾮线性电阻R构成。

电感和C2并联构成振荡电路,线性电阻R0的作⽤是分相,⾮线性电阻R的伏安特性I R=g(u R),是⼀个分段线性负电阻,整体呈现对称但⾮线性的趋势。

由于g 总体是⾮线性函数,所以三元⾮线性⽅程组没有解析解。

南京理工大学电工电子综合实验

电工电子综合实验实验报告数字计时器设计姓名:学号:学院:自动化学院专业:自动化2013-9-6一、实验目的:1、掌握常见集成电路实现单元电路的设计过程。

2、了解各单元再次组合新单元的方法。

二、实验要求:实现0分0秒到59分59秒的可整点报时的数字计时器。

三、实验内容:1、设计实现信号源的单元电路。

2、设计实现0分0秒到59分59秒的计时单元电路。

3、设计实现快速校分单元电路,含防抖动电路。

4、加入任意时刻复位单元电路。

5、设计实现整点报时的单元电路。

四、实验所用元件及功能介绍元件型号数量NE555 1片CD4040 1片CD4518 2片CD4511 2片74LS00 3片74LS20 1片74LS21 3片74LS74 1片电容0.047uf 1个电阻1504个电阻1k1个电阻3k1个单字屏共阴极数码管2块蜂鸣器1个开关2个2、主要芯片引脚图及功能表2.2.1、CD4511译码器图2.2.1 CD4511译码器引脚图表2.2.1 CD4511译码器功能表输入输出LT BI LE D4 D3 D2 D1 g f e d c b a 字符测灯0 ×××××× 1 1 1 1 1 1 1 8 灭零 1 0 ×0 0 0 0 0 0 0 0 0 0 0 消隐锁存 1 1 1 ××××显示LE=0→1时数据译码1 1 0 0 0 0 0 0 1 1 1 1 1 1 0 1 1 0 0 0 0 1 0 0 0 0 1 1 0 1 1 1 0 0 0 1 0 1 0 1 1 0 1 1 2 1 1 0 0 0 1 1 1 0 0 1 1 1 1 3 1 1 0 0 1 0 0 1 1 0 0 1 1 0 4 1 1 0 0 1 0 1 1 1 0 1 1 0 1 5 1 1 0 0 1 1 0 1 1 1 1 1 0 0 6 1 1 0 0 1 1 1 0 0 0 0 1 1 1 7 1 1 0 1 0 0 0 1 1 1 1 1 1 1 8 1 1 0 1 0 0 1 1 1 0 0 1 1 1 92.2.2、CD4518计数器图2.2.2 CD4518BCD码计数器引脚图表2.2.2 CD4518BCD码计数器功能表:输入输出CR CP EN Q3 Q2 Q1 Q0 清零 1 ××0 0 0 0 计数0 ↑ 1 BCD码加法计数保持0 ×0 保持计数0 0 ↓BCD码加法计数保持0 1 ×保持2.2.3、CD4040分频器图2.2.3 CD4040分频器引脚图2.2.4、NE555定时器图2.2.2 NE555定时器引脚图表2.2.2 NE555定时器功能表Vi1(引脚6) Vi2(引脚2) VO(引脚3) (引脚4 )0 ××01 >2/3Vcc >1/3Vcc 01 <2/3 Vcc <1/3Vcc 11 <2/3 Vcc >1/3Vcc 不变2.2.5、74LS74 D触发器图2.2.5 74LS74D触发器引脚图表2.2.5 74LS74D触发器功能表输入输出CP D清零×0 1 ×0 1 置“1”× 1 0 × 1 0 送“0”↑ 1 1 0 0 1 送“1”↑ 1 1 1 1 0 保持0 1 1 ×保持不允许×0 0 ×不确定2.2.6、74LS00 双四与非门图2.2.6 74LS00双四与非门引脚图2.2.7、74LS20 四入双与非门图2.2.7 74LS20 四入双与非门引脚图2.2.8、74LS21四入双与门图2.2.8 74LS21四入双与门引脚图3、电子计时器设计原理3.1、各部分电路解析3. 1.1、脉冲发生电路脉冲发生电路即为电子计时器产生脉冲的电路,本文采用NE555振荡器和CD4040分频器产生实验所需要的脉冲信号频率其中:f0=1.44/[(R1+2R2)C]=4.38kHz R1=1KΩ,R2=3KΩ,C=0,047uF。

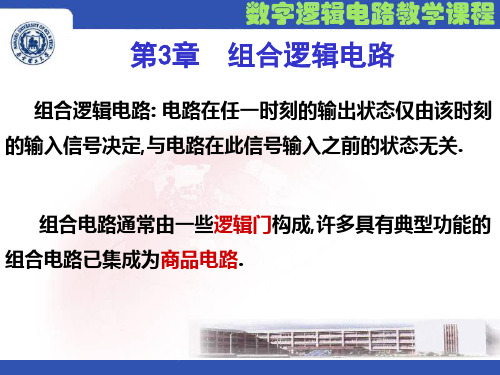

南京理工大学 数字电路课件

P

A

X B C Q 高位

0 1 2 3 4 5 6 7 0 1 2 3 4 5 6 7

≥1

F(Q,X,P)

F(Q,X,P)=m0+m1+m4+m6+m7

P

A

X B C Q 高位

&

F(Q,X,P)

F(Q,X,P)=m0m1m4m6m7

③ 利用高电平输出有效的译码器和或非门。 F(Q,X,P)=m2+m3+m5

74148为8线—3线优先编码器, 输入为低电平有效,输出 为3位二进制反码,HPRI是最高位优先编码器的说明.图 中: ST端为输入控制端,当ST=0时,电路处于正常工作状 态; 当ST=1时,电路禁止工作, Y2Y1Y0=111 .

YS:选通输出端.

YS=ST I0I1I2I3I4I5I6I7

A 0 0 0 0 1 1 1 1

B 0 0 1 1 0 0 1 1

C 0 1 0 1 0 1 0 1

F 0 0 0 1 0 1 1 1

(2) 化简、求最简函数表达式 BC 00 A 0 1

01

11

1

10

1

1

1

F=AB+AC+BC =AB· BC AC·

(3) 画电路图

F

&

&

&

&

A

B

C

例

设计一个两位二进制数比较器。

设计一个具有互相排斥输入条件的编码器. 输入: X0 、X1、X2 、X3 对应关系:

输入 X0 X1 X2 X3

输出:A1、A0

A1 A0 0 0 0 1 1 0 1 1

南京理工大学课程设计

课程设计报告——直流斩波电路设计姓名:闫耀程学号:0810190142指导老师:李强直流斩波电路的设计摘要:本文主要介绍的是直流斩波电路的设计,通过对直流源,控制电路,驱动电路和保护电路的设计完成整个直流斩波电路的设计。

关键词:直流斩波;控制;驱动;保护。

引言:直流斩波器(DC Chopper)又称为截波器,它是将电压值固定的直流电,转换为电压值可变的直流电源装置,是一种直流对直流的转换器(DC/DC Converter)已被被广泛使用,如直流电机之速度控制、交换式电源供应器(Switching-Power-Supply)等。

直流斩波是将固定的直流电压变换成可变的直流电压,也称为DC/DC变换。

斩波器的工作方式有两种,一是脉宽调制方式,Ts(周期)不变,改变Ton(通用,Ton为开关每次接通的时间),二是频率调制方式,Ton不变,改变Ts(易产生干扰)。

其具体的电路由以下几类:降压斩波器(Buck Chopper电路),其输出平均电压Uo小于输入电压Ui,输出电压与输入电压极性相同。

升压斩波器(Boost Chopper电路),其输出平均电压Uo大于输入电压Ui,输出电压与输入电压极性相同降压或升压斩波器(Buck-Boost Chopper电路)降压或升压斩波器(Cuk Chopper电路)Sepic斩波电路Zeta斩波电路,其中前两种是最基本的电路。

复合斩波电路——不同基本斩波电路组合多相多重斩波电路——相同结构基本斩波电路组合直流传动是斩波电路应用的传统领域,而开关电源则是斩波电路应用的新领域,前者的应用是逐渐萎缩,而后者的应用方兴未艾、欣欣向荣,是电力电子领域的一大热点。

用直流斩波器代替变阻器可节约电能(20~30)%。

直流斩波器不仅能起调压的作用(开关电源),同时还能起到有效地抑制电网侧谐波电流噪声的作用。

当今软开关技术使得DC/DC发生了质的飞跃,美国VICOR公司设计制造的多种ECI 软开关DC/DC变换器,其最大输出功率有300W、600W、800W等,相应的功率密度为(6、2、10、17)W/cm^3,效率为(80-90)%。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

南京理工大学电子线路课程设计实验报告摘要本次实验利用QuartusII7.0软件并采用DDS技术、FPGA芯片和D/A转换器,设计了一个直接数字频率信号合成器,具有频率控制、相位控制、测频、显示多种波形等功能。

并利用QuartusII7.0软件对电路进行了详细的仿真,同时通过SMART SOPC 实验箱和示波器对电路的实验结果进行验证。

报告分析了整个电路的工作原理,还分别说明了设计各子模块的方案和编辑、以及仿真的过程。

并且介绍了如何将各子模块联系起来,合并为总电路。

最后对实验过程中产生的问题提出自己的解决方法。

并叙述了本次实验的实验感受与收获。

关键词数字频率信号合成器频率控制相位控制测频示波器AbstractThis experient introduces using QuartusII7.0software, DDS technology,FPGA chip and D/A converter to design a multi—output waveform signal generator in which the frequency and phase are controllable and test frequency,display waveform.It also make the use of software QuartusII7.0 a detailed circuit simulation, and verify the circuit experimental results through SMART SOPC experiment box and the oscilloscope.The report analyzes the electric circuit principle of work,and also illustrates the design of each module and editing, simulation, and the process of using the waveform to testing each Sub module. Meanwhile,it describes how the modules together, combined for a total circuit. Finally the experimental problems arising in the process of present their solutions. And describes the experience and result of this experiment.Keywords multi—output waveform signal- generator frequency controllable phase controllable test frequency oscilloscope目录一、实验目的与要求 (4)二、电路工作原理 (4)三、子模块设计原理 (8)3.1 分频电路 (8)3.2频率预置和调节电路 (11)3.3累加寄存电路 (13)3.4相位控制电路 (15)3.5波形存储电路 (15)3.6测频电路 (18)3.7译码显示电路 (20)3.8波形选择电路 (22)3.9 节省ROM的设计 (23)3.10总电路 (25)3.11AM调制 (25)四、调试 (29)五、编程下载 (29)六、波形结果 (29)七、结论 (32)八、实验小结 (32)参考文献 (33)一.实验目的与要求本实验使用DDS的方法设计一个任意频率的正弦信号发生器,要求具有频率控制、相位控制、测频、切换波形,动态显示以及使能开关等功能。

利用Quartus II7.0完成设计、仿真等工作。

并利用SmartSOPC实验箱实现电路,用示波器观察输出波形。

基本要求如下:1、利用QuartusII软件和SmartSOPC实验箱实现DDS的设计。

2、DDS中的波形存储器模块用Altera公司的Cyclone系列FPGA 芯片中的RAM实现,RAM结构配置成4096×10类型。

3、具体参数要求:频率控制字K取4位;基准频率fc=1MHZ,由实验板上的系统时钟分频得到。

4、系统具有清零功能。

5、利用实验箱上的D/A转换器件将ROM输出的数字信号转换为模拟信号,能够通过示波器观察到输出波形。

6、通过开关(实验箱上的Ki)输入DDS的频率和相位控制字,并能用示波器观察加以验证。

提高部分要求:1、通过按键(实验箱上的Si)输入DDS的频率和相位控制字,以扩大频率控制和相位控制的范围;(注意:按键后有消颤电路)2、能够同时输出正余弦两路正交信号;3、在数码管上显示生成的波形频率;4、充分考虑ROM结构及正弦函数的特点,进行合理的配置,提高计算精度;5、设计能输出多种波形(三角波、锯齿波、方波等)的多功能波形发生器;6、在DDS的基础上,完成AM调制;二.电路工作原理(1)DDS概念直接数字频率合成器(Direct Digital Frequency Synthesizer)是一种基于全数字技术,从相位概念出发直接合成所需波形的一种频率合成技术。

(2)DDS的组成及工作原理频率预置与调节电路作用:实现频率控制量的输入;不变量K被称为相位增量,也叫频率控制字。

累加器相位累加器的组成= N位加法器+N位寄存器;相位累加器的作用:在时钟的作用下,进行相位累加。

应注意:当相位累加器累加满量时就会产生一次溢出,完成一个周期性的动作。

DDS的输出频率为:f0=fCK/2N ;DDS输出的最低频率:K=1时,fC/2NDDS输出的最高频率:Nyquist采样定理决定,即fC/2;K的最大值为2N-1结论:只要N足够大,DDS可以得到很细的频率间隔。

要改变DDS的输出频率,只要改变频率控制字K即可。

\ 波形存储器作用:进行波形的相位—幅值转换。

原理:ROM的N位地址把0O—360O的正弦角度离散成具有2N个样值的序列ROM的D位数据位把2N个样值的幅值量化为D位二进制数据(有符号数)D/A转换器D/A转换器的作用:把已经合成的正弦波的数字量转换成模拟量。

低通滤波器D/A转换器的作用:滤除生成的阶梯形正弦波中的高频成分,将其变成光滑的正弦波。

时钟脉冲发生电路模块提供电路各模块工作所需要的时钟脉冲;本次设计的电路需要将振荡源提供的48MHZ的脉冲频率分为:1MHz,1KHz,1Hz,0.5Hz。

显示电路:显示电路输出波形的频率以及频率和相位控制字。

测频模块:测试电路输出的各种信号的频率。

ROM模块预先存储了正弦波与余弦波以及三角波,锯齿波,方波等的二进制幅值且存储单元有212=4096,每个单元存储的幅值大小用10位二进制数来表示。

频率和相位均可控制的具有正弦和余弦输出的DDS核心单元电路示意图如下图所示:每来一个CLOCK,加法器就将频率控制字fwrod与累加寄存器输出的累加相位数据相加,相加的结果又反馈送至累加寄存器的数据输入端,以使加法器在下一个时钟脉冲的作用下继续与频率控制字相加。

这样,相位累加器在时钟作用下,不断对频率控制字进行线性相位累加。

由此,相位累加器在每一个时钟脉冲输入时,把频率控制字累加以此,相位累加器输出的数据作为波形存储器的相位取样地址,这样就可把存储在波形存储器内的波形抽样值进行找表查出,完成相位到幅值的转换。

由于相位累加器为N 位,相当于把正弦信号在相位上的精度定为N 位,所以分辨率为1/2N 。

若系统时钟频率为f c ,频率控制字fword 为1,则输出频率为f OUT =f C /2N ,这个频率相当于"基频"。

若fword 为K ,则输出频率为:f out =K* f C /2N当系统输入时钟频率f C 不变时,输出信号的频率由频率控制字K 所决定。

由上式可得:K=2N *f out /f C ,其中,K 为频率字,注意K 要取整,会有误差。

三、各子模块设计3.1分频电路本实验中使用的 SmartSOPC 实验系统给出的振荡频率源为 48MHz ,因此我们需要使用分频电路得到作为直接数字频率合成器电路所使用的各种频率脉冲。

累加器电路中的寄存时钟信号、 ROM 的 CLOCK 使用 1MHz 脉冲频率 ,动态译码显示电路使用 1KHz 脉冲频率,频率、相位控制电路、模16电路使用 1Hz 脉冲频率,测频电路使0.5Hz 。

所以我们进行如下电路的设计:(1)2分频电路二分频电路由一个D 触发器构成,原理图如下:二分频器仿真波形如下图:(2)48分频电路3分频电路由74160构成一个模3计数器,原理图如下:8分频电路由三个2分频电路串联而成,24分频电路由3分频器和8分频器串联而成,48分频电路由24分频器和2分频器串联而成,原理图如下:48分频电路仿真波形如下:(3)1000分频电路10分频电路由74163构成一个模10计数器,并实现占空比为50%,原理图如下:10分频电路仿真波形如下:1000分频电路由三个10分频器串联而成,原理图如下:(4)脉冲发生总图封装如下:封装图各引脚说明:Input:48MHZ:接时钟信号输入端(即48MHZ)output:1/2HZ:引出0.5HZ信号1HZ:引出1HZ信号1KHZ:引出1000HZ信号1MHZ:引出1MHZ信号3.2频率预置和调节电路频率预置与调节电路由1片模16的74161计数器组成,1Hz信号输入让其变化。

该模块有清零和保持端,通过开关控制,以便计数到需要值时保持或清零。

频率频率预置与调节电路实现频率控制量(步长)的输入。

其中,K被称为相位增量,也叫频率控制字。

DDS的输出频率表达式为fout=K*fc/2N,当K=1时,DDS输出最低频率为fc/2N,而DDS的最高输出频率由Nyquist采样定理决定,即fc/2,也就是说K的最大值为2N-1。

电路图如下:仿真波形如下:封装如下:封装图各引脚说明:Input:baochi:接保持开关qingling:接清零开关1hz:接1hz脉冲output:k[3..0]:计数器的输出3.3累加寄存电路相位累加器结构图如下图所示:相位累加器由12位加法器与12位寄存器级联构成。

每来一个时钟脉冲,加法器将频率控制字K与寄存器输出的累加相位数据相加,再把相加后的结果送至寄存器的数据输入端。

寄存器将加法器的上一个时钟作用后所产生的相位数据反馈至加法器的输入端,以使加法器在下一个时钟作用下继续与频率控制字进行相加。

这样,相位累加器在时钟作用下,进行相位累加。

当相位累加器累加满量时就会产生一次溢出,完成一个周期性的动作。