数字电子技术考试题及答案

数字电子技术考试题及答案

数字电子技术考试题及答案一、选择题(每题2分,共20分)1. 以下哪个不是数字电子技术中的基本逻辑门?A. 与门(AND)B. 或门(OR)C. 非门(NOT)D. 异或门(XOR)答案:C2. 在数字电路中,一个触发器的稳定状态是指:A. 触发器输出为高电平B. 触发器输出为低电平C. 触发器输出不随输入变化而变化D. 触发器输出随输入变化而变化答案:C3. 以下哪个不是数字电子技术中的计数器类型?A. 二进制计数器B. 十进制计数器C. 十六进制计数器D. 以上都是答案:D4. 在数字电路设计中,以下哪个不是常用的时序逻辑元件?A. 寄存器B. 计数器C. 译码器D. 触发器答案:C5. 以下哪个不是数字电路的分类?A. 组合逻辑电路B. 时序逻辑电路C. 模拟电路D. 混合电路答案:C6. 一个简单的数字电子系统通常包括哪些基本部分?A. 输入、处理、输出B. 电源、输入、输出C. 输入、存储、输出D. 电源、输入、处理、输出答案:D7. 以下哪个不是数字电子技术中常用的存储元件?A. 触发器B. 寄存器C. 锁存器D. 放大器答案:D8. 在数字电子技术中,一个信号的上升时间是指:A. 信号从0%到90%的最大值所需的时间B. 信号从10%到90%的最大值所需的时间C. 信号从0%到100%的最大值所需的时间D. 信号从10%到100%的最大值所需的时间答案:A9. 以下哪个是数字电子技术中的同步电路的特点?A. 所有触发器的时钟信号是独立的B. 所有触发器的时钟信号是同步的C. 电路中没有时钟信号D. 电路中只有一个触发器答案:B10. 在数字电子技术中,以下哪个不是布尔代数的基本运算?A. 与(AND)B. 或(OR)C. 非(NOT)D. 除(DIV)答案:D二、填空题(每空2分,共20分)11. 在数字电路中,逻辑“1”通常表示电压为______,逻辑“0”通常表示电压为______。

数字电子技术试题及参考答案

数字电子技术试题及参考答案数字电子技术试题及参考答案(第三版)《数字电子技术》试卷姓名:__ _______ 班级:__________ 考号:___________ 成绩:____________ 本试卷共 6 页,满分100 分;考试时间:90 分钟;考试方式:闭卷1. 有一数码10010011,作为自然二进制数时,它相当于十进制数( 147 ),作为8421BCD 码时,它相当于十进制数( 93 )。

2.三态门电路的输出有高电平、低电平和(高阻态)3种状态。

3.TTL与非门多余的输入端应接(高)。

4.TTL 集成JK 触发器正常工作时,其Rd 和Sd 端应接(低)电平。

5. 已知某函数 ))((________________------+++=D C AB D C A B F ,该函数的反函数___F =()6. 如果对键盘上108个符号进行二进制编码,则至少要( 7 )位二进制数码。

7 . 典型的TTL 与非门电路使用的电路为电源电压为( 5 )V ,其输出高电平为( 3.6 )V ,输出低电平为( 0.35 )V , CMOS 电路的电源电压为( 3 —— 18 ) V 。

8.74LS138是3线—8线译码器,译码为输出低电平有效,若输入为A2A1A0=110时,输出____________________________1234567YYYYYYYY应为()。

9.将一个包含有32768个基本存储单元的存储电路设计16位为一个字节的ROM。

该ROM有(11 )根地址线,有(16 )根数据读出线。

10. 两片中规模集成电路10进制计数器串联后,最大计数容量为( 8 )位。

11 .Y3 =( A < B )。

12 . 某计数器的输出波形如图1所示,该计数器是(八)进制计数器。

13 .驱动共阳极七段数码管的译码器的输出电平为()有效。

二、单项选择题(本大题共15小题,每小题2分,共30分)(在每小题列出的四个备选项中只有一个是最符合题目要求的,请将其代码填写在题后的括号内。

数字电子技术测试试卷与答案精选全文完整版

可编辑修改精选全文完整版附录D 模拟试卷及参考答案D.1 模拟试卷一、填空(共10小题,每空2分,共40分)1、(8C.4)16 = ( )10 =( )8=( )2421BCD 。

2、将160个字符用二进制编码,至少需要( )位二进制码。

3、已知F =A(B +C)+A +C ,则其对偶式为( );其反函数为( )。

(直接用对偶规则和反演规则)。

4、已知TTL 与非门参数V CC =+5V ,U OH =3.6V ,U OL =0.4V ,U OFF =1.1V ,U ON =1.4V ,高电平输入时的抗干扰容限U NH 为( )。

5、连续异或1999个“1”的结果是( )。

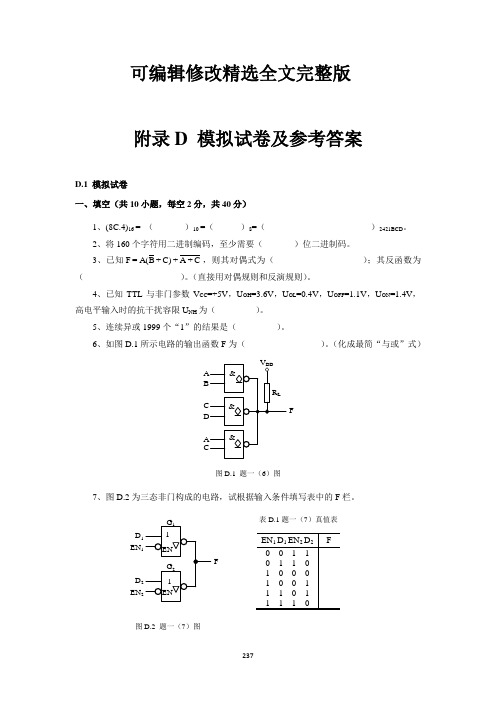

6、如图D.1所示电路的输出函数F 为( )。

(化成最简“与或”式)F图D.1 题一(6)图7、图D.2为三态非门构成的电路,试根据输入条件填写表中的F 栏。

图D.2 题一(7)图表D.1题一(7)真值表D 1EN 1D 2EN 2F8、设计模值为61的自然二进制码计数器、十进制计数器和余3 BCD码计数器分别需要()级、()级和()级触发器。

一个五位二进制加法计数器,由00000状态开始,问经过109个输入脉冲后,此计数器的状态为()。

9、用()片1024×4位的RAM可组成8K×8位的RAM,需要增加()条地址线、()条数据线。

10、在10位的倒T型电阻网络D/A转换器中,若U REF = ─10V,该D/A转换器能分辨的最小输出电压U LSB=()mV。

二、选择题(共10小题,每小题2分,共20分)1、有符号位二进制数的补码为(10011),则对应的十进制数为()。

A、-29B、+13C、-13D、-32、下列说法正确的是()。

A、n个变量所构成的全部最小项之和恒等于0B、n个变量所构成的全部最大项之和恒等于0C、n个变量所构成的全部最小项之积恒等于1D、n个变量所构成的全部最大项之积恒等于03、下列说法正确的是()。

数字电子技术试卷和答案

数字电子技术试卷(1)一.填空(16)1.十进制数123的二进制数是 1111011 ;十六进制数是 7B 。

2.100001100001是8421BCD 码,其十进制为 861 。

3.逻辑代数的三种基本运算是 与 , 或 和 非 。

4.三态门的工作状态是 0 , 1 , 高阻 。

5.描述触发器逻辑功能的方法有 真值表,逻辑图,逻辑表达式,卡诺图,波形图 。

6.施密特触发器的主要应用是 波形的整形 。

7.设4位D/A 转换器的满度输出电压位30伏,则输入数字量为1010时的输出模拟电压为。

8.实现A/D 转换的主要方法有 , , 。

二.判断题(10)1.BCD 码即8421码 ( 错 )2.八位二进制数可以表示256种不同状态。

( 对 )3.TTL 与非门与CMOS 与非门的逻辑功能不一样。

( )4.多个三态门的输出端相连于一总线上,使用时须只让一个三态门传送信号,其他门处于高阻状态。

(对 )5.计数器可作分频器。

( 对 )三.化简逻辑函数(14)1.用公式法化简--+++=A D DCE BD B A Y ,化为最简与或表达式。

解;D B A Y +=-2.用卡诺图化简∑∑=m d D C B A Y ),,,,()+,,,,(84210107653),,,(,化为最简与或表达式。

四.电路如图1所示,要求写出输出函数表达式,并说出其逻辑功能。

(15)解;C B A Y ⊕⊕=, C B A AB C )(1++=,全加器,Y 为和,1C 为进位。

五.触发器电路如图2(a ),(b )所示,⑴写出触发器的次态方程; ⑵对应给定波形画出Q 端波形(设初态Q =0)(15)解;(1)AQ Q Q n +=-+1,(2)、A Q n =+1 六.试用触发器和门电路设计一个同步的五进制计数器。

(15)七.用集成电路定时器555所构成的自激多谐振荡器电路如图3所示,试画出V O ,V C 的工作波形,并求出振荡频率。

《数字电子技术》习题及答案

第1章 数制和码制 一、填空题1.数制转换:(011010)2 =( )10 =( )8 =( )16。

2.数制转换:(35)10 =( )2 =( )8 =( )16。

3.数制转换:(251)8 =( )2 =( )16 =( )10。

4.数制转换:(4B )16 =( )2 =( )8 =( )10。

5.数制转换:(69)10 =( )2 =( )16 =( )8。

6.将二进制数转换为等值的八进制和十六进制数 (10011011001)2 =( )8 =( )16。

7.将二进制数转换为等值的八进制和十六进制数 (1001010.011001)2 =( )8 =( )16。

一、填空题答案: 1.26、32、1A ; 2.100011、43、 23; 3.10101001、A9、169; 4.1001011、113、75; 5.1000101、45、105; 6.2331、4D9; 7.112.31、4A.64。

第2章 逻辑代数基础 一、填空题1.逻辑函数Y AB A B ''=+,将其变换为与非-与非形式为 。

2.逻辑函数Y A B AB C ''=+,将其变换为与非-与非形式为 。

3. 将逻辑函数AC BC AB Y ++=化为与非-与非的形式,为 。

4.逻辑函数Y A A BC '''=+,化简后的最简表达式为 。

5.逻辑函数Y A B A B ''=++,化简后的最简表达式为 。

6.逻辑函数()()Y A BC AB ''''=+,化简后的最简表达式为 。

7. 逻辑函数Y AB AB A B ''=++,化简后的最简表达式为 。

一、填空题答案1.()()()Y AB A B '''''= ; 2.()()()Y A B AB C '''''=; 3. ()()()()Y AB BC AC ''''=; 4. Y A '=; 5.1Y =; 6.1Y =; 7.Y A B =+。

数字电子技术试卷及答案打印版.doc

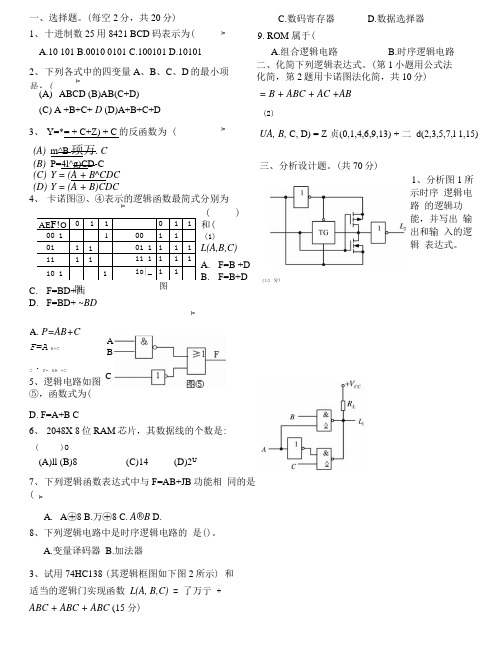

)oAE F!O 0 1 10 1 1 00 1 1 00 11011 101 1 1 1 1 11 1 111 1 1 1 1 10 1 1 io|_ 1 1(10 分)A. P=AB+CF=A B+CC・F= AB +C(A) ABCD (B)AB(C+D) (C) A +B+C+ D (D)A+B+C+D3、 Y=*= + C+Z) + C 的反函数为 ((A) m^B 顼万. C (B) P=4l^g)CD-C (C) Y = (A + B^CDC (D) Y = (A + B)CDC4、 卡诺图③、④表示的逻辑函数最简式分别为 ( )和( (1) L(A,B,C) = B + ABC + AC +AB(2)UA, B, C, D) = Z 贞(0,1,4,6,9,13) + 二 d(2,3,5,7,l 1,15)三、分析设计题。

(共70分) 1、分析图1 所示时序 逻辑电路 的逻辑功 能,并写出 输出和输 入的逻辑 表达式。

A. F=B +DB. F=B+DC. F=BD+西D. F=BD+ ~BD 5、逻辑电路如图⑤,函数式为(D. F=A+B C6、 2048X 8位RAM 芯片,其数据线的个数是:()O(A)ll (B)8 (C)14(D)2U7、 下列逻辑函数表达式中与F=AB+JB 功能相 同的是( )oA. A ㊉8B.万㊉8C. A®BD.8、下列逻辑电路中是时序逻辑电路的 是()。

A.变量译码器 B.加法器3、试用74HC138 (其逻辑框图如下图2所示) 和适当的逻辑门实现函数 L(A, B,C) = 了万亍 +ABC + ABC + ABC (15 分)一、选择题。

(每空2分,共20分) 1、 十进制数25用8421 BCD 码表示为( A.10 101 B.0010 0101 C.100101 D.101012、 下列各式中的四变量A 、B 、C 、D 的最小项 是:(C.数码寄存器D.数据选择器)o)o9. ROM 属于(A.组合逻辑电路 二、化简下列逻辑表达式。

数字电子技术习题及答案

第一章 数字逻辑基础1-1. 将下列的二进制数转换成十进制数(1)、1011,(2)、10101,(3)、11111,(4)、1000011-2. 将下列的十进制数转换成二进制数(1)、8,(2)、27,(3)、31,(4)、1001-3. 完成下列的数制转换(1)、(255)10=( )2=( )16=( )8421BCD(2)、(11010)2=( )16=( )10=( )8421BCD(3)、(3FF )16=( )2=( )10=( )8421BCD(4)、(1000 0011 0111)8421BCD =()10=()2=()161-4. 完成下列二进制的算术运算(1)、1011+111,(2)、1000-11,(3)、1101×101,(4)、1100÷100 1-5. 设:AB Y 1=,B A Y 1+=,B A Y 1⊕=。

已知A 、B 的波形如图题1-5所示。

试画出Y 1、Y 2、Y 3对应A 、B 的波形。

图题1-51-6选择题1.以下代码中为无权码的为 。

A . 8421BCD 码B . 5421BCD 码C . 余三码D . 格雷码2.以下代码中为恒权码的为 。

A .8421BCD 码B . 5421BCD 码C . 余三码D . 格雷码3.一位十六进制数可以用 位二进制数来表示。

A . 1B . 2C . 4D . 164.十进制数25用8421BCD码表示为。

A.10 101B.0010 0101C.100101D.101015.在一个8位的存储单元中,能够存储的最大无符号整数是。

A.(256)10B.(127)10C.(FF)16D.(255)106.与十进制数(53.5)10等值的数或代码为。

A.(0101 0011.0101)8421BCDB.(35.8)16C.(110101.1)2D.(65.4)87.矩形脉冲信号的参数有。

A.周期B.占空比C.脉宽D.扫描期8.与八进制数(47.3)8等值的数为:A. (100111.011)2B.(27.6)16C.(27.3 )16D. (100111.11)29. 常用的BCD码有。

数字电子技术试卷及答案五套

数字电子技术试卷一、选择题:A组:1.如果采用偶校验方式,下列接收端收到的校验码中,( A )是不正确的A、00100B、10100C、11011D、111102、某一逻辑函数真值表确定后,下面描述该函数功能的方法中,具有唯一性的是(B)A、逻辑函数的最简与或式B、逻辑函数的最小项之和C、逻辑函数的最简或与式D、逻辑函数的最大项之和3、在下列逻辑电路中,不是组合逻辑电路的是(D)A、译码器B、编码器C、全加器D、寄存器4、下列触发器中没有约束条件的是(D)A、基本RS触发器B、主从RS触发器C、同步RS触发器D、边沿D触发器5、555定时器不可以组成D。

A.多谐振荡器B.单稳态触发器C.施密特触发器D.J K触发器6、编码器(A)优先编码功能,因而(C)多个输入端同时为1。

A、有B、无C、允许D、不允许7、(D)触发器可以构成移位寄存器。

A、基本RS触发器B、主从RS触发器C、同步RS触发器D、边沿D触发器8、速度最快的A/D转换器是(A)电路A、并行比较型B、串行比较型C、并-串行比较型D、逐次比较型9、某触发器的状态转换图如图所示,该触发器应是( C )A. J-K触发器B. R-S触发器C. D触发器D. T触发器10.(电子专业作)对于VHDL以下几种说法错误的是(A )A VHDL程序中是区分大小写的。

B 一个完整的VHDL程序总是由库说明部分、实体和结构体等三部分构成C VHDL程序中的实体部分是对元件和外部电路之间的接口进行的描述,可以看成是定义元件的引脚D 结构体是描述元件内部的结构和逻辑功能B组:1、微型计算机和数字电子设备中最常采用的数制是--------------------------------( A )A.二进制B.八进制C. 十进制D.十六进制2、十进制数6在8421BCD码中表示为-------------------------------------------------( B )A.0101B.0110C. 0111D. 10003、在图1所示电路中,使__AY 的电路是---------------------------------------------( A )A. ○1B. ○2C. ○3D. ○44、接通电源电压就能输出矩形脉冲的电路是------------------------------------------( D )A. 单稳态触发器B. 施密特触发器C. D触发器D. 多谐振荡器5、多谐振荡器有-------------------------------------------------------------------------------( C )A. 两个稳态B. 一个稳态C. 没有稳态D. 不能确定6、已知输入A、B和输出Y的波形如下图所示,则对应的逻辑门电路是-------( D )A. 与门B. 与非门C. 或非门D. 异或门7、下列电路中属于时序逻辑电路的是------------------------------------------------------( B )A. 编码器B. 计数器C. 译码器D. 数据选择器8、在某些情况下,使组合逻辑电路产生了竞争与冒险,这是由于信号的---------( A )A. 延迟B. 超前C. 突变D. 放大9、下列哪种触发器可以方便地将所加数据存入触发器,适用于数据存储类型的时序电路--------------------------------------------------------------------------------( C )A. RS触发器B. JK触发器C. D触发器D. T触发器10、电路和波形如下图,正确输出的波形是-----------------------------------------------( A )A. ○1B. ○2C. ○3D. ○4C组:1.十进制数25用8421BCD码表示为 B 。

数字电路试题五套(含答案)

《数字电子技术》试卷一一、 填空(每空1分,共25分)1、(10110)2=( )10=( )16(28)10=( )2=( )16 (56)10=( )8421BCD2、最基本的门电路是: 、 、 。

3、有N 个变量组成的最小项有 个。

4、基本RS 触发器的特征方程为_______ ,约束条件是 __.5、若存储器的容量是256×4RAM,该RAM 有 ___存储单元,有 字,字长_____位,地址线 根。

6、用N 位移位寄存器构成的扭环形计数器的模是________.7、若令JK 触发器的J=K=T 则构成的触发器为_______.8、如图所示,Y= 。

9、如图所示逻辑电路的输出Y= 。

10、已知Y=D AC BC B A ++,则Y = ,Y/= 。

11、组合逻辑电路的特点是_________、___________;与组合逻辑电路相比,时序逻辑电路的输出不仅仅取决于此刻的_______;还与电路 有关。

二、 化简(每小题5分,共20分)1、公式法化简(1)Y=ABC ABC BC BC A ++++=+++(2)Y ABC A B C2、用卡诺图法化简下列逻辑函数=+++(1)Y BCD BC ACD ABDY=∑+∑(2)(1,3,4,9,11,12,14,15)(5,6,7,13)m d三、设下列各触发器初始状态为0,试画出在CP作用下触发器的输出波形(10分)四、用74LS161四位二进制计数器实现十进制计数器(15分)五、某汽车驾驶员培训班结业考试,有三名评判员,其中A 为主评判员,B 、C 为副评判员,评判时,按照少数服从多数原则,但若主评判员认为合格也可以通过。

试用74LS138和与非门实现此功能的逻辑电路。

(15分)P Q A Q B Q C Q D C T 74LS161 LD CPQ A 、Q B 、Q C 、Q D :数据输出端; A 、B 、C 、D :数据输入端; P 、T :计数选通端;r C :异步复位端;CP :时钟控制输入端;D L :同步并置数控制端;六、试分析如图电路的逻辑功能,设各触发器的初始状态为0(15分)《数字电子技术》试卷一参考答案一、填空(每空1分,共25分)1、10(22)、16(16);2(11100)、16(1)C ;8421(01010110)BCD 。

数字电子技术试卷及答案

第1页(共10页) 第2页(共10页)DC B AD C A B ++一、填空题(每空1分,共20分)1。

有一数码10010011,作为自然二进制数时,它相当于十进制数(147),作为8421BCD 码时,它相当于十进制数(93)。

2.三态门电路的输出有高电平、低电平和(高阻)3种状态。

3.TTL 与非门多余的输入端应接(高电平或悬空)。

4.TTL 集成JK 触发器正常工作时,其d R 和d S 端应接(高)电平。

5。

已知某函数⎪⎭⎫ ⎝⎛+⎪⎭⎫ ⎝⎛++=D C AB D C A B F ,该函数的反函数F = 6. 如果对键盘上108个符号进行二进制编码,则至少要(7)位二进制数码。

7。

典型的TTL 与非门电路使用的电路为电源电压为(5)V,其输出高电平为(3.6)V ,输出低电平为(0。

35)V, CMOS 电路的电源电压为(3-18) V 。

8.74LS138是3线-8线译码器,译码为输出低电平有效,若输入为A 2A 1A 0=110时,输出 01234567Y Y Y Y Y Y Y Y 应为(10111111)。

9.将一个包含有32768个基本存储单元的存储电路设计16位为一个字节的ROM 。

该ROM 有(11)根地址线,有(16)根数据读出线。

10。

两片中规模集成电路10进制计数器串联后,最大计数容量为(100)位。

11。

下图所示电路中, Y 1=(AB );Y 2 =(AB+AB );Y 3 =(AB ).12. 某计数器的输出波形如图1所示,该计数器是(5)进制计数器。

13.驱动共阳极七段数码管的译码器的输出电平为(低)有效。

1.逻辑函数有四种表示方法,它们分别是(真值表、)、(逻辑图式)、(逻辑表达 )和(卡诺图).2.将2004个“1”异或起来得到的结果是(0).3.由555定时器构成的三种电路中,(施密特触发器和单稳态触发器)是脉冲的整形电路。

4.TTL 器件输入脚悬空相当于输入(高)电平。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

太原科技大学

数字电子技术 课程试卷 B 卷

一、单选题(20分,每小题1分)请将本题答案全部写在下表中

1、8421BCD 码10000001转化为十六进制数是( )。

A 、15

B 、51

C 、81

D 、18 2、n 位二进制数的反码或其原码,表示的十进制数是( )。

A 、21n

- B 、2n C 、1

2n - D 、2n

3、TTL 与非门多余输入端的处理是( )。

A 、接低电平

B 、任意

C 、 通过 100电阻接地

D 、通过 100k

电阻接地

4、OD 非门在输入为低电平(输出端悬空)情况下,输出为( )状态。

A 、高电平 B 、低电平 C 、开路 D 、不确定

5、与()Y A B A 相等的逻辑函数为( )。

A 、Y

B B 、Y A

C 、Y A B

D 、Y A B

6、下列(,,)F A B C 函数的真值表中1Y 最少的为( )。

A 、Y C =

B 、Y AB

C = C 、Y AB C =+

D 、Y BC C =+ 7、( )是组合逻辑电路的特点。

A 、输出仅取决于该时刻的输入

B 、后级门的输出连接前级门的输入

C 、具有存储功能

D 、由触发器构成 8、半加器的两个加数为A 和B ,( )是进位输出的表达式。

A 、AB B 、A B C 、AB D 、AB

9、欲使JK 触发器1

n Q Q ,J 和K 取值正确的是( )。

A 、,J

Q K Q B 、J K Q C 、0J K D 、,1J Q K

10、字数为128的ROM 存储器存储容量为1204位,字长为( )位,地址线为( )根。

A 、8,8 B 、8,7 C 、4,7 D 、4,8

11、一个四位二进制减法计数器初始状态为0110,经过101个脉冲有效沿触发后,它的输出是 ( )。

A 、0000 B 、0001 C 、0011 D 、0010 12、要用1K×8的RAM 扩展成8K×16的RAM ,需选用( )译码器。

A 、 3线-8线

B 、2线-4线

C 、1线-2线

D 、4线-16线

13、施密特触发器可以把( )波形变换成( )波形。

A 、正弦,三角

B 、矩形,三角

C 、三角,方波

D 、正弦,矩形

14、555定时器可以组成的多谐振荡器,Vcc=9V ,则电容器电压Uc 最大为( ),可以通过改变( )改变Uc 的大小。

A 、6V ,充电回路电阻、电容值 B 、3V ,充电回路电阻、电容值 C 、6V ,Vcc D 、3V ,Vcc 15、八位的逐次比较式A/D 转换器完成一次转换的时间为0.08 s ,其时钟信号频率( )Hz A .60 B .80 C .100 D .120 二、化简题(10分,每小题5分)要求有详细的解题步骤

1、用公式法将函数式1F 化简为最简与或式;

2、用卡诺图化简法化简2F

1()()()F ABCD AB AB C AD BC =++

(2分)

三、(10分)判断图题3所示各电路为TTL 或CMOS 结构时的输出是高电平还是低电平,并将结果填入表 题3中。

=1

V 50K Ω500IH V Ω

50k V Y

2

Y

34

5

(a)

(b)(d)(c)

图 题3.1

V

V V (e)

1

100k Ω

表 题3.1

四、(10分)M 为三位二进制数,设计一个具有数据范围指示功能的组合逻辑电路,使之能区分下列三种情况:①0≤M ≤2;②3≤M ≤5;③6≤M ≤7;设构成M 的三位二进制数分别为A 、B 、C ,其中A 为高位,C 为地位;对应与①、②、③三种情况的输出为X 、Y 、Z ,且高电平(逻辑“1”)代表M 在范围内。

要求: 1、根据题目要求进行逻辑抽象,列写逻辑真值表和函数式;

2、在图 题4.1中用3线-8线译码器74LS138实现逻辑函数。

解:1、逻辑真值表如表 题4.1所示(2分);函数式为下式。

2、74LS138实现逻辑函数如图 题4.1所示。

(5分)

,,X

ABC ABC ABC Y ABC ABC ABC Z ABC ABC (3分)

()()()()(2)

()0(3)

ABC ABC AD BC ABC AD BC ABC AD BC ABCD ABC ABC

=++=+++=++=分分2(,,,)(0,1,2,8,10,12,13,14,15)

F A B C D m AB BD ABC

==++∑(3分)

F 2

表 题4.1

五、(15分)写出如图2所示电路的驱动方程、状态方程、输出方程、状态表和状态图,并按照所给波形画出输出端Y 的波形(Q

初值为0),并说明是何种状态机(摩尔、梅里)。

A

图 题5.1

A Q 图 题5.2

Y

表 题5.2 解:驱动方程:J K A Q ==⊕(2分) 状态方程:1

n Q

A Q Q +=⊕⊕(2分)

输出方程Y Q A =+(2分) 梅里型(2分)

状态表如表题5.2所示:(2分)

状态图如图题5.3所示。

(2分)输出的波形图如图题5.2所示。

(3分。

Q : 2分;Y : 1分)

六、(10分)试用JK 触发器设计一个同步2位二进制(四进制)加法计数器。

要求画出状态图、列写状态表、写出驱动方程并在图题6.1中完成逻辑图。

表 题6.1

Q 1Q 0

图 题6.2

图 题6.1

CLK

图 题5.3图题4.1

74LS138

解:状态图如图题6.2所示(2分);状态表如表题6.1所示(2分); 驱动方程为1

1

110

100101011022

,(2),1(2)

n

n

Q Q Q Q Q Q Q Q Q Q J K Q J K 分分;逻辑图如图题6.1所示(2分)。

七、(10分)试说明图题7.1所示由十进制计数器74LS160(异步清零,同步置数功能)构成的计数器为多少进制,为同步级联还是异步级联方式?试使用两片16进制计数器74LS161(异步清零,同步置数功能)采用异步级联、整体清零法组成相同进制数的计数器,设计数器初始状态Q D Q C Q B Q A =0000。

图 题7.1

解:图题7.1为21进制计数器(3分),采用的是同步级联方式(2分);用74LS161实现相同的进制数如图题7.2所示。

(5分)

图 题7.2

八、(20分)电路如图 题8.1所示,要求做如下分析计算:

1、试计算定时器555的输出信号的周期T 1为多少ms (小数点后保留1位)?(2分)

2、根据图 题8.2所示定时器555的输出信号CLK 的波形画出74LS160的Q B 输出端的波形,并确定其周期T 。

(3分);

3、试确定74LS161组成的计数器是多少进制(2分),并画出其状态图;(2分)

4、通过查表

题8.1ROM 地址和数据对应表,计算出图 题8.1中74LS161构成的计数器每一个输出状态所对应的DAC0832的输出电压值(V REF =−2.56V );(3分)

5、在图 题8.3中按照横纵坐标单位标注横纵坐标值(2分),画出输出V o 的波形(3分)图并确定其周期(3分)。

(两个计数器初始状态均为Q D Q C Q B Q A =0000)。

Q 图 题8.2

表题7.1

74LS160

74LS161

功能表

2.22.2k k 图 题8.1

表 题8.1

解:1、312

112(2)ln 244103300100.690.1T R R C ms -=+=⨯⨯⨯⨯=

2、Q B 波形如图题8.2所示。

T=4 T 1=0.4ms

3、74LS161组成的计数器是11进制;状态图如图题8.3所示。

4、计

数器状

态与输出电压分为:

32108888888(1)22.56

00000000(0)022.56

00010001(1)1022.56

00100011(3)3022.56

00110111(7)7022.56

01001111(15)15022.56

01011111(15)15022.56

01101111(15)152D C B A O O O O O O O Q Q Q Q D D D D V V V mV

V mV

V mV

V mV

V mV

V =

=============分(分)888802.56

01111111(15)15022.56

1000

0111(7)7022.56

1001

0011(3)3022.56

1010

0001

(1)102O O O O mV

V mV

V mV

V mV

V mV

========

5、图形如图题8.4所示,波形周期为4.4ms

ms 图题8.4

图题8.3。