竞赛抢答器设计报告

抢答器设计实验报告

抢答器设计实验报告抢答器设计实验报告一、引言在现代教育中,互动性和参与度是学生学习的重要因素。

为了提高课堂的活跃程度和学生的参与度,我们设计了一种抢答器。

本实验报告将介绍抢答器的设计原理、实验过程和结果分析。

二、设计原理抢答器的设计基于无线电频率识别技术。

抢答器由两部分组成:主机和抢答器设备。

主机通过无线电频率识别技术与抢答器设备进行通信,实现答题者的抢答功能。

三、实验过程1. 材料准备我们准备了一台电脑、一块Arduino开发板、一块无线电频率识别模块、若干个按钮开关和一些导线。

2. 硬件连接我们将Arduino开发板与无线电频率识别模块通过导线连接,并将按钮开关分别连接到Arduino开发板上。

3. 软件编程我们使用Arduino开发环境编写了控制程序。

程序主要实现了无线电频率识别模块的初始化、按钮开关的状态检测和与主机的通信功能。

4. 抢答器设备制作我们将按钮开关固定在一个小盒子上,连接好导线,并将无线电频率识别模块放置在盒子内。

5. 实验验证我们进行了一系列实验来验证抢答器的功能。

首先,我们将主机与抢答器设备进行配对。

然后,我们进行了多次抢答实验,记录了每个学生的抢答时间和正确率。

四、结果分析通过实验,我们发现抢答器在提高课堂互动性和学生参与度方面有着显著的效果。

抢答器能够快速准确地记录学生的抢答时间,并通过主机进行统计分析。

我们还发现,学生在使用抢答器后更加积极主动地参与课堂讨论,提高了他们的学习兴趣和主动性。

然而,我们也发现了一些问题。

由于抢答器设备的制作过程较为复杂,需要一定的技术支持和时间投入。

此外,抢答器的使用也需要一定的操作技巧,对于一些不熟悉技术的教师和学生来说可能存在一定的学习成本。

五、结论抢答器作为一种课堂互动工具,能够有效提高学生的参与度和学习效果。

然而,在推广和应用抢答器时,需要考虑到设备制作和操作技巧等方面的问题。

未来,我们可以进一步改进抢答器的设计,使其更加简单易用,以满足更广泛的教育需求。

四人抢答器设计报告

四人抢答器设计报告一、设计任务及要求1、设计用于竞赛的四人抢答器(1)有多路抢答器,台数为四;(2)具有抢答开始后20秒倒计时,20秒倒计时后无人抢答显示超时,并报警;(3)能显示超前抢答台号并显示犯规报警;2、系统复位后进入抢答状态,当有一路抢答键按下时,该路抢答信号将其余各路抢答封锁,同时铃声响起,直至该路按键放松,显示牌显示该路抢答台号;3、用VHDL语言设计符合上述功能要求的四人抢答器,并用层次设计方法设计该电路;4、完成电路全部设计后,通过系统实验箱下载验证设计课题的正确性。

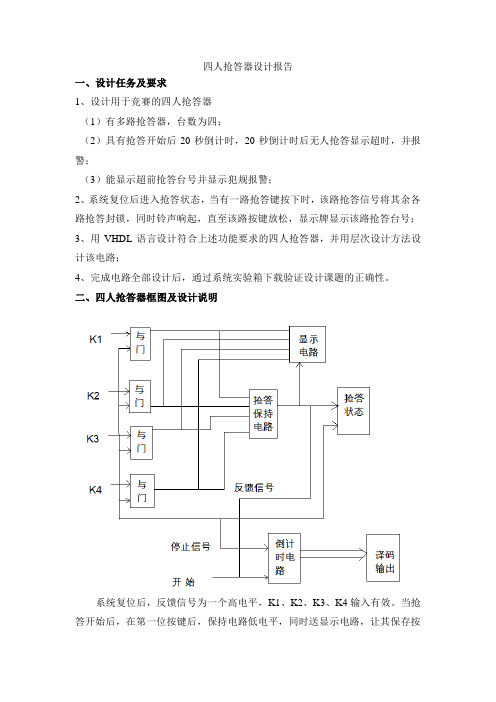

二、四人抢答器框图及设计说明系统复位后,反馈信号为一个高电平,K1、K2、K3、K4输入有效。

当抢答开始后,在第一位按键后,保持电路低电平,同时送显示电路,让其保存按键的台号并输出,同时反馈给抢答台,使所有抢答台输入无效,计时电路停止;当在规定的时间内无人抢答时,倒计时电路输出超时信号;当主持人开始说话未说完有人抢先按键时,显示犯规信号。

当选手回答正确时加分,回答错误时减分。

由主持人控制加减分数。

三、设计思路:根据设计框图和设计要求,本次实验可以采用模块化设计方法来实现智力竞赛四人抢答器。

将抢答器划分为抢答鉴别保持模块,倒计时模块,记分模块和判断显示模块。

再利用元件例化语句将这四个模块组成总的抢答器的设计电路。

选用模式五进行程序的下载。

四、VHDL语言设计与分析1、鉴别模块library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity jianbie isport(nu1,nu2,nu3,nu4:in std_logic;clk,en,rst:in std_logic;warn:out std_logic;back:buffer std_logic;s:out std_logic_vector(3 downto 0));end jianbie;architecture jianbiebeh of jianbie issignal num,warnd:std_logic;signal cnt:std_logic_vector(2 downto 0);beginnum<=nu1 or nu2 or nu3 or nu4;p1:process(rst, nu1,nu2,nu3,nu4,back) --判断抢答信号beginif rst='1' then back<='1';s<="0000";elsif back='1' thenif nu1='1' then s<="0001";back<='0'; --一号台抢答,输出S为1 elsif nu2='1' then s<="0010";back<='0'; --二号台抢答,输出S为2elsif nu3='1' then s<="0011";back<='0'; --三号台抢答,输出S为3 elsif nu4='1' then s<="0100";back<='0'; --四号台抢答,输出S为4 else back<='1'; s<="0000"; --无人抢答,输出S为0end if ;end if;end process p1;p2:process(clk,en,back,rst,cnt)beginif rst='1' then cnt<="000";warnd<='0';elsif clk'event and clk='1' thenif en='0' and back='0' thenif cnt<"111" then warnd<=not warnd; cnt<=cnt+1;else warnd<='0';end if; end if;end if;end process p2;warn<=warnd;end jianbiebeh;鉴别保持模块由两个进程组成,进程一主要用于鉴别强大信号,进程二用于鉴别是否为超前抢答,若是超前抢答,则输出报警信号。

数字式竞赛抢答器设计报告

数字式竞赛抢答器设计报告实验日期:学院:班级:姓名:学号:1、设计任务与要求(1)设计一个可容纳7组参赛的数字式抢答器,每组设一个按钮,供抢答使用。

(2)抢答器具有第一信号鉴别和锁存功能,使除第一抢答者外的按钮不起作用。

(3)设置一个主持人“复位”按钮。

(4)主持人复位后,开始抢答,第一信号鉴别锁存电路得到信号后,由指示灯显示抢答组的编号,同时扬声器发出2~3秒的音响。

选做扩展功能:(5)设置一个计分电路,每组开始预制100分,由主持人计分,答对一次加10分,答错一次减10分。

2、设计原理定时抢答器的总体框图如图1所示,它由主体电路和扩展电路两部分构成,主体电路完成基本的抢答功能,即开始抢答后,当选手按动抢答键时,能显示选手的编号,同时能封锁输入电路,禁止其他选手抢答。

扩展电路完成各选手的得分显示功能。

定时抢答器的工作过程是:接通电源时,主持人将开关置于“清除”位置,抢答器处于禁止工作状态,编号显示器灭灯;抢答开始时,主持人将控制开关拨到“开始”位置,扬声器给出声响提示,抢答器处于工作状态,这时,抢答器完成以下工作:(1)优先编码器电路立即分辨出抢答者编号,并由锁存器进行锁存,然后由译码显示电路显示编号;(2)扬声器发出短暂声响,提醒主持人注意;(3)控制电路要对输入编码电路进行封锁,避免其他选手再次进行抢答;(4)当选手将问题回答完毕,主持人操作计分开关,计分电路采用十进制加/减计数器、数码管显示。

本轮抢答完毕,主持人操作控制开关,使系统回复到禁止工作状态,以便进行下一轮抢答。

单元电路设计:(1)抢答电路抢答电路包括抢答按钮、优先编码电路、锁存器、译码显示电路。

抢答电路的功能有两个:一是能分辨出选手按键的先后,并锁存优先抢答者的编号,供译码显示电路用;二是要使其他选手的按键操作无效。

1)抢答按钮电路抢答按钮电路由8个按钮开关及限流电阻所组成,如图2所示。

其供电电源选5V与系统电源一致。

限流电阻的确定,一方面要考虑开关断开时,要保证加到编码器(TTL电路)输入端的高电平大于器件所需的最低高电平(如2V);另一方面又要考虑开关闭合时,不至于有太大电流以增加电源消耗。

开放课题智力竞赛抢答器设计报告(一)

开放课题智力竞赛抢答器设计报告(一)开放课题智力竞赛抢答器设计报告一、背景介绍开放课题智力竞赛是一项智力竞赛,需要选手快速准确地抢答问题,因此需要一个抢答器来辅助比赛,提高比赛的公正和效率。

二、需求分析1. 选择器为了避免抢答造成混乱,需要一个选择器,能够依次选择下一个抢答选手。

选择器可以是一个按钮或者一个旋钮。

2. 显示器为了确保比赛公正,需要一个显示器来显示抢答选手的编号和得分。

显示器可以是数字显示屏或LED灯。

3. 计时器为了控制比赛时间,需要一个计时器。

当比赛时间到达设定时间时,抢答器会自动停止,不能再进行抢答。

4. 抢答按钮每个选手都需要一个抢答按钮,选手按下按钮后,抢答器会记录下时间并发出声音。

选手抢答的时间越短,得分越高。

三、系统设计抢答器主要由选择器、显示器、计时器和抢答按钮组成。

选择器通过按钮或旋钮选择下一个抢答选手,选手按下抢答按钮来开始抢答。

计时器会记录抢答时间并停止计时器,同时记录抢答选手的编号和得分。

显示器显示抢答选手的编号和得分。

四、原理图设计抢答器的原理图如下图所示:五、电路设计抢答器的电路设计如下图所示,采用了ATmega328P单片机作为控制核心,用按钮或旋钮控制下一个抢答选手,同时记录选手的编号和得分。

显示器使用LED显示器,可以清晰显示抢答选手的编号和得分。

六、实验结果经过实验可以发现,抢答器的响应速度非常快,抢答选手的编号和得分可以清晰显示在LED屏幕上。

同时,计时器的精度非常高,可以确保比赛的公正性。

七、结论本文设计了一种抢答器,用于开放课题智力竞赛。

经过实验可以发现,抢答器的响应速度非常快,计时器的精度非常高,可以确保比赛的公正性。

因此,本文设计的抢答器可以广泛应用于各种智力竞赛和抢答活动中。

竞赛抢答器(微机实验报告)

竞赛抢答器一、实验目的1、了解微机化竞赛抢答器的基本原理。

2、进一步学习使用并行接口。

二、实验内容图1为竞赛抢答器(模拟)的原理图,逻辑开关K0~K7代表竞赛抢答按钮0~7号,当某个逻辑电平开关置“1”时,相当某组抢答按钮按下。

在七段数码管上将其组号(0~7)显示出来,并使微机扬声器响一下。

图1 硬件连接图表1 LED 数码表三、编程提示设置8255为C口输入、A口输出,读取C口数据,若为0表示无人抢答,若不为0则有人抢答。

根据读取数据可判断其组号。

从键盘上按空格键开始下一轮抢答,按其它键程序退出。

四、参考流程图(见图2)图2 程序流程图五、实验代码data segment led db 3fh,06h,5bh,4fh,66h,6dh,7dh,07hdata endscode segment ;段定义开始assume cs:code,ds:datastart:mov ax, datamov ds,axmov dx,28bh ;设置8255的输出输入mov ax,89hout dx,al ;将AL的值送入DX端口mov bx,offset led ;设置bx指向sss:mov dx,28ahin al,dx ;输入数据or al,alje sssmov cl,0ffhrr:shr al,1inc cljnc rrmov al,clxlatmov dx,288hout dx,almov al,7mov ah,2int 21hwai:mov ah,1int 21h ;调用21中断cmp al,20hjne eeemov al,0mov dx,288hout dx,aljmp ssseee:mov ah,4ch ;将4CH存入AH,int 21h ;调用21中断code ends ;代码段结束end start ;程序结束六、实验总结通过实验,了解微机化竞赛抢答器的基本原理,熟悉汇编代码的编写,进一步学习使用并行接口。

抢答器的实验报告

抢答器的实验报告抢答器的实验报告一、引言在现代教育中,积极主动的学习参与是培养学生思维能力和团队合作精神的关键。

而在课堂互动中,抢答环节常常能够激发学生的学习热情和积极性。

为了提高课堂效果,我们进行了一项抢答器实验。

二、实验目的本实验的目的是通过使用抢答器,评估其对学生参与度和学习效果的影响。

我们希望通过实验结果,为教育者提供参考,以便更好地利用抢答器来促进学生的学习。

三、实验方法1. 实验设计本实验采用了对照组与实验组相结合的设计。

课堂上,我们将学生分为两组,其中一组使用抢答器进行抢答,另一组则采用传统的手举方式。

通过对比两组学生的表现,我们可以评估抢答器对学生参与度和学习效果的影响。

2. 实验过程在课堂上,我们首先向学生介绍了抢答器的使用方法,并说明了实验的目的和意义。

然后,我们将学生分为两组,并给每个学生发放一个抢答器或者一个手举卡片。

在课堂上,教师提出问题后,学生使用相应的方式进行抢答或者举手回答。

我们记录了每个学生的回答情况和回答正确率,并对两组学生的表现进行了比较分析。

四、实验结果通过对实验数据的统计和分析,我们得出了以下结论:1. 学生参与度提高:使用抢答器的实验组学生在课堂参与度上表现更好。

相比于传统的手举方式,抢答器能够更快速、公平地选择回答者,激发学生的积极性和主动性。

2. 学习效果提升:实验组学生在学习效果上也取得了显著的提升。

抢答器的使用不仅能够促使学生更加专注于课堂内容,还能够培养学生的思维能力和解决问题的能力。

3. 学生互动增加:抢答器的引入使得学生之间的互动增加。

学生们通过抢答的过程,不仅能够与教师进行互动,还能够与同学们进行竞争和合作,促进团队合作精神的培养。

五、实验讨论虽然抢答器在本实验中取得了积极的效果,但我们也要注意其使用的适度与合理性。

过多地依赖抢答器可能会导致学生过度竞争,降低课堂氛围。

因此,在使用抢答器时,教师需要根据实际情况进行灵活运用,合理安排抢答环节,以达到最佳的教学效果。

八路竞赛抢答器设计实验报告

八路竞赛抢答器设计实验报告#八路竞赛抢答器设计实验报告##1.实验目的通过设计和制作八路竞赛抢答器,掌握数字电子技术的基本原理和应用,培养实际动手能力,提高团队协作和创新能力。

##2.实验原理八路竞赛抢答器主要基于数字电子技术的逻辑门、计数器、时序电路等原理。

每个参赛者的抢答器包含按钮、计数器、显示器等组件,通过按下按钮触发计数器计数,同时在显示器上显示计数结果。

##3.实验材料与器件-逻辑门:使用TTL(Transistor-Transistor Logic)或CMOS(Complementary Metal-Oxide-Semiconductor)逻辑门芯片。

-计数器:选择适当的计数器芯片,如74LS190或74HC161等。

-按钮开关:作为参赛者抢答的触发器。

-显示器:使用数码管或LED等显示模块。

##4.实验步骤###4.1设计电路图根据竞赛抢答器的要求,设计电路图,包括逻辑门的连接、计数器的接入、按钮开关和显示器的布置等。

###4.2制作原型根据电路图,制作抢答器的原型。

连接逻辑门、计数器、按钮、显示器,并确保电路的正确性。

###4.3编程(如有需要)如果抢答器需要特定的计分逻辑或显示效果,可能需要进行微控制器的编程工作。

在这一步骤中,确保编写的程序与硬件连接相匹配。

###4.4调试与测试逐一检查电路连接,确保没有短路或开路。

通过模拟按下按钮的操作,测试计数器和显示器的正常工作。

##5.实验结果与分析经过调试与测试,八路竞赛抢答器实现了预期的功能。

通过观察显示器的计数结果,可以准确判断参赛者的抢答顺序。

##6.实验总结通过本次实验,加深了对数字电子技术原理的理解,提高了动手制作电子装置的能力。

同时,实验中的问题与挑战也促使我们更好地合作解决问题,培养了团队协作与创新的精神。

##7.实验改进与展望为了进一步提高抢答器的性能,可以考虑引入更多的计数器、添加蓝牙或无线模块,以实现远程监控和计分等功能。

八路智力竞赛抢答器设计实验报告-抢答器设计实验报告

.. . ..数字电子技术课程设计题目: 八路智力竞赛抢答器设计姓名:专业: 电子科学与技术班级: 122班学号:指导教师:20 年月日.XX科技学院理学院八路智力竞赛抢答器设计一、课程设计题目(与实习目的)(一)、题目:八路智力竞赛抢答器设计(二)、实习目的:1.进一步掌握数字电路课程所学的理论知识。

2.熟悉几种常用集成数字芯片的功能和应用,并掌握其工作原理,进一步学会使用其进行电路设计。

3.了解数字系统设计的基本思想和方法,学会科学分析和解决问题。

4.培养认真严谨的工作作风和实事求是的工作态度。

5.数点课程实验是大学中为我们提供的唯一一次动手实践的机会,增强动手实践的能力。

二、任务和要求实现抢答器的方法很多,如EPROM编程、RAM编程、单板机、单片机等,都可以组成抢答器系统。

(1)抢答器设计要求设计一个抢答器,基本要求:1. 抢答器可以实现基本抢答;可同时供8名选手或8个代表队参加比赛,他们的编号分别是0、1、2、3、4、5、6、7,各用一个抢答按钮,按钮的编号与选手的编号相对应,分别是S0、S1、S2、S3、S4、S5、S6、S7。

2.给节目主持人设置一个控制开关,用来控制系统的清零(编号显示数码管灭灯)和抢答的开始。

3.抢答器具有数据锁存和显示的功能。

抢答开始后,若有选手按动抢答按钮,编号立即锁存,并在LED数码管上显示出选手的编号,同时扬声器给出音响提示。

此外,要封锁输入电路,禁止其他选手抢答。

优先抢答选手的编号一直保持到主持人将系统清零为止。

三、总体方案的选择(1)总体方案的设计针对题目设计要求,经过分析与思考,拟定以下二种方案:方案一:该方案是将抢答按钮先直接与锁存器而不是优先编码器相连,将最先抢答的选手的编号锁定,再依次经过优先编码器、译码器和七段显示器,最后显示的是抢答选手的编号,经过优先编码器后的信号到单稳态触发器,单稳态触发器又与报警电路直接连接,所以显示编号的同时可以发出报警信号。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

一、设计内容:为了保证抢答竞赛的公正性、准确性、提高竞赛得分的透明性并能产生激烈的竞赛气氛,要求由电子电路实现一个多人参赛,具备限时开始抢答, 限时结束抢答, 抢答结束后有声、光指示并能加/减计分的“竞赛抢答器”。

二、主要要求及指标:1. 设一个主持人按键, 供主持人宣布抢答开始. 抢答开始后, 四个抢答按键才有效, 同时启动限时定时器。

2. 设四个抢答按键供四人抢答使用,第一个抢答键按下后要锁住抢答器,并用声、光指示,要显示是几号按键抢到。

后按的抢答键不起作用。

3. 安排倒计数定时器。

开始后若预定时间内无人抢答,自动给出信号停止抢答。

倒计数定时器的时间可以随意预置。

倒计数计数脉冲要准确。

4.设两个计分按键,加/减由主持人控制。

5.每组安排一个三位加/减可逆计数器实现计分,从预置的100分开始,答对者加10分,答错则扣10分。

三、设计思路及电路工作原理:设计思路及原理根据要求可以将电路分为三大部分,控制抢答结果的抢答电路;负责倒计时的倒计时电路;完成分数加减的计分电路。

其中抢答电路最为重要,倒计时电路与计分电路都由抢答电路控制,倒计时电路与计分电路有很多相似的地方所用的芯片应该相似,关键在于如何将三个电路联系在一起。

抢答电路要实现的功能是在主持人开关控制下能够让四个选手抢答,并且在第一个人抢答之后其他人不能抢答。

这就要求电路能够进行优先编码并且能够锁存优先编码。

编码器使用74LS148能够实现四位的抢答,要实现锁存只需要将该芯片的使能端EI变成高电平。

能够让主持人控制编码器可以通过基本RS触发器或者与非门实现,但是后者显然逻辑会比较复杂所以放弃。

倒计时电路,可以通过秒脉冲触发计数器的使其实现倒计时,同时要在有选手抢答后停止倒计时,就需要计数器有一个类似使能端的端口。

使用74LS192芯片可以将秒脉冲接入DOWN端UP端接高电平能够实现单一的倒计时。

需要倒计时停止的时候,可以给CLR端输入高电平,此时计时器清零。

同时也可以使用74LS190实现相同的功能,与前者不同的是190在有人抢答后可以显示剩余时间,而且其接线要比192简单,只需将U/D 端接高电平即可倒计时。

需要停止倒计时将CTEN 端接高电平就可以。

计分电路,要实现两个开关控制四个人的分数就必须要有数据分配器,使用74LS138可以将译码器转译出的二进制数分配到各个选手的计分电路中。

各个选手的计分电路由74LS190为主要芯片,当数据分配器的信号输出后只有相应的计分电路被导通,在数据分配器的信号输入端输入脉冲信号,给出脉冲后只有相应的选手的分数会变动。

竞赛抢答器的结构框图如下:四、设计方案的比较选择抢答电路:1、用与非门等 逻辑门电路拼凑出所需的逻辑结果。

弃用原因:涉及的门电路过多,在实际连接中容易出错。

2、用基本RS 触发器。

无需时间脉冲就能触发,容易实现清零与置数功能。

弃用原因:实验室没有提供基本RS 触发器。

3、用74LS76 JK 触发器,功能基本能够代替基本RS 触发器。

加减分电路:1、用JK 触发器实现可逆二进制计数器。

弃用原因:需要五位二进制,多位二进制转化为十进制难实现并且使用芯片过多。

2、用74LS192可预置加减法器。

弃用原因:要方便的实现加减转换比较主持人控制开关 译码电路 抢答电路 定时电路选择器 加减分电路 译码显示困难。

3、用74LS190实现加减法功能。

使用原因:能够实现两位十进制加减法,且加减转换方便,可预置分数。

计时电路:1、用74LS192可预置加减法器。

弃用原因,可以实现所需要求,考虑到加减分电路中使用的是74LS190芯片,为简化电路放弃使用。

2、用74LS190芯片。

与加减电路中使用相同的芯片,简化连接和准备的过程。

四、单元电路设计:(电路结构的选择及主要特点,工作原理,要完成的任务;画出必要的功能表格、时序图、状态表或要实现的指标、逻辑流程、波形图、时序图或真值表等;画出电路图;元器件的选择、计算、具体参数值、元器件型号;逻辑推理过程、状态转换表、卡诺图;关键元件的资料说明)。

1、抢答电路:抢答电路要实现当主持人开关在“清零”端时,任何选手抢答均无效。

当主持人开关“开始”时,触发倒计时电路开始计时,并且允许抢答。

当有选手抢答时显示管显示抢答者编号,反馈至倒计时电路使其停止计时,并且其它选手抢答无效。

对于74LS148芯片,其真值表及管脚图如图Inputs | OutputsEI | 0 1 2 3 4 5 6 7 | A2 A1 A0 | GS EO---|-----------------|----------|-------1 | X X X X X X X X | 1 1 1 | 1 10 | 1 1 1 1 1 1 1 1 | 1 1 1 | 1 00 | X X X X X X X 0 | 0 0 0 | 0 10 | X X X X X X 0 1 | 0 0 1 | 0 10 | X X X X X 0 1 1 | 0 1 0 | 0 10 | X X X X 0 1 1 1 | 0 1 1 | 0 10 | X X X 0 1 1 1 1 | 1 0 0 | 0 10 | X X 0 1 1 1 1 1 | 1 0 1 | 0 10 | X 0 1 1 1 1 1 1 | 1 1 0 | 0 10 | 0 1 1 1 1 1 1 1 | 1 1 1 | 0 1输入端1、2、3、4分别代表四位选手的抢答按钮,输入为低电平时为抢答状态,高电平为非作答状态。

EI为输入使能端,当EI=0时芯片处于工作状态,EI=1时输入无效。

当无输入即无人抢答时GS=1,一旦有人抢答,GS输出变为0。

对于74LS76芯片,其真值表及管脚图如图___ ___ _PRE CLR CLK J K | Q Q----------------------------0 1 X X X | 1 01 0 X X X | 0 10 0 X X X | 1 11 1 P 0 0 | Hold1 1 P 1 0 | 1 01 1 P 0 1 | 0 11 1 P 1 1 | Toggle抢答电路图如下:为满足功能要求需使用两个74LS76芯片,将两个芯片的每个CLR端均与一开关(即主持人开关)相连,使其同时置向高电平或低电平。

第一个芯片的1PRE、2PRE分别与74LS148的Q0、Q1相连,第二个芯片的1PRE与74LS148的Q2相连。

当主持人开关为“清零”时(即CLR=0),无论74LS148输出Q0、Q1、Q2为0或1,74LS76的输出Q均为0。

当主持人宣布“开始”后(即CLR=1),在无人作答情况下74LS148的输出Q0、Q1、Q2为1、1、1,经74LS76后相应输出Q均为0。

此时若有选手抢答(例如2号选手作答),74LS148输出Q0、Q1、Q2为1、0、1,经74LS76后相应输出变为0、1、0。

输出端与显示管相连显示出抢答者编号。

另外,第二个芯片的2PRE端与74148的GS端,其相应输出2Q与74148的EI端相连。

当主持人宣布“开始”后(即CLR=1),2、倒计时电路倒计时电路要实现的功能是预置选手抢答时间进行倒计时,在倒计时结束后反馈到主电路中锁住优先编码器并给出声光提示,在有选手抢答后倒计时要能够自行停止,在主持人开关关闭后倒计时器能自动显示回预置时间。

对于74LS190芯片,其真值表如图CTEN D/U CLK LOAD A B C D QA QB QC QD0 X X 0 X X X X A B C D0 1 POS 1 X X X X Count Down0 0 POS 1 X X X X Count Up1 X X X X X X X Qa0 Qb0 Qc0 Qd0给A,B,C,D输入相应的二进制数当LOAD接低电平时可以实现置数,所以LOAD端要与主持人开关联系,当主持人开关处于关闭状态是使得LOAD端为低电平;主持人开关打开时LOAD端为高电平将芯片的U/D端接高电平,给时钟端秒脉冲就能实现倒计时功能。

当有选手抢答后要求倒计时停止,则需要有抢答电路中有信号输入CTEN端使得在有人抢答后CTEN端能够及时变成高电平。

如果没有人抢答要使倒计时电路停止工作,由QA,QB,QC,QD四路输出控制使得CTEN端在四项输出均为零时变为高电平。

具体电路如图所示图中两片74LS190构成两位数的倒计时器,图下方的开关用来设定倒计时的时间,右侧芯片的时钟端与秒脉冲相连LOAD端与主持人开关相连,输出端QA,QB,QC,QD与译码器相连。

输出的结果经过非门之后在经过与非门回到CTEN端能使得当输出全部为零,即时间到后没人抢答的情况下使得CTEN端成为高电平倒计时停止。

图中或门的另一端与主电路相连,使得在有人抢答后CTEN也能变成高电平。

倒计时个位与十位的连接方法:当个位输出为1001时十位的芯片应该接受一个脉冲,即QA与QD同时输出为1的时候左侧的190芯片接收一个脉冲,所以把QA,QD作为与门的输入端,左侧芯片的时钟端作为与门的输出端以实现两位数的倒计时。

QA QB QC QD CTEN0 0 0 0 10 0 0 1 00 0 1 0 0…倒计时电路的自锁:在电路中要使倒计时结束时电路停止工作,就要使QA,QB,QC,QD 输出均为0时CTEN 变为1。

( 真值表如右图)与与非门的输入特性相同,只要把输入输出的结果加非门就可以,所以在QA,QB,QC,QD 输出加非门后进入四输入的与非门,再将结果进行非就能实现上述要求。

3、计分电路:计分电路要实现的功能是在有人抢答之后由数据选择器选择,将控制相应的选手分数的电路导通,通过改变74LS190U/D 端的电平决定分数的加减,CLK 端接选择器的输出端。

数据选择器的输入端接按钮,这样在相应选手选择后可以将脉冲输入到计分电路的时钟端实现分数的控制。

74LS138数据选择器功能如图GL G1 G2 | C B A | Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7X X 1 | X X X | 1 1 1 1 1 1 1 1X 0 X | X X X | 1 1 1 1 1 1 1 10 1 0 | 0 0 0 | 0 1 1 1 1 1 1 10 1 0 | 0 0 1 | 1 0 1 1 1 1 1 10 1 0 | 0 1 0 | 1 1 0 1 1 1 1 10 1 0 | 0 1 1 | 1 1 1 0 1 1 1 10 1 0 | 1 0 0 | 1 1 1 1 0 1 1 10 1 0 | 1 0 1 | 1 1 1 1 1 0 1 10 1 0 | 1 1 0 | 1 1 1 1 1 1 0 10 1 0 | 1 1 1 | 1 1 1 1 1 1 1 0将脉冲输入到G2端,当A,B,C 输入后Y1,Y2,Y3,Y4会有相应输出具体电路图如下1 0 0 1 0四个选手的计分电路的U/D端都连接到一个开关上由主持人控制选手是加分还是减分。