数字竞赛抢答器课程设计Verilog语言实现

用Verilog HDL编写的四路抢答器

module count20(a,clr,q1,q2); //计数器,从20计到0 input wire a; input wire clr; output reg [3:0]q1; output reg [3:0]q2; always@(posedge a or negedge clr) begin if(clr==0) begin q1<=4'b0000; q2<=4'b0010; end else if(q1==0) begin q2<=q2-1; q1<=9; end else q1<=q1-1; end endmodule

在BASYS 2 开发板的管脚配置: NET "A_TO_D[3]" LOC = F12; NET "A_TO_D[2]" LOC = J12; NET "A_TO_D[1]" LOC = M13; NET "A_TO_D[0]" LOC = K14; NET "a_to_g[6]" LOC = L14; NET "a_to_g[5]" LOC = H12; NET "a_to_g[4]" LOC = N14; NET "a_to_g[3]" LOC = N11; NET "a_to_g[2]" LOC = P12; NET "a_to_g[1]" LOC = L13; NET "a_to_g[0]" LOC = M12; NET "qiang_da[3]" LOC = A7; NET "qiang_da[2]" LOC = M4; NET "qiang_da[0]" LOC = G12; NET "qiang_da[1]" LOC = C11; NET "clk" LOC = B8; NET "button" LOC = P11; NET "button" CLOCK_DEDICATED_ROUTE = FALSE; NET "xuan" LOC = G1;

Verilog数字抢答器

数字抢答器设计与制作一、设计任务设计并制作一个数字抢答器。

二、设计要求1.抢答器同时供9名选手或9个代表队比赛,分别用9个按钮SW1 ~ SW9表示。

2.设置一个系统清除和抢答控制开关S,该开关由主持人控制。

3.抢答器具有锁存与显示功能。

即选手按动按钮,锁存相应的编号,并在LCD数码管上显示。

选手抢答实行优先锁存,优先抢答选手的编号一直保持到主持人将系统清除为止。

三、方案论证与总体设计1、提出方案。

本设计是一个数字电路设计题,可提出两种方案。

方案Ι由COMS系列数字集成电路:CD4543、CD4071、CD4069及少数外围电路组成。

方案Π由TTL系列数字集成电路:74LS248、74LS04、74LS32、74LS116及少数外围电路组成。

两种电路原理方框图一样(见图一),其工作原理为:接通电源后,主持人将开关拨到”清除”状态,抢答器处于禁止状态,编号显示器灭灯,定时器显示设定时间;主持人将开关置于“开始”状态,抢答器开始工作。

选手在抢答时,抢答器完成:优先判断、编号锁存、编号显示。

当一轮抢答之后,如果再次抢答必须由主持人再次操作”清除”和”开始”状态开关。

图一、电路原理方框图2、方案比较。

两种方案的设计原理相同,只是用的集成电路不同。

TTL 双极器件、电源电压5V、速度快数ns、功耗大mA级、负载力大,负载以mA计,不用端多半可不做处理。

CMOS 单级器件、电源电压可到15V、速度慢几百nS,功耗低省电uA级、负载力小以容性负载计,不用端必须处理。

设计便携式和电池供电的设备多用CMOS芯片,对速度要求较高的最好选用TTL中的74SXXX系列。

本电路对速度要求不大,选用CMOS型数字集成块来组成抢答器。

四、单元电路设计1.图中左上方所示为9路开关阵列电路,从图上可以看出其结构非常简单。

电路中,R1为下拉和限流电阻。

R2、R3、R4、R5用于分压,其中R1的阻值必须比R2~R5都小,当任一开关按下时,相应的输出为高电平,否则为低电平。

基于Verilog HDL的数字竞赛抢答器

欽件打夜场宗用2021年第2期售廉与电atChina Computer & Communication 基于Verilog HDL 的数字竞赛抢答器孙阔王颖*(大连理工大学城市学院电子与自动化学院,辽宁大连116024)摘 要:数字抢答器拥有广阔的市场前景,在电视节目、各类高校的比赛中都可以使用数字抢答器。

本文基于 Verilong HDL 设计了一种数字抢答器,该数字抢答器以6个参赛组为基础实现其他功能,具有一定的审场价值.关键词:Verilog HDL;数字抢答器;FPGA中图分类号:TP311.52 文献标识码:A 文章编号:1003-9767 (2021) 02-112-02Digital Competition Answerer Based on Verilog HDLSUN Kuo, WANG Ying*(School of Electronics and Automation, City College, Dalian University of Technology, Dalian Liaoning 116024, China)Abstract : Digital answering devices have broad market prospects, and digital answering devices can be used in TV programs and competitions in various colleges and universities. This paper designs a digital answering device based, on Verilong HDL ・ The digital answering device implements other functions based on 6 participating groups and has a certain market value.Keywords : Verilog HDL; digital answerer; FPGA0引言近年来,随着科学技术的不断发展,抢答器的功能以及实现方法也越来越多,在竞赛中使用抢答器是一种很流行的 比赛方式,深受比赛各方的青睐冋。

verilog--4路抢答器设计-带30s倒计时

四路抢答器一、程序module qiangda4(clr,clk,input1,input2,input3,input4,seg,clockin,scan,LED);input clr,clk,input1,input2,input3,input4;output [7:0] seg; //7段数码管数据output [7:0] scan; //数码管位选output [3:0] LED; //输出LED灯指示output clockin; //蜂鸣器reg [7:0] seg;reg [7:0] scan;reg [3:0] LED;reg clockin;reg [3:0] data;reg input_flag,count_flag;reg [14:0] count1;reg [8:0] count2;reg [3:0] LED_N;//reg clock_flag;reg div1khz,div1hz;reg [2:0] cnt;reg [3:0] dat;//reg [7:0] data_count;reg [3:0] count_one,count_ten;initial count_one='d0; //初始化initial count_ten='d3;initial data=4'b0000;initial LED_N=4'b1111;//-------------fenping分频1khz-----------------------------------always @(posedge clk )beginif(count1=='d25000)begin div1khz<=~div1khz;count1<=0;endelsebegin count1<=count1+1'b1;endend//-------------fenping--1hz-------------------------------always @(posedge div1khz)beginif(count2=='d500)begin div1hz<=~div1hz;count2<=0;endelsebegin count2<=count2+1'b1;endend//----------------------------------------------------------always @(posedge div1hz or negedge clr)beginif(!clr)begincount_one<='d0;count_ten<='d3;count_flag<=1'b0;endelse if((!input_flag)&(!count_flag))begin if(count_one=='d0&&count_ten=='d0)begin count_flag<=1'b1;endelse if(count_one=='d0)begin count_one<=4'b1001;count_ten<=count_ten-1'b1;endelsebegin count_one<=count_one-1'b1;endendelsebegin count_one<=count_one;count_ten<=count_ten;endend//-----------------------------------------------------------always @(posedge clk ) //or input1 or input2 or input3 or input4 beginif(!clr)beginLED_N<=4'b1111;//clock_flag<=1'b0;input_flag<=1'b0;data<=4'b0000;endelse if((!input_flag)&(!count_flag))beginif(input1==0)begindata<=4'b0001;LED_N<=4'b0111;input_flag<=1'b1;endelse if(input2==0)begindata<=4'b0010;LED_N<=4'b1011;input_flag<=1'b1;endelse if(input3==0)begindata<=4'b0011;LED_N<=4'b1101;input_flag<=1'b1;endelse if(input4==0)begindata<=4'b0100;LED_N<=4'b1110;input_flag<=1'b1;endelsebegindata<=data;LED_N<=LED_N;input_flag<=input_flag;endendend//-------------led灯及蜂鸣器--------------------------------------------------- always @(posedge clk)beginLED<=LED_N;clockin<=div1khz&(input_flag|count_flag);//dat<=data;end//--------------shu ma guan sao miao数码管扫描--------------------------------- always @(posedge div1khz)beginif(cnt=='d3)begin cnt<=0;endelsebegin cnt<=cnt+1'b1;endend//-----------------------------------------------------always @(cnt,data,count_one,count_ten)begincase(cnt)//3'b000 : begin scan<=8'b01111111;end3'b001 : begin scan<=8'b10111111;dat<=data;end //选手编号3'b010 : begin scan<=8'b11011111;dat<=count_one;end //倒计时3'b011 : begin scan<=8'b11101111;dat<=count_ten;enddefault : begin scan<=8'bx;dat<=4'bx;endendcaseend//--------------------------------------------------------always @(dat)begincase(dat)4'b0000 : seg[7:0]<=8'b11000000;4'b0001 : seg[7:0]<=8'b11111001;4'b0010 : seg[7:0]<=8'b10100100;4'b0011 : seg[7:0]<=8'b10110000;4'b0100 : seg[7:0]<=8'b10011001;4'b0101 : seg[7:0]<=8'b10010010;4'b0110 : seg[7:0]<=8'b10000010;4'b0111 : seg[7:0]<=8'b11111000;4'b1000 : seg[7:0]<=8'b10000000;4'b1001 : seg[7:0]<=8'b10010000;4'b1010 : seg[7:0]<=8'b10001000;4'b1011 : seg[7:0]<=8'b10000011;4'b1100 : seg[7:0]<=8'b11000110;4'b1101 : seg[7:0]<=8'b10100001;4'b1110 : seg[7:0]<=8'b10000110;4'b1111 : seg[7:0]<=8'b10001110;default : seg[7:0]<=8'bx;endcaseendendmodule二、框图三、设计思路四路抢答,有30s倒计时,当有人抢答时,数码管显示对应选手编号,同时对应LED灯亮,蜂鸣器响起,此时其他选手抢答无效。

数字式竞赛抢答器设计

实验七

实验步骤

1步

抢答触 发锁存 电路

数字式竞赛抢答器设计

2步

编 码 器 犯规 指示 显 示 译 码

3步

数码 管显 示器

反 码 犯规触 发锁存 电路

反 码

定时 电路

复位 电路

抢答器的组成框图

4步

5步

1. 根据设计指标,画出抢答器的组成框图。 2. 根据抢答器的组成框图、设计指标和所提供的集成块设计各个模块的电路图。 3. 根据各个模块之间关系,设计出总电路图。 4. 设计好接线、调试的方案。 5. 逐步接线、调试,解决调试过程中遇到的问题。 6. 记录、整理实验结果,完善电路图。

4.

主持人置开关为“开始”后,开始抢答,第一信号鉴别锁存电路得到信号后, 该组对应的指示灯亮,并用数码管显示抢答组别。要求开始抢答时,数码管 出于消隐(不亮)状态。

5.

设置定时电路,开始抢答后,9秒内未抢答,自动锁定抢答器。如9秒内有 人抢答,则停止计数,倒计数值用数码管显示。

6.

设置犯规电路,对提前抢答组别,即在主持人置开关为“开始”前,开关已 经按下,其对应的“犯规”指示灯亮。

实验七

数字式竞赛抢答器设计

胡俊杰 2006.4

实验七

实验目的

数字式竞赛抢答器设计

1. 学习数字电路综合应用。 2. 学习简单数字系统设计方法。

实验七

设计指标

1. 2. 3.

数字式竞赛抢答器设计

可供4组参赛队抢答,每组1个开关。 开始抢答后,除第一抢答者的开关外,其它抢答开关不起作用。 设置一个主持人操作的开关,有“复位”和“开始”功能,“复位”时不能 抢答。

实验七

实验要求

数字式竞赛抢答器设计

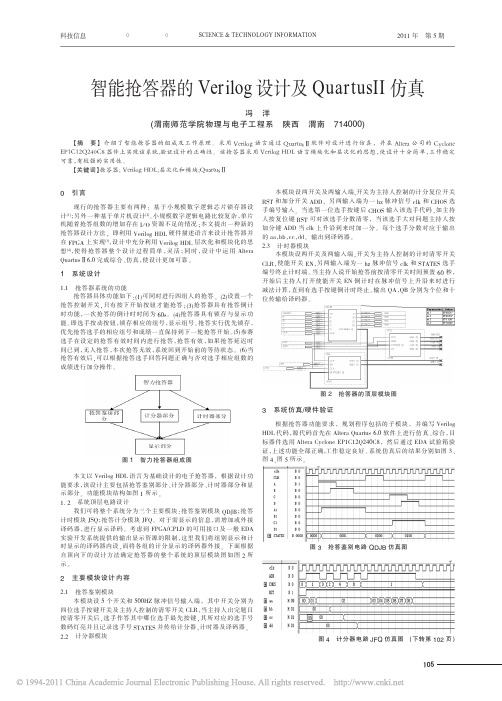

智能抢答器的Verilog设计及Quartus_仿真

本文用 Verilog HDL 设计实现一个具有四组输入的, 能够显示抢 答倒计时时间和抢答组数等信息,并且对抢答后各组的成绩进行处理 并显示的抢答器。利用 Verilog HDL 硬件描述语言设计抢答器,使抢答 器 硬 件 电 路 更 加 简 单 ,抢 答 器 时 序 控 制 灵 活 ;利 用 FPGA I / O 端 口 可 自定义特点,在本文设计智能抢答器基础上,增加抢答器的按键阵列,

1 系统设计

1.1 抢答器系统的功能 抢答器具体功能如下:(1)可同时进行四组人的抢答。 (2)设置一个

抢答控制开关,只有按下开 始 按 钮 才 能 抢 答 ;(3)抢 答 器 具 有 抢 答 倒 计 时功能,一次抢答的倒计时时间为 60s。 (4)抢 答 器 具 有 锁 存 与 显 示 功 能。 即选手按动按钮 ,锁存相应的组号 ,显示组号 。 抢答实行优先锁存 , 优先抢答选手的相应组号和成绩一直保持到下一轮抢答开始 。(5)参赛 选手在设定的抢答有效时间内进行抢答,抢答有效,如果抢答延迟时 间已到,无人抢答,本次抢答无效,系统回到开始前的等待状态。 (6)当 抢答有效后,可以根据抢答选手回答问题正确与否对选手相应组数的 成绩进行加分操作。

中央空调系统是按天气最热、负荷最大设计的,并留有 10%-20% 的余量,根据负载变化随之增减,但冷冻水泵和冷却水泵不能随负载 变化作出相应的调节,冷冻水、冷却水几乎长期在大流量、小温差的状 态下运行,造成能量的极大浪费。

3 节能改造的可行性分析

变频调速性能好,调速范围大,静态稳定性好,运行效率高。 根据 冷却水温选择冷却塔开启的台数,容易造成能源浪费,冷却水的温度 由温度传感器传送信号至 PLC,由 PLC 计算后,对冷却塔风机开启,以 28℃为基数,温度每上 升 2℃开 启 两 台 散 热 风 机 ,每 下 降 2℃延 时 5 分 钟后停止 2 台风机,以达到节能效果。

抢答器verilog版

抢答器-verilog一.实验要求设计一个可容纳四组参赛的数字式抢答器,每组设一个按钮供抢答使用。

抢答器具有第一信号鉴别和锁存功能,使除第一抢答者外的按钮不起作用;设置一个主持人“复位”按钮,主持人复位后,开始抢答,第一信号鉴别锁存电路得到信号后,用指示灯显示抢答组别,扬声器发出2—3s的音响。

设置犯规电路,对提前抢答和超时答题(例如3min)的组别鸣笛示警,并由组别显示电路显示出犯规组别。

设置一个计分电路,每组开始预置10分,由主持人记分,答对一次加1分,答错一次减1分。

二.实验方框图三.答题规则(本实验均采用脉冲按键模式)四.本次实验的verilog源程序module answer(clk,k1,k2,k3,k4,o1,o2,o3,o4,out1,out2,start,reset1, save); //抢答信号鉴别,保持模块input clk,k1,k2,k3,k4,start,reset1;//k1~k2是选手按键output o1,o2,o3,o4,out1,out2;//o1~o2是抢答信号显示灯output[2:0] save; //用于保存选手的抢答信号reg o1,o2,o3,o4,out1,out2,ok;reg[7:0] counter;reg[2:0] save;integer i;always@(posedge clk)if(reset1)//当reset1为1时复位清零begin{o1,o2,o3,o4,out1,out2,ok}<=7'b0000000;counter<=0;i=0;endelsebegin////if(start)beginok<=1;save<=0;endif(!ok)//reset1和ok为0时,有人按键表示犯规begin //一旦有人按键,他的输出信号将屏蔽其他人的按键if(k1&&!o2&&!o3&&!o4)begino1<=1;save<=1;endif(k2&&!o1&&!o3&&!o4)begino2<=1;save<=2;endif(k3&&!o1&&!o2&&!o4)begino3<=1;save<=3;endif(k4&&!o1&&!o2&&!o3)begino4<=1;save<=4;endif(o1 || o2 || o3 || o4)//提前按键扬声器响out1<=1;endelse//reset1为0,ok为1时,有人按键为正常抢答begin//if(k1 || k2 || k3 || k4)begin //一旦有人按键,他的输出信号将屏蔽其他人的按键if(k1&&!o2&&!o3&&!o4)begino1<=1;save<=1;endif(k2&&!o1&&!o3&&!o4)begino2<=1;save<=2;endif(k3&&!o1&&!o2&&!o4)begino3<=1;save<=3;endif(k4&&!o1&&!o2&&!o3)begino4<=1;save<=4;endendif(o1 || o2 || o3 || o4)begini=i+1;if(i<2)out2<=1;//有人抢到题,响几下铃。

VHDL语言设计竞赛抢答器设计方案

VHDL语言设计竞赛抢答器毕业论文随着电子技术的发展,现在的抢答器功能越来越强,可靠性和准确性也越来越高。

以前的抢答器大部分都是基于传统数字电路组成的。

制作过程复杂,而且准确性与可靠性不高,成品面积大,安装、维护困难。

由于近年来电子技术发展迅速,逐渐出现用现场可编程门阵列(简称FPGA)制作抢答器,使得电子系统的设计者利用EDA(电子设计自动化)软件,就可以独立设计自己的专用集成电路(ASIC)器件。

制作过程简单,而且安装、维护简单。

1.1选题的现实意义抢答器控制系统是学校、政府机关、金融单位、广播电视系统或党委、工会、团委、企事业单位等部门举办竞赛问答、各种知识测试、娱乐活动中经常使用的重要基础设备之一,它是一个能准确、公正、直观地判断出抢答者的机器[1]。

通过一些方式如数码管显示抢答成功者的信息,或者通过声音来判别成功抢答的选手。

随着现代科学技术的迅猛发展和经济全球化的加强,电子抢答器成为了不可逆转的发展趋势。

因此,研究智能电子抢答器及扩大其应用,有着非常现实的意义。

2 语言、软件介绍2.1 FPGA2.1.1 FPGA简介FPGA(Field-Programmable Gate Array),即现场可编程门阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。

它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点[2]。

目前以硬件描述语言(Verilog或VHDL)所完成的电路设计,可以经过简单的综合与布局,快速的烧录至 FPGA 上进行测试,是现代 IC 设计验证的技术主流。

这些可编辑元件可以被用来实现一些基本的逻辑门电路(比如AND、OR、XOR、NOT)或者更复杂一些的组合功能比如解码器或数学方程式。

在大多数的FPGA里面,这些可编辑的元件里也包含记忆元件例如触发器(Flip-flop)或者其他更加完整的记忆块。

抢答器( Verilog HDL实现)

桂林电子科技大学信息科技学院《EDA技术与应用》实训报告学号0952100110姓名赵万里指导教师:江国强杨艺敏2011年04月20日实训题目:智能电子抢答器1.系统设计1.1 设计要求1.1.1 设计任务设计并制作一台智能电子抢答器。

1.1.2 技术要求①用EDA实训仪的I/O设备和PLD芯片实现智能电子抢答器的设计。

②智能电子抢答器可容纳4组参赛者抢答,每组设一个抢答钮。

③电路具有第一抢答信号的鉴别和锁存功能。

在主持人将复位按钮按下后开始抢答,并用EDA实训仪上的八段数码管显示抢答者的序号,同时扬声器发出“嘟嘟”的响声,并维持3秒钟,此时电路自锁,不再接受其他选手的抢答信号。

④设计一个计分电路,每组在开始时设置为100分,抢答后由主持人计分,答对一次加10分,答错一次减10分。

⑤设计一个犯规电路,对提前抢答和超时抢答者鸣喇叭示警,并显示犯规的组别序号。

1.2 方案比较(1) 设计制作一个可容纳四组参赛者的数字智力抢答器,每组设置一个抢答按钮。

(2) 电路具有第一抢答信号的鉴别和锁存功能。

在主持人按下复位按钮后,若参加者按抢答开关,则该组指示灯亮。

此时,电路应具备自锁功能,使别组的抢答开关不起作用。

(3)自锁后,用八段数码管显示抢答者的序号,同时指示灯亮。

(4) 设置计分电路。

每组在开始时预置成100,抢答后由主持人计分,答对一次加10,否则减10分。

(5)电路具有淘汰功能,当每组的100分减少到0时,该组被淘汰,以后每次抢答,该组抢答按钮都无效。

1.3 方案论证1.3.1 总体思路总体分为四部分:倒计时模块、计分模块、抢答模块和分屏显示模块。

倒计时模块用一个20000000分频。

产生一个进位,连接一个30的减法计数器构成。

计分模块中分为两部分,一部分用于计分,另一部分用于处理计数器的进制问题,当加到A时自动向前进位,并且把A变为0。

当减少到F时,向前借位,并且把F变为9。

这就实现了把十六进制变成一般用的十进制。

verilog抢答器(最经典)

抢答器设计题目:智能电子抢答器专业:电子信息工程2011 年 1 月 7 日摘要抢答器是在竞赛、文体娱乐活动(抢答活动)中,能准确、公正、直观地判断出抢答者的机器。

电子抢答器的中心构造一般都是由抢答器由单片机以及外围电路组成。

本设计是以四路抢答为基本概念。

从实际应用出发,利用电子设计自动化( EDA)技术,用可编程逻辑器件设计具有扩充功能的抢答器。

它以Verilog HDL 硬件描述语言作为平台,结合动手实验而完成的。

它的特点是电路简单、制作方便、操作简单、方便、性能可靠,实用于多种智力竞赛活动。

本抢答器的电路主要有四部分组成:鉴别锁存电路、FPGA主芯片EP1C3T144C8电路、计分电路以及扫描显示模块的电路,并利用Quartus II工具软件完成了Verilog HDL源程序编写和硬件下载。

这个抢答器设计基本上满足了实际比赛应用中的各种需要。

在实际中有很大的用途。

关键词:抢答器 Quartus II Verilog HDL EP1C3T144C81引言硬件描述语言 Hardware Description Language 是硬件设计人员和电子设计自动化 EDA 工具之间的界面。

其主要目的是用来编写设计文件,建立电子系统行为级的仿真模型。

即利用计算机的巨大能力对用 Verilog HDL 或 VHDL 建模的复杂数字逻辑进行仿真,然后再自动综合以生成符合要求且在电路结构上可以实现的数字逻辑网表 Netlist,根据型仿真验证无误后用于制造ASIC芯片或写入 EPLD 和 FPGA 器件中。

Verilog HDL是一种硬件描述语言(HDL:Hardware Discription Language),是一种以文本形式来描述数字系统硬件的结构和行为的语言,用它可以表示逻辑电路图、逻辑表达式,还可以表示数字逻辑系统所完成的逻辑功能。

Verilog HDL就是在用途最广泛的C语言的基础上发展起来的一种件描述语言,它是由GDA(Gateway Design Automation)公司的PhilMoorby在1983年末首创的,最初只设计了一个仿真与验证工具,之后又陆续开发了相关的故障模拟与时序分析工具。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

数字竞赛抢答器课程设计Verilog语言实现可编程器件与应用课程设计报告姓名:XXX学号:XXXXXXXXXX专业班级:信息XXX题目:数字式竞赛抢答器指导老师:一、绪论背景:随着电子技术的发展,可编程逻辑器件(PLD)的出现,使得电子系统的设计者利用EDA(电子设计自动化)软件,就可以独立设计自己的专用集成电路(ASIC)器件。

可编程逻辑器件是一种半导体集成器件的半成品。

在可编程逻辑器件的芯片中按一定方式(阵列形式或单元阵列形式)制作了大量的门、触发器等基本逻辑器件,对这些基本器件适当地连接,就可以完成某个电路或系统的功能。

数字式竞赛抢答器控制系统是工厂、学校和电视台等单位举办各种智力竞赛等娱乐活动中经常使用的重要基础设备之一。

目前设计抢答器的方法很多,例如用传统的PCB板设计、用PIC 设计或者用单片机设计。

而用Verilog可以更加快速、灵活地设计出符合各种要求的抢答器,优于其他设计方法,使设计过程达到高度自动化。

本文介绍的4路数字式竞赛抢答器基于Verilog 语言、以EDA技术作为开发手段、采用CPLD (复杂的可编程逻辑器件)作为控制核心设计而成。

与传统设计相比较,不仅简化了接口和控制,也提高了系统的整体性能和工作可靠性,具有电路简单、成本低廉、操作方便、灵敏可靠等优点。

意义:数字式竞赛抢答器作为一种电子产品,早已广泛应用于各种智力和知识竞赛场合,但目前所使用的抢答器存在分立元件使用较多,造成每路的成本偏高,而现代电子技术的发展要求电子电路朝数字化、集成化方向发展,因此设计出数字化全集成电路的多路抢答器是现代电子技术发展的要求。

二、实现方案设计要求:1、设计一个可容纳4组参赛的数字式抢答器,每组设一个按钮,供抢答使用。

2、抢答器具有第一信号鉴别和锁存功能,使除第一抢答者外的按钮不起作用。

3、设置一个主持人“复位”按钮。

4、主持人复位后,开始抢答,第一信号鉴别锁存电路得到信号后,有指示灯显示抢答组别,扬声器发出2~3秒的音响。

5、设置一个计分电路,每组开始预置5分,由主持人记分,答对一次加1分,答错一次减1分。

6、设置犯规电路,对超时答题(例如1分钟)的组别鸣笛示警,并由组别显示电路显示出犯规组别,该轮该选手退出,由裁判员重新发令,其他人再抢答。

设计方案:此设计问题可分为第一信号鉴别、锁存模块,答题计时电路模块,计分电路模块和扫描显示模块四部分。

第一信号鉴别锁存模块的关键是准确判断出第一抢答者并将其锁存,在得到第一信号后,将输入端封锁,使其他组的抢答信号无效,可以用触发器或锁存器实现。

设置抢答按钮K1、K2、K3、K4,主持人复位信号judge,蜂鸣器驱动信号buzzout。

judge=0时,第一信号鉴别、锁存电路、答题计时电路复位,在此状态下,若有抢答按钮按下,鸣笛示警并显示犯规组别;judge=1时,开始抢答,由第一信号鉴别锁存电路形成第一抢答信号,进行组别显示,控制蜂鸣器发出声响,并启动答题计时电路,若计时时间到,主持人复位信号还没有按下,则由蜂鸣器发出犯规示警声。

计分电路是一个相对独立的模块,采用十进制加/减计数器、数码管数码扫描显示,设置复位信号Reset、加减分信号add_min,加减分状态键key_state,Reset=0时所有得分回到起始分(5分),且加、减分信号无效;Reset=1时,由第一信号鉴别、锁存电路的输出信号选择进行加减分的组别,当key_state=1时,按一次add_min,第一抢答组加1分;当key_state=0时,每按一次add_min,则减1分。

以下为每个模块的设计过程。

三、程序及仿真/**************************************** **************************顶层模块信号定义:clk:基准时钟输入信号;k1,k2,k3,k4:抢答按钮输入信号;seg:数码管段输出引脚;sl:数码管位输出引脚;add_min:加减分按键;key_state:加减分模式选择按键;reset:初始5分设置键信号;judge:裁判员抢答开始键信号;o5:超时信号;o1、o2、o3、o4:抢答组别LED显示输出信号;buzz:示警输出信号;***************************************** *************************/moduleqiangdaqi(clk,k1,k2,k3,k4,seg,sl,add_min,key_st ate,reset,judge,o1,o2,o3,o4,o5,buzz,vg,sel);inputclk,k1,k2,k3,k4,add_min,key_state,reset,judge; output[7:0] seg; output[3:0] sl; output reg sel; output o1,o2,o3,o4,o5,vg; output buzz;reg [3:0] vg=0010; wire o1,o2,o3,o4; wire[3:0] s1,s2,s3,s4;/* 模块引用*/selQ1(clk,k1,k2,k3,k4,judge,o1,o2,o3,o4,o5,buzz); //调用抢答信号锁存显示电路countQ2(clk,o1,o2,o3,o4,add_min,key_state,reset,s1,s2 ,s3,s4); //调用计分电路dled Q3(seg,sl,s1,s2,s3,s4,clk); //调用数码管显示电路endmodule/****************************************************************信号锁存电路信号定义:CLK:时钟信号;K1、K2、K3、K4、K5、K6:抢答按钮信号;out1、out2、out3、out4、out5、out6:抢答LED显示信号;judge:裁判员抢答开始信号;buzzout:示警输出信号;flag:答题是否超时的标志;***************************************** ***********************/modulesel(clk,k1,k2,k3,k4,judge,out1,out2,out3,out4,ou t5,buzzout);input clk,k1,k2,k3,k4,judge; output out1,out2,out3,out4,out5,buzzout;reg out1,out2,out3,out4,out5,block,buzzout; reg[32:0] count;reg[27:0] counter; reg flag;always@(posedge clk )begin counter=counter+1; //裁判员发开始抢答信号,初始指示灯灭,蜂鸣器禁声if(!judge) begin{out1,out2,out3,out4,out5,block}<=6'b111110; count=0; flag=0; endelse begin if(!k1) //第一组别按键是否按下begin if(!block)begin out1=0; //点亮第一组别指示灯block=1; //封锁别组抢答信号count=1; //第一组已按下按钮,可启动答题计时器end endelse if(!k2) //第二组别按键是否按下begin if(!block)begin out2=0; block=1;count=1; endendelse if(!k3) //第三组别按键是否按下begin if(!block)begin out3=0; block=1; count=1; endendelse if(!k4) //第四组别按键是否按下begin if(!block)begin out4=0; block=1; count=1; endendend /*答题计时开始,并判断是否答题超时*/ if(count!=0)begin if(count==32'hc11e7a00) //如果答题时间到了1分钟,亮犯规灯begin count=0; out5<=0; flag=1'b1; end else begin count=count+1; endendend ////蜂鸣器发声always@(counter[7])if(flag==1)buzzout=!(counter[11]&counter[22]&counter[27 ]);else buzzout=1'b0;endmodule/**************************************** **********************去键盘抖动信号定义:clkin:基准时钟输入信号;clkout:周期为20ms的信号输出;***************************************** ********************/module f_1M(clkin,clkout);Input clkin; output clkout;reg clkout; reg[18:0] count;always @(negedge clkin)if(count==19'd500000)begin count<=19'd000000; clkout<=~clkout; endelse count<=count+1'b1;endmodule/**************************************** **********************计分电路信号定义:clk:时钟信号;c1,c2,c3,c4:抢答组别输入信号;add_min:加减分按钮;key_state:加减分标志按钮;reset:初始5分设置信号;count1:第一组得分输出;count2:第二组得分输出;count3:第三组得分输出;count4:第四组得分输出;***************************************** ********************/modulecount(clk,c1,c2,c3,c4,add_min,key_state,reset,co unt1,count2,count3,count4);input clk,c1,c2,c3,c4,add_min,key_state,reset; output[3:0] count1,count2,count3,count4;reg[3:0] count1,count2,count3,count4; wire clk0; reg keyout;f_1M f_1Ma(clk,clk0); //引用获得20毫秒的子模块always @(negedge clk0)keyout=add_min;always @(posedge keyout) //根据相应组别加减分begin if(!reset) //初始化各组的起始分数{count1,count2,count3,count4}=16'h5555;if(!key_state) // key_state为低电平,选组别减分模式begin if(!c1) //第一组别减1分,最高分为10分,最低分为0分begin if(count1!=4'b0000) count1=count1-1; endif(!c2) //第二组别减1分,最高分为10分,begin if(count2!=4'b0000) count2=count2-1; endif(!c3) //第三组别减1分,最高分为10分,最低分为0分begin if(count3!=4'b0000) count3=count3-1; endif(!c4) //第四组别减1分,最高分为10分,最低分为0分begin if(count4!=4'b0000) count4=count4-1; endend else // key_state为高电平,选组别加分模式begin if(!c1) //第一组别加分,最高分为10分,最低分为0分begin if(count1>9) count1=0;else count1=count1+1; endif(!c2) //第二组别加分,最高分为10分,最低分为0分begin if(count2>9) count2=0;else count2=count2+1; endif(!c3) //第三组别加分,最高分为10分,begin if(count3>9) count3=0;else count3=count3+1; endif(!c4) //第四组别加分,最高分为10分,最低分为0分begin if(count4>9) count4=0;else count4=count4+1; end end end endmodule/**************************************** **************************数码管显示电路信号定义:clk:时钟信号;seg:数码管段输出引脚;sl:数码管位输出引脚;score1:第一组得分输入;score2:第二组得分输入;score3:第三组得分输入;score4:第四组得分输入;***************************************** *************************/module dled (seg,sl,score1,score2,score3,score4,clk,vg); output[7:0] seg; output[3:0] sl; output reg[3:0] vg=0010;input clk; input[3:0]score1,score2,score3,score4;reg[7:0] seg_reg; //定义数码管段输出寄存器reg[3:0] sl_reg; //定义数码管位输出寄存器reg[3:0] disp_dat; //定义显示数据寄存器reg[16:0] count; //定义计数器寄存器always@(posedge clk) //定义clock信号上升沿触发begin count=count+1; //计数器值加1 endalways@(count[14:13]) //定义显示数据触发事件begin case(count[14:13]) //选择扫描显示数据2'h0:disp_dat=score1; //在个位数码管上显示第一组别的分数值2'h1:disp_dat=score2; //在十位数码管上显示第二组别的分数值2'h2:disp_dat=score3; //在百位数码管上显示第三组别的分数值2'h3:disp_dat=score4; //在千位数码管上显示第四组别的分数值endcasecase(count[14:13]) //选择数码管显示位2'h0:sl_reg=4'b1110; //选择个位数码管2'h1:sl_reg =4'b1101; //选择十位数码管2'h2:sl_reg =4'b1011; //选择百位数码管2'h3:sl_reg =4'b0111; //选择千位数码管endcase endalways@(disp_dat) //显示数据的解码过程begincase(disp_dat)4'h0:seg_reg=8'h3f; //显示数据04'h1:seg_reg=8'h06; //显示数据14'h2:seg_reg=8'h5b; //显示数据24'h3:seg_reg=8'h4f; //显示数据34'h4:seg_reg=8'h66; //显示数据44'h5:seg_reg=8'h6d; //显示数据54'h6:seg_reg=8'h7d; //显示数据64'h7:seg_reg=8'h07; //显示数据74'h8:seg_reg=8'h7f; //显示数据84'h9:seg_reg=8'h6f; //显示数据94'ha:seg_reg=8'h77; //显示数据a4'hb:seg_reg=8'h7c; //显示数据b4'hc:seg_reg=8'h39; //显示数据c4'hd:seg_reg=8'h51; //显示数据d4'he:seg_reg=8'h79; //显示数据e4'hf:seg_reg=8'h71; //显示数据fendcase endassign seg=seg_reg; //输出数码管解码结果assign sl=sl_reg; //输出数码管选择endmodule管脚分配图如下:四、总结1、打开Quartus II软件,对该工程文件进行编译处理,若在编译过程中发现错误,找出并更正错误直至成功为止。