LDO设计小结一

本科论文(设计)ldo稳压器的电路及版图设计

LDO稳压器的电路及版图设计摘要随着信息科学的飞速发展,电源IC技术已经变得越来越重要。

在众多的电源技术中,由于低压差线性稳压器(LDO)的体积小、电源抑制比高、功耗小、噪声低及其应用端的电路简单等优点在众多电源IC中,人们的关注度非常普遍。

另外,由于LDO还具备比较好的负载瞬态响应与线性瞬态响应,这些优点使它在各个领域占有非常重要的地位,比如在MP3播放器、无线电话、PDA等电子设备中被广泛应用。

因此,当前电源IC技术领域的研究热点为线性稳压器的设计,具有重要的理论意义和实际应用价值。

文中详细的对LDO线性稳压器的整体电路结构及其工作原理作了简单介绍,并给出了各个主要子模块电路的设计。

另外,保证芯片在正常工作时能够安全,还对限流保护电路和过温保护电路进行了设计。

LDO线性稳压器在设计时的一个很大的难点就是整个系统的稳定性问题,本设计也不例外。

本文的仿真结果均采用Cadence-Spectre仿真工具来完成的,并且本文的版图也是利用Cadence完成的。

在实现匹配过程中,集成电路版图设计是一个非常重要的环节。

一个优秀的版图就可以大大提升一个设计。

关键词:线性稳压器,瞬态响应,稳定性,版图设计大连东软信息学院毕业设计(论文) Abstract LDO Regulator Circuit and Layout DesignAbstractWith the rapid development of information science, power IC technology has become increasingly important. Among the many power technology, due to low dropout linear regulator (LDO) small size, power supply rejection ratio, low power consumption, low noise and its applications side simple circuit in the power supply IC in many people’s attention very common. In addition, due to the LDO also has better load transient response with a linear transient response, these advantages in that it occupies a very important position in various fields, such as MP3 players, wireless phones, PDA and other electronic devices are widely used. Therefore, the current research focus power IC technologies for the linear regulator design has important theoretical and practical value.In detail on the overall LDO linear regulator circuit structure and its working principle is briefly introduced, and the design of each major sub-modules of the circuit. In addition, to ensure that the chip can be safe in normal operation, but also to limit protection circuit and over-temperature protection circuit design. In the design of a great difficulty LDO linear regulator is the stability of the whole system, this design is no exception.The simulation results in this paper are used Cadence-Spectre simulation tools to complete, and the layout of this paper also uses Cadence completed. In the realization of the matching process, IC layout design is a very important part. A good layout can greatly enhance a design.Key words: Linear regulators, Transient response, Stability, Layout目录摘要 (I)ABSTRACT (II)第1章绪论 (1)1.1背景及意义 (1)1.2LDO的国内外现状 (1)1.3LDO的发展趋势 (2)第2章LDO基本原理及性能参数 (4)2.1LDO的基本原理 (4)2.1.1 LDO的基本结构 (4)2.1.2 LDO的工作原理 (5)2.2LDO的性能参数 (5)第3章LDO的电路构架 (10)3.1构架概述 (10)3.1.1 标准分类 (10)3.1.2 芯片的整体电路 (11)3.2各个子模块的设计 (11)3.2.1 使能控制模块 (11)3.2.2 基准电压模块 (12)3.2.3 过温保护模块 (13)3.2.4 误差放大器模块 (14)3.2.5 限流保护模块 (15)3.2.6 静电释放模块 (16)3.3电路仿真 (16)第4章LDO的版图 (18)4.1集成电路版图设计(LA YOUT)概述 (18)4.2版图设计基本规则 (18)4.2.1 匹配性设计 (18)4.2.1.1 匹配电阻设计 (19)4.2.1.2 匹配电容设计 (19)4.2.1.3 匹配MOS管设计 (19)4.2.2 耦合效应 (20)4.2.3 寄生效应和闩锁效应 (20)4.3模拟电路的版图技术 (21)4.3.1 器件的匹配 (21)4.3.2 天线效应(Antenna effect) (22)4.4版图验证 (25)4.4.1 设计规则检查DRC (25)4.4.2 版图与原理图一致性检查LVS (25)第5章总结 (26)参考文献 (27)致谢 (28)第1章绪论近十几年来,具有低压差、低功耗的LDO(Low Dropout)稳压器被掌上电脑、笔记本电脑、移动电话等便携式设备及医疗、测试仪器的迅猛发展所拉动而快速发展。

LDO与PWM设计资料整理

LDO与PWM设计资料整理1.定义:LDO:LOW DROPOUT VOLTAGE,低压差线性稳压器,仅能在降压中应用。

输出电压必需小于输入电压。

PWM:脉冲宽度调制(PWM),是英文“Pulse Width Modulation”的缩写,是一种模拟控制方式,其根据相应载荷的变化来调制晶体管栅极或基极的偏置,来实现开关稳压电源输出晶体管或晶体管导通时间的改变,这种方式能使电源的输出电压在工作条件变化时保持恒定,是利用微处理器的数字信号对模拟电路进行控制的一种非常有效的技术。

2.LDO与DC/DC优缺点LDO:优点:稳定性好,负载响应快。

输出纹波小。

缺点:效率低,输入输出的电压差不能太大。

负载不能太大,目前最大的LDO为5A(但要保证5A的输出还有很多的限制条件)。

PWM开关电源:优点:输入电压范围较宽, 高效率,高输出电流,低静态电流。

缺点:负载响应比LDO差,输出纹波比LDO大,成本相对较高。

3.工作原理LDO:右图为串联线性电源的主要组成部分,其电压调整单元采用有源器件并串联在输入电源和负载之间,负反馈环路决定调整单元的导通程度,以维持输出电压稳定。

负反馈环路的核心是一个高增益的运算放大器,称作电压误差放大器,用它来对输出电压和稳定的基准电压之间作比较,当有误差存在时,电压误差放大器的增益将误差电压放大很多倍,放大后的误差电压直接控制串联调整单元的导通电阻,从而维持额定的输出电压。

电压误差放大器对输出变化的响应速度和输出电压的控制精度取决于误差放大器的反馈环补偿设计。

负反馈补偿的大小由分压电阻和接到电压误差放大器负输入端与输出端之间的电阻大小决定。

DC/DC开关电源:开关电源采用功率半导体器件作为开关元件,通过周期性通断开关,控制开关元件的占空比来调整输出电压。

如右图所示,其中DC/DC变换器进行功率变换,是开关电源的核心部分,反馈回路检测其输出电压,并与基准电压比较,其误差电压通过误差放大器放大及控制脉宽调制电路,再经过驱动电路控制半导体开关的通断时间比,从而调整输出电压的大小。

LDO学习与总结

LDO总结与学习<1>先从TVS管开始吧!那就先从他的命名开始。

然而对于我们的这个TVS来说所选用的型号是SMCJ30CA,按照上面的命名方法所讲解的意思就是那当中耐压30V,而对于当中的命名法则着看如下讲解。

然而在这个地方我想穿插一些自己方面的一个理解,昨天听培训说这里面TVS有一个功能就是关于当中的是为了过一个5b脉冲的作用(GWM3097标准之中)其实讲实话,我到现在为止都还不知道为啥是5b而不是3b或者是3a,我估计是不是在这里这个缘故才导致选择这个型号的TVS管。

当然了在这里的作用也可以是吸收静电及尖峰电涌。

而对当中的TVS的一份资料Appendix;一、选用指南1、首先确定被保护电路的最大直流或连续工作电压,电路的额定标准电压和“高端”容限。

2、TVS的额定反向关断电压VWM应大于或等于被保护电路的最大工作电压,若选用的VWM太低,器件有可能进入雪崩状态或因反向漏电流太大影响电路的正常工作。

3、TVS的最大箝位电压VC应小于被保护电路的损坏电压。

4、TVS的最大峰值脉冲功率PW必须大于被保护电路内可能出现的峰值脉冲功率。

5、在确定了TVS的最大箝位电压后,其峰值脉冲电流应大于瞬态浪涌电流。

6、对于数据接口电路的保护,必须注意选取尽可能小的电容值C的TVS器件。

7、带A的TVS二极管比不带A的TVS二极管的离散性要好,在TVS二极管A前面加C的型号表示双向TVS二极管。

8、直流保护一般选用单向TVS二极管,交流保护一般选用双向TVS二极管,多路保护选用TVS阵列器件,大功率保护选用TVS专用保护模块。

特殊情况,如:RS-485和RS-232保护可选用双向TVS二极管或TVS阵列。

9、TVS二极管可以在-55℃到+150℃之间工作,如果需要TVS在一个变化的温度下工作,由于其反向漏电流ID是随温度的增加而增大;功耗随TVS结温度增加而下降,故在选用TVS时应考虑温度变化对其特性的影响。

LDO设计小结一

是很有必要的。 (2)很多应用场合下,负载电路的电流消耗并不大(<20mA) ,这种情况下即使没有片外 的大电容,也可以保证 LDO 的瞬态性能。 对于没有外接电容的 LDO,其补偿方式通常是在环路内部产生主极点,同时结合 其它补偿技术来完成。 1.BIA + Cascode 补偿结构 该结构参考的是 07 年的 JSSC《A Transient-Enhanced Low-Quiescent Current Low-Dropout Regulator With Buffer Impedence Attenuation》 。 BIA 是 Buffer Impedence Attenuation 的简称。这种结构的基本思想如下图所示:

2 Vn,op

Vref

2 Vn,R1

R1

V

2 n,bg

2 Vn,R2

R2

电路的输出噪声主要有三个来源,bandgap 的输出噪声,误差放大器的等效输入噪 声及分压电阻 R1 和 R2 的噪声,将它们都等效到输出端,经过简单的化简后,可以得到 下面的表达式:

V

2 n,out

V

2 n,op

V

2 n,bg

PSR Vout Vdd

我们先来考虑 DC 情况下的 PSR,从电源到输出有两条通路,如下图所示:

Vdd Vref Vout

Aop

Vg

R1

R2

图中红色的两条虚线表示了从电源到输出的两条通路,一条是从电源经过 pass element 直接到输出,另一条是输出经过由电阻分压网络,误差放大器和 pass element 构成的反馈环路后回到输出。由此可以得到如下关系式:

Vref

Vref

上图左边的电路利用 PMOS 作为 pass element,显然 drop-out 电压即为 PMOS 管的饱和压降 Vdsat,大约为 200mv 左右。而对于右边的电路,由于采用 NMOS 管作 为 pass element,drop-out 电压受到了误差放大器输出电压的限制(误差放大器的输出 电 压 最 大 只 能达 到 其电 源 电 压 , 即 LDO 的 输 入 电 压 ) , 大 小为 NMOS 的 Vgs (Vdsat+Vth) 。虽然利用 NMOS 管作为 pass element 的 drop-out 电压比 PMOS 大, 但其某些性能比 PMOS 好,例如 PSRR(后文会详细介绍) 。并且,利用一些特殊的电 路技术可以使 NMOS 管作为 pass element 的 drop-out 电压与 PMOS 相同。比如,可 以额外引入 charge pump 电路来产生误差放大器的电源电压(该电压高于 LDO 的输入 电压) ,从而降低对 LDO 输入电压的要求。 2.3 输出电压抖动 该指标描述了 LDO 的瞬态响应特性,具体表达式如下:

LDO稳压器高精度电压基准源的分析与设计

LDO稳压器高精度电压基准源的分析与设计、随着集成电路规模的发展,电子设备的体积、重量和功耗越来越小,这对电源电路的集成化、小型化及电源管理性能提出了越来越高的要求。

电源IC产品主要包括线性稳压器、开关式稳压器(DC/DC)、电池充电/管理IC、PWM/PFM控制器、AC/DC稳压器及功率因数校正(PFC)预稳压器等。

而目前在所有这些电源IC中,线性稳压器IC 的销售额最大,LDO线性稳压器又是增长最多和最快的产品,它的快速崛起源自于便携式产品的不断涌现,如便携式电话、PDA(个人数字助理)、掌上型/膝上型电脑、数码相机等。

LDO线性稳压器综述LDO(LowDropout)线性稳压器,也称低压差线性稳压器或低漏失线性稳压器。

LDO线性稳压器与开关式稳压器的比较LDO线性稳压器,比传统的线性稳压器有更高的电源转换效率,而比开关式稳压器有更简单的结构、更低的成本和更低的噪声特性,因此它在便携式电子产品中越来越受欢迎。

LDO线性稳压器和开关式稳压器作为当今便携式电子产品中最常用的两类电源管理电路,它们的特点比较如表1所示。

从表中可看出,LDO线性稳压器和开关式稳压器各有优缺点,在应用时需权衡考虑各种特点。

LDO线性稳压器应用效率在便携式电子设备中,电源效率越高意味着电池使用时间越长,这是用户渴望的事情。

因此,输入输出压差越低、静态电流(输入电流和输出电流之差)越低线性稳压器的工作效率就越高。

在实际应用中,我们分析效率时还必须清楚:电池不是理想电源,它具有输出电阻,供电时,它的电压是逐渐下降的。

电池的这种特性是非常有利于LDO线性稳压器工作效率的。

LDO线性稳压器工作效率随着电池电压的下降而逐渐升高。

另外,在小负载电流时,稳压器的效率将受静态电流的限制,比如输出电流等于输入电流的一半,则稳压器的效率将减少一半,因此当设备处于“待机”状态时,静态电流决定了电池的使用寿命。

因此设计低压差、低静态电流的线性稳压器已成为便携式设备电源管理课题的一大技术解决方案。

ldo的应用与选型设计

ldo的应用与选型设计LDO(Low Dropout)是一种常用的电压稳压器件,广泛应用于各种电子设备中。

本文将从LDO的应用和选型设计两个方面进行详细介绍。

一、LDO的应用LDO电压稳压器具有输入电压和输出电压之间的较小压降(Dropout Voltage),因此被广泛应用于需要稳定输出电压的电路中。

以下是LDO的几个常见应用场景。

1. 电子产品电源管理在手机、平板电脑、数码相机等电子产品中,LDO被用于稳定供电电路,确保电路中各个模块正常工作。

LDO可以将高压降低到适合芯片工作的低电压,同时具备较好的抗干扰能力,提供稳定可靠的电源。

2. 通信设备在无线通信设备中,LDO被广泛应用于基站、天线放大器和射频前端等模块,用于提供稳定的电源供应。

LDO具有较低的噪声和纹波,可以有效降低射频系统中的杂散信号和噪声干扰。

3. 汽车电子在汽车电子系统中,LDO被用于提供稳定的电源给各个模块,如发动机控制单元(ECU)、车载娱乐系统和车身控制模块等。

LDO具有较好的温度稳定性和抗振动能力,能够适应汽车环境的复杂性。

4. 工业控制在工业自动化控制领域,LDO广泛应用于PLC(可编程逻辑控制器)、传感器和执行器等设备中,用于稳定电源。

LDO具有快速响应的特点,能够满足工业控制系统对电源的高要求。

二、LDO的选型设计在选择和设计LDO时,需要考虑以下几个关键因素。

1. 输入和输出电压根据实际需求,选择合适的输入和输出电压范围。

输入电压应该大于输出电压,以确保LDO正常工作。

2. 最大输出电流根据需要稳定的负载电流大小,选择具有足够输出电流能力的LDO。

一般来说,LDO的额定输出电流应大于负载电流的1.2倍。

3. Dropout电压根据应用场景的最大允许压降,选择具有较小Dropout电压的LDO。

Dropout电压越小,LDO在输入电压接近输出电压时的稳定性越好。

4. 噪声和纹波根据应用的需求,选择具有较低噪声和纹波的LDO。

LDO设计小结1

t1

1 1 V tsr Cpar BWcl BWcl Isr

由上面两个表达式可以看出,要降低输出电压抖动,主要办法是提高 LDO 的闭环 带宽,减小 pass element 的寄生电容,同时增大对该寄生电容的驱动能力。 (Iout-max, Cout 和 Vesr 等指标通常是给定的) 2.4 电流效率 该指标反映了 LDO 给负载提供输出电流的效率,其表达式如下:

Vtr- max Iout max t1 Vesr Cout

其中 Iout-max 表示 LDO 的最大输出电流,Cout 表示电路的输出电容(包括片内寄生 电容,外接旁路电容及负载电容等) , Vesr 表示输出电容的 ESR 带来的电压抖动, t1 与电路的闭环带宽及内部转换速率(与 pass element 的寄生电容相关)有关,具体表 达式如下:

PSR Vout Vdd

我们先来考虑 DC 情况下的 PSR,从电源到输出有两条通路,如下图所示:

Vdd Vref Vout

Aop

Vg

ቤተ መጻሕፍቲ ባይዱ

R1

R2

图中红色的两条虚线表示了从电源到输出的两条通路,一条是从电源经过 pass element 直接到输出,另一条是输出经过由电阻分压网络,误差放大器和 pass element 构成的反馈环路后回到输出。由此可以得到如下关系式:

2.1 线路及负载调整率 线路调整率即输出电压随输入电压的变化情况, 而负载调整率指输出电压随负载电 流的变化情况,这两个指标都对应电路的稳态响应。具体公式如下:

Line regulation = VO VO Load regulation = VI IO

通常情况下,输出电压随输入电压的降低及负载电流的增大而降低。在实际仿真中 发现,要想提高线路及负载调整率,较为直接的方法是提高环路增益。 2.2 drop-out 电压 drop-out 电压表征了使输出电压稳定的最小输入电压,其大小即为此时输入输出之 间的电压差。显然,减小 drop-out 电压可以提高 LDO 的电流效率。下面分析两种典型 电路的 drop-out 电压,即 pass element 分别用 PMOS 和 NMOS 的情况,如下图所示:

LDO经验总结

L D O经验总结(总2页)--本页仅作为文档封面,使用时请直接删除即可----内页可以根据需求调整合适字体及大小--自己总结的一些LDO应用经验,供大家参考。

很多观点可能不是很精确,欢迎工程师排砖交流!一、选型1、确定电路需要的电压类型是正电压还是负电压。

正电压的器件较多,负电压的器件可以考虑LM2991(较多大公司使用);2、确定电路的输出电压、负载电流和输入电压(注意输入电压和负载电流都需要降额80%考虑)3、确定电路的最大、最小输入-输出电压差;电路的最大、最小输入-输出电压差应该满足器件要求;4、单板PCB、结构尺寸和生产线对封装形式的要求;5、确定电路的电性能指标要求(如静态电流、精度、纹波、效率等);器件的指标应该满足电路指标的要求,并且考虑温度对各种性能指标的影响;6、确定器件的输出电容以及ESR值,如果器件对输出电容以及ESR有特殊要求,考虑公司现有器件是否满足要求;7、其他要求(如电路是否需要使能控制端、价格因素等)。

二、外围元件1、输入电容输入电容的主要作用是对调整器的输入进行滤波,另外输入电容也可以抵消输入线较长时引入的寄生电感效应,防止电路产生自激振荡;所以调整器输入端一般采用两个电容并联的设计。

较大的电容提供滤波作用,一般取10uF左右;较小电容提供消除振荡作用,取值一般为1uF,实际应用中一般选用,位置尽量靠近调整器的输入管角。

如果输入端采用工频变压器和二极管整流电路,为了提高滤波性能,输入端的滤波电容值应该取的更大一些。

输入电容除了考虑容值外,纹波电流额定值也必须考虑,输入电容的纹波电流应小于器件手册给出的额定值,电路的纹波电流可以用下面的公式简单计算:Iripple=PI×Vp×f×C 其中:Iripple:输入电容的纹波电流Vp:纹波电压的峰-峰值C:输入电容值f:为纹波电压的频率,一般取100KHz再考虑以上因素的时候还应该注意温度对电容特性的影响,如钽电容其电容值以及纹波电流额定值都随着温度的升高而降低。

低压差线性稳压器(LDO)浅谈

技术文库欲打印此文章,从您的浏览器菜单中选择“文件”后再选“打印”。

低压差线性稳压器(LDO)浅谈上网时间: 2006年07月25日摘要:本文论述了低压差线性稳压器(LDO )的基本原理和主要参数,并介绍LDO 的典型应用和国内发展概况。

引言便携电子设备不管是由交流市电经过整流(或交流适配器)后供电,还是由蓄电池组供电,工作过程中,电源电压都将在很大范围内变化。

比如单体锂离子电池充足电时的电压为4.2V ,放完电后的电压为2.3V ,变化范围很大。

各种整流器的输出电压不仅受市电电压变化的影响,还受负载变化的影响。

为了保证供电电压稳定不变,几乎所有的电子设备都采用稳压器供电。

小型精密电子设备还要求电源非常干净(无纹波、无噪声),以免影响电子设备正常工作。

为了满足精密电子设备的要求,应在电源的输入端加入线性稳压器,以保证电源电压恒定和实现有源噪声滤波[1]。

一.LDO 的基本原理低压差线性稳压器(LDO)的基本电路如图1-1所示,该电路由串联调整管VT 、取样电阻R1和R2、比较放大器A 组成。

取样电压加在比较器A 的同相输入端,与加在反相输入端的基准电压Uref 相比较,两者的差值经放大器A 放大后,控制串联调整管的压降,从而稳定输出电压。

当输出电压Uout 降低时,基准电压与取样电压的差值增加,比较放大器输出的驱动电流增加,串联调整管压降减小,从而使输出电压升高。

相反,若输出电压Uout 超过所需要的设定值,比较放大器输出的前驱动电流减小,从而使输出电压降低。

供电过程中,输出电压校正连续进行,调整时间只受比较放大器和输出晶体管回路反应速度的限制。

应当说明,实际的线性稳压器还应当具有许多其它的功能,比如负载短路保护、过压关断、过热关断、反接保护等,而且串联调整管也可以采用MOSFET 。

二.低压差线性稳压器的主要参数1.输出电压(Output Voltage)输出电压是低压差线性稳压器最重要的参数,也是电子设备设计者选用稳压器时首先应考虑的参数。

LDO设计讨论

Error Amplifier

Error Amplifier

1

1 R oCL

原理:通过该结构将两个次极点(P2和P3) 推向高频,P1为主极点,miller补偿和零

2

1 R oa C par

点在大电流负载时起作用

R oa R 3 || (1/ g m7)

3

1 (1 g m6R 2 )R1Cc

电容倍乘原理

2019/11/10

Ceq (n1)

Ic

(1 k x SVn1

)

(1

kx

)Cc

12

LDO频率补偿

3. 零点--极点跟踪补偿

Dc gain:>72dB, PM:86° UGB: around 1khz Iout:0~100mA

2019/11/10

原理:利用可变电阻Zc和补偿 电容Cc构成的零点抵消输出 端极点

2019/11/10

8

LDO频率补偿

1. 使用ESR补偿

原理:使用ESR电阻与Co构成的零点抵消一个次极点影响

Pdom

: pd

1 R oCo

2

1 R ESR C b

3

1 R oa C par

Zesr : esr

1 R esrCo

(Co Cb )

频率响应最差情况发生在最大负载时,此时主极点处于较高频率,高频极点有可能落在

zf

1 R F1C F1

15

LDO频率补偿

电路实现

CL:2.2uF Iout:0~3A Dc gain:>60dB, PM:>60° PSRR: -30dB@20khz@10mA

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

由于 Iout-max 通常是设计指标给定的, 所以提高 Ieff 的唯一方法就是降低 LDO 的静态 电流 Iq。 2.5 输出噪声 该指标反映了 LDO 的噪声特性,这里做一点简单的分析,一个典型 LDO 的噪声源 如下图所示:

2 Vn,out

t1

1 1 V tsr Cpar BWcl BWcl Isr

由上面两个表达式可以看出,要降低输出电压抖动,主要办法是提高 LDO 的闭环 带宽,减小 pass element 的寄生电容,同时增大对该寄生电容的驱动能力。 (Iout-max, Cout 和 Vesr 等指标通常是给定的) 2.4 电流效率 该指标反映了 LDO 给负载提供输出电流的效率,其表达式如下:

Vref

Vref

上图左边的电路利用 PMOS 作为 pass element,显然 drop-out 电压即为 PMOS 管的饱和压降 Vdsat,大约为 200mv 左右。而对于右边的电路,由于采用 NMOS 管作 为 pass element,drop-out 电压受到了误差放大器输出电压的限制(误差放大器的输出 电 压 最 大 只 能达 到 其电 源 电 压 , 即 LDO 的 输 入 电 压 ) , 大 小为 NMOS 的 Vgs (Vdsat+Vth) 。虽然利用 NMOS 管作为 pass element 的 drop-out 电压比 PMOS 大, 但其某些性能比 PMOS 好,例如 PSRR(后文会详细介绍) 。并且,利用一些特殊的电 路技术可以使 NMOS 管作为 pass element 的 drop-out 电压与 PMOS 相同。比如,可 以额外引入 charge pump 电路来产生误差放大器的电源电压(该电压高于 LDO 的输入 电压) ,从而降低对 LDO 输入电压的要求。 2.3 输出电压抖动 该指标描述了 LDO 的瞬态响应特性,具体表达式如下:

2.1 线路及负载调整率 线路调整率即输出电压随输入电压的变化情况, 而负载调整率指输出电压随负载电 流的变化情况,这两个指标都对应电路的稳态响应。具体公式如下:

Line regulation = VO VO Load regulation = VI IO

通常情况下,输出电压随输入电压的降低及负载电流的增大而降低。在实际仿真中 发现,要想提高线路及负载调整率,较为直接的方法是提高环路增益。 2.2 drop-out 电压 drop-out 电压表征了使输出电压稳定的最小输入电压,其大小即为此时输入输出之 间的电压差。显然,减小 drop-out 电压可以提高 LDO 的电流效率。下面分析两种典型 电路的 drop-out 电压,即 pass element 分别用 PMOS 和 NMOS 的情况,如下图所示:

和电路的等效输出阻抗。将 Add 的表达式代入上式,化简可得

PSR Vout Add 1 Vdd 1 Aop gmRout Aop

由上式可以看出,如果只采用简单的 LDO 结构(即上图所示的结构) ,提高 PSR 的方法只有两个,一是增大误差放大器的开环增益,二是提高环路的反馈系数。对于第 二种方法,可以理解为随着输出电压的增大(参考电压保持不变) ,PSR 越差。 上面的表达式是一种理想情况,即电源仅通过 pass element 影响输出,实际上电 源会通过运放影响输出, 需要考虑电源到运放输出端的小信号增益 Ap, 此时对 PMOS 进行小信号分析,可得

从上式可以看出, 提高 PSR 的另一个方法是让 Ap=1, 具体做法可以参考 05 年 CICC 的文章《 A Low Noise, High Power Supply Rejection Low Dropout Regulator for Wireless System-on-Chip》 。 二.尝试的几种结构 在进行 LDO 设计时,最重要的也是最先需要考虑的是稳定性,因为这是 LDO 正常 工作的前提。如果不能保证环路具备足够的相位裕度,很容易在输出引起震荡。并且这 种稳定性需要在整个负载变化范围内均得到保证,因为实际应用中 LDO 的负载电流是 在不断变化的。 在传统的 LDO 设计中, 通常会在片外的输出端接一个大电容 (一般在 uF 这个量级) , 这个电容通常有两个作用,其一是在输出端形成一个很大的主极点,通过该主极点降低 环路的带宽,从而保证环路的稳定性。其二是降低输出电压的瞬态抖动,这从前面给出 的输出电压瞬态变化的表达式中可以看出。 尽管有外接电容,LDO 环路的稳定性仍然很难保证,尤其是在驱动电流范围较大 (100mA 以上)时,输出极点,环路增益及带宽都强烈依赖于负载的变化。因此在早 期的 LDO 设计中,通常会引入外接电容的 ESR 构成的零点来对相位裕度进行补偿。这 也就是为什么早期的 LDO 芯片数据手册中都会给出 ESR 的安全范围。 正因为这种 LDO 对外接电容的 ESR 有很高的要求,所以后来的 LDO 设计中逐渐抛弃了这种做法,而是 采用一些高级的电路技术对环路进行补偿,例如极点分离技术,零极点抵消技术等。 再后来,很多人开始研究无需外接电容的 LDO,这一领域的兴起主要基于以下两 点原因: (1)考虑到现代集成电路的发展方向是 soc(system on chip) ,省掉 LDO 片外的大电容

越低,噪声越好。另外,在条件允许的情况下,提高参考电压的大小可以减小电路的噪 声。 (2)bandgap 及误差放大器的噪声对电路总的噪声影响较大,是电路设计中可以重点优 化的对象。其中 bandgap 的噪声优化主要有两种方式,第一种方法是直接在 bandgap 的输出端加 RC 滤波,这种方法只有当 RC 较大时效果比较明显,所以需要占用很大的 电路面积。第二种方法是从电路结构和参数上对噪声进行优化,这需要消耗很大的电路 功耗。而误差放大器的噪声优化一般也需要消耗电路功耗。 (3)减小 R1 也可以降低电路的噪声,但代价是增大了 LDO 的静态工作电流。 (4)在仿真中发现,要想设计低噪声的 LDO,主要代价就是电路功耗,所以设计瓶颈在 于如何在给定的功耗约束下完成噪声的优化。 2.6 电源抑制比 该指标反映了 LDO 的输出电压对电源电压的扰动的抑制能力, 在这里的定义如下:

(Vdd Vg )gmpRout (Vdd Vout )

化简,得 1 gmpRout

Vout Vg gmpRout Add ApgmpRout Vdd Vdd

即 Add gmpRout (1 Ap ) 1 将该式代入前面 PSR 的表达式,可得

PSR

1 Ap Vout gmpRout (1 Ap ) 1 1 Vdd 1 AopgmRout AopgmRout Aop

是很有必要的。 (2)很多应用场合下,负载电路的电流消耗并不大(<20mA) ,这种情况下即使没有片外 的大电容,也可以保证 LDO 的瞬态性能。 对于没有外接电容的 LDO,其补偿方式通常是在环路内部产生主极点,同时结合 其它补偿技术来完成。 1.BIA + Cascode 补偿结构 该结构参考的是 07 年的 JSSC《A Transient-Enhanced Low-Quiescent Current Low-Dropout Regulator With Buffer Impedence Attenuation》 。 BIA 是 Buffer Impedence Attenuation 的简称。这种结构的基本思想如下图所示:

LDO 设计小结

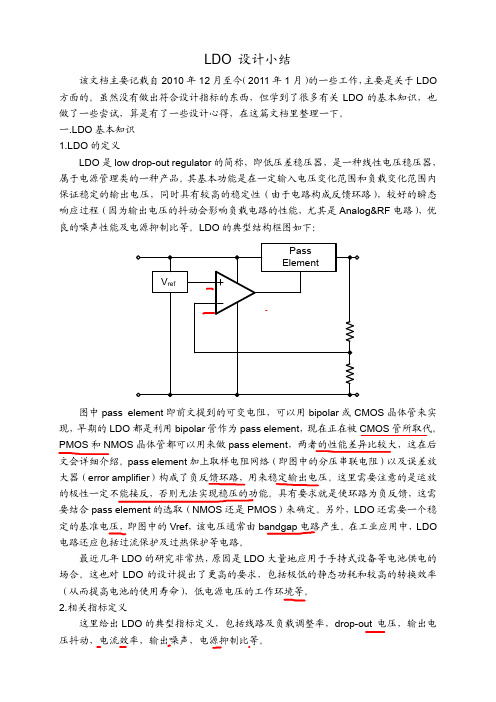

该文档主要记载自 2010 年 12 月至今 (2011 年 1 月) 的一些工作, 主要是关于 LDO 方面的。虽然没有做出符合设计指标的东西,但学到了很多有关 LDO 的基本知识,也 做了一些尝试,算是有了一些设计心得,在这篇文档里整理一下。 一.LDO 基本知识 1.LDO 的定义 LDO 是 low drop-out regulator 的简称,即低压差稳压器,是一种线性电压稳压器, 属于电源管理类的一种产品。 其基本功能是在一定输入电压变化范围和负载变化范围内 保证稳定的输出电压,同时具有较高的稳定性(由于电路构成反馈环路) ,较好的瞬态 响应过程(因为输出电压的抖动会影响负载电路的性能,尤其是 Analog&RF 电路) ,优 良的噪声性能及电源抑制比等。LDO 的典型结构框图如下:

R1 R1 2 1 Vn,R1 1 R2 R2

2

2 2 (注意,在推导时,Vn,op 和Vn,bg 需要乘以电路的闭环增益,近似为环路反馈系数的

倒数。将 R1 和 R2 的噪声折算到输出时利用电流噪声进行推导) 从上式可以看出,电路的输出噪声主要与 bandgap 的输出噪声,误差放大器的等 效输入噪声,电阻 R1 的输出噪声及分压电阻的比例有关。由此可以得到下面几个结论: (1)若参考电压不变,则 R1 和 R2 的比例越小,噪声性能越好。即 LDO 的稳定输出电压

Pass Element Vref

图中 pass element 即前文提到的可变电阻,可以用 bipolar 或 CMOS 晶体管来实 现, 早期的 LDO 都是利用 bipolar 管作为 pass element, 现在正在被 CMOS 管所取代。 PMOS 和 NMOS 晶体管都可以用来做 pass element,两者的性能差异比较大,这在后 文会详细介绍。pass element 加上取样电阻网络(即图中的分压串联电阻)以及误差放 大器(error amplifier)构成了负反馈环路,用来稳定输出电压。这里需要注意的是运放 的极性一定不能接反,否则无法实现稳压的功能。具有要求就是使环路为负反馈,这需 要结合 pass element 的选取(NMOS 还是 PMOS)来确定。另外,LDO 还需要一个稳 定的基准电压,即图中的 Vref,该电压通常由 bandgap 电路产生。在工业应用中,LDO 电路还应包括过流保护及过热保护等电路。 最近几年 LDO 的研究非常热, 原因是 LDO 大量地应用于手持式设备等电池供电的 场合。这也对 LDO 的设计提出了更高的要求,包括极低的静态功耗和较高的转换效率 (从而提高电池的使用寿命) ,低电源电压的工作环境等。 2.相关指标定义 这里给出 LDO 的典型指标定义,包括线路及负载调整率,drop-out 电压,输出电 压抖动,电流效率,输出噪声,电源抑制比等。