ISE约束UCF编辑的操作介绍

摘要:本文主要通过一个实例具体介绍ISE中通过编辑UCF文件来对FPGA设计进行约束,主要涉及到的约束包括时钟约束、群组约束、逻辑管脚约束以及物理属性约束。

Xilinx FPGA设计约束的分类

Xilinx定义了如下几种约束类型:

? “Attributes and Constraints”

? “CPLD Fitter”

? “Grouping Constraints”

? “Logical Constraints”

? “Physical Constraints”

? “Mapping Directives”

? “Placement Constraints”

? “Routing Directives”

? “Synthesis Constraints”

? “Timing Constraints”

? “Configuration Constraints”

通过编译UCF(user constraints file)文件可以完成上述的功能。

还是用实例来讲UCF的语法是如何的。

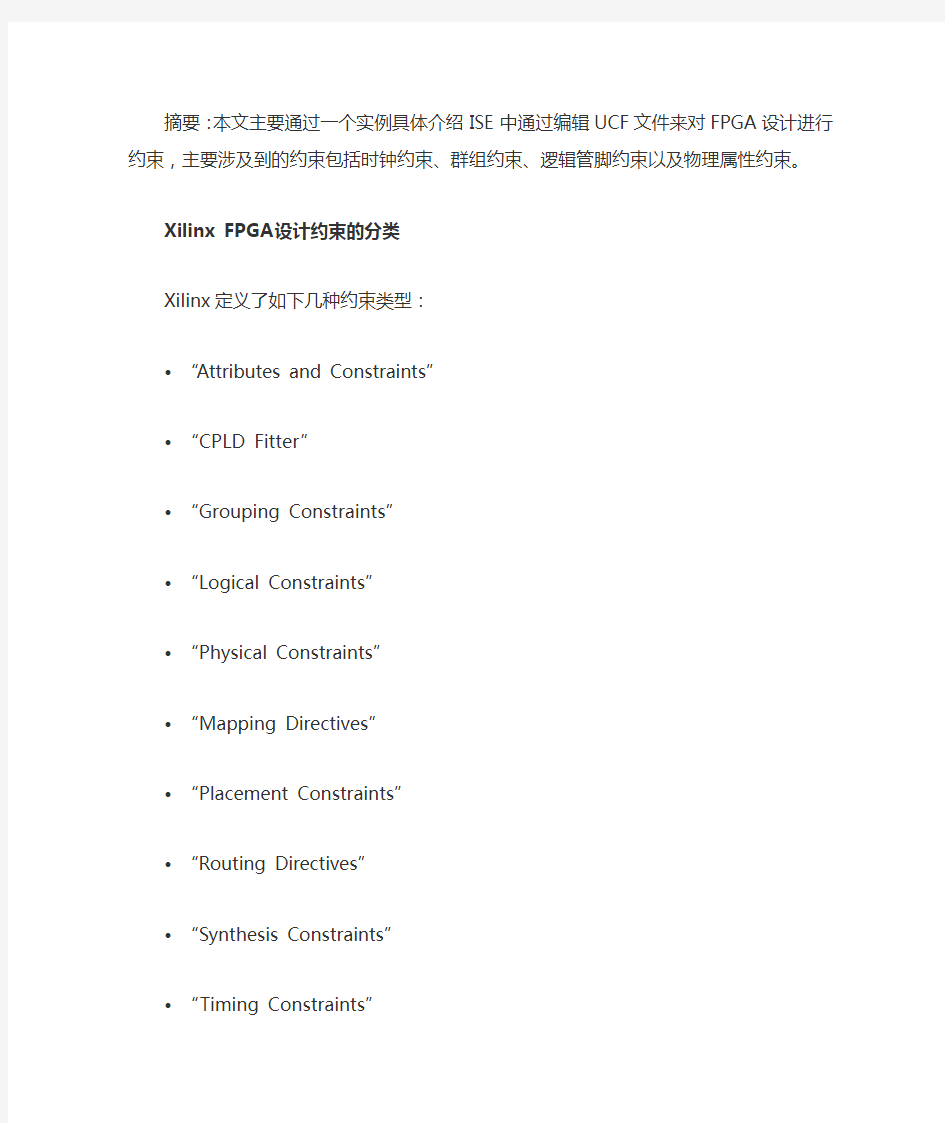

图1 RTL Schematic

图1 是顶层文件RTL图,左侧一列输入,右侧为输出,这些端口需要分配相应的FPGA管脚。

1: NET "pin_sysclk_i" LOC = AD12 | TNM_NET = pin_sysclk_i;

2: TIMESPEC TS_pin_sysclk_i = PERIOD "pin_sysclk_i" 15 ns HIGH 50 %; 3:#

4: NET "pin_plx_lreset_n_i" LOC = B18;

5:#

6: NET "pin_plx_lhold_i" LOC = C17;

7: NET "pin_plx_lholda_o" LOC = D17 | SLEW = FAST;

8:#

9: NET "pin_plx_ads_n_i" LOC = E18;

10:NET "pin_plx_ads_n_i"OFFSET = IN 6.3 ns AFTER "pin_sysclk_i"HIGH; 11:#

12: NET "pin_plx_lw_r_n_i" LOC = E9;

13:NET "pin_plx_lw_r_n_i"OFFSET = IN 6.3 ns AFTER "pin_sysclk_i"HIGH; 14:#

15: NET "pin_plx_blast_n_i" LOC = D18;

16:NET "pin_plx_blast_n_i"OFFSET = IN 6.3 ns AFTER "pin_sysclk_i"HIGH; 17:#

18: NET "pin_plx_lad_io<0>" LOC = AD13 | SLEW = FAST | TNM = LAD;

19: NET "pin_plx_lad_io<1>" LOC = AC13 | SLEW = FAST | TNM = LAD;

20: NET "pin_plx_lad_io<2>" LOC = AC15 | SLEW = FAST | TNM = LAD;

21: NET "pin_plx_lad_io<3>" LOC = AC16 | SLEW = FAST | TNM = LAD;

22: NET "pin_plx_lad_io<4>" LOC = AA11 | SLEW = FAST | TNM = LAD;

23: NET "pin_plx_lad_io<5>" LOC = AA12 | SLEW = FAST | TNM = LAD;

24: NET "pin_plx_lad_io<6>" LOC = AD14 | SLEW = FAST | TNM = LAD;

25: NET "pin_plx_lad_io<7>" LOC = AC14 | SLEW = FAST | TNM = LAD;

26: NET "pin_plx_lad_io<8>" LOC = AA13 | SLEW = FAST | TNM = LAD;

27: NET "pin_plx_lad_io<9>" LOC = AB13 | SLEW = FAST | TNM = LAD;

28: NET "pin_plx_lad_io<10>" LOC = AA15 | SLEW = FAST | TNM = LAD; 29: NET "pin_plx_lad_io<11>" LOC = AA16 | SLEW = FAST | TNM = LAD; 30: NET "pin_plx_lad_io<12>" LOC = AC11 | SLEW = FAST | TNM = LAD; 31: NET "pin_plx_lad_io<13>" LOC = AC12 | SLEW = FAST | TNM = LAD; 32: NET "pin_plx_lad_io<14>" LOC = AB14 | SLEW = FAST | TNM = LAD; 33: NET "pin_plx_lad_io<15>" LOC = AA14 | SLEW = FAST | TNM = LAD; 34: NET "pin_plx_lad_io<16>" LOC = D12 | SLEW = FAST | TNM = LAD;

35: NET "pin_plx_lad_io<17>" LOC = E13 | SLEW = FAST | TNM = LAD;

36: NET "pin_plx_lad_io<18>" LOC = C16 | SLEW = FAST | TNM = LAD;

37: NET "pin_plx_lad_io<19>" LOC = D16 | SLEW = FAST | TNM = LAD;

38: NET "pin_plx_lad_io<20>" LOC = D11 | SLEW = FAST | TNM = LAD;

39: NET "pin_plx_lad_io<21>" LOC = C11 | SLEW = FAST | TNM = LAD;

40: NET "pin_plx_lad_io<22>" LOC = E14 | SLEW = FAST | TNM = LAD;

41: NET "pin_plx_lad_io<23>" LOC = D15 | SLEW = FAST | TNM = LAD; 42: NET "pin_plx_lad_io<24>" LOC = D13 | SLEW = FAST | TNM = LAD; 43: NET "pin_plx_lad_io<25>" LOC = D14 | SLEW = FAST | TNM = LAD; 44: NET "pin_plx_lad_io<26>" LOC = F15 | SLEW = FAST | TNM = LAD; 45: NET "pin_plx_lad_io<27>" LOC = F16 | SLEW = FAST | TNM = LAD; 46: NET "pin_plx_lad_io<28>" LOC = F11 | SLEW = FAST | TNM = LAD; 47: NET "pin_plx_lad_io<29>" LOC = F12 | SLEW = FAST | TNM = LAD; 48: NET "pin_plx_lad_io<30>" LOC = F13 | SLEW = FAST | TNM = LAD; 49: NET "pin_plx_lad_io<31>" LOC = F14 | SLEW = FAST | TNM = LAD; 50: TIMEGRP "LAD" OFFSET = IN 6.4 ns AFTER "pin_sysclk_i" HIGH;

51: TIMEGRP "LAD" OFFSET = OUT 3.1 ns BEFORE "pin_sysclk_i" HIGH; 52:#

53: NET "pin_plx_ready_n_o" LOC = F18 | SLEW = FAST;

54: NET "pin_plx_ready_n_o" OFFSET = OUT 4.2 ns BEFORE "pin_sysclk_i" HIGH;

55:#

56: NET "pin_plx_bterm_n_o" LOC = D10 | SLEW = FAST;

57: NET "pin_plx_bterm_n_o" OFFSET = OUT 4.2 ns BEFORE "pin_sysclk_i" HIGH;

58:#

59: NET "pin_led_o<0>" LOC = D22;

60: NET "pin_led_o<1>" LOC = C22;

61: NET "pin_led_o<2>" LOC = E21;

62: NET "pin_led_o<3>" LOC = D21;

63: NET "pin_led_o<4>" LOC = C21;

64: NET "pin_led_o<5>" LOC = B24;

65: NET "pin_led_o<6>" LOC = C20;

66: NET "pin_led_o<7>" LOC = B23;

表1. UCF example

对上面的UCF文件进行一些注释:

该UCF文件主要是完成了管脚的约束、时钟的约束,以及组的约束。

第一、二行:主要定义了时钟以及对应的物理管脚。

第一行,端口pin_sysclk_i 分配到FPGA管脚AD12,并放到了 pin_sysclk_i group中。那如何得知是AD12的管脚呢,请看图2,FPGA管脚AD12 是一个66MHz的外部时钟。FPGA的开发板肯定有电路原理图供你分配外部管脚。

图2,电路原理图

第二行:时钟说明:周期15ns,占空比50%。关键词TIMESPEC(Timing Specifications),即时钟说明。一般的语法是:

TIMESPEC "TSidentifier"=PERIOD "timegroup_name" value [units];

其中TS identifier用来指定TS(时钟说明)的唯一的名称。

第七行:pin_plx_lholda_o 连接至物理管脚D17,并配置该管脚电平变化的速率。关键词:SLEW,用来定义电平变化的速率的,一般语法是:

NET "top_level_port_name" SLEW="value";

其中value = {FAST|SLOW|QUIETIO}, QUIETIO仅用在Spartan-3A。

第十行:定义pin_plx_ads_n_i 输入跟时钟的关系。OFFSET IN和OFFSET OUT 的约束。OFFSET IN 定义了数据输入的时间和接收数据时钟沿(capture Edge)的关系。

一般的语法是:OFFSET = IN value VALID value BEFORE clock

OFFSET = OUT value VALID value AFTER clock

图3 时序图(OFFSET IN)

例子:

NET "SysCLk" TNM_NET = "SysClk";

TIMESPEC "TS_SysClk" = PERIOD "SysClk" 5 ns HIGH 50%; OFFSET = IN 5 ns VALID 5 ns BEFORE "SysClk";

上面的定义了基于SysClk的全局OFFSET IN的属性。时序可看图3.

图4 时序图(OFFSET OUT)

例子:

NET "ClkIn" TNM_NET = "ClkIn";

OFFSET = OUT 5 ns AFTER "ClkIn";

上面设置主要是定了了时钟跟数据的时间关系,时序图4。可以看到这时一种全局定义,Data1 和Data2输出时间都受到OFFSET = OUT 5 ns AFTER "ClkIn" 的约束。如果需要单独定义输出端口的OFFSET OUT的,需要制定相应的NET,可参考表1中的第57行。

第18至49行:pin_plx_lad_io<*> 被归到了名称为LAD的TMN(Timing name),这个可以说是GROUP的约束。这样往往给约束带来方便,不用一个一个的NET 或者INST进行约束。

第50至51行:对TIMEGRP 是LAD进行OFFSET IN和OUT的定义。

在时序约束中,在这里还未提及FROM TO的约束。FROM TO的约束主要是用来两个同步模块之间的时间关系的约束。在这里不做深入的讨论。

至此,基本上把一般的UCF文件的作用进行了注释。

注:一般的时间的约束需要通过静态的时序分析,然后再设定相应PERIOD,OFFSET IN 以及OFFEET OUT等的时间参数。

当然在例子中还没有涉及到区域的约束。下面会试图说一下。

ISE进行综合后会将设计代码生成相应的逻辑网表,然后经过translate过程,转换到Xilinx特定的底层结构和硬件原语,MAP过程就是将映射到具体型号的器件上,最后就是就是布线和布局的操作了。

区域的约束相当于将布局过程中指定特定型号的器件的位置,这完全可以通过FloorPlanner的GUI界面进行设置,用图形界面设置完后,配置信息会放到UCF 中,这里只介绍UCF的使用。

例如:

INST "Done" LOC = "SLICE_X32Y163" ; #Done映射为一个寄存器,映射到SLICE_X32Y163的位置上。(32,163)相当于一个坐标,可以用FloorPlanner进行查看。

INST"BRAM4/BU2/U0/blk_mem_generator/valid.cstr/ramloop[0].ram.r /v4_init.ram/TRUE_DP.SINGLE_PRIM.TDP"LOC = "RAMB16_X2Y22" ; #RAM16的一个映射。

又例如,X,Y,Z是对应的是寄存器。现在想把它们放在一个指定的区域中,我可以这样写,

INST“X”AREA_GROUP = reg;

INST“X”AREA_GROUP = reg;

INST“X”AREA_GROUP = reg;

AREA_GROUP reg RANGE = SLICE_X1Y1 :SLICE_X1Y6;

注:如何查看INST中的名称呢?在ISE中 Timing constraints editor中可以查看。

注:NET,LOC,TNM_NET,TIMESPEC,PERIOD,OFFSET,IN,OUT,SLEW,HIGH等都是关键字,UCF文件是大小敏感的,端口名称必须和源代码中的名字一致,且端口名字不能和关键字一样。但是关键字NET是不区分大小写的。

其实上述都是约束的入门的内容,如果要想深入的了解的话,请参考Ref1。

笔者也是初学者,如果有什么不对的地方,请批评指正。

ISE 约束文件的基本操作

1.约束文件的概念

FPGA设计中的约束文件有3类:用户设计文件(.UCF文件)、网表约束文件(.NCF文件)以及物理约束文件(.PCF文件),可以完成时序约束、管脚约束以及区域约束。3类约束文件的关系为:用户在设计输入阶段编写UCF文件,然后UCF文件和设计综合后生成NCF文件,最后再经过实现后生成PCF 文件。本节主要介绍UCF文件的使用方法。

UCF文件是ASC 2码文件,描述了逻辑设计的约束,可以用文本编辑器和Xili nx约束文件编辑器进行编辑。NCF约束文件的语法和UCF文件相同,二者的区别在于:UCF文件由用户输入,NCF文件由综合工具自动生成,当二者发生冲突时,以UCF文件为准,这是因为UCF的优先级最高。PCF文件可以分为两个部分:一部分是映射产生的物理约束,另一部分是用户输入的约束,同样用户约束输入的优先级最高。一般情况下,用户约束都应在UCF文件中完成,不建议直接修改NCF文件和PCF文件。

2.创建约束文件

约束文件的后缀是.ucf,所以一般也被称为UCF文件。创建约束文件有两种方法,一种是通过新建方式,另一种则是利用过程管理器来完成。

第一种方法:新建一个源文件,在代码类型中选取“Implementation Constrains File”,在“File Name”中输入“one2two_ucf”。单击“Next”按键进入模块选择对话框,选择模块“one2two”,然后单击“Next”进入下一页,再单击“Finish”按键完成约束文件的创建。

第二种方法:在工程管理区中,将“Source for”设置为“Synthesis/Implementati on”。“Constrains Editor”是一个专用的约束文件编辑器,双击过程管理区中“Us er Constrains”下的“Create Timing Constrains”就可以打开“Constrains Edito r”,其界面如图所示:

图启动Constrains Editor引脚约束编辑

在“Ports”选项卡中可以看到,所有的端口都已经罗列出来了,如果要修改端口和FPGA管脚的对应关系,只需要在每个端口的“Location”列中填入管脚的编号即可。例如在UCF文件中描述管脚分配的语法为:

NET “端口名称” LOC = 引脚编号;

需要注意的是,UCF文件是大小敏感的,端口名称必须和源代码中的名字一致,且端口名字不能和关键字一样。但是关键字NET是不区分大小写的。

3.编辑约束文件

在工程管理区中,将“Source for”设置为“Synthesis/Implementation”,然后双击过程管理区中“User Constrains”下的“Edit Constraints (Text)”就可以打开约束文件编辑器,如下图所示,就会新建当前工程的约束文件。

图用户约束管理窗口

UCF文件的语法说明

1.语法

UCF文件的语法为:

{NET|INST|PIN} "signal_name" Attribute;

其中,“signal_name”是指所约束对象的名字,包含了对象所在层次的描述;“At tribute”为约束的具体描述;语句必须以分号“;”结束。可以用“#”或“/* */”添加注释。需要注意的是:UCF文件是大小写敏感的,信号名必须和设计中保持大小写一致,但约束的关键字可以是大写、小写甚至大小写混合。例如:

NET "CLK" LOC = P30;

“CLK”就是所约束信号名,LOC = P30;是约束具体的含义,将CLK信号分配到FPGA的P30管脚上。

对于所有的约束文件,使用与约束关键字或设计环境保留字相同的信号名会产生错误信息,除非将其用" "括起来,因此在输入约束文件时,最好用" "将所有的信号名括起来。

2.通配符

在UCF文件中,通配符指的是“*”和“?”。“*”可以代表任何字符串以及空,“?”则代表一个字符。在编辑约束文件时,使用通配符可以快速选择一组信号,当然这些信号都要包含部分共有的字符串。例如:

NET "*CLK?" FAST;

将包含“CLK”字符并以一个字符结尾的所有信号,并提高了其速率。

在位置约束中,可以在行号和列号中使用通配符。例如:

INST "/CLK_logic/*" LOC = CLB_r*c7;

把CLK_logic层次中所有的实例放在第7列的CLB中。

3.定义设计层次

在UCF文件中,通过通配符*可以指定信号的设计层次。其语法规则为:* 遍历所有层次

Level1/* 遍历level1及以下层次中的模块

Level1/*/ 遍历level1种的模块,但不遍历更低层的模块

例4-5 根据图4-75所示的结构,使用通配符遍历表4-3所要求的各个模块。

图层次模块示意图

表要求遍历的符号列表

管脚和区域约束语法

LOC约束是FPGA设计中最基本的布局约束和综合约束,能够定义基本设计单元在FPGA芯片中的位置,可实现绝对定位、范围定位以及区域定位。此外,LOC还能将一组基本单元约束在特定区域之中。LOC语句既可以书写在约束文件中,也可以直接添加到设计文件中。换句话说,ISE中的FPGA底层工具编辑器(FPGA Editor)、布局规划器(Floorplanner)和引脚和区域约束编辑器的主要功能都可以通过LOC语句完成。

LOC语句语法

INST "instance_name " LOC = location;

其中“location”可以是FPGA芯片中任一或多个合法位置。如果为多个定位,需

要用逗号“,”隔开,如下所示:

LOC = location1,location2,...,locationx;

目前,还不支持将多个逻辑置于同一位置以及将多个逻辑至于多个位置上。需要说明的是,多位置约束并不是将设计定位到所有的位置上,而是在布局布线过程中,布局器任意挑选其中的一个作为最终的布局位置。

范围定位的语法为:

INST “instance_name” LOC=location:location [SOFT];

常用的LOC定位语句如表4-4所列。

表常用的LOC定位语句

使用LOC完成端口定义时,其语法如下:

NET "Top_Module_PORT" LOC = "Chip_Port";

其中,“Top_Module_PORT”为用户设计中顶层模块的信号端口,“Chip_Port”为FPGA芯片的管脚名。

LOC语句中是存在优先级的,当同时指定LOC端口和其端口连线时,对其连线约束的优先级是最高的。例如,在图4-76中,LOC=11的优先级高于LOC=38。

图LOC优先级示意图

2.LOC属性说明

LOC语句通过加载不同的属性可以约束管脚位置、CLB、Slice、TBUF、块RA M、硬核乘法器、全局时钟、数字锁相环(DLL)以及DCM模块等资源,基本涵盖了FPGA芯片中所有类型的资源。由此可见,LOC语句功能十分强大,表4-5列出了LOC的常用属性。

表LOC语句常用属性列表

可参考xilinx实例教程操作。

监控系统操作说明

监控系统操作说明 一、监控键盘操作 1、登录 在确定键盘的电源接通且与矩阵数据线(网线)连接好的情况下,开启电源开关,键盘液晶屏幕显示用户登录界面,输入用户名和密码进行登录。(见说明书P20)用户名:1 密码:000000 2、切换操作 1)要在X号监视器上显示XX号摄像机图像按如下步骤操作: 输入要使用的监视器号码(监视器左下角显示,MON-XX)+MON键,此时键盘显示屏显示监视器X;再按所要查看的摄像机号码+CAM键,此时键盘显示屏显示摄像机XX;完成操作。 2)在同一监视器上顺序切换摄像机 先选中要使用的监视器(按监视器号码+CAM键),然后按键盘上的PREV/NEXT 键,摄像机将按向前/向后的顺序在显示器上显示。 3)在同一监视器上自动循环显示 在1号监视器上循环显示1~14号摄像机图像 启动:1+MACRO,结束:11+MACRO; 在2号监视器上循环显示15~28号摄像机图像 启动:2+MACRO,结束:12+MACRO; 在3号监视器上循环显示29~42号摄像机图像 启动:3+MACRO,结束:13+MACRO; 在4号监视器上循环显示43~57号摄像机图像

启动:4+MACRO,结束:14+MACRO; 3、前端摄像机控制 选择要操作的摄像机(摄像机编号+CAM键),根据需要摇动操作键盘上的控制杆,完成摄像机上下左右等动作,扭动操作杆完成变焦等动作。 可控摄像机点表如下: 4、解锁 操作键盘长时间不用会自动锁定,不能操作,键盘显示屏会提示先解锁再操作,如果重新使用,先按键盘上的LOCK键,即可解锁。 1)摄像机锁定:按LOCK键锁定选定监视器显示的摄像机,按SHIFT+LOCK 解除摄像机锁定。 2)监视器锁定:按数字+LOCK键锁定选定摄像机,按数字+SHIFT+LOCK解除监视器锁定。 二、录像机操作 1、登录 1)先将电脑与交换机连接,将电脑的IP地址及子网掩码修改到与硬盘录像机同一地址段,方可登录。 IP地址:192.0.0.5 子网掩码:255.255.255.0

教学一体机操作方法

一、使用教学一体机的操作流程 第1步:按下教学一体机右下方面板上的电源键,电脑投影同步开机。 第2步:开展正常的教学工作。 第3步:下课关机:按下教学一体机右下方面板上的电源键,电脑投影同步关机。或通过计算机系统的关机程序,关闭计算机。关闭计算机后,投影仪会在充分冷却后自动关机。 第4步:教师关闭黑板 二、使用教学一体机的过程中可能出现的问题及解决办法 1、计算机在使用过程中,出现蓝屏或死机等故障。 解决办法:教学一体机右侧后方有一个总电源开关,找到那个开关,关闭总电源,过20秒后重新打开总电源,再通过正常方法开机。 2、计算机在使用过程中,出现触摸屏定位不准现象。 解决办法:用面纸擦除一体机屏幕四周边框内侧的灰尘,特别是下方的粉笔灰。 三、教学一体机其他功能及使用方法 1、直接播放U盘中的音乐或视频。 操作过程:把U盘直接接入到一体机右方外接的USB接口中,把信号源选择设置为“多媒体”,使用一体机面板按键,即可播放声音或视频。

2、使用笔记本电脑以投影仪为输出设备。 操作过程:用一根VGA线连接笔记本与投影仪右侧的VGA输入接口,再调节相应的输入源即可。 3、使用教学一体机开展班级文娱活动。 可以使用本机的视频播放功能开展文娱活动,使用方法:安装“酷我k歌”软件,通过该软件提前从网上下载准备演出的歌曲;使用一个外置麦克风接入电脑的音频输入插孔(在一体机右侧方有一个6.5的插头),这种方法只能使用一只麦克风。如果需要使用两只麦克风,需要另外安装一个功放设备,把麦克风接在功放上,再把功放的输出接到电脑音频输入线上。 还可以使用一台DVD,一台功放,把DVD的AV输出线连接到一体机右方的AV输入线接口。 它集合了电子白板、短焦投影、功放、音响、计算机、视频展台、中控等多媒体设备功能于一体,极大的满足了学校信息化教学对媒体设备的需求。 为了更快的掌握这个崭新的教学平台,使之能够快速的融入到我校的现代化教育教学当中,我在经历了两小时的技术培训后,结合自身已有的经验开始了自行研究。这篇文章就是根据我在使用东泰(DTIT)多媒体教学一体机中所累积的经验总结而成的,如果在专业术语或是操作方法上存在错误,还望各位教师多多包涵,并给予指正。

动环监控软件操作手册

深圳市通讯威科技有限公司 EP-MEVP SYSTEM 动力环境集中监控系统 安装使用说明书 版本

目录

第一章软件的安装、卸载、升级 软件安装对计算机的配置要求 CPU 主频或以上 内存最低要求256MB [推荐 512MB] 硬盘系统驱动器上需要 100MB以上的可用空间 显示 Super VGA (1024x768) 或更高分辨率的显示器(颜色设置为 256 色或更高) 鼠标 Microsoft 鼠标或兼容的指点设备 操作系统: Windows 2000 Windows XP Windows 7 (管理员权限) Microsoft Windows Server 2003 Microsoft Windows Server 2008 软件的安装 首先将光盘放入光驱,执行光盘目录【安装软件】里面的,系统会弹出安装界面 (如下图) 注意: Framework 软件包和中文语言包,是必需安装的。如果不安装 .NET软件包,程序将无法正常运行。如果您的系统已经安装过语言包,系统会自动跳到下一安装环节,进行软件的安装。 单击【接受】系统将自动安装组件以及动环监控系统软件。如下图: 组件和中文语言包安装完成后会弹出如下界面安装动环监控系统软件。【如下图】 单击【下一步】选择你所要软件安装的目录【下一步】一般软件默认安装路径为C:\Program Files\综合机房动力环境监控系统\ 点击【磁盘开销】可以了解软件所安装目录的磁盘空间大小,如果选择的空间不够安装软件请选择其它目录安装,选择目录后点击【确定】。 点击【任何人】或者【只有我】,如果使用本电脑的任何人都可以使用此软件的话请选择【任何人】单击【下一步】 安装中选择安装动环监控模块,如下图 单击安装完成后,点击【关闭】即可。 桌面将自动增加快捷方式。 软件的卸载 首先,打开 [我的电脑] \ [控制面板] 双击 [添加和删除程序] 在[目前安装的程序]栏中找到动环监控系统软件,选中然后按[更改/删除]按钮。 单击【删除】可直接卸载动环监控系统软件。 备注: 以下几个是软件运行必须具备的控件,请勿删除,如果不小心删除了,请重新安装软件. 软件的升级 如果您从我公司获取了更新版本的软件想升级的话,对于使用Access数据库的用户,请安装以下步骤进行操作。

ISE约束UCF编辑的操作介绍

摘要:本文主要通过一个实例具体介绍ISE中通过编辑UCF文件来对FPGA设计进行约束,主要涉及到的约束包括时钟约束、群组约束、逻辑管脚约束以及物理属性约束。 Xilinx FPGA设计约束的分类 Xilinx定义了如下几种约束类型: ? “Attributes and Constraints” ? “CPLD Fitter” ? “Grouping Constraints” ? “Logical Constraints” ? “Physical Constraints” ? “Mapping Directives” ? “Placement Constraints” ? “Routing Directives” ? “Synthesis Constraints” ? “Timing Constraints” ? “Configuration Constraints” 通过编译UCF(user constraints file)文件可以完成上述的功能。 还是用实例来讲UCF的语法是如何的。 图1 RTL Schematic

图1 是顶层文件RTL图,左侧一列输入,右侧为输出,这些端口需要分配相应的FPGA管脚。 1: NET "pin_sysclk_i" LOC = AD12 | TNM_NET = pin_sysclk_i; 2: TIMESPEC TS_pin_sysclk_i = PERIOD "pin_sysclk_i" 15 ns HIGH 50 %; 3:# 4: NET "pin_plx_lreset_n_i" LOC = B18; 5:# 6: NET "pin_plx_lhold_i" LOC = C17; 7: NET "pin_plx_lholda_o" LOC = D17 | SLEW = FAST; 8:# 9: NET "pin_plx_ads_n_i" LOC = E18; 10:NET "pin_plx_ads_n_i"OFFSET = IN 6.3 ns AFTER "pin_sysclk_i"HIGH; 11:# 12: NET "pin_plx_lw_r_n_i" LOC = E9; 13:NET "pin_plx_lw_r_n_i"OFFSET = IN 6.3 ns AFTER "pin_sysclk_i"HIGH; 14:# 15: NET "pin_plx_blast_n_i" LOC = D18; 16:NET "pin_plx_blast_n_i"OFFSET = IN 6.3 ns AFTER "pin_sysclk_i"HIGH; 17:# 18: NET "pin_plx_lad_io<0>" LOC = AD13 | SLEW = FAST | TNM = LAD; 19: NET "pin_plx_lad_io<1>" LOC = AC13 | SLEW = FAST | TNM = LAD; 20: NET "pin_plx_lad_io<2>" LOC = AC15 | SLEW = FAST | TNM = LAD; 21: NET "pin_plx_lad_io<3>" LOC = AC16 | SLEW = FAST | TNM = LAD; 22: NET "pin_plx_lad_io<4>" LOC = AA11 | SLEW = FAST | TNM = LAD; 23: NET "pin_plx_lad_io<5>" LOC = AA12 | SLEW = FAST | TNM = LAD; 24: NET "pin_plx_lad_io<6>" LOC = AD14 | SLEW = FAST | TNM = LAD; 25: NET "pin_plx_lad_io<7>" LOC = AC14 | SLEW = FAST | TNM = LAD; 26: NET "pin_plx_lad_io<8>" LOC = AA13 | SLEW = FAST | TNM = LAD; 27: NET "pin_plx_lad_io<9>" LOC = AB13 | SLEW = FAST | TNM = LAD; 28: NET "pin_plx_lad_io<10>" LOC = AA15 | SLEW = FAST | TNM = LAD; 29: NET "pin_plx_lad_io<11>" LOC = AA16 | SLEW = FAST | TNM = LAD; 30: NET "pin_plx_lad_io<12>" LOC = AC11 | SLEW = FAST | TNM = LAD; 31: NET "pin_plx_lad_io<13>" LOC = AC12 | SLEW = FAST | TNM = LAD; 32: NET "pin_plx_lad_io<14>" LOC = AB14 | SLEW = FAST | TNM = LAD; 33: NET "pin_plx_lad_io<15>" LOC = AA14 | SLEW = FAST | TNM = LAD; 34: NET "pin_plx_lad_io<16>" LOC = D12 | SLEW = FAST | TNM = LAD; 35: NET "pin_plx_lad_io<17>" LOC = E13 | SLEW = FAST | TNM = LAD; 36: NET "pin_plx_lad_io<18>" LOC = C16 | SLEW = FAST | TNM = LAD; 37: NET "pin_plx_lad_io<19>" LOC = D16 | SLEW = FAST | TNM = LAD; 38: NET "pin_plx_lad_io<20>" LOC = D11 | SLEW = FAST | TNM = LAD; 39: NET "pin_plx_lad_io<21>" LOC = C11 | SLEW = FAST | TNM = LAD; 40: NET "pin_plx_lad_io<22>" LOC = E14 | SLEW = FAST | TNM = LAD;

教学软件功能介绍

教学软件功能介绍 1、开机步骤: (1)把IC卡放在刷卡处,听见“滴”一声,代表主机柜门已开。 (2)在听见“滴”一声后,用手轻按一下柜门,柜门就会打开。 (3)在柜门打开后,按下“上课”键,老师就可以正常上课了。 (4)在上课结束后,按下“下课”键,把柜门关好,老师就可以离开了。注:如果老师在上课中要使用实物展台、换页器、麦克风、激光笔、鼠标、键盘、遥控器、等可以在(2)结束后,再打开下面柜门。 2、手势 桌面手势(以下手势均使用三根或三根以上手指) (1).手指向上推动—--窗口最大化 (2).手指向下滑动----窗口最小化 (3).手指横向滑动----窗口切换 (4).两只手手指向下滑动----所有窗口最小化 (5).手掌从白板最下端向上滑动----所打开窗口平铺 (6).两只手指向外拉动实现图片或字体的放大/缩小 软件内手势 (1).手掌平铺滑动实现板擦功能 (2).手掌平铺停留实现聚光灯功能 (3).两只手指拖动实现无限漫游功能 (4).手掌双击白板软件实现回到桌面功能

3、软件下方功能键说明 工具按钮 按钮功能描述 新建页面:在当前文档下可新建4种背景页面,点击下拉菜单可进行选择:新建白色、黑 色、图片或屏幕批注页等页面 硬笔:类似圆珠笔书写效果 排笔:类似毛笔书写效果 智能笔:用户在绘制线段或图像时,笔画可自动识别并转换为直线或近似的几何图形 多笔书写:用户在使用此按钮时即可多人同时书写,最多支持10人同时书写 插入图形:直接插入标准图形,插入时可根据要求进行拖拉到合适大小 插入图片或视频:用户可点击该按钮将图片或mp3、wav、swf、asf、rmvb、avi等格式文档 直接插入到当前页面,并保存到文档中,下次再打开该文档,所插入内容不变。 插入文本框:用户可点击该按钮后,在当前页面任意位置进行拖动,生成文本框,并可使用键 盘、软键盘和手写识别等书写工具进行文本输入;当点击文本框数秒后出现右键功能,可对文 本框进行“装入文本文件”、剪切、复制、粘贴等操作,还可以对文本框内容进行设置。如字 体、字体颜色、背景颜色、透明背景 填充几何图形:该按钮用来填充几何图形颜色,需要与填充几何图形按钮连用 笔迹选择工具:该工具是用来选取当前页面上的笔迹,选取笔迹后可以对该笔迹进行拖动和缩 放等调整。使用该工具会出现此样线段,用该线段对需要选取的笔迹进行圈选,该笔迹变成空 心说明已被选中。如图: 移动工具:该工具用来移动当前页面上的几何图形、文本框、图片等 旋转与缩放:该工具用来对当前页面上的几何图形、图片等内容进行旋转或重设大小(手势识别 中两根手指将图片向两端或中间移动时即为此功能)

赛灵思(Xilinx)FPGA用户约束文件的分类和语法说明

赛灵思(Xilinx)FPGA用户约束文件的分类和语法说明 FPGA设计中的约束文件有3类:用户设计文件(.UCF文件)、网表约束文件(.NCF文件)以及物理约束文件(.PCF文件),可以完成时序约束、管脚约束以及区域约束。3类约束文件的关系为:用户在设计输入阶段编写UCF文件,然后UCF文件和设计综合后生成NCF文件,最后再经过实现后生成PCF 文件。UCF文件是ASC 2码文件,描述了逻辑设计的约束,可以用文本编辑器和Xilinx约束文件编辑器进行编辑。NCF约束文件的语法和UCF文件相同,二者的区别在于:UCF文件由用户输入,NCF文件由综合工具自动生成,当二者发生冲突时,以UCF文件为准,这是因为UCF的优先级最高。PCF文件可以分为两个部分:一部分是映射产生的物理约束,另一部分是用户输入的约束,同样用户约束输入的优先级最高。一般情况下,用户约束都应在UCF文件中完成,不建议直接修改NCF文件和PCF文件。约束文件的后缀是.ucf,所以一般也被称为UCF文件。创建约束文件有两种方法,一种是通过新建方式,另一种则是利用过程管理器来完成。第一种方法:新建一个源文件,在代码类型中选取ImplementaTIon Constrains File,在File Name中输入约束文件的名称。单击Next按键进入模块选择对话框,选择要约束的模块,然后单击Next进入下一页,再单击Finish按键完成约束文件的创建。第二种方法:在工程管理区中,将Source for设置为Synthesis/ImplementaTIon。Constrains Editor是一个专用的约束文件编辑器,双击过程管理区中User Constrains下的Create TIming Constrains就可以打开Constrains Editor。需要注意的是,UCF文件是大小敏感的,端口名称必须和源代码中的名字一致,且端口名字不能和关键字一样。但是关键字NET是不区分大小写的。UCF文件的语法说明:1.语法UCF文件的语法为:{NET|INST|PIN} signal_name Attribute;其中,signal_name是指所约束对象的名字,包含了对象所在层次的描述;Attribute为约束的具体描述;语句必须以分号;结束。可以用#或添加注释。需要注意的是:UCF文件是大小写敏感的,信号名必须和设计中保持大小写一致,但约束的关键字可以是大写、小写甚至大小写混合。例如:NET CLK LOC = P30;CLK就是所约束信号名,LOC = P30;是约束具体的含义,将CLK信号分配到FPGA的P30管脚上。对于所有的约束文件,使用与

锁相环pll工作原理及verilog代码

锁相环的组成和工作原理 #1 1.锁相环的基本组成 . 许多电子设备要正常工作, 通常需要外部的输入信号与内部的振荡信 许多电子设备要正常工作, 号同步,利用锁相环路就可以实现这个目的。 号同步,利用锁相环路就可以实现这个目的。 锁相环路是一种反馈控制电路, 锁相环路是一种反馈控制电路,简称锁相环 )。锁相环的特点是 (PLL)。锁相环的特点是:利用外部输入的 )。锁相环的特点是: 参考信号控制环路内部振荡信号的频率和相 位。 因锁相环可以实现输出信号频率对输入信号频率的自动跟踪, 所以锁 因锁相环可以实现输出信号频率对输入信号频率的自动跟踪, 相环通常用于闭环跟踪电路。锁相环在工作的过程中, 相环通常用于闭环跟踪电路。锁相环在工作的过程中,当输出 于闭环跟踪电路 信号的频率与输入信号的频率相等时, 信号的频率与输入信号的频率相等时,输出电压与输入电压保 持固定的相位差值,即输出电压与输入电压的相位被锁住,这 持固定的相位差值,即输出电压与输入电压的相位被锁住, 就是锁相环名称的由来。 就是锁相环名称的由来。 ( ) 锁相环通常由鉴相器 PD) 环路滤波器 LF) 、 ( ) 和压控振荡器 VCO) ( ) 三部分组成, 所示。 三部分组成,锁相环组成的原理框图如图 8-4-1 所示。 锁相环中的鉴相器又称为相位比较器, 它的作用是检测输入信号和输 锁相环中的鉴相器又称为相位比较器, 出信号的相位差,并将检测出的相位差信号转换成 uD(t)电压信号 出信号的相位差, ) 输出, 该信号经低通滤波器滤波后形成压控振荡器的控制电压 u(t) 输出, , C ) 对振荡器输出信号的频率实施控制。 对振荡器输出信号的频率实施控制。 施控制 2.锁相环的工作原理 . 锁相环中的鉴相器通常由模拟乘法器组成, 利用模拟乘法器组成的鉴 锁相环中的鉴相器通常由模拟乘法器组成, 相器电路如图 8-4-2 所示。 所示。

推荐广东省会计电算化通用教学软件操作步骤--截图版(精华)

会计电算化通用教学软件操作教程 第一节总账 例1、以系统管理员(Admin)的身份注册系统管理。 启动系统管理→系统→注册→管理员:admin 密码:空 编号姓名口令 001 赵超 1 002 王刚 2 权限→操作员→增加 例3、设置账套信息。 为北京友联科技有限责任公司建立666号账套。启用日期为2006年1月。 账套→建立→账套号:666→账套名:北京友联科技有限责任公司→启用时间:2006年1月

例4、设置单位信息。 单位名称:北京友联科技有限责任公司; 简称:友联科技 例5、确定核算类型 本币代码:RMB 本币名称:人民币企业类型:工业 行业性质:新会计制度科目账套主管:[001] 赵超 不选中“按行业性质预置科目” 修改行业性质(选“新会计制度科目”)→账套主管:001,赵超→不选择‘“按行业性质预置科目” 例6、确定分类信息。假设对客户、供应商、存货不分类,有外币核算。 例7、确定编码方案。假设科目编码级次为4—2—2—2—2,其他编码级次采用默认

值。 例8、设置数据精度。所有小数位均设置为2位。 例9、启用总帐子系统。 例10、设置编号为“002”的操作员“王刚”具有“总帐”、“财务报表”、“现金管理”的全部权限。 权限→权限→选择666账套→王刚→增加→双击:总帐、UFO报表、现金管理→确定→退出★先选账套后选人。

例11、以“赵超”的身份注册进入会计电算化通用教学软件。 启动会计电算化通用教学软件→进入注册(控制台)→用户名:001→密码:1→账套:666(北京友联科技)→会计年度:2006→日期:2006-01-01 部门编码部门名称部门编码部门名称 1 管理部 2 财务部 3 采购部 4 销售部 基础设置→机构设置→部门档案→增加→输入数据→单击“保存” 例13、按以下资料设置职员档案。

监控系统操作流程

开发区监控系统操作流程 一、大屏监控上屏 1.1将大屏专用电脑中4200软件“”进入系统中如下图所示: 1.2选择右下方全屏按钮进行放大(默认监控视频2分钟进行轮巡播放),如果退出全屏按键盘“ESC”键。 1.3在机柜中视频处理器上将输出模式调成全屏缩放“启用”(按1次旋钮进入菜单—输出模式—全屏缩放—按旋钮进行切换 —按“ESC”退出);如下图所示: 二、大屏视频图像(播放素材)上屏 2.1 将监控系统退出或最小化(按电脑键盘“ESC”—最少化窗口);

2.2 打开桌面上LED演播室软件“”,进入软件窗口如下: 2.3 如果保存过播放文件直接打开文件选择“播放”按钮,如果 没有创建需要新建文件; 2.4 将准备好的视频资料通过U盘或其它复制到电脑上,并知道 路径; 2.5 新建一个“正常节目页”,在“正常节目页”中新建“文 件窗”在右侧增加之前准备素材资料; 2.6 按“播放”按钮 2.7在机柜中视频处理器上将输出模式调成“全屏缩放”禁止(按 1次旋钮进入菜单—输出模式—全屏缩放—按旋钮进行切换—按“ESC”退出);如下图所示: 2.8 具体操作视频见文件夹“大屏视频操作说明”; 三、大屏时间控制 3.1 大屏通电开关时间通过“时控开关”设置,设备需要对1#1 单元后电气箱内时控开关设备同时也要对物业机柜内“时控开关” 设置同步开关时间,具体参考“时控开关说明书”

四、监控回放保存录像(以下操作在录像机中) 4.1 先确定需要调录像视频画面是那一画面; 4.2 右击鼠标---选择“回放”如下图所示 4.3 绘画下图找开密码; 4.4 输入完后进入回放界面,选择日期、可以选择其它通道,可 同时对四个画面进行回放; 4.5 对调取录像视频保存至U盘上,首先将U盘安装至录像机USB

SAM中文说明书

SAMlight教程一.Samlight软件安装 1.软件安装过程 SAMlight 点击“sc_sam_setup_complete_v_XXXXXX.exe”文件,然后运行它便可以进入自动安装,您可以在各种Windows操作系统中进行安装,建议安装完成后重新启动计算机。 安装过程 双击图标安装。出现下列窗口1. .点击继续安装。2

1 / 83 后,点击继续安装。.选中3

,要改变路径单击”C:\scaps\sam2d按钮,然后选择软件安装位置。再点.上图中软件默认的安装路径在“4击按钮继续安装。2 / 83 .点击继续安装5 .在文件复制结束后出现的窗口内点击。完成安装。6,在紧接着弹出窗口中点击 驱动。点击图标会弹出以下对话框,要求用户当第一次连接打标机时,计算机会自动引导您安装USB7.输入控制卡密码,输入密码后即可正常使用。 xxxx”。在说明书中找到相应密码输入即“#(密码代号出现在对话框标题栏,格式可){了。

如果你没有看到以上窗口,或在屏幕左至此您应当可以使用软件对控制卡进行操作evaluation” only for 表明软件与硬件之间的通讯version 到下角看“demo - } 确认控制卡有足够的电出现故障。关闭软件,力,然后重新启动软件。*密码查询: *培训说明书查询: 8、软件USB连接问题 当我们打开SAMlight软件时,有时软件无法打开,会出现DEMO演示版的打标软件,这时我们就要看USB驱动是否安装好. 首先,我们用鼠标右键点击“我的电脑”,点“属性”。选择“硬件”—“设备管理器”如图 3 / 83

PLL(锁相环)电路原理及设计 [收藏]

PLL(锁相环)电路原理及设计[收藏] PLL(锁相环)电路原理及设计 在通信机等所使用的振荡电路,其所要求的频率范围要广,且频率的稳定度要高。无论多好的LC振荡电路,其频率的稳定度,都无法与晶体振荡电路比较。但是,晶体振荡器除了可以使用数字电路分频以外,其频率几乎无法改变。如果采用PLL(锁相环)(相位锁栓回路,PhaseLockedLoop)技术,除了可以得到较广的振荡频率范围以外,其频率的稳定度也很高。此一技术常使用于收音机,电视机的调谐电路上,以及CD唱盘上的电路。 一PLL(锁相环)电路的基本构成 PLL(锁相环)电路的概要 图1所示的为PLL(锁相环)电路的基本方块图。此所使用的基准信号为稳定度很高的晶体振荡电路信号。 此一电路的中心为相位此较器。相位比较器可以将基准信号与VCO (Voltage Controlled Oscillator……电压控制振荡器)的相位比较。如果此两个信号之间有相位差存在时,便会产生相位误差信号输出。 (将VCO的振荡频率与基准频率比较,利用反馈电路的控制,使两者的频率为一致。) 利用此一误差信号,可以控制VCO的振荡频率,使VCO的相位与基准信号的相位(也即是频率)成为一致。 PLL(锁相环)可以使高频率振荡器的频率与基准频率的整数倍的频率相一致。由于,基准振荡器大多为使用晶体振荡器,因此,高频率振荡器的频率稳定度可以与晶体振荡器相比美。 只要是基准频率的整数倍,便可以得到各种频率的输出。 从图1的PLL(锁相环)基本构成中,可以知道其是由VCO,相位比较器,基准频率振荡器,回路滤波器所构成。在此,假设基准振荡器的频率为fr,VCO的频率为fo。 在此一电路中,假设frgt;fo时,也即是VC0的振荡频率fo比fr低时。此时的相位比较器的输出PD 会如图2所示,产生正脉波信号,使VCO的振荡器频率提高。相反地,如果frlt;fo时,会产生负脉波信号。

鸿合一体机教学软件操作试题

鸿合触摸一体机及教学软件(Hitepanel pro) 操作试题 1、怎么样给一体机定位? 通常采用9 点定位法。定位方法:在服务上点击“定位”按钮,如 图右键点击服务后显示癿菜单所示。 2、怎么样启动Hitepanel pro程序。 方法一、双击桌面快捷方式图标; 方法二、开始菜单-------程序------Hiclass-------Hitepanel pro 3、Hitepanel pro的两种模式:备课模式、授课模式。 4、Hitepanel pro软件备课模式下的窗口组成:有标题栏、菜单栏、工具栏、书写区域、功能面板,放映工具栏。 5、利用导入功能,导入ppt文件导入到当前hht文件中。 方法:文件---导入---根据对话框来选择ppt文件路径。 6、利用导出功能,将hht文件导出成自己需要的文件类型。 方法:文件---导出---根据对话框来选择保存文件路径和文件的类型。 7、利用“克隆”命令来“克隆”书写区域的一个对象,知道“克隆 “复制”、“粘贴”的区别。

8、使用“拖动克隆”命令绘制草坪,要求如下: 1)在学科资源中选择——植物——花草将名为草-02image图片拖到 书写区域; 2)将名为草-02image图片选择,然后设置为“拖动克隆” 3)通过拖动来绘制草坪。 9、使用“清页”清除当前页面中的所有对象。 10、新建hht文件,并在其中完成新建、删除页面等操作,要求如下: 1)新建一个文件名为“练习”的hht文件; 2)在该hht文件中分别插入一个“白板页”、一个“屏幕页”、一个“黑 板页”; 3)再利用“上一页”和“下一页”按钮将页面切换到第二张“白板页” 并将该页面的背景设置为黄色; 4)在将页面切换到第一张页面,为该页面添加一个“田字格”的背 景纹理线,利用“漫游功能”(当单手癿三指或三指以上同时落在页面上时,也会切换到页面漫游功能。)实现大屏幕书写。 5)保存该文件于d盘 11、“插入菜单”的练习,操作要求如下: 1)新建文件名为“插入菜单练习”的文件,新建五个“白板页” 页面; 2)在第一个“白板页”页面中插入一个音频文件,并进行播放、暂 停和停在的操作,然后在音频文件图标旁边输入该音频文件的 名字,对文字进行格式编辑;

SEM基本结构及工作原理

SEM基本结构及原理 1 电子束与样品表面的作用 弹性散射:电子束的能量不损失,只改变方向,如背散射电子。 非弹性散射:入射电子熟不进改变方向,也改变能量。包括二次电子,俄歇电子,特征X射线,荧光。 图1 电子束与样品的作用深度示意图

1.1 二次电子Secondary electron 二次电子是指背入射电子轰击出来的核外电子。由于原子核和外层价电子间的结合能很小,当原子的核外电子从入射电子获得了大于相应的结合能的能量后,可脱离原子成为自由电子。如果这种散射过程发生在比较接近样品表层处,那些能量大于材料逸出功的自由电子可从样品表面逸出,变成真空中的自由电子,即二次电子。二次电子来自表面5-10nm的区域,二次电子的逃逸深度很小,在入射电子束处,约为5λ,金属λ=1nm,非金属λ=10nm。 图2 二次电子产量与逃逸深度关系 能量为0-50eV。它对试样表面状态非常敏感,能有效地显示试样表面的微观形貌。由于它发自试样表层,入射电子还没有被多次反射,因此产生二次电子的面积与入射电子的照射面积没有多大区别,所以二次电子的分辨率较高,一般可达到5-10nm。扫描电镜的分辨率一般就是二次电子分辨率。 二次电子产额随原子序数的变化不大,它主要取决于表面形貌,呈以下关系: δ(θ)= δ0Secθ 图3二次电子产量与样品倾斜角度关系 θ增大时δ增大,样品表面的起伏形貌与样品倾转原理一样,形成形貌衬度。 入射电子与样品核外电子碰撞,使样品表面的核外电子被激发出来的电子,是作为SEM的成像信号,代表样品表面的结构特点。

图4 二次电子的检测示意图 1.2 背散射电子back scattered electron 背散射电子是由样品反射出来的初次电子,是弹性散射返回来的电子,其主要特点是:能量很高,有相当部分接近入射电子能量,总能量约占入射点子能量的30%,在试样中产生的范围大,像的分辨率低。背散射电子发射系数随原子序数增大而增大。作用体积随入射束能量增加而增大,但发射系数变化不大。 背散射电子的原子序数衬度: 图5背散射电子产量与原子序数关系 图6背散射电子产量与入射束能量关系

动环监控软件操作手册

动环监控软件操作 手册

深圳市通讯威科技有限公司 EP-MEVP SYSTEM 动力环境集中监控系统 安装使用说明书 版本 2.0

目录 第一章软件的安装卸载升级 ................................. 错误!未定义书签。 1.1软件安装对计算机的配置要求........................ 错误!未定义书签。 1.2软件的安装 ....................................................... 错误!未定义书签。 1.3软件的卸载 ....................................................... 错误!未定义书签。 1.4软件的升级 ....................................................... 错误!未定义书签。第二章软件的基本操作 .......................................... 错误!未定义书签。 2.1登录和进入软件操作界面................................ 错误!未定义书签。 2.2添加/设置/修改/删除硬件设备以及参数设置错误!未定义书签。 2.2.1添加/设置控制器、采集器参数................. 错误!未定义书签。 2.2.2修改/删除硬件设备 .................................... 错误!未定义书签。 2.3监控设置及记录查询 ....................................... 错误!未定义书签。 2.3.1报警方式定义 ............................................. 错误!未定义书签。 2.3.2语音电话报警 ............................................. 错误!未定义书签。 2.3.3短信报警 ..................................................... 错误!未定义书签。 2.3.4监控实时记录 ............................................. 错误!未定义书签。 2.3.5监控报警记录 ............................................. 错误!未定义书签。 2.3.6温湿度数据记录.......................................... 错误!未定义书签。 2.3.7 UPS监控数据记录 ...................................... 错误!未定义书签。 2.3.8 电话短信报警数据记录 .............................. 错误!未定义书签。 2.3.9 空调监控数据记录...................................... 错误!未定义书签。

如何编写ucf文件

.4.1 约束文件的基本操作 1.约束文件的概念 FPGA设计中的约束文件有3类:用户设计文件(.UCF文件)、网表约束文件(.NCF文件)以及物理约束文件(.PCF文件),可以完成时序约束、管脚约束以及区域约束。3类约束文件的关系为:用户在设计输入阶段编写UCF文件,然后UCF文件和设计综合后生成NCF文件,最后再经过实现后生成PCF 文件。本节主要介绍UCF文件的使用方法。 UCF文件是ASC 2码文件,描述了逻辑设计的约束,可以用文本编辑器和Xilinx约束文件编辑器进行编辑。NCF约束文件的语法和UCF文件相同,二者的区别在于:UCF文件由用户输入,NCF文件由综合工具自动生成,当二者发生冲突时,以UCF文件为准,这是因为UCF的优先级最高。PCF文件可以分为两个部分:一部分是映射产生的物理约束,另一部分是用户输入的约束,同样用户约束输入的优先级最高。一般情况下,用户约束都应在UCF文件中完成,不建议直接修改NCF文件和PCF文件。 2.创建约束文件 约束文件的后缀是.ucf,所以一般也被称为UCF文件。创建约束文件有两种方法,一种是通过新建方式,另一种则是利用过程管理器来完成。 第一种方法:新建一个源文件,在代码类型中选取“Implementation Constrains File”,在“File Name”中输入“one2two_ucf”。单击“Next”按键进入模块选择对话框,选择模块“one2two”,然后单击“Next”进入下一页,再单击“Finish”按键完成约束文件的创建。 第二种方法:在工程管理区中,将“Source for”设置为“Synthesis/Implementation”。“Constrains Editor”是一个专用的约束文件编辑器,双击过程管理区中“User Constrains”下的“Create Timing Constrains”就可以打开“Constrains Editor”,其界面如图4-73所示:

绘通软件使用方法基础操作教程

绘通软件使用方法基础操作教程 绘通软件主窗口界面如下: 软件启动后,绘通操作主界面如上图所示: A.标题条 B.菜单 C.常用工具条 D.当前编辑的文件名 E.编辑工具 F.提示条幅大小及鼠标位置 G.工作区 H.标尺 当光标移动到每一个快捷工具按钮上停止不动时,系统会自动提示功能说明或常用的执行方法。 第1节快捷图标说明 一、常用工具 a.新建:创建一个新文档。 b.打开:打开一个已存在的文档。 c.保存:保存当前文档。 d.撤消:撤消最后一步操作。 e.重新执行:重新执行先前已撤消的操作。 f.X方向:横居中。 g.Y方向;纵居中。

h.X/Y方向:横纵同时居中。 i.设置:打印设置。 j.打印:直接打印。 k.关于:显示版本及网址。 二、编辑工具 a. “编辑工具”状态:自动隐藏或关闭编辑工具条。 b. 非编辑状态:进入非编辑状态,此时可以选中界面的某些内容并对选中内容进行拖拽。 c. 文字输入:进入文字输入状态。 d. 直线:可以生成想要的直线。 e. 矩形:可以生成任意矩形。 f. 椭圆:可以生成椭圆形。 g. 多边形:可以画出不规则多边形。 在工作区右击鼠标也可产生与A相同功能的快捷方式,如图B所示。 第2节文字录入和排版 一、文字录入的方法 进入绘通打印软件后,用鼠标在编辑工具栏选择快捷图标,光标变成“A”状态,在排版面内按下鼠标左键,光标即在选定处闪动。 以录入“芯一科技”四个字为例,您只要在鼠标“I”状态下,将光标点放入版面任意地方便可以在此进行输入,而且在输入文字时随时可以对版面内容进行各种修改,只要将光标移到需要修改的文字后面,用键盘上的“BACKSPACE”键便可以把光标前的一个文字删除,然后输入新的文字,后面文字会自动续排。如果想要修改录入的文字块位置,可以先将光标切换到非编辑状态,选中这个文字块,如上图所示,点击选中您想移动的文字块,按鼠标左键不放,拖到版面内您想要的任一位置。 在录入工作完成后,需要修改文字时,用鼠标左键双击需要修改的文字块,使光标变为“I”状态,插入需要修改文字后面,用键盘上的“Backspace”键便可以把光标前的一个文字删除,然后输入新的文字,后面文字会自动续排。 二、字体类型及高宽度的设定与修改 具体操作时有二种方法:1.从菜单栏内单击“文字”出现下拉菜单,选中“文字设置”;2.右击文字块,当出现“修改文本”就选中。都会弹出如下图所示对话框,在“字体信息”内依次设置:字体类型、高度、宽度、字间距、排列方式。

监控系统软件操作说明

监控系统的软件操作说明 服务器部分 一.把组态王运行系统发送到桌面快捷方式. 二.点击运行系统进入运行环境,出现监控系统的主画面,如下图1.1: 监控系统主画面图1.1

三.用户登陆 1.选择用户登陆, 如下图1.2,如:系统管理员登陆(权限最高), 用户登陆图1.2 2.系统管理员可以在用户配置里添加操作员,操作员优先级不需太高,不应 高过900,如下图1.3: 添加操作员图1.3

四.参数校正 在监控系统主画面里”进入参数校正”能够对系统参数标定, 如下图 1.4,当现场值大于计算机的显示值时,增大系统参数,例如:1#放卷张力的现场运行值大于计算机显示1#放卷张力的运行值,就需增加1#放卷张力的运行值系数,使1#放卷张力的现场值和计算机的显示值相等. 参数系数标定图1.4

五.进入一线系统,出现一线系统主画面.如下图1.5: 一线主画面图1.5 1.在一线系统流程图中显示每个工序运行设备的当前值,设定值,标准值,上 限值,下限值和设备运行值的曲线图,.,当前值为设备上仪表当前的运行值,当前值大于上限值或小于下限值时都会产生报警,设定值为设备上仪表所设定的值,标准值为这套工序的标准值,设定值的误差不应超过标准值的5%,例如进入涂覆工序,如下图1.6:

一线涂覆图1.6 2.在一线系统主画面下方的表中显示报警信息. 3.在”参数选择”选择参数编号 4.在”参数设置”里修改参数,进入参数设置后出现参数设置画面,如下图1.7, 在”输入修改品种编号”中输入所要修改配方的编号或点击”上一组”和”下一组”选择,所修改的参数为当前值,上限值和下限值,修改完成后点击”修改后确认并存储”,点击”品种参数列表”后能够在右侧查看到所有参数.

百威软件操作流程说明教学内容

百威软件操作流程说明 【STEP 1】进入后台管理系统 双击进入系统,此时系统提示输入管理员密码,实验室POS机无需密码,直接点击确定进入后台管理系统 【STEP 1】系统主要功能

从系统主界面上可以看出,POS收银后台系统可以实现多种功能。这里主要介绍以下几种。 [商品分类] 商品分类是用来设置本公司所有商品的类别,分类必须明确方便易记。 操作方法:进入此界面后如果要新建大类,就点击新的大类按钮,如果需新建子类,则首先点到需某大类,然后在该大类下面新建子类。需修改类别名称,首先点击该类别然后按修改类别,如需删除某类,首先点击到该类,然后按删除类别即可,删除类别时要注意,如果该类中已有子类或者有商品,则该类不能删除。 以上操作全部作完后,如果需要保存,则按确定按钮,如果不需要保存,则按取消。 [类别代码] 类别代码是用来为每个类别指定一个唯一的代码,代码可以是英文字母,也可是数字,一般不要用中文。

操作方法是:首先点击到该类,然后按设置按钮或双击该类,系统会弹出输入框,可在此框中输入类别代码,输入完后按确定即可。此处需注意的是类别代码不能重复,如果该类中已有商品,类别代码不可更改。 如果打印商品类别列表,可按打印按钮即可进行打印。 [商品档案] 商品档案是用来设置本公司所有的商品信息,包括商品的供应商,条码,价格以及包装规格等。操作方法如下: 进入信息档案 商品档案,出现如下界面。

商品档案可进行新建、删除、打印、复制、导出、表格设置 新建:如果需增加商品档案,可按新建按钮,新建商品档案时首先要选择要新建商品所属的类别,然后再点击新建,系统会弹出新建商品的输入界面。 (基本信息) ◇自编码/条码:表示商品的条形码或者是商品的店内码(要用条形码)◇商品名称:表示商品的名称或者是叫法 ◇单位:表示商品的计量单位,在这里也是商品的最小单位 ◇进价:表示商品的参考进货价格 ◇零售价:表示商品的零售价格 ◇供应商:表示该商品的供货商 ◇所属类别:表示该商品属于哪个类别,以后还可更改 ◇库存上限:表示商品的库存最高限度,如果超过此限度,系统将会在库存积压报表中体现出来 ◇库存下限:表示商品的库存最低限度,如果低于此限度,系统将会在库存不足报表中体现出来 ◇期初库存:表示在开业前该商品的实际库存 ◇此商品只按零售价销售:表示该商品在前台销售时只允许按零售价销