Allegro_SI仿真流程简介

在Allegro 中进行SI 仿真

第一章在Allegro 中准备好进行SI 仿真的PCB 板图1)在Cadence 中进行SI 分析可以通过几种方式得到结果:* Allegro 的PCB 画板界面,通过处理可以直接得到结果,或者直接以*.brd 存盘。

* 使用Specctre Quest 打开*.brd,进行必要设置,通过处理直接得到结果。

这实际与上述方式类似,只不过是两个独立的模块,真正的仿真软件是下面的SigXplore 程序。

* 直接打开SigXplore 建立拓扑进行仿真。

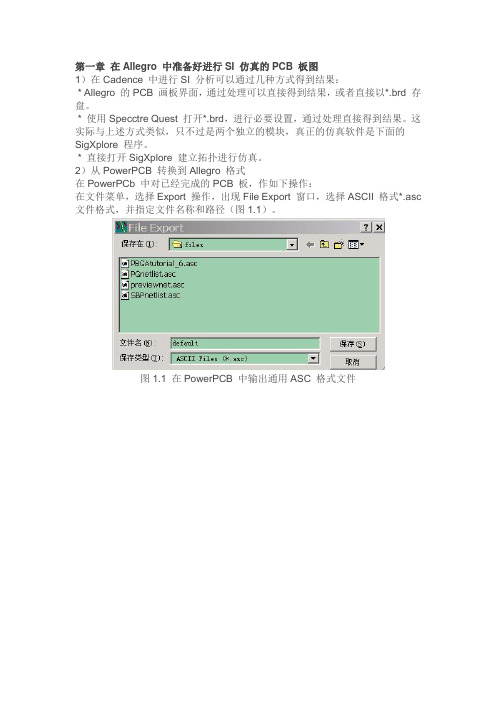

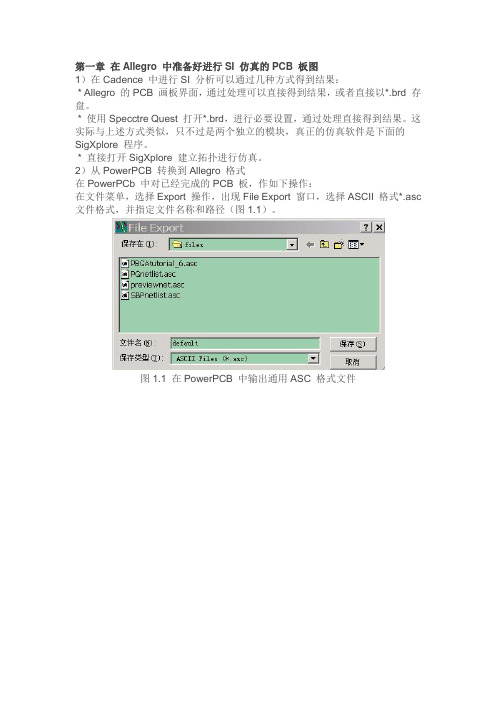

2)从PowerPCB 转换到Allegro 格式在PowerPCb 中对已经完成的PCB 板,作如下操作:在文件菜单,选择Export 操作,出现File Export 窗口,选择ASCII 格式*.asc 文件格式,并指定文件名称和路径(图1.1)。

图1.1 在PowerPCB 中输出通用ASC 格式文件图1.2 PowerPCB 导出格式设置窗口点击图1.1 的保存按钮后出现图1.2 ASCII 输出定制窗口,在该窗口中,点击“Select All”项、在Expand Attributes 中选中Parts 和Nets 两项,尤其注意在Format 窗口只能选择PowerPCB V3.0 以下版本格式,否则Allegro 不能正确导入。

3)在Allegro 中导入*.ascPCB 板图在文件菜单,选择Import 操作,出现一个下拉菜单,在下拉菜单中选择PADS 项,出现PADS IN 设置窗口(图1.3),在该窗口中需要设置3 个必要参数:图1.3 转换阿三次文件参数设置窗口i. 在的一栏那填入源asc 文件的目录ii. 在第二栏指定转换必须的pads_in.ini 文件所在目录(也可将此文件拷入工作目录中,此例)iii. 指定转换后的文件存放目录然后运行“Run”,将在指定的目录中生成转换成功的.brd 文件。

注:pads_in.ini 所在目录路:.Psd_14.2ToolsPCBbin 中。

Allegro165 PCB SI 仿真流程.

Allegro PCB SI:一步一步学会一步一步学会前仿真前仿真 Learn Allegro PCB SI Pre-simulation Step by StepDoc Scope: Cadence 16.5 Doc Number: SFTEC12007 Author: Daniel Zhong Create Date: 2012-04-10 Rev: 1.00Sofer Technology Co., Ltd目录1 Cadence Allegro PCB SI简介 (12)1.1 高速PCB 设计流程 ...................................................... 12 2 Allegro PCB SI的前仿真 . (13)2.1 准备仿真模型和其他需求 (13)2.1.1 获取所使用元器件的仿真模型 (14)2.1.2 获取所使用连接器的仿真模型 (15)2.1.3 获取所使用元器件和连接器的器件手册和用户指南等相关资料 (15)2.1.4 获取所需的规范文档 (15)2.1.5 了解相关电路和接口工作原理 (15)2.1.6 提取与信号完整性相关的要求 (15)2.1.7 预先创建拓扑样本 (16)2.1.8 预先创建相对于不同阈值电压的眼图模板 (16)2.1.9预先创建自定义测量 .................................................. 17 2.2仿真前的规划 .......................................................... 17 2.3关键器件预布局 . ........................................................ 18 2.4 模型加载和仿真配置 .. (18)2.4.1 模型的转化 (19)2.4.2使用SI Design Setup配置 (20)Sofer Technology Co., Ltd2.4.3选择需要配置的信号线 ................................................ 21 2.4.4设置仿真库 ........................................................ 23 2.4.5设置电源和地网络 ................................................... 25 2.4.6设置叠层 .......................................................... 29 2.4.7设置元器件类别 ..................................................... 32 2.4.8为元器件分配和创建模型 .............................................. 33 2.4.9设置差分对 ........................................................ 42 2.4.10设置仿真参数 ..................................................... 47 2.4.11SI Design Audit相关 . ............................................ 55 2.4.12提取拓扑 ........................................................ 57 2.4.13在SigXP 中设置仿真库和仿真参数 ...................................... 59 2.4.14在SigXP 中绘制拓扑 ................................................ 63 2.5 方案空间分析 (73)2.5.1 输出驱动力扫描分析 (76)2.5.2 Stub 长度扫描分析 (78)2.5.3线宽线间距扫描分析 .................................................. 79 2.6 方案到约束规则的转化 . (81)2.6.1 传输线延迟规则的设置 (82)2.6.2 拓扑结构等传输线特性规则的设置 (85)2.6.3 传输线耦合规则的设置 (85)2.6.4拓扑规则在约束管理器中的应用 (86)Sofer Technology Co., Ltd 3 Allegro PCB SI的后仿真 (89)表格表格 1:Routed Interconnect Models参数 (50)表格 2:Simulation 栏眉仿真参数 (52)表格 3:IO Cell Stimulus Edit窗口中的选项 (73)图图 1:传统的PCB 设计流程图 (12)图 2:Allegro PCB SI高速PCB 设计流程图 (13)图 3:眼图模式下的眼图模板 (16)图 4:地址、命令和控制信号传输线拓扑 (17)图 5:RDIMM 的布局示意图 (18)图 6:Model Integrity界面 (19)图 7:使用Model Integrity将IBIS 文件转换至DML 格式 (20)图 8:Cadence Product Choices产品选择器窗口 (21)图 9:Allegro PCB SI GXL界面 (22)图 10:Setup Category Selection窗口 (22)图 11:Setup Xnet Selection窗口 (22)图 12:Allegro PCB SI GXL关于网络设置的提醒框 (23)Sofer Technology Co., Ltd图 13:Setup Library Search Directories窗口 (24)图 14:Setup Library File Extensions窗口 (24)图 15:Setup Working Libraries窗口 (24)图 16:Setup Power and Ground Nets窗口 (25)图 17:Allegro PCB SI GXL电压赋值窗口 (26)图 18:选择“Edit Voltage On Any Net In Design” . (26)图 19:Identify DC Nets窗口。

Allegro流程详解

Allegro流程详解Allegro流程详解⼀.零件建⽴在Allegro 中, Symbol 有五种, 它们分别是Package Symbol 、Mechanical Symbol、Format Symbol、Shape Symbol、Flash Symbol。

每种Symbol 均有⼀个Symbol Drawing File(符号绘图⽂件), 后缀名均为*.dra。

此绘图⽂件只供编辑⽤, 不能给Allegro 数据库调⽤。

Allegro 能调⽤的Symbol 如下:1、Package Symbol⼀般元件的封装符号, 后缀名为*.psm。

PCB 中所有元件像电阻、电容、电感、IC 等的封装类型即为Package Symbol。

2、Mechanical Symbol由板外框及螺丝孔所组成的机构符号, 后缀名为*.bsm。

有时我们设计PCB 的外框及螺丝孔位置都是⼀样的, ⽐如显卡, 电脑主板, 每次设计PCB时要画⼀次板外框及确定螺丝孔位置, 显得较⿇烦。

这时我们可以将PCB的外框及螺丝孔建成⼀个Mechanical Symbol, 在设计PCB 时, 将此Mechanical Symbol 调出即可。

3、Format Symbol由图框和说明所组成的元件符号, 后缀名为*.osm。

⽐较少⽤。

4、Shape Symbol供建⽴特殊形状的焊盘⽤, 后缀为*.ssm。

像显卡上⾦⼿指封装的焊盘即为⼀个不规则形状的焊盘, 在建⽴此焊盘时要先将不规则形状焊盘的形状建成⼀个Shape Symbol, 然后在建⽴焊盘中调⽤此Shape Symbol。

5、Flash Symbol焊盘连接铜⽪导通符号, 后缀名为*.fsm。

在PCB 设计中, 焊盘与其周围的铜⽪相连, 可以全包含, 也可以采⽤梅花辨的形式连接,我们可以将此梅花辨建成⼀个Flash Symbol, 在建⽴焊盘时调⽤此Flash Symbol。

其中应⽤最多的就是Package symbol即是有电⽓特性的零件,⽽PAD是Package symbol构成的基础.Ⅰ建⽴PAD启动Padstack Designer来制作⼀个PAD,PAD按类型分分为:1.Through,贯穿的;2.Blind/Buried,盲孔/埋孔;3.Single,单⾯的.按电镀分:1.Plated,电镀的;2.Non-Plated,⾮电镀的.a.在Parameters选项卡中, Size值为钻孔⼤⼩;Drill symbol中Figure为钻孔标记形状,Charater为钻孔标记符号,Width为钻孔标记得宽度⼤⼩,Height为钻孔标记得⾼度⼤⼩;/doc/c98e12f0f61fb7360b4c654b.html yers选项卡中,Begin Layer为起始层,Default Internal为默认内层,End Layer 为结束层,SolderMask_Top为顶层阻焊, ,SolderMask_Bottom为底层阻焊PasteMask_Top为顶层助焊, PasteMask_Bottom为底层助焊;Regular Pad为正常焊盘⼤⼩值,Thermal Relief为热焊盘⼤⼩值,Anti Pad为隔离⼤⼩值.Ⅱ建⽴Symbol1.启动Allegro,新建⼀个Package Symbol,在Drawing Type中选Package Symbol,在Drawing Name中输⼊⽂件名,OK.2.计算好坐标,执⾏Layout→PIN,在Option⾯板中的Padstack中找到或输⼊你的PAD,Qty代表将要放置的数量,Spacing代表各个Pin之间的间距,Order则是⽅向Right为从左到右,Left为从右到左,Down为从上到下,Up为从下到上;Rotation是Pin要旋转的⾓度,Pin#为当前的Pin脚编号,Text block为⽂字号数;3.放好Pin以后再画零件的外框Add→Line,Option⾯板中的Active Class and Subclass分别为Package Geometry和Silkscreen_Top,Line lock为画出的线的类型:Line直线;Arc弧线;后⾯的是画出的⾓度;Line width为线宽.4.再画出零件实体⼤⼩Add→Shape→Solid Fill, Option⾯板中的Active Class and Subclass分别为Package Geometry和Place_Bound_Top,按照零件⼤⼩画出⼀个封闭的框,再填充之Shape→Fill.5.⽣成零件Create Symbol,保存之Ⅲ编写Device若你从orCad中直接⽣成PCB的话就⽆需编写这个⽂件,这个⽂件主要是⽤来描述零件的⼀些属性,⽐如PIN的个数,封装类型,定义功能等等!以下是⼀个实例,可以参考进⾏编写:74F00.txt(DEVICE FILE: F00 - used for device: 'F00')PACKAGE SOP14 ? 对应封装名,应与symbol相⼀致CLASS IC ? 指定封装形式PINCOUNT 14 ? PIN的个数PINORDER F00 A B Y ? 定義Pin NamePINUSE F00 IN IN OUT ? 定義Pin 之形式PINSWAP F00 A B ? 定義可Swap 之PinFUNCTION G1 F00 1 2 3 ? 定義可Swap 之功能(Gate) PinFUNCTION G2 F00 4 5 6 ? 定義可Swap 之功能(Gate) PinFUNCTION G3 F00 9 10 8 ? 定義可Swap 之功能(Gate) PinFUNCTION G4 F00 12 13 11 ? 定義可Swap 之功能(Gate) PinPOWER VCC; 14 ? 定義電源Pin 及名稱GROUND GND; 7 ? 定義Ground Pin 及名稱END⼆.⽣成⽹表以orCad⽣成⽹表为例:在项⽬管理器下选取所要建⽴⽹络表的电路图系■Tools>>Create Netlist…■或按这个图标:有两种⽅式⽣成⽹表:◆按value值(For Allegro).◆按Device 值(For Allegro)◆按value值建⽴⽹络表1.编辑元件的封装形式在Allegro元件库中value形式为“!0_1uf__bot_!”,在ORCAD元件属性中已有相应value项“0.1uf (bot)”。

Allegro后仿真流程介绍

Allegro后仿真流程介绍作成期:04/01/2009作成人:SOLDERMASKForewordGetting IBIS ModelsPre-WorkingSimulationView WaveformForeword●Getting IBIS Models ●Pre-Working Simulation●●View WaveformForeword前仿真和后仿真的区别前仿真又可以分为布局前仿真和布局后仿真。

前者是在设计的最初阶段,通过SigXplorer建立和验证详细的电气拓扑结构并以此制定出详细的约束规则。

后者是在布局完成的状态下,在布线过程中遇到的具体设计问题需要仿真的过程。

后仿真是在PCB布线完成以后,对已经完成的关键网络进行仿真验证的过程。

可以检查实际的物理执行过程(布局布线)是否违背设计意图;或是已知的改动,通过仿真来验证这种改动给高速设计带来的影响。

本篇文档主要介绍后仿真的操作流程Index●ForewordGetting IBIS Models●Pre-Working●Simulation●View Waveform到下列网站搜索各个公司IBIS模型下载网站/ibis/ibis%20table/models.htm到Google网站直接搜索某个型号的IBIS模型到器件厂商的官方网站下载IBIS模型需要检查是否存在语法错误,或者其他的错误,这一步是必须的。

打开软件Model Integrity,点击Open打开ibs文件,打开文件时软件自动进行Check。

若遇到错误,及时查明原因,一般都是语法错误,所以稍加修改就OK了。

点击此按钮查看报错的行并修改之有10个错误,原因是超出80字符IBIS to DML由于Allegro SI不能够直接对应IBIS模型,需要把IBIS模型转换成Allegro专用的DML模型,两者实际上都是文本文档,只是在描述的方式上有所区别。

右击,在弹出的框内选择IBIS to DML生成dml模型后保存至ibis模型同一路径待所有需要的器件模型全部转换成DML模型以后,要和IBIS模型保存在同一文件夹。

在Allegro 中进行SI 仿真

第一章在Allegro 中准备好进行SI 仿真的PCB 板图1)在Cadence 中进行SI 分析可以通过几种方式得到结果:* Allegro 的PCB 画板界面,通过处理可以直接得到结果,或者直接以*.brd 存盘。

* 使用Specctre Quest 打开*.brd,进行必要设置,通过处理直接得到结果。

这实际与上述方式类似,只不过是两个独立的模块,真正的仿真软件是下面的SigXplore 程序。

* 直接打开SigXplore 建立拓扑进行仿真。

2)从PowerPCB 转换到Allegro 格式在PowerPCb 中对已经完成的PCB 板,作如下操作:在文件菜单,选择Export 操作,出现File Export 窗口,选择ASCII 格式*.asc 文件格式,并指定文件名称和路径(图1.1)。

图1.1 在PowerPCB 中输出通用ASC 格式文件图1.2 PowerPCB 导出格式设置窗口点击图1.1 的保存按钮后出现图1.2 ASCII 输出定制窗口,在该窗口中,点击“Select All”项、在Expand Attributes 中选中Parts 和Nets 两项,尤其注意在Format 窗口只能选择PowerPCB V3.0 以下版本格式,否则Allegro 不能正确导入。

3)在Allegro 中导入*.ascPCB 板图在文件菜单,选择Import 操作,出现一个下拉菜单,在下拉菜单中选择PADS 项,出现PADS IN 设置窗口(图1.3),在该窗口中需要设置3 个必要参数:图1.3 转换阿三次文件参数设置窗口i. 在的一栏那填入源asc 文件的目录ii. 在第二栏指定转换必须的pads_in.ini 文件所在目录(也可将此文件拷入工作目录中,此例)iii. 指定转换后的文件存放目录然后运行“Run”,将在指定的目录中生成转换成功的.brd 文件。

注:pads_in.ini 所在目录路:.Psd_14.2ToolsPCBbin 中。

allegro SI 信号完整性仿真介绍

基于Cadence Allegro SI 16.3的信号完整性仿真信号完整性是指信号在信号线上的质量。

信号具有良好的信号完整性是指当在需要的时候,具有所必需达到的电压电平数值。

差的信号完整性不是由某一因素导致的,而是由板级设计中多种因素共同引起的。

特别是在高速电路中,所使用的芯片的切换速度过快、端接元件布设不合理、电路的互联不合理等都会引起信号的完整性问题。

具体主要包括串扰、反射、过冲与下冲、振荡、信号延迟等。

信号完整性问题由多种因素引起,归结起来有反射、串扰、过冲和下冲、振铃、信号延迟等,其中反射和串扰是引发信号完整性问题的两大主要因素。

反射和我们所熟悉的光经过不连续的介质时都会有部分能量反射回来一样,就是信号在传输线上的回波现象。

此时信号功率没有全部传输到负载处,有一部分被反射回来了。

在高速的PCB中导线必须等效为传输线,按照传输线理论,如果源端与负载端具有相同的阻抗,反射就不会发生了。

如果二者阻抗不匹配就会引起反射,负载会将一部分电压反射回源端。

根据负载阻抗和源阻抗的关系大小不同,反射电压可能为正,也可能为负。

如果反射信号很强,叠加在原信号上,很可能改变逻辑状态,导致接收数据错误。

如果在时钟信号上可能引起时钟沿不单调,进而引起误触发。

一般布线的几何形状、不正确的线端接、经过连接器的传输及电源平面的不连续等因素均会导致此类反射。

另外常有一个输出多个接收,这时不同的布线策略产生的反射对每个接收端的影响也不相同,所以布线策略也是影响反射的一个不可忽视的因素。

串扰是相邻两条信号线之间的不必要的耦合,信号线之间的互感和互容引起线上的噪声。

因此也就把它分为感性串扰和容性串扰,分别引发耦合电流和耦合电压。

当信号的边沿速率低于1ns时,串扰问题就应该考虑了。

如果信号线上有交变的信号电流通过时,会产生交变的磁场,处于磁场中的相邻的信号线会感应出信号电压。

一般PCB板层的参数、信号线间距、驱动端和接收端的电气特性及信号线的端接方式对串扰都有一定的影响。

allegro仿真简单例程 -回复

allegro仿真简单例程-回复什么是allegro仿真?allegro仿真是一种计算机软件工具,用于电子设计自动化(EDA)领域。

它主要用于模拟和验证电路设计,并提供性能评估、信号完整性分析和功耗优化等各种功能。

allegro仿真能够帮助设计工程师预测和解决潜在的电路设计问题,从而提高产品质量和性能。

allegro仿真的应用范围广泛,可用于数字电路、模拟电路、混合信号电路和射频(RF)电路等各种电路设计。

它可以模拟和验证电路的行为,以及与其他外部组件的交互。

除此之外,该仿真工具还提供各种分析和优化功能,帮助设计工程师对设计进行验证和优化,从而减少产品开发周期和成本。

在使用allegro仿真之前,我们需要进行一系列的准备工作。

首先,准备好要仿真的电路设计。

这包括电路的原理图和物理布局。

其次,确保我们已经安装了allegro仿真软件,并具备了基本的操作和使用知识。

最后,我们还需要编写仿真脚本或者配置仿真设置,以便进行仿真分析。

一旦准备工作完成,我们可以开始进行allegro仿真了。

首先,打开allegro 仿真软件,并导入我们的电路设计。

接下来,我们需要根据设计规范和要求,配置仿真设置。

这包括选择仿真模型、设定仿真时间、设置仿真条件等。

这些设置将决定仿真的精确度和结果。

配置完成后,我们可以进行仿真分析了。

allegro仿真工具提供了多种仿真分析模式,例如时域分析、频域分析、傅立叶变换等。

我们可以根据需要选择不同的分析模式,以获得所需的仿真结果。

同时,allegro仿真还允许我们在仿真过程中监测和分析电路的各种信号和性能指标。

当仿真完成后,我们还可以对仿真结果进行进一步的分析和优化。

allegro 仿真工具提供了丰富的数据处理和可视化功能,可以帮助我们分析电路的性能和故障,并进行相应的优化。

例如,我们可以绘制电压-电流曲线、功耗分布图等,以便更好地了解电路的工作情况。

除了仿真分析,allegro仿真还支持其他功能,如信号完整性分析和功耗优化等。

Allegro_PCB_SI 一步一步学会前仿真

Allegro PCB SI:一步一步学会前仿真Learn Allegro PCB SI Pre-simulation Step by StepDoc Scope : Cadence 16.5Doc Number : SFTEC12007Author : Daniel ZhongCreate Date : 2012-04-10Rev : 1.00目录1Cadence Allegro PCB SI简介 (7)1.1高速PCB设计流程 (7)2Allegro PCB SI的前仿真 (8)2.1准备仿真模型和其他需求 (8)2.1.1获取所使用元器件的仿真模型 (9)2.1.2获取所使用连接器的仿真模型 (10)2.1.3获取所使用元器件和连接器的器件手册和用户指南等相关资料 (10)2.1.4获取所需的规范文档 (10)2.1.5了解相关电路和接口工作原理 (10)2.1.6提取与信号完整性相关的要求 (10)2.1.7预先创建拓扑样本 (11)2.1.8预先创建相对于不同阈值电压的眼图模板 (11)2.1.9预先创建自定义测量 (12)2.2仿真前的规划 (12)2.3关键器件预布局 (13)2.4模型加载和仿真配置 (13)2.4.1模型的转化 (14)2.4.2使用SI Design Setup配置 (15)2.4.3选择需要配置的信号线 (16)2.4.4设置仿真库 (18)2.4.5设置电源和地网络 (20)2.4.6设置叠层 (24)2.4.7设置元器件类别 (27)2.4.8为元器件分配和创建模型 (28)2.4.9设置差分对 (37)2.4.10设置仿真参数 (42)2.4.11SI Design Audit相关 (50)2.4.12提取拓扑 (52)2.4.13在SigXP中设置仿真库和仿真参数 (54)2.4.14在SigXP中绘制拓扑 (58)2.5方案空间分析 (68)2.5.1输出驱动力扫描分析 (71)2.5.2Stub长度扫描分析 (73)2.5.3线宽线间距扫描分析 (74)2.6方案到约束规则的转化 (76)2.6.1传输线延迟规则的设置 (77)2.6.2拓扑结构等传输线特性规则的设置 (80)2.6.3传输线耦合规则的设置 (80)2.6.4拓扑规则在约束管理器中的应用 (81)3Allegro PCB SI的后仿真 (84)表格表格 1:Routed Interconnect Models参数 (45)表格 2:Simulation栏眉仿真参数 (47)表格 3:IO Cell Stimulus Edit窗口中的选项 (68)图图 1:传统的PCB设计流程图 (7)图 2:Allegro PCB SI高速PCB设计流程图 (8)图 3:眼图模式下的眼图模板 (11)图 4:地址、命令和控制信号传输线拓扑 (12)图 5:RDIMM的布局示意图 (13)图 6:Model Integrity界面 (14)图 7:使用Model Integrity将IBIS文件转换至DML格式 (15)图 8:Cadence Product Choices产品选择器窗口 (16)图 9:Allegro PCB SI GXL界面 (17)图 10:Setup Category Selection窗口 (17)图 11:Setup Xnet Selection窗口 (17)图 12:Allegro PCB SI GXL关于网络设置的提醒框 (18)图 13:Setup Library Search Directories窗口 (19)图 14:Setup Library File Extensions窗口 (19)图 15:Setup Working Libraries窗口 (19)图 16:Setup Power and Ground Nets窗口 (20)图 17:Allegro PCB SI GXL电压赋值窗口 (21)图 18:选择“Edit Voltage On Any Net In Design” (21)图 19:Identify DC Nets窗口。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

上海市共进通信技术有限公司

仿真步骤

开始 指定仿真信号线 准备好要仿真的PCB图 生成仿真报告

转换库模式并加载 给器件加载模型 定义电源和地线

提取拓扑结构

更改电路条件重复仿真

根据阻抗要求调整叠层 结果分析 仿真参数设置 结束

上海市共进通信技术有限公司

仿真Байду номын сангаас数设置

• Allegro菜单中Analyze\SI/EMI Smi\ Preference

上海市共进通信技术有限公司

指定仿真信号线

• Allegro菜单中Analyze\SI/EMI Smi\ Probe

上海市共进通信技术有限公司

仿真结果

• Driver端增加电阻

加电阻

上海市共进通信技术有限公司

Crosstalk

• Crosstalk Waveform

上海市共进通信技术有限公司

仿真结果参数

SIM ID(模拟的次数) Diver(驱动端) Receiver(接收端) Cycle(仿真的周期) FTS MODE(仿真模式) Monotonic(单调性) Noise Margin(噪声裕量) Overshoothigh(上过冲) Overshootlow(下过冲) PropDelay(传输延迟,驱动端到接收端)

IBIS库转换DML

• Allegro菜单中Analyze\SI/EMI Smi\ Library

上海市共进通信技术有限公司

加载DML库

• Allegro菜单中Analyze\SI/EMI Smi\ Library

上海市共进通信技术有限公司

生成仿真报告

• Reflection

上海市共进通信技术有限公司

提取电路拓扑结构

上海市共进通信技术有限公司

更改条件重复仿真

Driver端增加电阻的波形图

上海市共进通信技术有限公司

给器件加载对应模型

• Allegro菜单中Analyze\SI/EMI Smi\ Model

上海市共进通信技术有限公司

定义电源

• Allegro菜单中Logic\Identify DC Nets

上海市共进通信技术有限公司

定义地线

• Allegro菜单中Logic\Identify DC Nets

上海市共进通信技术有限公司

根据阻抗要求调整PCB叠层

• Allegro菜单中Tools\setup advisor

上海市共进通信技术有限公司

Switch delay(开关延迟) Settle delay(建立时间)

上海市共进通信技术有限公司

Thanks!

上海市共进通信技术有限公司