QuartusII软件中两种仿真结果的分析研究

在quartusII中用modelsim-altera仿真

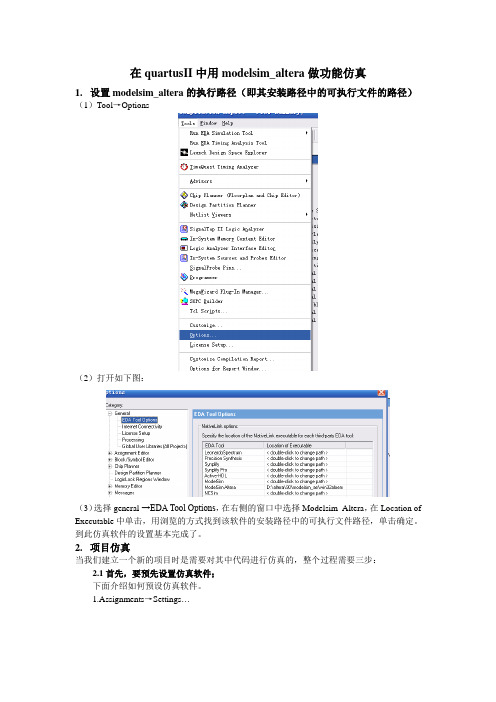

在quartusII中用modelsim_altera做功能仿真1.设置modelsim_altera的执行路径(即其安装路径中的可执行文件的路径)(1)Tool→Options(2)打开如下图:(3)选择general →EDA Tool Options,在右侧的窗口中选择Modelsim_Altera,在Location of Executable中单击,用浏览的方式找到该软件的安装路径中的可执行文件路径,单击确定。

到此仿真软件的设置基本完成了。

2.项目仿真当我们建立一个新的项目时是需要对其中代码进行仿真的,整个过程需要三步:2.1首先,要预先设置仿真软件;下面介绍如何预设仿真软件。

1.Assignments→Settings…2.打开如下界面3选择“Simulation”,右侧设置按上图设置。

2.2其次,仿真之前需要编写测试平台,测试平台有两种的方法:●直接建立XX.v文件●在quartusII中自动生成测试平台模板文件,文件为XX.vt文件下面介绍如何自动生成测试平台模板文件。

1.Processing→Start→Start Test Bench Template Writer注意:要生成testbench模板的前提条件是为项目选择预用的仿真软件,然后模块必须编译成功。

Testbench模板生成后的默认路径为:项目目录\simulation\modelsim\项目名.vt(因为刚才在预设置仿真软件时的“Output Directory”选择的是默认的值simulation\modelsim)。

2.对于自动生成的测试平台模版需要打开修改测试激励信号,这里不做介绍,很简单的。

2.3改写完后要在项目里添加测试平台文件到项目里。

1.Assignments→Settings…2.在打开界面做如下操作:(1)选择“Compile test bench”,然后单击“Test Benches…”(2)打开下面的窗口(3)单击“New”打开下面的窗口,且按图中填写相关信息这个窗口是用来输入testbench的资料和选择testbench的路径的。

(完整版)基于QuartusII的数字电路仿真实验报告手册

数字电路仿真实验报告班级通信二班姓名:孔晓悦学号:10082207 作业完成后,以班级为单位,班长或课代表收集齐电子版实验报告,统一提交.文件命名规则如“通1_王五_学号”一、实验目的1. 熟悉译码器、数据选择器、计数器等中规模数字集成电路(MSI)的逻辑功能及其使用方法。

2. 掌握用中规模继承电路构成逻辑电路的设计方法。

3. 了解EDA软件平台Quartus II的使用方法及主要功能。

二、预习要求1. 复习数据选择器、译码器、计数器等数字集成器件的工作原理。

2. 熟悉所有器件74LS153、74LS138、74LS161的功能及外引线排列。

3.完成本实验规定的逻辑电路设计项目,并画出接线图,列出有关的真值表。

三、实验基本原理1.译码器译码器的逻辑功能是将每个输入的二进制代码译成对应的高、低电平信号。

译码器按功能可分为两大类,即通用译码器和显示译码器。

通用译码器又包括变量译码器和代码变换译码器。

变量译码器是一种完全译码器,它将一系列输入代码转换成预知一一对应的有效信号。

这种译码器可称为唯一地址译码器。

如3线—8线、4线—16线译码器等。

显示译码器用来将数字或文字、符号的代码译成相应的数字、文字、符号的电路。

如BCD-七段显示译码器等。

2.数据选择器数据选择器也陈伟多路选择器或多路开关,其基本功能是:在选择输入(又称地址输入)信号的控制下,从多路输入数据中选择某一路数据作为输出。

因此,数据选择器实现的是时分多路输入电路中发送端电子开关的功能,故又称为复用器。

一般数据选择器有n 个地址输入端,2n错误!未找到引用源。

个数据输入端,一个数据输出端或反码数据输出端,同时还有选通端。

目前常用的数据选择器有2选1、4选1、8选1、16选1等多种类型。

3.计数器计数器是一个庸医实现技术功能的时序部件,它不仅可以用来对脉冲计数,还常用作数字系统的定时、分频、执行数字运算以及其他一些特定的逻辑功能。

74LS161是4位同步二进制计数器,它除了具有二进制加法计数功能外,还具有预置数、保质和异步置零等附加功能。

quartus ii实验报告

quartus ii实验报告Quartus II实验报告引言:Quartus II是一款由Intel公司开发的集成电路设计软件,广泛应用于数字逻辑设计和FPGA开发领域。

本实验报告旨在介绍Quartus II的基本功能和使用方法,并通过实际案例展示其在数字逻辑设计中的应用。

一、Quartus II概述Quartus II是一款功能强大的集成电路设计软件,它提供了从设计到验证的全套工具。

Quartus II支持多种编程语言,如VHDL和Verilog,使得用户可以根据自己的需求选择适合的语言进行设计。

此外,Quartus II还提供了丰富的库和模块,方便用户进行快速原型开发和验证。

二、Quartus II的基本功能1. 设计入口Quartus II提供了多种设计入口,包括图形界面、命令行和脚本等方式。

用户可以根据自己的习惯和需求选择适合的方式进行设计。

图形界面友好易用,适合初学者;命令行和脚本则更适合有一定经验和需求的用户。

2. 设计编辑Quartus II提供了强大的设计编辑功能,用户可以在其中创建和编辑设计模块、信号线和电路连接等。

设计编辑界面清晰简洁,用户可以方便地进行设计布局和调整。

3. 仿真和验证Quartus II内置了仿真和验证工具,用户可以通过仿真来验证设计的正确性和性能。

仿真工具支持波形查看和信号分析等功能,帮助用户进行设计调试和优化。

4. 综合和优化Quartus II具备强大的综合和优化功能,可以将设计代码转化为硬件描述,进而生成逻辑电路。

综合工具会根据用户的约束条件和优化目标,自动进行逻辑优化和资源分配,提高设计的性能和效率。

5. 布局和布线Quartus II提供了先进的布局和布线工具,可以将逻辑电路映射到实际的FPGA芯片上。

布局工具可以根据用户的约束条件和性能要求,自动进行电路元件的位置分配;布线工具则负责将电路元件之间的连接线路进行规划和布线。

6. 下载和调试Quartus II支持将设计文件下载到目标FPGA芯片上,并提供了调试工具来验证和调整设计的正确性。

quartusii19.4和modelsim的仿真

quartusii19.4和modelsim的仿真由于quartus 19.4不⽀持直接在⼯程中启动modelsim⼀起联合仿真,所以需要⾃⼰写tb⽂件。

对于⼀个新安装的quartus 19.4。

⾸先需要做的第⼀步:点击“Launch Simlulation Library Compiler”⽣成altera的库⽂件。

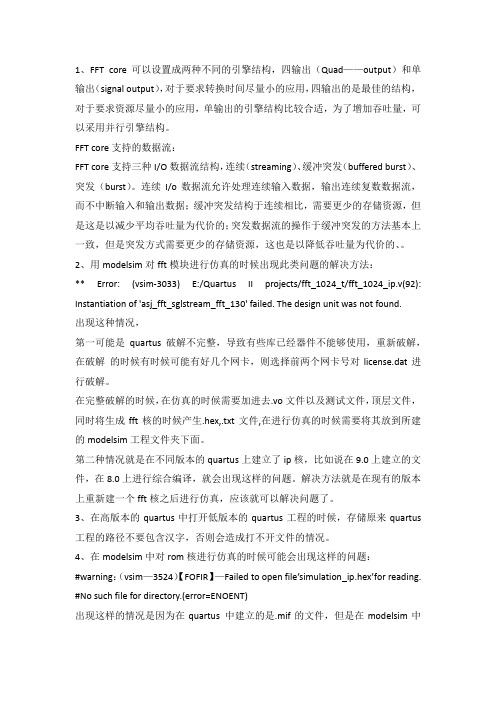

进⼊下图所⽰:1、选择modelsim图标的⽂件地址;2、选择要进⾏仿真的芯⽚;3、选择仿真的语⾔verilog4、选择⽣成库⽂件的地址。

点击“Start Compilation”按钮,⽣成库⽂件。

之后在modelsim的安装包中找到modelsim.ini⽂件并加⼊⼀下字段内容:altera_ver = G:/modeltech_10.1b/verilog_libs/altera_verlpm_ver = G:/modeltech_10.1b/verilog_libs/lpm_versgate_ver = G:/modeltech_10.1b/verilog_libs/sgate_veraltera_mf_ver = G:/modeltech_10.1b/verilog_libs/altera_mf_veraltera_lnsim_ver = G:/modeltech_10.1b/verilog_libs/altera_lnsim_vertwentynm_ver = G:/modeltech_10.1b/verilog_libs/twentynm_vertwentynm_hssi_ver = G:/modeltech_10.1b/verilog_libs/twentynm_hssi_vertwentynm_hip_ver = G:/modeltech_10.1b/verilog_libs/twentynm_hip_ver然后环境就配置完成了,就是再do或者tcl等脚本⽂件中加⼊库的编译。

quartus仿真

(6) 仿真。

Quartus II内置波形编辑程序(Waveform Editor)可以生成和编辑波形设计文件,从而设计者可观察和分析模拟结果。

Quartus II中的仿真包括功能仿真和时序仿真,功能仿真检查逻辑功能是否正确,不含器件内的实际延时分析;时序仿真检查实际电路能否达到设计指标,含器件内的实际延时分析。

两种仿真操作类似,只需在Tools菜单中选择Simulater Tool,在其Simulater mode中进行选择即可,如图1.5所示。

图1.5、QuartusII项目仿真设定窗口现以时序仿真为例,介绍仿真的具体操作过程:Step1、新建一个波形文件:该过程与新建Verilog HDL文件类似,只是在弹出页式对话框后选择Other F iles页面的Vector Waveform File。

Step2、在波形文件中加入所需观察波形的管脚:在Name中单击右键,选择Insert Node or bus...选项,出现Insert Node or bus对话框,此时可在该对话框的Name栏直接键入所需仿真的管脚名,也可点击No de Finder...按钮,将所有需仿真的管脚一起导入。

Node Finder对话框如图1.6所示。

图1.6、QuartusII建立待仿真文件时的管脚及内部信号选择窗口在Pins下拉列表框中选择合适的选项,点击List按钮,将所需仿真的管脚移至Select Noder框中。

点击OK进入波形仿真界面。

Step3、给输入管脚指定仿真波形:分别选中输入管脚,使用波形编辑器:对其输入波形进行编辑。

最后保存波形文件,如图1.7所示。

图1.7、QuartusII中编辑完成的待仿真波形文件如何将quartus 2的仿真时间设置为大于1usEdit -> end time修改默认Tools->Options->Waveform Editor这里面可以更改选项错误:Error: Run Generate Functional Simulation Netlist (quartus_map clkdiv --generate_functional_sim_netlist) to generate functional simulation netlist for top level entity "clkdiv" before running the Simulator (quartus_sim)在prosessing -> generate functional simulation netlist。

在QuartusII波形仿真技巧

目前越来越多的通信系统采用FPGA进行硬件设计,而FPGA设计中非常重要而频繁进行的一环是仿真。

仿真能将硬件设计中的逻辑和时序问题及早暴露出来,以便工程师改进设计或调整方案。

仿真是硬件设计流程中较为耗时和烦琐的一环。

主要原因有:仿真的激励波形必须由设计者自行创建,测试波形必须人工输入;仿真的结果正确与否必须由设计者自行判断,很难自动化;时序仿真前必须对整个设计做耗时的全编译;仿真过程是计算机软件模拟芯片对测试输入的逻辑处理,通常计算时间消耗很大。

在这4个步骤中,第2步依赖于设计者的经验和特定设计逻辑的复杂程度,第3、4步则由计算机完成,基本上是个定数,只有第一步还具有提高效率的空间。

我们在进行实际的FPGA 设计处理信号时,针对第1步有大量仿真数据输入的需求,在研究Quartus II激励波形文件的格式后,编程设计了一种将输入数据转化为激励波形的方法。

QuartusII中仿真流程现在Altera公司的器件均可由Quartus II进行设计。

Quartus II除了能完成语法检查、综合、布局布线、生成配置文件和时序分析的设计全流程,还自带仿真功能(Quartus II Simulator)。

Quartus II中时序仿真的流程图如图1所示。

vwf文件全称是矢量波形文件(Vector Waveform File),是Quartus II中仿真输入、计算、输出数据的载体。

一般设计者建立波形文件时,需要自行建立复位、时钟信号以及控制和输入数据、输出数据信号等。

其中工作量最大的就是输入数据的波形录入。

比如要仿真仅1KB 的串行输入数据量,则手工输入信号的波形要画8000个周期,不仅费时费力而且容易出错。

如果能找到一种简易的将输入数据转化为激励波形的方法,则可以极大提高仿真速度,减少手工操作时间,因此需要研究vwf文件的格式。

vwf文件格式分析既然vwf文件是仿真数据的载体,那么必需首先弄清楚该文件存放数据的格式,再针对这种格式做一定的变换得到所需要的波形。

QuartusII与Modelsim波形仿真区别

QuartusII与Modelsim仿真的区别:用QuartusII写了一个隔直滤波器,运用QuartusII9.1自带的波形仿真,仿真结果与matlab 仿真后的结果比较近似。

仿真结果为:下图为testbench部分代码:LIBRARY ieee;USE ieee.std_logic_1164.all;use IEEE.STD_LOGIC_ARITH.ALL;useieee.std_logic_unsigned.all;useieee.std_logic_signed.all;ENTITY gezhi_filter_vhd_tst ISEND gezhi_filter_vhd_tst;ARCHITECTURE gezhi_filter_arch OF gezhi_filter_vhd_tst ISconstantclk_period :time :=10 ns; -- constants-- signals);END COMPONENT;BEGINi1 :gezhi_filterPORT MAP (-- list connections between master ports and signalsclk,clr,d00,d02,d04,d06,d11,d22,d_sf0,d_sf10,d_sf20,d_sf30,d_sf40,d_sf120,d_sf340,din_x, dou_y);clk_gen: PROCESS-- variable declarationsBEGINclk<='0'; -- code that executes only oncewait for clk_period/2;clk<='1';wait for clk_period/2;END PROCESS;clr_gen: PROCESSBEGIN--clr<='1'; -- code executes for every event on sensitivity list--wait for clk_period/4;clr<='0';WAIT;END PROCESS;din_x_gen: PROCESSBEGINdin_x<=CONV_STD_LOGIC_VECTOR(256,18); -- code that executes only oncewait for clk_period;din_x<=CONV_STD_LOGIC_VECTOR(-12,18); -- code that executes only oncewait for clk_period;din_x<=CONV_STD_LOGIC_VECTOR(32,18); -- code that executes only oncewait for clk_period;din_x<=CONV_STD_LOGIC_VECTOR(39,18); -- code that executes only oncewait for clk_period;din_x<=CONV_STD_LOGIC_VECTOR(-128,18); -- code that executes only oncewait for clk_period;din_x<=CONV_STD_LOGIC_VECTOR(512,18); -- code that executes only oncewait for clk_period;din_x<=CONV_STD_LOGIC_VECTOR(520,18); -- code that executes only oncewait for clk_period;din_x<=CONV_STD_LOGIC_VECTOR(15,18); -- code that executes only oncewait for clk_period;END PROCESS;END gezhi_filter_arch;调用modelsim6.5SE仿真后的波形图:仿真结果中,din_x是输入,dou_y是输出,modelsim结果中的红线X代表未知输出而不是0,导致最后的结果dou_y开头都是0输出,和Quartus仿真结果不同。

使用modelsin对quartus II仿真时遇到问题的解决方法

1、FFT core可以设置成两种不同的引擎结构,四输出(Quad——output)和单输出(signal output),对于要求转换时间尽量小的应用,四输出的是最佳的结构,对于要求资源尽量小的应用,单输出的引擎结构比较合适,为了增加吞吐量,可以采用并行引擎结构。

FFT core支持的数据流:FFT core支持三种I/O数据流结构,连续(streaming)、缓冲突发(buffered burst)、突发(burst)。

连续I/o数据流允许处理连续输入数据,输出连续复数数据流,而不中断输入和输出数据;缓冲突发结构于连续相比,需要更少的存储资源,但是这是以减少平均吞吐量为代价的;突发数据流的操作于缓冲突发的方法基本上一致,但是突发方式需要更少的存储资源,这也是以降低吞吐量为代价的、。

2、用modelsim对fft模块进行仿真的时候出现此类问题的解决方法:** Error: (vsim-3033) E:/Quartus II projects/fft_1024_t/fft_1024_ip.v(92): Instantiation of 'asj_fft_sglstream_fft_130' failed. The design unit was not found.出现这种情况,第一可能是quartus破解不完整,导致有些库已经器件不能够使用,重新破解,在破解的时候有时候可能有好几个网卡,则选择前两个网卡号对license.dat进行破解。

在完整破解的时候,在仿真的时候需要加进去.vo文件以及测试文件,顶层文件,同时将生成fft核的时候产生.hex,.txt文件,在进行仿真的时候需要将其放到所建的modelsim工程文件夹下面。

第二种情况就是在不同版本的quartus上建立了ip核,比如说在9.0上建立的文件,在8.0上进行综合编译,就会出现这样的问题。

解决方法就是在现有的版本上重新建一个fft核之后进行仿真,应该就可以解决问题了。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

QuartusII软件中两种仿真结果的分析研究作者:陈贞

来源:《电子技术与软件工程》2016年第14期

摘要本文运用QuartusII软件对数字逻辑电路的时序仿真和功能仿真结果进行分析,其结果表明两种仿真结果不一致的原因为数字逻辑电路的竞争-冒险现象。

文中详细地讨论产生竞争-冒险现象的原因和防范竞争-冒险现象的一些办法。

【关键词】QuartusII软件时序仿真功能仿真竞争-冒险现象

1 引言

EDA(Electronic Design Automation,电子设计自动化)技术是以QuartusII软件为设计平台,以Verilog或VHDL为硬件描述语言,以FPGA或PLD等可编程逻辑芯片为载体,将电子系统的软件仿真与硬件设计电路相结合的一门电子设计技术。

我校的应用电子技术专业和电子信息工程技术专业已开设EDA技术课程多年,多数学生反应VHDL语言编程较难,分析仿真结果较难等等,在学习过程中容易产生畏难的情绪,影响学习效果。

所以针对学生反映的仿真结果分析较难的问题,此文章重点分析两种仿真结果不一致的难点。

2 QuartusII软件中两种仿真过程

EDA设计流程包括设计输入,逻辑综合,布线/适配,仿真,下载及硬件调试。

在整个设计流程中,完成设计输入并成功进行编译仅能说明设计符合一定的语法规范或电路绘图的规则,并不能说明设计功能的正确性,这就需要通过仿真对设计进行验证,保证设计符合其功能性。

在QuartusII设计平台中,仿真一般分为功能仿真和时序仿真。

功能仿真又叫逻辑仿真,是指在不考虑器件延时和布线延时的理想情况下对源代码进行逻辑功能的验证,以了解实现的功能是否满足设计要求,其仿真结果与电路设计的真值表的结果相对应;而时序仿真是在布线后进行,是最接近真实器件运行的仿真,它与特定的器件有关,又包含了器件和布线的延时信息,主要验证程序在目标器件中的时序关系。

现以原理图输入的方式设计加法器为例来说明两种仿真结果的不同,其电路图如图1所示。

从图2时序仿真图和图3功能仿真图中可以发现,在相同的电路图和相同的输入信号赋值的条件下,输出的波形是不一样的,这种结果往往会造成学生学习过程中的疑惑,对电路分析也造成难点。

3 两种仿真结果不一致的原因

在QuartusII软件中造成时序仿真和功能仿真结果不一致的原因是数字逻辑电路中的竞争—冒险现象。

在数字逻辑电路的分析中,信号电平的高低跳变为理想状态,就是在输入信号的状态发生变化时,输出信号的状态会立即做出反应。

但在实际电路中,输入信号要通过数字电路的逻辑单元器件和连线才能够到达输出端,这个过程中就会产生延时,即当输入状态发生变化时,输出状态会延时做出相应变化,并且延时时间的长短与连线的长短和逻辑单元器件的数目有关,同时还受逻辑单元器件的制造工艺、工作电压、温度等条件的影响;其次信号的高低电平转换也需要一定的过渡时间。

这些因素就导致在输入信号状态发生改变时,输出信号的状态改变的时刻不一致,这种现象称为竞争。

由于竞争而引起电路输出信号中出现了非预期信号,产生瞬间错误的现象称为冒险,同时将输出端出现的不正确的尖峰脉冲,称为毛刺。

在传统的PCB板设计时,电路布线存在分布电容,几纳秒的毛刺可以被滤波掉,但PLD 器件内部无分布电容,在单元电路设计时,输入信号在通过PLD器件的内部逻辑单元和内部布线时产生的延时,会在输出端产生毛刺,这些毛刺将被完整的保留并向下一级电路传递。

因此在EDA设计中,解决由竞争—冒险现象带来的毛刺问题显得尤为重要,而毛刺问题可以通过时序仿真和功能仿真结果对比清晰的观察到。

4 竞争一冒险现象解决方案

在数字逻辑电路的设计中,由于PLD器件自身的特点,其竞争—冒险现象是不可避免的,但是可以通过一些技术手段减少竞争一冒险现象带来的毛刺问题。

4.1 增加冗余项

在一些组合逻辑电路的设计中可以通过增加冗余项来解决竞争一冒险现象,并且在PLD 器件里只要资源足够,增加冗余项也不是一件困难的事,但是要保持信号在路径上的延迟一致,则需要不断的实验。

4.2 增加D触发器

D触发器的输入端,只要竞争冒险信号(毛刺)不出现在时钟脉冲的上升沿且满足数据的建立和保持时间,就不会对组合逻辑电路造成危害。

因此利用D触发器的输入端对毛刺信号不敏感的特点,在输出信号的保持时间内,用触发器读取组合逻辑的输出信号。

4.3 增加选通脉冲

增加选通脉冲是指在逻辑电路中加入一个控制脉冲,这个控制脉冲在信号稳定以后才到达,即只有控制脉冲到达以后,输出端才有输出,可以减少毛刺现象。

同时在同步时序电路的设计中将输入端的时钟信号保持同步,对于此电路在纳秒级仿真,不会出现竞争一冒险现象。

5 结语

在数字逻辑电路的设计中,竞争一冒险现象往往会影响到数字电路的稳定性,甚至可能会使系统出错,避免和消除竞争—冒险现象是十分必要的。

通过QuartusII软件设计平台的两种仿真结果对比可以很清楚的反映竞争—冒险现象带来的毛刺现象,同时教师可以指导学生对可能出现竞争—冒险现象进行仔细地分析,并采取适当的措施,就可能抑制竞争—冒险带来的毛刺干扰。

参考文献

[1]韩芳,张亚.EDA技术在竞争一冒险现象教学中的应用[J].福建电脑,2008(12):198-199.

[2]邢思茗,丁岩松,杨月婷.QuartusII8.0在竞争冒险现象教学中的应用[J].中国科技博览,2012(05):184-185.

[3]张睛.FPGA设计中竞争冒险问题的研究[J].实验室研究与探索,2003(22):47-49.

[4]杨延宁,李建成,杨世平,赵小杰.可编程逻辑器件(PLD)的竞争冒险现象研究[J].延安大学学报:自然科学版,2002(21):36-37.。