eda 实验考试答案 石化学院

2

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity twelvecounter is

port (cp: in std_logic;

LD,R:in std_logic;

A:in std_logic_vector (4 downto 0);

Q:buffer std_logic_vector(4 downto 0);

co:out std_logic);

end twelvecounter ;

architecture one of twelvecounter is

begin

co<='1' when(Q="10001") else'0'; process(cp,R)

begin

if R='0' then

Q<="00000";

elsif(cp'event and cp='1') then

if LD='0' then Q<=A;

elsif Q="10001" then Q <= "00000" ;

else Q <= Q + 1;

end if;

end if;

end process;

end one;

EDA技术试验问答题答案(基本包含)

第一章 1-1 EDA技术与ASIC设计和FPGA开发有什么关系?FPGA/CPLD在ASIC设计中有什么用途? 答:利用EDA技术进行电子系统设计的最后目标是完成专用集成电路ASIC的设计和实现;FPGA和CPLD是实现这一途径的主流器件。FPGA和CPLD通常也被称为可编程专用IC,或可编程ASIC。FPGA和CPLD的应用是EDA技术有机融合软硬件电子设计技术、SoC(片上系统)和ASIC设计,以及对自动设计与自动实现最典型的诠释。FPGA/CPLD在ASIC设计中,属于可编程ASIC的逻辑器件;使设计效率大为提高,上市的时间大为缩短。 1-2与软件描述语言相比,VHDL有什么特点? P6 答:编译器将软件程序翻译成基于某种特定CPU的机器代码,这种代码仅限于这种CPU而不能移植,并且机器代码不代表硬件结构,更不能改变CPU的硬件结构,只能被动地为其特定的硬件电路结构所利用。综合器将VHDL程序转化的目标是底层的电路结构网表文件,这种满足VHDL设计程序功能描述的电路结构,不依赖于任何特定硬件环境;具有相对独立性。综合器在将VHDL(硬件描述语言)表达的电路功能转化成具体的电路结构网表过程中,具有明显的能动性和创造性,它不是机械的一一对应式的“翻译”,而是根据设计库、工艺库以及预先设置的各类约束条件,选择最优的方式完成电路结构的设计。 l-3什么是综合?有哪些类型?综合在电子设计自动化中的地位是什么? P5 什么是综合? 答:在电子设计领域中综合的概念可以表示为:将用行为和功能层次表达的电子系统转换为低层次的便于具体实现的模块组合装配的过程。 有哪些类型?答:(1)从自然语言转换到VHDL语言算法表示,即自然语言综合。(2)从算法表示转换到寄存器传输级(RegisterTransport Level,RTL),即从行为域到结构域的综合,即行为综合。(3)从RTL级表示转换到逻辑门(包括触发器)的表示,即逻辑综合。(4)从逻辑门表示转换到版图表示(ASIC设计),或转换到FPGA的配置网表文件,可称为版图综合或结构综合。 综合在电子设计自动化中的地位是什么?答:是核心地位(见图1-3)。综合器具有更复杂的工作环境,综合器在接受VHDL程序并准备对其综合前,必须获得与最终实现设计电路硬件特征相关的工艺库信息,以及获得优化综合的诸多约束条件信息;根据工艺库和约束条件信息,将VHDL程序转化成电路实现的相关信息。 1-4在EDA技术中,自顶向下的设计方法的重要意义是什么? P7~10 答:在EDA技术应用中,自顶向下的设计方法,就是在整个设计流程中各设计环节逐步求精的过程。 1-5 IP在EDA技术的应用和发展中的意义是什么? P11~12 答:IP核具有规范的接口协议,良好的可移植与可测试性,为系统开发提供了可靠的保证。 1-6 叙述EDA的FPGA/CPLD设计流程。P13~16 答:1.设计输入(原理图/HDL文本编辑);2.综合;3.适配;4.时序仿真与功能仿真;5.编程下载;6.硬件测试。

中石化职称英语考试试卷(中级)

试卷一 I. Vocabulary Directions: There are 20 incomplete sentences in this part. For each sentence there are four choices marked A, B, C and D. Choose the ONE answer that best completes the sentence and mark your answer on the Answer Sheet. 1. It is possible to predict how much energy and water a building will consume, how much _______ will be needed. A. matter B. things C. material D. substance 2. They found that the positive thinkers sold 37 percent more insurance than did the_______ thinkers. A. negative B. positive C. active D. passive 3. In labs around the world, bad bugs are undergoing the ultimate rehabilitation, being _______ from life-threatening viruses and bacteria into lifesaving therapeutic agents. A. translated B. transported C. transformed D. transmitted 4. The fresh air is sometimes humid from the _______rainfall of this area. A. numerous B. abundant C. plenty D. substantive 5. We know that many animals _______ the deep seas at pressures of 15,000 pounds per square inch. A. live on B. live in C. live through D. live up to 6. Speakers and writers of the Germanic languages _______for a great deal of the world's output in everything from economics to literature to military to science and technology. A. account B. allow C. apply D. arrange 7. _______of the great state of Illinois, let me express my deepest gratitude for the privilege of addressing this convention. A. On account B. In honor C. In place D. On behalf 8. The companies that are finding ways to hang on to their older workers _______ from an intangible commodity: wisdom. A. obtain B. earn C. develop D. benefit 9. I raced to_______ Jill. A. keep on B. keep up with C. come up with D. come up to 10. Managers need to monitor inflation trends so they can make good _______. A. decisive B. decisions C. decide D. decided 11. Fluency can be _______ defined as "being able to communicate ideas without having to stop and think too much about what one is saying." A. simple B. simply C. similar D. simplify 12. The number of vehicles has been steadily increasing. _______, more than 100 cities in the United States still have levels of carbon monoxide that exceed legally established limits. A. Continuously B. Consequently C. Constantly D. Consistently 13. A(An) _______ is better than the text and may make the point clear. A. interpretation B. representation C. illustration D. draw 14. Some of the world's best mountain _______ is available within the 500-kilometer long chain of the Southern Alps. A. scene B. scenery C. scarce D. scare 15. After a through research, the police __ most of the missing jewels. A. retreated B. refreshed C. recovered D. reminded 16. A gold-rated building is estimated to have reduced its environmental impact by 50% compared with a(an) __ conventional building. A. equivalent B. alike C. uniform D. likely 17. When pessimists __ in their first attempt, they usually say, "I can't do this." A. feel B. fail C. defeat D. lost 18. Six years __ before she got another note from Teddy. A. went into B. went around C. went by D. went on 19. The company owns a large number of _______ stores. A. export B. bargain C. retail D. trade 20. The cost of self-education has fallen with the multitude of sources of knowledge and information _______ on CD-ROMs and the Internet. A. preferable B. ready C. available D. considerable II. Grammatical Structure Directions: There are 20 incomplete sentences in this part. For each sentence there are four choices marked A, B, C and D. Choose the ONE answer that best completes the sentence and mark your answer on the Answer Sheet. 21. Put things back _______ you found them.

(完整版)EDA期末考试题1

1.一个项目的输入输出端口是定义在( A )1-5 ACDCD 6-10 CCACA A. 实体中;. B. 结构体中; C. 任何位置; D. 进程中。 2. MAXPLUS2中编译VHDL源程序时要求( C ) A. 文件名和实体可以不同名; B. 文件名和实体名无关; C. 文件名和实体名要相同; D. 不确定。 3. VHDL语言中变量定义的位置是(D ) A. 实体中中任何位置; B. 实体中特定位置; C. 结构体中任何位置; D. 结构体中特定位置。 4.可以不必声明而直接引用的数据类型是(C ) A. STD_LOGIC ; B. STD_LOGIC_VECTOR; C. BIT; D. ARRAY。 5. MAXPLUS2不支持的输入方式是(D ) A 文本输入;.B. 原理图输入;C. 波形输入;D. 矢量输入。 6.大规模可编程器件主要有FPGA、CPLD两类,下列对FPGA结构与工作原理的描述中,正确的是( C ) A. FPGA全称为复杂可编程逻辑器件; B. FPGA是基于乘积项结构的可编程逻辑器件; C. 基于SRAM的FPGA器件,在每次上电后必须进行一次配置; D. 在Altera公司生产的器件中,MAX7000系列属FPGA结构。 7.下面不属于顺序语句的是( C ) A. IF语句; B. LOOP语句; C. PROCESS语句; D. CASE语句。 8. VHDL语言是一种结构化设计语言;一个设计实体(电路模块)包括实体与结构体两部分,实体体描述的是( A ) A. 器件外部特性; B. 器件的内部功能; C. 器件的综合约束; D. 器件外部特性与内部功能。 9. 进程中的信号赋值语句,其信号更新是( C ) A. 按顺序完成; B. 比变量更快完成; C. 在进程的最后完成; D. 都不对。 10. 嵌套使用IF语句,其综合结果可实现:(A ) A. 带优先级且条件相与的逻辑电路; B. 条件相或的逻辑电路; C. 三态控制电路; D. 双向控制电路。 一、单项选择题:(20分) 1. IP核在EDA技术和开发中具有十分重要的地位;提供用VHDL等硬件描述

8位全加器实验报告

实验1 原理图输入设计8位全加器 一、实验目的: 熟悉利用QuartusⅡ的原理图输入方法设计简单组合电路,掌握层次化设计的方法,并通过一个8位全加器的设计把握利用EDA软件进行电子线路设计的详细流程。 二、原理说明: 一个8位全加器可以由8个1位全加器构成,加法器间的进位可以串行方式实现。即将低位加法器的进位输出cout与其相邻的高位加法器的最低进位输入信号cin相接。而一个1位全加器可以按照本章第一节介绍的方法来完成。 三、实验内容: 1:完全按照本章第1节介绍的方法与流程,完成半加器和全加器的设计,包括原理图输入、编译、综合、适配、仿真。 2:建立一个更高的原理图设计层次,利用以上获得的1位全加器构成8位全加器,并完成编译、综合、适配、仿真和硬件测试。 四、实验环境: 计算机、QuartusII软件。 五、实验流程: 实验流程: 根据半加器工作原 理,建立电路并仿 真,并将元件封装。 ↓ 利用半加器构成一位 全加器,建立电路并 仿真,并将元件封 装。 ↓ 利用全加器构成8位全 加器,并完成编译、综 合、适配、仿真。 图1.1 实验流程图

六、实验步骤: 1.根据半加器工作原理建立电路并仿真,并将元件打包。(1)半加器原理图: 图1.2 半加器原理图(2)综合报告: 图1.3 综合报告: (3)功能仿真波形图4: 图1.4 功能仿真波形图

时序仿真波形图: 图1.5 时序仿真波形图 仿真结果分析:sout为和信号,当a=1,b=0或a=0,b=1时,和信号sout为1,否则为0.当a=b=1时,产生进位信号,及cout=1。 (4)时序仿真的延时情况: 图1.6 时序仿真的延时情况 (5)封装元件: 图1.7 元件封装图 2. 利用半加器构成一位全加器,建立电路并仿真,并将元件封装。 (1)全加器原理图如图: 图2.1 全加器原理图

中国石油化工集团中石化招聘笔试试题及答案

中国石油化工集团中石化招聘笔试试题及答案

绝密 招聘综合素质能力测试试题 时间:70分钟 祝各位考生发挥出自己的最佳水平!

说明:

请仔细阅读以下的注意事项,这对你顺利经过考试非常重要: ?监考老师宣布考试开始时,你才能够开始答题。 ?请用2B铅笔在答题卡上作答,写在本题册上的答案无效,请勿折叠答题卡。 ?答题卡“试卷类型”必填,“工号”栏填准考证号,如有遗漏,视作废卷。 ?请勿在本题册上书写、涂改或留下任何标记,题册最后两页是空白草稿纸,可拆下来正反使用,如果 需要增加,请举手示意监考老师。 ?在考试结束时,请留在座位上,等监考老师收取答题卡、考卷和草稿纸。不得将这些物品带出考场。 如需提前交卷,请先举手示意监考老师收取。

第一部分语言理解与表示 1.非学历民办学校:指国家机构以外的社会组织和个人利用非国家财政性经费,面向社会举力、不具备颁发学历文凭资格的培训、进修、专修学院(学校、中心)。 根据上述定义,下列不属于非学历民办学校的一项是: A.某四星级普通高级中学的分校B.几位退休教师办的高考复习班 C.企业老总出资办了计算机培训中心D.某市工商联办的技能培训班 “四星级普通高级中学的分校”乃属于普通高中,【解析】 能够颁发高中文凭,不能列入“非学历民办学校”的范畴,因此选A。 2.劣币:靠投机或贪污受贿等不良途径获得的财富。 下列与定义相合的是:

A.卖假药发财 B.中奖所得C.抄股所得 D.百万富翁的财产 【解析】只有“卖假药发财”具备不良途径这一条件,因此选A。 3. 利人利己者把生活看成一个合作的舞台,而不是一个角斗场。一般人看事情:非强即弱、非胜即败。世界之大。人人都有足够的立足空间,她人之得不必就视为自己之失。这段话谈论的核心意思是( )。 A.生活是一个合作的舞台 B.双赢符合现实人生的辩证法 C.善待她人也要善待自己 D.利人与利己并存不悖 答案:D【解析】文段中提到利人利己者把生活看成一个合作的舞台,即利人与利己并不相悖。因此答案为D项。4.当前中国法律对个人隐私的保护力度比较薄弱,个人的隐私主要是经过个人名誉权来保护的。而且,个人名誉权受到侵害的,要造成侵害后果的才予以追究。对于绝大多数受“骚扰”的人来说,受侵害的后果并不是很明显,也很难追究。经过这段话,作者想表示的是( )。 A.中国有关保护个人隐私权的法律有待完善 B.中国个人受侵害的后果并不明显 C.中国现行法律保护个人的名誉权 D.中国的个人隐私主要是经过个人名誉权来保护的 答案:A【解析】文段中第一句话即提到当前中国法律对个人的保护力度比较薄弱,下文展开分析,因此作者想表示的即为A项。 5.美国和日本科学家近日经过分析采集来的三维地震数据,揭示了太平洋底南海海槽下的地壳结构。这一发现有助于科学家深入了解为什么地震在海底有些地方会引

EDA期末考试考卷及答案

(A卷) 赣南师范学院 2010—2011学年第一学期期末考试试卷(A卷)(闭卷)年级 2008 专业电子科学与技术(本)课程名称 EDA技术基础 2、学生答题前将密封线外的内容填写清楚,答题不得超出密封线; 3、答题请用蓝、黑钢笔或圆珠笔。 一、单项选择题(30分,每题2分) 1.以下关于适配描述错误的是 B A.适配器的功能是将综合器产生的网表文件配置于指定的目标器件中,使之产生最终的下载文件 B.适配所选定的目标器件可以不属于原综合器指定的目标器件系列 C.适配完成后可以利用适配所产生的仿真文件作精确的时序仿真 D.通常,EDAL软件中的综合器可由专业的第三方EDA公司提供,而适配器则需由FPGA/CPLD供应商提供 2.VHDL语言是一种结构化设计语言;一个设计实体(电路模块)包括实体与结构体两部分,结构体描述 D 。 A.器件外部特性B.器件的综合约束 C.器件外部特性与内部功能D.器件的内部功能 3.下列标识符中, B 是不合法的标识符。 A.State0 B.9moon C.Not_Ack_0 D.signall 4.以下工具中属于FPGA/CPLD集成化开发工具的是 D A.ModelSim B.Synplify Pro C.MATLAB D.QuartusII 5.进程中的变量赋值语句,其变量更新是 A 。 A.立即完成B.按顺序完成 C.在进程的最后完成D.都不对 6.以下关于CASE语句描述中错误的是 A A.CASE语句执行中可以不必选中所列条件名的一条 B.除非所有条件句的选择值能完整覆盖CASE语句中表达式的取值,否则最末一个条件句的选择必须加上最后一句“WHEN OTHERS=><顺序语句>” C.CASE语句中的选择值只能出现一次 D.WHEN条件句中的选择值或标识符所代表的值必须在表达式的取值范围 7.以下哪个程序包是数字系统设计中最重要最常用的程序包 B A.STD_LOGIC_ARITH B.STD_LOGIC_1164 C.STD_LOGIC_UNSIGNED D.STD_LOGIC_SIGNED 8.基于EDA软件的FPGA / CPLD设计流程为:原理图/HDL文本输入→A →综合→适配→时序仿真→编程下载→硬件测试。 A.功能仿真B.逻辑综合C.配置D.引脚锁定 9.不完整的IF语句,其综合结果可实现 D A.三态控制电路B.条件相或的逻辑电路 C.双向控制电路D.时序逻辑电路 10.下列语句中,属于并行语句的是A A.进程语句B.IF语句C.CASE语句D.FOR语句11.综合是EDA设计流程的关键步骤,综合就是把抽象设计层次中的一种表示转化成另一种表示的过程;在下面对综合的描述中, C 是错误的。 A.综合就是将电路的高级语言转化成低级的,可与FPGA / CPLD的基本结构相映射的网表文件 B.综合可理解为,将软件描述与给定的硬件结构用电路网表文件表示的映射过程,并且这种映射关系不是唯一的 C.综合是纯软件的转换过程,与器件硬件结构无关 D.为实现系统的速度、面积、性能的要求,需要对综合加以约束,称为综合约束 12.CPLD的可编程是主要基于什么结构 D 。 A.查找表(LUT)B.ROM可编程 C.PAL可编程D.与或阵列可编程 13.以下器件中属于Altera 公司生产的是 B A.ispLSI系列器件B.MAX系列器件 C.XC9500系列器件D.Virtex系列器件 14.在VHDL语言中,下列对时钟边沿检测描述中,错误的是 D A.if clk'event and clk = '1' then B.if clk'stable and not clk = '1' then C.if rising_edge(clk) then D.if not clk'stable and clk = '1' then 15.以下关于状态机的描述中正确的是 B A.Moore型状态机其输出是当前状态和所有输入的函数 B.与Moore型状态机相比,Mealy型的输出变化要领先一个时钟周期C.Mealy型状态机其输出是当前状态的函数

EDA期末考试题大全

附带: 一.问答题 1信号赋值语句在什么情况下作为并行语句?在什么情况下作顺序语句?信号赋值和变量赋值符号分别是什么?两种赋值符号有什么区别? ●信号赋值语句在进程外作并行语句,并发执行,与语句所处的位置无关。信号赋值语句在进程内 或子程序内做顺序语句,按顺序执行,与语句所处的位置有关。 ●信号赋值符号为“<=”变量赋值用“:=”。信号赋值符号用于信号赋值动作,不立即生效。 变量,赋值符号用于变量赋值动作,立即生效。 2进程的敏感信号表指的是什么?简述敏感信号表在进程中的作用? ●进程的“敏感信号表”也称敏感表,是进程的激活条件,可由一个或多个信号组成,各信号 间以“,”号分隔。当敏感信号表中的任一个信号有事件发生,即发生任意变化,此时,进程被激活,进程中的语句将从上到下逐句执行一遍,当最后一条语句执行完毕之后,进程即进入等待挂起状态,直到下一次敏感表中的信号有事件发生,进程再次被激活,如此循环往复。 3什么是库、程序包、子程序、过程调用和函数调用? ●库和程序包用来描述和保存元件、类型说明和子程序等,以便在其它设计中通过其目录可查询、 调用。子程序由过程和函数组成。在子程序调用过程中,过程能返回多个变量,函数只能返回一个变量。若子程序调用的是一个过程,就称为过程调用,若子程序调用的是一个函数,则称为函数调用。过程调用、函数调用都是子程序调用。 二.改错题 1.已知sel为STD_LOGIC_VECTOR(1 DOWNTO 0)类型的信号,而a、b、c、d、q均为STD_LOGIC类型的 信号,请判断下面给出的CASE语句程序片段:

●CASE sel IS ●WHEN“00”=>q<=a; ●WHEN“01”=>q<=b; ●WHEN“10”=>q<=c; ●WHEN“11”=>q<=d; ●END CASE; ●答案:CASE语句缺“WHEN OTHERS”语句。 2.已知data_in1, data_in2为STD_LOGIC_VECTOR(15 DOWNTO 0) 类型的输入端口,data_out为STD_LOGIC_VECTOR(15 DOWNTO 0)类型的输出端口,add_sub为STD_LOGIC类型的输入端口,请判断下面给出的程序片段: ●LIBRARY IEEE; ●USE IEEE.STD_LOGIC_1164.ALL; ●ENTITY add IS ● PORT(data_in1, data_in2:IN INTEGER; ● data_out:OUT INTEGER); ●END add; ●ARCHTECTURE add_arch OF add IS ●CONSTANT a:INTEGER<=2; ●BEGIN ●data_out<=( data_in1+ data_in2) * a; ●END addsub_arch; 答案:常量声明时赋初值的“<=”符号应改用“:=”符号。 3.已知Q为STD_LOGIC类型的输出端口,请判断下面的程序片段: ●ARCHITECTURE test_arch OF test IS ●BEGIN ●SIGNAL B:STD_LOGIC; ●Q<= B; END test_arch 答案:信号SIGNAL的声明语句应该放在BEGIN语句之前。 4.已知A和Q均为BIT类型的信号,请判断下面的程序片段: ●ARCHITECTURE archtest OF test IS ●BEGIN ●CASE A IS ●WHEN ‘0’=>Q<=‘1’; ●WHEN ‘1’=>Q<=‘0’; ●END CASE; ●END archtest; 答案:CASE语句应该存在于进程PROCESS内。 三.程序设计 LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL;

EDA 1位全加器实验报告

南华大学 船山学院 实验报告 (2009 ~2010 学年度第二学期) 课程名称EDA 实验名称1位全加器 姓名学号200994401 专业计算机科学与 班级01 技术 地点8-212 教师

一、实验目的: 熟悉MAX+plus 10.2的VHDL 文本设计流程全过程 二、实验原理图: ain cout cout ain bin sum cin bin sum cin f_adder or2a f e d u3 u2u1b a c co so B co so B h_adder A h_adder A 三、实验代码: (1)LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY f_adder IS PORT (ain ,bin ,cin : IN STD_LOGIC; cout ,sum : OUT STD_LOGIC ); END ENTITY f_adder; ARCHITECTURE fd1 OF f_adder IS COMPONENT h_adder PORT ( a ,b : IN STD_LOGIC; co ,so : OUT STD_LOGIC); END COMPONENT ; COMPONENT or2a PORT (a ,b : IN STD_LOGIC; c : OUT STD_LOGIC); END COMPONENT ; SIGNAL d ,e ,f : STD_LOGIC; BEGIN u1 : h_adder PORT MAP(a=>ain ,b=>bin ,co=>d ,so=>e); u2 : h_adder PORT MAP(a=>e , b=>cin , co=>f ,so=>sum); u3 : or2a PORT MAP(a=>d , b=>f , c=>cout);

2017年中国石油化工集团(中石化)招聘笔试试题及答案

绝密 2017年招聘综合素质能力测试试题祝各位考生发挥出自己的最佳水平!

说明: 请仔细阅读以下的注意事项,这对你顺利通过考试非常重要: 监考老师宣布考试开始时,你才可以开始答题。 请用2B铅笔在答题卡上作答,写在本题册上的答案无效,请勿折叠答题卡。 答题卡“试卷类型”必填,“工号”栏填准考证号,如有遗漏,视作废卷。 请勿在本题册上书写、涂改或留下任何标记,题册最后两页是空白草稿纸,可拆下来正反使用,如果需要增加,请举手示意监考老师。 在考试结束时,请留在座位上,等监考老师收取答题卡、考卷和草稿纸。不得将这些物品带出考场。如需提前交卷,请先举手示意监考老师收取。

第一部分常识判断 (共8题,参考时限5分钟) 请开始答题: 1.古人云:“天下事有难易乎?为之,则难者亦易矣;不为,则易者亦难矣。人之为学有难易乎?学之,则 难者亦易矣;不学,则易者亦难矣。”这句话反映了()。 A.世界上一切事物都是相对运动的 B.时间与空间是事物的存在方式 C.矛盾是对立统一的 D.物质和运动是不可分的 2. 《国家“十二五”规划纲要》提出积极构建有利于转变经济发展方式的财税体制。下列表述不属于加快财 税体制改革的是()。 A.完善转移支付制度,增加一般性特别是均衡性转移支付规模和比例 B.在完善社会保险基金预算基础上研究编制社会保障预算 C.继续推进费改税,全面推进资源税和耕地占用税改革 D.稳步推进利率市场化改革,加强金融市场基准利率体系建设 3. 下列关于我国司法系统的说法,正确的是()。 A.国务院是最高国家审判机关和最高法律监督机关 B.司法机关在审理案件中独立行使职权的同时,必须依法行事,不得滥用权利 C.人民检察院可与人民法院在法律允许的范围类协商合作,依照法律行使自己的职权 D.国家司法权只能由国家各级审判机关独立行使,任何其他机关和团体均无权行使此权力 4. 军衔是区别军人等级的称号,一般分为将官、校官、尉官、士官和士兵5等,每级再细分数级,部分国家 设元帅和准尉。下列各图是中国人民解放军现行军衔的肩章,其中代表上将军衔的是()。 A B C D 5. 下列古代医学著作,按时间先后顺序排列正确的是()。 ①《黄帝内经》②《千金方》③《伤寒杂病论》④《本草纲目》 A.①②③④ B.②④③① C.①③②④ D.④②①③ 6. “君子之交淡若水,小人之交甘若醴”出自下列哪部作品()。 A.《老子》 B.《论语》

EDA技术期末试卷含答案资料

精品文档 一、单项选择题(30分)9.嵌套使用IF语句,其综合结果可实现 A 。A.带优先级且条件相与的逻辑电路1.以下描述错误的是 C B.条 件相或的逻辑电路 C.三态控制电路是A.QuartusIIAltera提供的FPGA/CPLD集成开发环境D.双向控制电路 10.在VHDLAlteraB.是世界上最大的可编程逻辑器件供应商之一语言中,下列对时钟边沿检测描述中,错误的是 D 。 A.if clk'event and clk = ‘1' then B.if falling_edge(clk) then 前一代C.MAX+plusII是AlteraFPGA/CPLD集成开发环境QuartusII的更 C.if clk'event and clk = ‘0' then 新换代新产品D.if clk'stable and not clk = ‘1' then 11.下列那个流程是正确的基于.DQuartusII完全支持VHDL、Verilog的设计流程EDA软件的FPGA / CPLD设计流程 B A.原理图/HDL文本输入→适配→综合→功能仿真→编程下载→硬件测试开发工具中的专用综合器的是2.以下工具中属于FPGA/CPLD B B.原理图/HDL文本输入→功能仿真→综合→适配→编程下载→硬件测试 C .Active HDL D.QuartusII Leonardo Spectrum .AModelSim B.C.原理图/HDL文本输入→功能仿真→综合→编程下载→→适配硬件测试;.3以下器件中属于Xilinx 公司生产的是 C /HDL文本输入→功能仿真→适配→编程下载→综合→硬件测试 D.BMAX系列器件.原理图A.ispLSI系列器件 )语句的语句结构及语法规则语言中,下列对进程(PROCESS系列器件 C.XC9500系列器件D.FLEX 12.在VHDL 。A 的描述中,正确的是以下关于信号和变量的描述中错误的是4. B 为一无限循环语句;敏感信号发生更新时启动进程,执行完..信号是描述硬件系统的基本数据对象,它的性质类似于连接线PROCESSAA .信号的定义范围是结构体、进程B 成后,等待下一次进程启动C.除了没有方向说明以外,信号与实体的端口概念是一致的B.敏感信号参数表中,应列出进程中使用的所有输入信号CD.在进程中不能将变量列入敏感信号列表中.进程由说明部分、结构体部分、和敏感信号参数表三部分组成D.当前进程中声明的变量也可用于其他进程以下关于状态机的描述中正确的是5. B B MooreA.型状态机其输出是当前状态和所有输入的函数13.下列语句中,不属于并行语句的是 语句B.CASE 型的输出变化要领先一个时钟周期型状态机相比,.与BMooreMealy A.进程语句 …语句…ELSE D.WHEN .元件例化语句MealyC.型状态机其输出是当前状态的函数 C 设计现行工作VHDL语言共支持四种常用库,其中哪种库是用户的14.以上都不对D .VHDL B 下列标识符中,.库是不合法的标识符。6 END BPP0 A...D .CNot_Ack sig D

(完整)EDA试题及答案,推荐文档

2013年电子系统设计考试试题--考试时间21号56节--公共409 一、填空题 1. Verilog的基本设计单元是模块。它是由两部分组成,一部分描述接口;另一部分描述逻辑功能,即定义输入是如何影响输出的。 2. 用assign描述的语句我们一般称之为组合逻辑,并且它们是属于并行语句,即于语句的书写次序无关。而用always描述的语句我们一般称之为组合逻辑或时序逻辑,并且它们是属于串行语句,即于语句的书写有关。 3.在case语句中至少要有一条default语句. 4. 已知x=4’b1001,y=4’0110,则x的4位补码为4’b1111,而y的4位的补码为4’b0110 . 5. 两个进程之间是并行语句。而在Always中的语句则是顺序语句。 二、简答题 1. 怎样理解在进程语句中,阻塞语句没有延迟这句话? 答:这是因为在进程语句中,有阻塞语句和非阻塞语句这两种,非阻塞语句是有延迟的,而阻塞语句也是有延迟的,这是因为因果系统都有延迟,只是阻塞语句的延迟比非阻塞语句的延迟小于若干个数量级,因此可视为没有延迟。 2.在进程中什么情况下综合为时序电路?什么情况下综合为组合电路? 答:在进程中,只有当敏感信号是边沿触发(即上升沿或下降沿)时,此时综合为时序电路;而在进程中只有当敏感信号是电平沿触发时,此时综合为组合电路。 3.为什么在Verilog语言中,其综合只支持次数确定的循环,而不支持次数不确定的循环? 答:这是因为,在Verilog语言中,它是为电路设计而设计的一门语言,它与高级语言不同,若循环的次数不确定,则会带来不确定的延迟,而这在电路中是不允许存在的,故综合只能支持次数确定的循环,即对于一个具体的芯片,其延迟只是一个定值。 4.Verilog HDL语言进行电路设计方法有哪几种? 答:①自上而下的设计方法(Top-down);②自下而上的设计方法(Bottom-Up) ③综合设计的方法。 5.specparam语句和parameter语句在参数说明方面不同之处是什么? 答:1.specparam语句只能在延时的格式说明块(specify)中出现,而parameter语句则不能再延时说明块内出现。 2.由specparam语句进行定义的参数只能是延时参数,而由parameter语句定义的参数可以是任何数据类型的参数。 3.由specparam语句定义的延时参数只能在延时说明块内使用,而由parameter语句定义的参数则可以在模块内(该parameter语句之后)的任何位置说明。 三、选择题: 1、下列标示符哪些是合法的(B) A、$time B、_date C、8sum D、mux# 2、如果线网类型变量说明后未赋值,起缺省值是(D) A、x B、1 C、0 D、z 3、现网中的值被解释为无符号数。在连续赋值语句中,assign addr[3:0]=-3;addr被赋予的值是(A) A、4’b1101 B、4’b0011 C、4’bxx11 D、4’bzz11 4、reg[7:0] mema[255:0]正确的赋值是(A) A、mema[5]=3’ d0, B、8’ d0; C、1’ b1; D、mema[5][3:0]=4’ d1 5、在code模块中参数定义如下,请问top模块中d1模块delay1、delay2的值是( D) module code(x,y); module top; paramee delay1=1,delay2=1; …………….

EDA设计实验报告

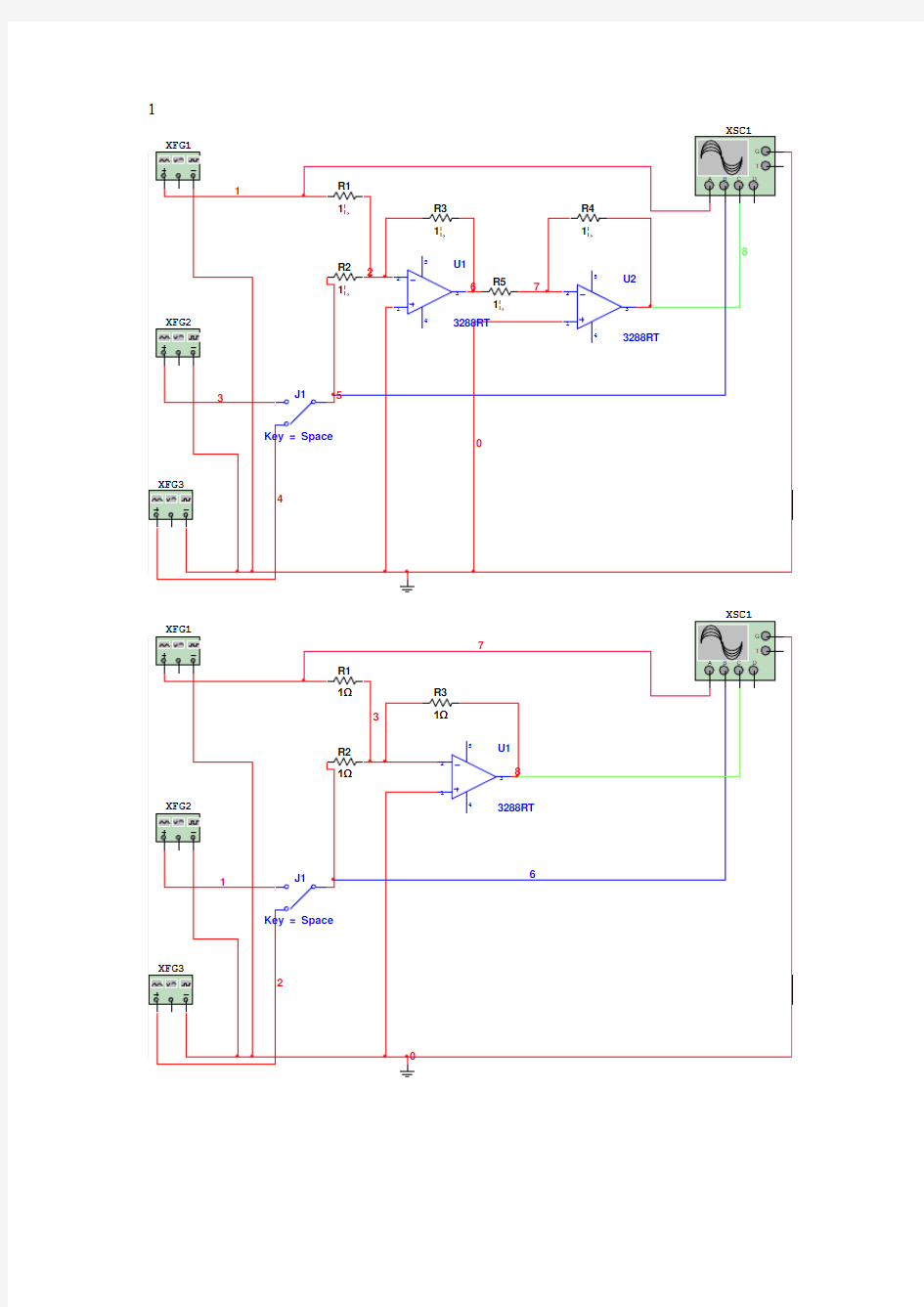

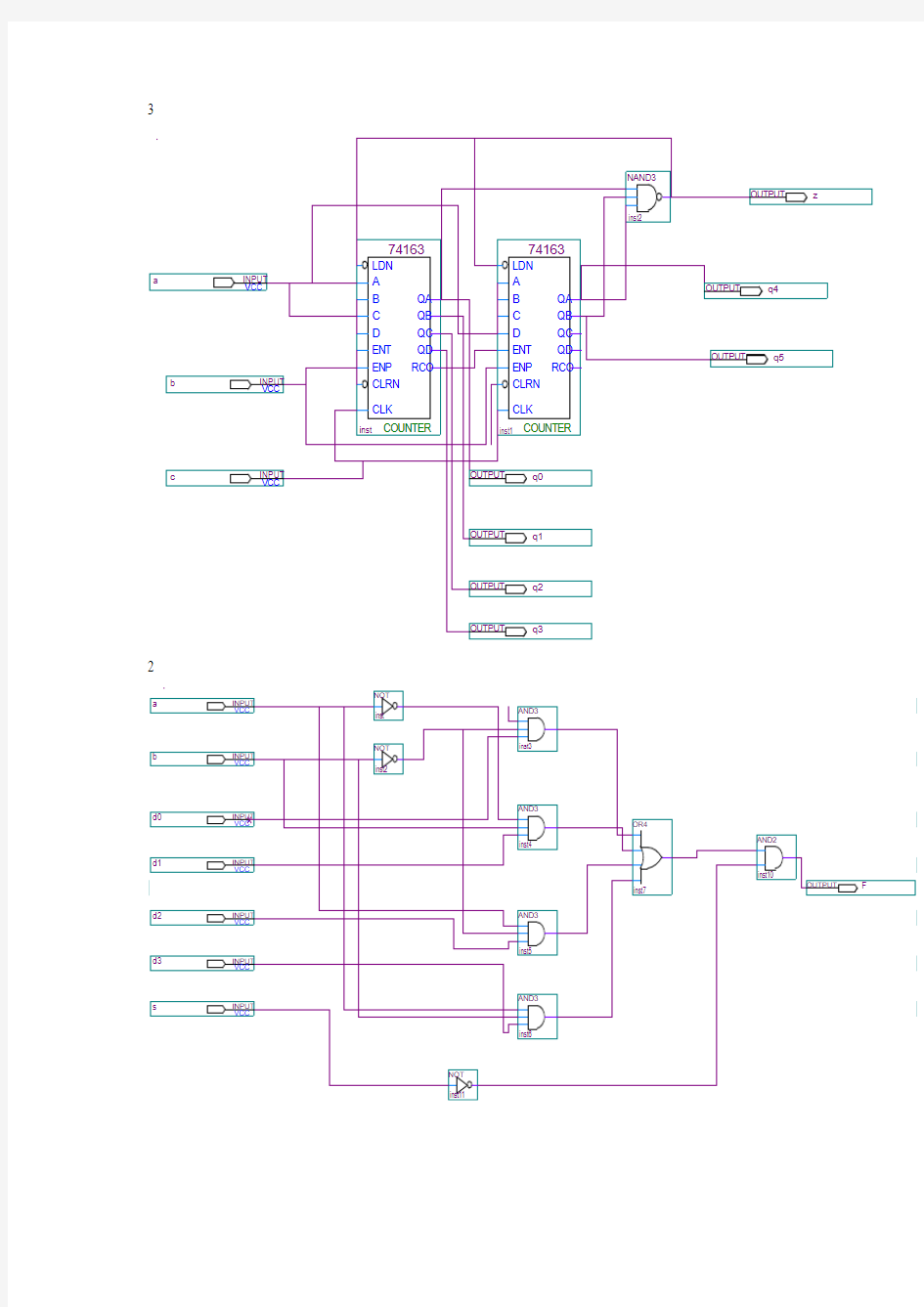

摘要 通过实验学习和训练,掌握基于计算机和信息技术的电路系统设计和仿真方法。要求: 1. 熟悉multisim软件的使用,包括电路图编辑、虚拟仪器仪表的使用和掌握常见电路分析 方法。2. 能够运用multisim软件对模拟电路进行设计和性能分析,掌握eda设计的基本方 法和步骤。multisim常用分析方法:直流工作点分析、直流扫描分析、交流分析。掌握设计 电路参数的方法。复习巩固单级放大电路的工作原理,掌握静态工作点的选择对电路的影响。 了解负反馈对两级放大电路的影响,掌握阶梯波的产生原理及产生过程。 关键字:电路仿真 multisim 负反馈阶梯波 目次 实验一 (1) 实验二............................................................................................. 11 实验三 (17) 实验一单级放大电路的设计与仿真 一、实验目的 1. 设计一个分压偏置的单管电压放大电路,要求信号源频率5khz(峰值10mv) , 负载电阻5.1kω,电压增益大于50。 2. 调节电路静态工作点(调节电位计),观察电路出现饱和失真和截止失真的输出 信号波形,并测试对应的静态工作点值。 3. 调节电路静态工作点(调节电位计),使电路输出信号不失真,并且幅度尽可能 大。在此状态下测试: ①电路静态工作点值; ②三极管的输入、输出特性曲线和? 、 rbe 、rce值;③电路的输入电阻、输出电 阻和电压增益;④电路的频率响应曲线和fl、fh值。 二、实验要求 1. 给出单级放大电路原理图。 2. 给出电路饱和失真、截止失真和不失真且信号幅度尽可能大时的输出信号波形 图,并给出三种状态下电路静态工作点值。 3. 给出测试三极管输入、输出特性曲线和? 、 rbe 、rce值的实验图,并给出 测试结果。 4. 给出正常放大时测量输入电阻、输出电阻和电压增益的实验图,给出测试结果 并和理论计算值进行比较。 5. 给出电路的幅频和相频特性曲线,并给出电路的fl、fh值。 6. 分析实验结果。 三、实验步骤 实验原理图: 饱和失真时波形: 此时静态工作点为: 所以,i(bq)=4.76685ua i(cq)=958.06700ua u(beq)=0.62676v u(ceq)=0.31402v 截止失真时波形: 此时静态工作点为: 所以,i(bq)=2.07543ua i(cq)=440.85400ua u(beq)=0.60519v u(ceq)=5.54322v 最大不失真时波形:篇二:eda课程设计实验报告电子电工实习 华北电力大学

中石化加油站主管计量操作及数质量技能考核试题

中石化加油站主管计量操作及数质量技能考核试题 一、名词说明(5题,共10分) 1.计量: 答:实现单位统一和量值准确可靠的测量叫计量。 2.温度补偿: 答:油库把公布温度下的体积(即交运数)换算成实际发油温度下的体积进行发油称为油库发油时对油站的温度补偿。 3.清罐损耗: 答:清洗油罐时,油罐存油的最后一次在油罐计量数量与用其他方式回收余油数量之差为清罐损耗。 4.十步法: 答:①引车到位;②连接静电接地线;③安全防护;④四确认;⑤进货验收;⑥卸油;⑦卸油;⑧卸后确认;⑨施打反向铅封;⑩卸后处理。 5.换算密度: 答:换算密度G t =(ρ20-0.0011)VCF 。式中:G t —油库发油换算密度,常用单位:g/cm 3、kg/m 3 ;ρ 20 —油品标准密度,常用单位:g/cm 3、kg/m 3;0.0011—空气浮力修正系数,常用单位:g/cm 3 、 kg/m 3 ; VCF —体积修正系数(石油在标准温度下的体积与其在非标准温度下的体积之比)。 二、填空(12题,共27分) 1.凡是日常检查发觉加油机封印断裂、失效时,加油站站长应赶忙报告 零管部门 ,经确认后,由零管部门向实施施封的部门报告,待处理。对封印有问题的加油机 停止发油 ,爱护好现场,等待处理。 2.测量卧罐内油面高度使用标称长度为5米的量油尺,它由 尺铊 、 尺带 和 尺架 组成,其最小分度值为1mm 。 3.测量卧罐或汽车罐车油温,使用最小分度为 0.2 ℃ 的 周密 、全浸 、 棒式 、水银温度计。温度测量可在液面高度测量后赶忙进行。应将带有 保温盒 的温度计放入油高的 中 部,停留至少 5min ,然后拉绳读取。注意视线与水银柱应 垂直 ,先读 小数 ,后读 大数 ,并记录,读数应估读至0.1 ℃。

《EDA》试题B答案

2007 至2008学年度第二学期期末考核 《EDA》试题(开卷) 卷号:B 时间:120 分钟 2008 年6 月 专业:电子信息工程学号:姓名: 一填空题(20分) 1、VHDL 2、DEVICE.LIB SYMBOLS.LIB 3、实际零件焊接到电路板时所指示的外观和焊点的位置 4、电子设计自动化电子CAD技术 5、A L T E R A,X I L I N X 6、WAIT 7、电路连接 8、SRAM-BASE 9、2.54mm 300mil 10、元件外观和元件引线端子的图形 二名词解释(20分) 1 PLD/FPGA PLD是可编程逻辑器件(Programable Logic Device)的简称,FPGA是现场可编程门阵列(Field Programable Gate Array)的简称,两者的功能基本相同,只是实现原理略有不同,所以我们有时可以忽略这两者的区别,统称为可编程逻辑器件或PLD/FPGA。 2.过孔 当需要连接两个层面上的铜膜走线时就需要过孔(Via),过孔 又称为贯孔、沉铜孔和金属化孔。 过孔分为穿透式(Through)、半隐藏式(Blind)和隐藏式(Buried) 3.铜膜线 就是连接两个焊盘的导线,称为Track,一般铜膜线走线在不 同层面取不同的走向,例如顶层走水平线,则底层走垂直线。顶 层和底层走线之间的连接采用过孔(Via)连接。 4 PROM、PAL和PLA PROM:与阵列固定,或阵列可编程,一般用作存储器,其输入为存储器的地址,输出为存储器单元的内容。但输入的数目太大时,器件功耗增加,其局限性大。 PLA:与或阵列均可编程,但是其慢速特性和相对PAL、PROM而高得多的价格妨碍了它被广泛使用。PAL:或阵列固定,与阵列可编程,其第二代产品GAL具有了可电擦写、可重复编程、可设置加密的功能。 5 自顶向下的/自下而上的设计方法 自下而上的设计方法,使用该方法进行硬件设计是从选择具体元器件开始,并用这些元器件进行逻辑电路设计,从而完成系统的硬件设计,然后再将各功能模块连接起来,完成整个系统的硬件设计,自顶向下的设计方法就是从系统的总体要求出发,自顶向下分三个层次对系统硬件进行设计。 第一个层次是行为描述第二个层次是数据流描述第三个层次为逻辑综合