Ch07寄存器与计数器

AMPCI-9111使用说明书

AMPCI-9111通用数据采集控制板使用说明书2001/03一、概述AMPCI-9111板是PCI总线通用采集控制板,该板可直接插入具备PCI插槽的工控机或个人微机,构成模拟量电压信号、数字量电压信号采集、监视输入和模拟量电压/电流信号输出、数字量信号输出及计数定时系统。

AMPCI-9111板为用户提供了单端32路/双端16路模拟量数据采集输入通道, 模拟量输入通道具有程控放大功能,2路12Bit模拟量电压或电流信号输出,16Bit TTL数字量输入和16Bit TTL数字量输出,配接AMPCD821光隔端子板实现光隔I/O,可直接驱动继电器, 3路16位计数定时通道(一片82C54),计数频率8M,板内自带基准时钟4M,82C54的0、 1、2通道均引至输出插座J2,可构成脉冲计数、频率测量、脉冲信号发生器等电路。

对AMPCI-9111板的所有读写操作均为16Bit即D00~D15,当对82C54进行读写时只有D00~D07有效,同样A/D转换数据一次读入的为B00~B11。

二、性能和技术指标2.1 性能•模拟信号输入A/D分辩率: 12Bit•模拟信号通道: 单端32路/双端16路•模拟信号输入程控放大倍数: 1/2/4/8 (B型为1/10/100/1000)•模拟信号输出D/A分辩率: 12Bit•模拟信号输出通道: 2路•数字量输入/输出: 16Bit DI/16Bit DO ;TTL/COMS兼容•计数定时通道: 3路16BIT• A/D转换触发工作方式: 软件触发• A/D转换数据传输方式: 查询方式2.2 技术指标•输入电压范围: ±5V、0-10V、±10V•输入阻抗: > 100 MΩ• A/D转换时间: 8.5uS• A/D转换精度: 优于±0.1%(10V满量程)•输出电压范围: ±5V、0-5V、0-10V•输出电流范围: 0-10mA 、4-20mA•内部时钟基准: 4MHz三、使用3.1本板A/D转换工作过程描述AMPCI-9111板的A/D转换是通过软件来控制和启动A/D转换的<1>使用时首先应程序设定要进行A/D转换的通道号,即要对哪一通道进行A/D转换,该写操作见后面《寄存器功能描述》的(1)节: “模拟输入通道选择、增益选择寄存器”,该寄存器I/O地址Offset=00H ,“Offset”是相对地址的偏移量,为该寄存器的I/O地址(详细对“Offset”的读写操作见软件说明部分)<2>程序设定完要进行A/D转换的通道号和放大倍数后,需执行程序启动A/D转换操作,A/D转换器才开始转换,即再执行《寄存器功能描述》的(2)节,“启动A/D转换”,该写操作的I/O地址 Offset=02H,该操作为软件触发启动一个周期的A/D转换,若A/D转换的放大倍数不是1倍,应在设定“模拟输入通道选择、增益选择寄存器”操作后,适当加几个μS的延时以给程控放大器足够的建立时间,再执行启动A/D转换操作,以保证精度<3>启动A/D转换后,通过软件查询A/D转换完成状态标志位,见《寄存器功能描述》的(3)节,“查询A/D 转换状态位+A/D转换数据”,“Z”该位为1,说明A/D转换器正在进行转换,不可读取A/D转换数据,继续查询该位,若该位为0,说明A/D转换已完成,可读取A/D转换数据,该读操作的I/O地址 Offset=0AH,标志位Z对应该标志寄存器数据线D15-D00的D15,当查询A/D转换完成状态标志位“Z”位为0时,此时读取该口的B11-B00 即为A/D转换数据3.2本板D/A转换工作过程描述进行D/A转换时只需向相应的I/O端口写12BIT数据即可,如对D/A1进行转换,将数据B11-B00写入D/A1数据寄存器offset=06H端口即可3.3本板结构如下:主要元件位置、信号输入/输出插座及跳线选择定义AMPCI-9111/9111BJ1: 模拟量输入输出37P孔式D型插座J2: 数字量计数定时输入输出50P双排针插座JP1/JP2: 单双端输入方式设定JP3: A/D输入范围设定JP6: D/A1输出方式设定JP7: D/A2输出方式设定3.4 J1模拟信号输入/输出插座定义:<1>模拟输入单端方式引线定义见下:⊙ 19 GNDGND 37 ⊙⊙ 18 D/A-1 +12V 36 ⊙⊙ 17 D/A-2通道32 35 ⊙⊙ 16 通道16通道31 34 ⊙⊙ 15 通道15通道30 33 ⊙⊙ 14 通道14通道29 32 ⊙⊙ 13 通道13通道28 31 ⊙⊙ 12 通道12通道27 30 ⊙⊙ 11 通道11通道26 29 ⊙⊙ 10 通道10通道25 28 ⊙⊙ 9 通道9通道24 27 ⊙⊙ 8 通道8通道23 26 ⊙⊙ 7 通道7通道22 25 ⊙⊙ 6 通道6通道21 24 ⊙⊙ 5 通道5通道20 23 ⊙⊙ 4 通道4通道19 22 ⊙⊙ 3 通道3通道18 21 ⊙⊙ 2 通道2通道17 20 ⊙□ 1 通道1印制板D/A-1: 模拟输出通道1D/A-2: 模拟输出通道2GND: 模拟输入/输出地单端方式时32路模拟输入信号连接到通道n输入端,所有信号的地端接到GND端,下图所示CH00(1通道)输入 CH01(2通道) Vi 被测信号端 .口 . Vi.CH1F(32通道)ViGND(地线)单端方式时32路模拟输入信号接线示意图单端输入时通道代码与选择通道对应关系如下:<2>模拟输入双端方式引线定义见下:双端方式时16路模拟输入信号连接到通道正端和通道负端,信号的负端经电阻接到GND端,下图所示⊙ 19 GNDGND 37 ⊙⊙ 18 D/A-1+12V 36 ⊙⊙ 17 D/A-2通道16- 35 ⊙⊙ 16 通道16+通道15- 34 ⊙⊙ 15 通道15+通道14- 33 ⊙⊙ 14 通道14+通道13- 32 ⊙⊙ 13 通道13+通道12- 31 ⊙⊙ 12 通道12+通道11- 30 ⊙⊙ 11 通道11+通道10- 29 ⊙⊙ 10 通道10+通道9- 28 ⊙⊙ 9 通道9+通道8- 27 ⊙⊙ 8 通道8+通道7- 26 ⊙⊙ 7 通道7+通道6- 25 ⊙⊙ 6 通道6+通道5- 24 ⊙⊙ 5 通道5+通道4- 23 ⊙⊙ 4 通道4+通道3- 22 ⊙⊙ 3 通道3+通道2- 21 ⊙⊙ 2 通道2+通道1- 20 ⊙□ 1 通道1+印制板现场信号双端方式时16路模拟输入信号接线示意图双端使用说明:双端输入时信号加在CHn+和CHn-之间,模拟输入采用双端方式时,负输入端应与GND之间接一只几十KΩ~几百KΩ的电阻(信号源内阻小于100Ω时,该电阻应为信号源内阻的1000倍,当信号源内阻大于100Ω时,该电阻应为信号源内阻的2000倍),从而为仪表放大器输入电路提供偏置,见上图所示双端输入时通道代码与选择通道对应关系如下(双端时只有16个通道):3.5 数字量和计数定时器输入输出插座J2定义:J2为50P双排针插座GND 50 ⊙⊙ 49 GND+5V 48 ⊙⊙ 47 +5VCLK2 46 ⊙⊙ 45 OUT2GATE2 44 ⊙⊙ 43 CLK1GATE1 42 ⊙⊙ 41 OUT1 OUT0 40 ⊙⊙ 39 CLK0GATE0 38 ⊙⊙ 37 ФGND 36 ⊙⊙ 35 GND+5V 34 ⊙⊙ 33 +5VPB07 32 ⊙⊙ 31 PB06PB05 30 ⊙⊙ 29 PB04PB03 28 ⊙⊙ 27 PB02PB01 26 ⊙⊙ 25 PB00PB08 24 ⊙⊙ 23 PB09PB10 22 ⊙⊙ 21 PB11PB12 20 ⊙⊙ 19 PB13PB14 18 ⊙⊙ 17 PB15PA07 16 ⊙⊙ 15 PAO6PA05 14 ⊙⊙ 13 PAO4PA03 12 ⊙⊙ 11 PAO2PA01 10 ⊙⊙ 9 PAO0PA08 8 ⊙⊙ 7 PA09PA10 6 ⊙⊙ 5 PA11PA12 4 ⊙⊙ 3 PA13PA14 2 ⊙□ 1 PA15插座J2定义见图示其中:PAO0~PA15: 16bit数字量输出PB00~PB15: 16bit数字量输入+5V: 机内PCI总线+5VGND: 机内地GATE0: 计数器通道0门控GATEOUT0: 计数器通道0输出端CLK0: 计数器通道0时钟输入端GATE1: 计数器通道1门控GATEOUT1: 计数器通道1输出端CLK1: 计数器通道1时钟输入端GATE2: 计数器通道2门控GATEOUT2: 计数器通道2输出端CLK2: 计数器通道2时钟输入端3.6 跨接线选择定义:<1> JP1/JP2: JP1和JP2用来设置A/D模拟输入采用单端方式/双端方式①A/D输入采用单端方式时JP1/JP2按如下设置(出品状态):□○○○○ JP1 ; 即JP1的2和3短接, 4和5短接 1□○○○○○ JP2 ; 即JP2的2和3短接, 5和6短接1② A/D输入采用双端差分方式时JP1/JP2按如下设置:□○○○○ JP1 ; 即JP1的1和2短接, 3和4短接 1□○○○○○ JP2; 即JP2的1和2短接, 4和5短接 1<2>JP3 ;JP3用于设置A/D输入范围;可分别设置①-5V~+5V; ②0~+10V; ③-10V~+10V① -5V ~ +5V 输入范围时按如下设置(出品状态):○○○○2 ○□ 1 JP3; 即JP3的1和3短接, 4和6短接② 0 ~ +10V 输入范围时按如下设置:○○○○2 ○□ 1 JP3; 即JP3的1和3短接, 2和4短接③ -10V ~ +10V 输入范围时按如下设置:○○○○2 ○□ 1 JP3; 即JP3的3和5短接, 4和6短接<3> JP6与JP7JP6与JP7分别用来设置D/A1输出和D/A2输出的输出方式, JP6与JP7设置方式相同,可分别设置① D/A输出电压方式 -5V ~ +5V(出品状态):3○○○○○○○○○○□○○○○即(3,6);(9,12);(10,13)短接1 JP6/JP7② D/A输出电压方式 0V ~ +5V:3○○○○○○○○○○□○○○○即(3,6);(12,15);(10,13)短接1 JP6/JP7③ D/A输出电压方式 0V ~ +10V:3○○○○○○○○○○□○○○○即 (3,6); (10,13) 短接1 JP6/JP7④ D/A输出电流方式 0 ~ 10mA:3○○○○○○○○○○□○○○○即 (2,3); (7,8);(12,15) 短接1 JP6/JP7⑤ D/A输出电流方式 4 ~ 20mA:3○○○○○○○○○○□○○○○即 (2,3); (4,5); (7,8);(11,14) ;(12,15) 短接1JP6/JP73.7 I/O寄存器功能描述①: 模拟输入通道选择、增益选择寄存器(写操作)Offset=00H,Offset:相对地址的偏移量,即该写操作的I/O地址(详细对Offset=##H I/O端口的读写操作见后面软件说明部分,后同)G2~G0:程控放大增益选择位,意义见下:G1 G0 程控放大增益倍数 B型程控放大增益倍数(此时放大器为PGA202)0 0 1 10 1 2 101 0 4 1001 1 8 1000C4~C0: 模拟信号输入通道选择位 (注:单端方式时)C4 C3 C2 C1 C0 通道代码通道号0 0 0 0 0 00H 通道10 0 0 0 1 01H 通道20 0 0 1 0 02H 通道3...... ....... .1 1 1 1 0 1EH1 1 1 1 1 1FH 通道32注:双端方式时只有C3~C0有意义,此时只有16个通道,C4位无意义②启动A/D转换 (写操作)Offset=02H,Offset是相对地址的偏移量,该写操作的I/O地址D15~D00 此时无意义,软件设定通道和增益后需执行启动A/D转换,即执行对Offset=02H的写操作③查询A/D 转换状态位+A/D转换数据 (读操作)Offset=0AH Offset:相对地址的偏移量,该读操作的I/O地址读Offset=0AH时数据对应表:Z: A/D 转换状态位 Z=1, A/D转换器正在进行转换Z=0, 转换结束,可以读取本次A/D转换数据B11~B0 : 本次A/D转换数值在用户应用程序执行启动A/D转换后,应查询”Z”标志位, 当Z=1时A/D转换器正在进行转换,处于忙状态, 当Z=0时A/D转换结束,此时读回的数据B11-B00为有效的A/D转换值④ D/A1 模出转换数据寄存器 (写操作)Offset=06H, Offset:相对地址的偏移量,对D/A1写操作的I/O地址D/A1输出数据对应表:X: 未用位B11~B00: D/A1转换12Bit数据,输出D/A1时向Offset=06H写入B11~B00数值即可⑤D/A2 模出转换数据寄存器 (写操作)Offset=08H, Offset:相对地址的偏移量,对D/A2写操作的I/O地址D/A2输出数据对应表:X: 未用位B11~B00: D/A2转换12Bit数据,输出D/A2时向Offset=08H写入B11~B00数值即可⑥16位PA口TTL数字量输出寄存器(写操作)Offset=0CH, Offset:相对地址的偏移量,该写操作的I/O端口地址输出寄存器数据格式:A15~A00 : 16Bit数字量输出,对应J2的PA15~PA00⑦: 16位TTL数据输入寄存器 (读操作)Offset=0EH , Offset:相对地址的偏移量,该读操作的I/O地址输入寄存器数据格式:B15~B00 : 16Bit数字量输入, 对应J2的PB15~PB00⑧计数定时器8254的I/O地址分配(读操作+写操作)Offset=10H-16H, Offset是相对地址的偏移量,具体I/O地址分配见下表, 对82C54的所有读写操作只有D7~D0 有意义,编程时请注意具体对82C54的工作方式设定请参阅INTEL8253手册等相关资料AMPCI-9111读写I/O操作命令表:3.8 调整电位器定义PR1: 程控放大器增益输出调整电位器PR2: A/D转换单极性零偏移调整电位器PR3: A/D转换双极性零偏移调整电位器PR4: A/D转换满量程调整电位器PR5: D/A输出电流方式基准源-2.5V调整电位器PR6: D/A1零偏移调整电位器PR7: D/A1满量程调整电位器PR8: D/A2零偏移调整电位器PR9: D/A2满量程调整电位器PR10: D/A输出基准源+5V调整电位器3.9校准①A/D部分校准a.程控放大器调整:软件设置放大倍数8倍,任一通道接一500mV电压,调整PR1 使PGA202的12脚输出为4.000V(出品时已调整)b.单极性输入0~+10V:任一通道对地短接,调整PR2,使转换值为001H;输入任一通道接5V,调整PR4,使转换值为800H;c.双极性输入-5V~+5V:任一通道对地短接,调整PR3,使转换值为800H;输入任一通道4.997V调整PR4使转换值为FFEH;需要注意的是此时A/D转换的零点与满度需反复调整d.双极性输入-10V~+10V:任一通道对地短接,调整PR3,使转换值为800H;输入任一通道10V调整PR4使转换值为FFEH;同样需要注意的是此时A/D转换的零点与满度需反复调整② D/A部分校准基准源调整: 调整PR10使336-5V输出+5.000V,出厂时已调整。

《单片机原理及应用》课件01-51单片机基本结构与存储器分配

内中断

并行口

外中断

P0 P1 P2 P3

串口模块 TXD RXD

中断模块 INT0 INT1

P0.0~P0.7

P2.0~P2.7

VCC (+5V)

GND

RAM地址 锁存器

RAM

通道0驱动器

通道0锁 存器

通道2驱动器

通道2锁 存器

ROM/ EPROM

程序地址寄存器

PSEN ALE

EA RST

B寄存器 ACC TMP2

片内地址空间:RAM 128B(00H-7FH) SFR 128B(80H-FFH)

128B SFR

128B RAM

FFH 21个SFR分布 在80H-FFH

83个可寻址位

80H 7FH

用户、

堆栈区

30H 2FH

位寻址区

20H 1FH

工作寄存器区

00H

内部RAM组织结构

10

所有的RAM区(位 寻址区、工作寄 存器区)都可以 用于存放数据, 故也称为数据缓 存寄存器

特殊功能寄存器(SFR)

▼特殊功能寄存器SFR(专用寄存器)

专用于控制、选择、管理、存放单片机内部各功能 部件的工作方式、条件、状态、结果的寄存器。

▼不同的SFR管理不同的硬件模块,负责不同的功 17 能——各司其职

换言之:要让单片机实现预定的功能,必须有相应 的硬件和软件,而软件中最重要的一项工作就是对 SFR写命令(要求)。

4 堆栈指针SP

堆栈:

在片内RAM中,指定一个专门的区域来存放某 些特别的数据,它遵循先进后出和后进先出 (LIFO/FILO)的原则,这个RAM区叫堆栈。

功用:

22

寄存器结构、存储器管理

08

例: MOV AX, [BX+03H]

CX——Count可以作计数寄存器使用。 在循环LOOP指令和串处理指令中用作隐含计数器。 例: MOV CX , 200H AGAIN: …… …… LOOP AGAIN ;(CX)-1(CX),结果0转AGAIN DX——Data可以作为数据寄存器使用。 一般在双字长乘除法运算时, 把DX和AX组合在一起存放一个双字长(32位)数,DX用来存放高16位; 对某些I/O操作DX可用来存放I/O的端口地址(口地址 256)。 例: MUL BX ; (AX)(BX)(DX)(AX) 例: IN AL , DX

奇偶标志PF(Parity Flag)

若算术运算的结果有溢出,则OF=1;

否则 OF=0

3AH + 7CH=B6H,产生溢出:OF=1 AAH + 7CH=(1)26H,没有溢出:OF=0

溢出标志OF(Overflow Flag)

3AH+7CH=B6H,就是58+124=182,

什么是溢出

处理器内部以补码表示有符号数 8位表达的整数范围是:+127 ~ -128 16位表达的范围是:+32767 ~ -32768 如果运算结果超出这个范围,就产生了溢出 有溢出,说明有符号数的运算结果不正确

01

AX——(Accumulator)作为累加器。

02

它是算术运算的主要寄存器,

03

所有I/O指令都使用这一寄存器与外部设备交换数据。

04

例: IN AL , 20H

05

OUT 30H , AX

06

BX——Base用作基址寄存器使用。

07

在计算内存储器地址时,经常用来存放基址。

0

48086CPU指令系统

XCHG DS,ES XCHG AX,DS XCHG DS,[ BX ] • 不能使用双存储器 XCHG [ BX ],[ SI ] • 不能使用立即数 XCHG AX,2000H XCHG 20H,BL

《例》用 MOV、PUSH,POP、XCHG 指令 完成两寄存器AX、BX 中数据的交换

• 指令格式

•

指令功能

OPR1、OPR2 两个操作数间交换数据

数据传送类指令

XCHG指令的应用范围

• 通用寄存器与通用寄存器间交换数据

XCHG AX,BX XCHG DL,CH • 通用寄存器与存储器间交换数据 XCHG AX,[ BX ] XCHG [ SI ],AL

数据传送类指令

XCHG指令的 禁用情况

通用传送指令 PUSH、POP 中 src、dst 操作数的使用

• 为通用寄存器、段寄存器操作数

PUSH AX、PUSH ES POP DS、 POP BX • 为存储器操作数 PUSH [ 2000H ]、PUSH [ BX ] POP [ BX ]、 POP [ 1000H ]

通用传送指令PUSH、POP中 src、dst 操作数的禁用

数据传送类指令

指令 LEA 与 LDS,LES 的区别

• LEA src

scr 表示存储器地址本身

• LDS r,src

LES r,src src 表示存储器地址中的值

地址传送指令的比较

已知:DS=09A0H,BX= 0048H

LEA DI,[BX] → 执行后:DI=0048H 等价于 MOV DI,OFFSET [BX] LDS DI,[BX] → 执行后:DI=003EH DS=0816H LES DI,[BX] → 执行后:DI=003EH ES=0816H Memory

定时器 计数器的结构、特殊功能寄存器TMOD、TCON

TC=1微秒

可见,初值越小,定时时间越长。

实验27 初值与定时时间的关系

因为 脉冲个数=溢出值-初值=216-初值 ①

计数脉冲的频率fc = 振荡频率fosc÷12

所以

定时时间=脉冲个数×计数脉冲的周期

=(216-初值)×1/计数脉冲的频率fc =(216-初值)×12/振荡频率fosc 由②式可得: … ②

5. 1-4 定时器/计数器的结构、特殊功பைடு நூலகம்寄存器TMOD、TCON

教学目的

1、单片机定时/计数器的结构及工作原理。 2、掌握初值的计算公式,理解初值、满值 和溢出值等概念。 3、掌握专用寄存器TMOD、TCON 。

教学重点

1、了解定时/计数器组成框图; 2、掌握定时/计数器的初值计算公式。

教学难点

1、GATE 门控位 GATE=0 以运行控制位TR启动定时器 GATE=1 以外中断请求信号(/IMT0或/INT1)启动定时器 2、C/T 定时方式或计数方式选择位 C/T=0 定时工作方式 C/T=l 计数工作方式(采用外部引脚的输入脉冲为计数脉冲) 3、M1、M0 工作方式选择位 M1、M0=00 方式0 M1、M0=01 方式1 M1、M0=10 方式2 M1、M0=11 方式3

微型计算机原理

I/O设备 图1.1 微型计算机的系统组成

3.

4.

微处理器子系统 存储器 I/O设备和I/O接口 系统总线

系统总线

总线是指传递信息的一组公用导线 总线是传送信息的公共通道 微机系统采用总线结构连接系统功能部件 总线信号可分成三组

地址总线AB:传送地址信息 数据总线DB

并行打印机接口LPT2 串行通信接口COM2 并行打印机接口LPT1 SDLC通信接口 BSC通信接口 单色显示/打印机适配器 彩色图形适配器CGA 软盘适配器 串行通信接口COM1

DMA控制器1 中断控制器1 定时计数器 并行接口电路 DMA页面寄存器 中断控制器2 DMA控制器2 15 协处理器

BX称为基址寄存器(Base address Register)

常用做存放存储器地址

CX称为计数器(Counter)

作为循环和串操作等指令中的隐含计数器

DX称为数据寄存器(Data register)

常用来存放双字长数据的高16位,或存放外设端口地址

第2章:(1)数据寄存器

AX称为累加器(Accumulator)

定堆栈段中的存储单元地址

内部结构

第2章:2. 指令指针寄存器

IP(Instruction Pointer)为指令指针寄存 器,指示主存储器指令的位置 随着指令的执行,IP将自动修改以指示下一 条指令所在的存储器位置 IP寄存器是一个专用寄存器 IP寄存器与CS段寄存器联合使用以确定下 一条指令的存储单元地址

进制的表示

二进制数用B或b结尾 十进制数可不用结尾字母,

也可用D或d结尾 十六进制数用H或h结尾

第二章

第2章51系列单片机系统结构2.2存储器组织

字节 地址 80H

复位后 初值 FFH

I/O 端口 0(P0 口)

*I/O 端口 1(P1 口)

P1

P1.7 A7H

90H

FFH

*I/O 端口 2(P2 口)

P2

P2.7 B7H P3.7

A0H

FFH

*I/O 端口 3(P3 口) 串行数据缓冲 *串行控制 电源控制及 波特率选择 从地址寄存器 从地址掩蔽寄存器

(1) 工作寄存器区。该区域容量为32个字节,分为 四个区,每区8个字节,对应R0~R7寄存器名。 因此,R0的物理地址可能是00H,也可能是08H、 10H 或18H;同理,R1的物理地址可能是01H, 也可能是09H、11H或19H。 任何时候都只能选择四个工作寄存器区中的一个区 作为当前工作寄存器区,当前工作寄存器区由程序 状态字寄存器PSW的b4(RS1)、b3(RS0)位确定,具 体情况4、b3位 当前区 寄存器R7~R0地址 00 0区 07H~00H 01 1区 0FH~08H 10 2区 17H~10H 11 3区 1FH~18H 由于复位后PSW的b4、b3位为00,因此复位后将选择0 区作为当前工作寄存器区。 修改PSW的b4、b3位即可选择不同的工作寄存器区,这 有利于快速保护现场,提高程序执行效率和中断的响应速 度。

SFR 寄存器名 累加器 B 寄存器 助功能寄存器 助功能寄存器 1 时钟控制寄存器 堆栈指针 数据指针低 8 位 数据指针高 8 位 *程序状态字 符号 b7 Acc B AUXR AUXR1 CKCON SP DPL DPH PSW D7H Cy AFH EA BFH IP — IPH — E7H F7 — — —

哈佛体系结构的程序存储器与数据存储器都拥有自己独立 的总线和寻址空间(典型的如DSP,TI的C5000系列)

试验一_寄存器试验

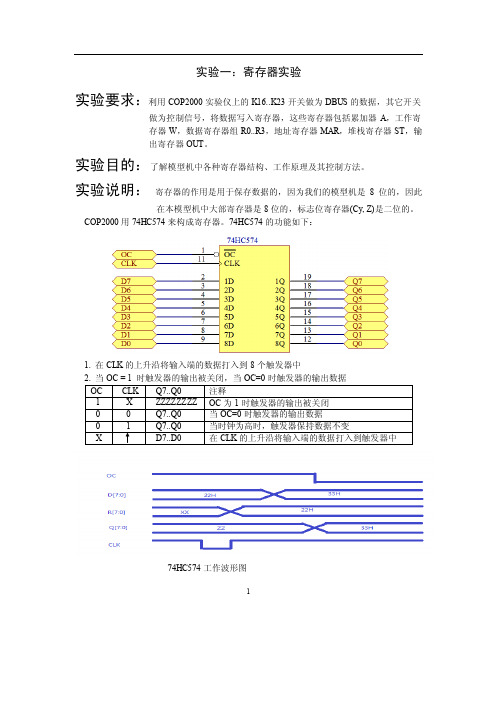

1实验一:寄存器实验实验要求:利用COP2000实验仪上的K16..K23开关做为DBUS 的数据,其它开关做为控制信号,将数据写入寄存器,这些寄存器包括累加器A ,工作寄存器W ,数据寄存器组R0..R3,地址寄存器MAR ,堆栈寄存器ST ,输出寄存器OUT 。

实验目的:了解模型机中各种寄存器结构、工作原理及其控制方法。

实验说明: 寄存器的作用是用于保存数据的,因为我们的模型机是8位的,因此在本模型机中大部寄存器是8位的,标志位寄存器(Cy, Z)是二位的。

COP2000用74HC574来构成寄存器。

74HC574的功能如下:1. 在CLK 的上升沿将输入端的数据打入到8个触发器中74HC574工作波形图第一部分:A,W寄存器实验寄存器A原理图寄存器W原理图寄存器A,W写工作波形图连接线表- 2 -将22H写入A寄存器二进制开关K23-K16用于DBUS[7:0]的数据输入,置数据22H置控制信号为:由高变低,这时寄存器A的黄色选择指示灯亮,表明选择A 寄存器。

放开CLOCK键,CLOCK由低变高,产生一个上升沿,数据22H被写入A寄存器。

将33H写入W寄存器二进制开关K23-K16用于DBUS[7:0]的数据输入,置数据33H置控制信号为:按住CLOCK脉冲键,CLOCK由高变低,这时寄存器W的黄色选择指示灯亮,表明选择W 寄存器。

放开CLOCK键,CLOCK由低变高,产生一个上升沿,数据33H被写入W寄存器。

体会:1.数据是在放开CLOCK键后改变的,也就是CLOCK的上升沿数据被打入。

2.WEN,AEN为高时,即使CLOCK有上升沿,寄存器的数据也不会改变。

第二部分:R0,R1,R2,R3寄存器实验3- 4 -寄存器R 原理图寄存器R 写工作波形图连接线表将33H 写入R0寄存器二进制开关K23-K16用于DBUS[7:0]的数据输入,置数据33HR0寄存器。

放开CLOCK 键,CLOCK 由低变高,产生一个上升沿,数据33H 被写入R0寄存器。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

數位邏輯設計 第7章 暫存器與計數器

7-3

數位邏輯設計 第7章 暫存器與計數器

7-4

數位邏輯設計 第7章 暫存器與計數器

7-5

數位邏輯設計 第7章 暫存器與計數器

7-6

數位邏輯設計 第7章 暫存器與計數器

導論(續)

7-7

• 計數器是特殊的暫存器

– 可以重覆產生預先決定的數字序列 – 設計用來記錄時脈脈波出現的次數與頻率除法

7.3 漣波計數器

7-27

7.3.1 7.3.2 7.3.3 7.3.4 7.3.5

基本電路 下數計數器 除以N的計數器 積體電路實作 漣波計數器的傳遞延遲

數位邏輯設計 第7章 暫存器與計數器 / 7.3 漣波計數器

非同步計數器導論

7-28

• 正反器時脈不同時動作

– 常只有最低位元正反器被時脈觸發 – 其餘正反器是由其他級的輸出觸發

右移順序 輸入

移位暫存器(續)

圖7.14 可控制移位暫存器

Q3

Q2

Q1

7-23

பைடு நூலகம்SHL 左移順序

輸入

Q3 D3

Q2 D2

Q1 D1

Q0 D0

CLK

數位邏輯設計 第7章 暫存器與計數器 / 7.2 暫存器

圖7.15 74194四位元雙向移位暫存器

D3 D2 D1D0

CLR S0 S1 R in L in

A B

CLK

S

Q 接下一級S

Q0

A

Q7

B

7491A

R

Q 接下一級R CLK

Q7

(a) 最低位元邏輯圖

(b)邏輯方塊圖

數位邏輯設計 第7章 暫存器與計數器 / 7.2 暫存器

移位暫存器(續)

7-20

圖7.12 74164八位元串列輸入並列輸出移位暫存器

數位邏輯設計 第7章 暫存器與計數器

圖7.13 74164串列輸入並列輸出時序圖

並列輸入

D3

D2

D1

D0

串列/並列

載入選擇

串列 SH/LD 輸入Din

串

列 輸

Q3 S3

出

Q3 R3

Q2 S2 Q2 R3

Q1 S1 Q1 R3

Q0 S0 Q0 R3

清除CLR

時脈CLK 時脈禁能 CLK INH

數位邏輯設計 第7章 暫存器與計數器 / 7.2 暫存器

圖7.7 74159並列存取移位暫存器

並列輸入

D3

D2

D1

D0

LO A D

串列輸出

PRE

Q3

D3

CLR

PRE Q2 D 2

CLR

PRE Q1 D1

CLR

PRE Q0 D0

CLR

D in 串列輸入

Q3

數位邏輯設計

Q2

Q1

Q0

CLK

並列輸出

第7章 暫存器與計數器 / 7.2 暫存器

移位暫存器(續)

7-14

圖7.6 可控制的並串列輸入移位暫存器

• 計數器結構

主要是由正反器與組合邏輯結構而成

• 計數器分類方式

依時脈的控制方式可分類為同步或非同步(漣波)

數位邏輯設計 第7章 暫存器與計數器 / 7.1 導論

7.2 暫存器

7-8

7.2.1 緩衝暫存器 7.2.2 移位暫存器

數位邏輯設計 第7章 暫存器與計數器 / 7.2 暫存器

7.2.1 緩衝暫存器

X3

X2

X1

X0

LOAD

Q3 D3

Q2 D2

Q1 D1

Q0 D0

CLK CLR

數位邏輯設計 第7章 暫存器與計數器 / 7.2 暫存器

7.2.2 移位暫存器

7-11

• 移位暫存器依輸入、輸出資料處理方式分為

(1) 串列輸入串列輸出(SISO)移位暫存器 (2) 串列輸入並列輸出(SIPO)移位暫存器 (3) 並列輸入串列輸出(PISO)移位暫存器 (4) 並列輸入並列輸出(PIPO)移位暫存器。

0

1

0

0

0

0

0

0

0

1

0

0

0

0

1

0

0

0

0

0

0

0

1

0

0

1

0

1

0

0

0

0

0

0

0

1

0

0

1

0

1

0

串列移位

串列移位

清

並列

除

載入

移位暫存器(續)

7-17

圖7.9 74165並列載入移位暫存器

數位邏輯設計 第7章 暫存器與計數器

圖7.10 74165並列載入移位暫存器的時序圖

移位暫存器(續)

7-19

圖7.11 7491A 8位元串列輸入串列輸出移位暫存器

D3 D2 D1 D0

J K S H /L D C LR C LK

74195

Q3 Q2 Q1 Q0

/ 7.2 暫存器

圖7.8 74195並列存取移位暫存器的時序圖

CLK

1

2

3

4

5

6

7

8

9

10

11

12

CLR

0

串

J

列

輸

入

K

S H /LD

D0

並 列

D1

輸 入

D2

D3

Q0

並

列

Q1

輸 出

Q2

Q3

0

0

1

0

0

0

Q2

J2

Q2 K2

Q1

J1

Q1

K1

Q0

J0

Q0 K0

(a) 邏輯電路圖

7-29

高電壓 CLK CLR

數位邏輯設計 第7章 暫存器與計數器 / 7.3 漣波計數器

CLK

74194

Q3 Q2 Q1 Q0

圖7.16 74194四位元雙向移位暫存器時序圖

74299八位元雙向移位暫存器7-26

L in

CLR

CLK S1 S0 G2 G1 R in

74299

QH HQH GQG FQF EQE DQD

CQC BQB AQA QA

數位邏輯設計 第7章 暫存器與計數器 / 7.2 暫存器

7-9

圖7.2 緩衝暫存器

X3

X2

X1

X0

PRE

Q3

D3

Q2

D2

Q1 D1

Q0 D0

CLK CLR

* X位元是預設正反器的輸入 在時脈上緣時儲存 Q=X (Q3Q2Q1Q0=X3X2X1X0)

數位邏輯設計 第7章 暫存器與計數器 / 7.2 暫存器

可控制的緩衝暫存器 7-10

圖7.3 可控制的緩衝暫存器

移位暫存器(續)

7-22

• 移位暫存器由串接的正反器組成

– 各級正反器輸出接到下一級正反器的輸入 – 所有正反器都接到共同的時脈

• 移位暫存器依資料傳送的方向分為

(1) 左移暫存器 (圖7.4 ) (2) 右移暫存器 (3) 可控制移位暫存器

數位邏輯設計 第7章 暫存器與計數器 / 7.2 暫存器

數位邏輯設計 第7章 暫存器與計數器 / 7.2 暫存器

移位暫存器(續)

7-12

圖7.4 SISO與SIPO移位暫存器

並列輸出

Q3

Q2

Q1

Q0

串列輸出

Q3 D3

Q2 D2

Q1

D1

串列輸入

Q0 D0

Din

CLK

數位邏輯設計 第7章 暫存器與計數器 / 7.2 暫存器

移位暫存器(續)

7-13

圖7.5 PISO與PIPO移位暫存器

• 常稱為漣波計數器(Ripple Counter)

– 指定級的觸發脈波必須由計數器前一級(較小的 位元)的波動而來

– 非同步計數器的操作比同步計數器慢 – 非同步計數器的控制電路經常較簡單

數位邏輯設計 第7章 暫存器與計數器 / 7.3 漣波計數器

7.3.1 基本電路

圖7.17 漣波計數器

Q3 J3 Q3 K3