数据采集电路和简易存储示波器设计

简易数字存储示波器设计

简易数字存储示波器设计摘要本文介绍了一种简易的数字存储示波器的设计。

示波器是一种广泛使用的电子测试仪器,用于显示电压随时间变化的波形。

数字存储示波器通过将波形样本存储在内存中,然后再进行显示,具有更高的分辨率和更多的功能。

本设计基于嵌入式系统,并通过一块液晶显示屏显示波形。

引言示波器是电子工程师和电子爱好者常用的测试设备之一。

然而,传统的示波器通常比较昂贵,且功能复杂。

为了满足一些简单的测试需求,我们设计了一款简易的数字存储示波器。

数字存储示波器具有存储和显示波形的功能,并且可以通过嵌入式系统实现。

本设计的核心部分是使用嵌入式开发板、模数转换器和液晶显示屏构建的简易数字存储示波器。

设计方案硬件设计嵌入式开发板本设计使用一块嵌入式开发板作为主要的处理器和控制单元。

开发板上应具备足够的计算能力和接口,以支持模数转换器、存储器和显示屏的连接。

模数转换器模数转换器(ADC)负责将输入的模拟信号转换为数字信号。

常见的ADC芯片有多种型号可选,选择合适的芯片以满足高精度和合适的采样率要求。

存储器用于存储模拟信号的样本数据。

根据要求,可以选择适当的存储器类型,如SRAM或SD卡。

显示屏显示屏用于显示存储器中的波形样本。

一块液晶显示屏是一个常见的选择,因为它可以提供高清晰度的图像和良好的视觉效果。

软件设计数据采集软件的第一步是通过ADC采集模拟信号,并将其转换为数字信号。

通过选择适当的采样率和转换精度,可以确保捕捉到所需的信号信息。

数据存储采集到的模拟信号样本将存储在嵌入式开发板的存储器中。

可以根据需要选择适当的存储器类型,以满足手头的需求。

从存储器中读取波形样本,然后将其显示在液晶显示屏上。

通过适当的算法和图形库,可以实现波形的平滑显示和良好的视觉效果。

操作流程本设计的操作流程如下:1.将待测试的电路连接到示波器的输入端口。

2.启动示波器,并设置合适的采样率和采样时间。

3.通过液晶显示屏查看波形样本。

4.根据需要对波形进行测量或分析。

简易数字存储示波器电子综合实验项目设计

2 实验要求

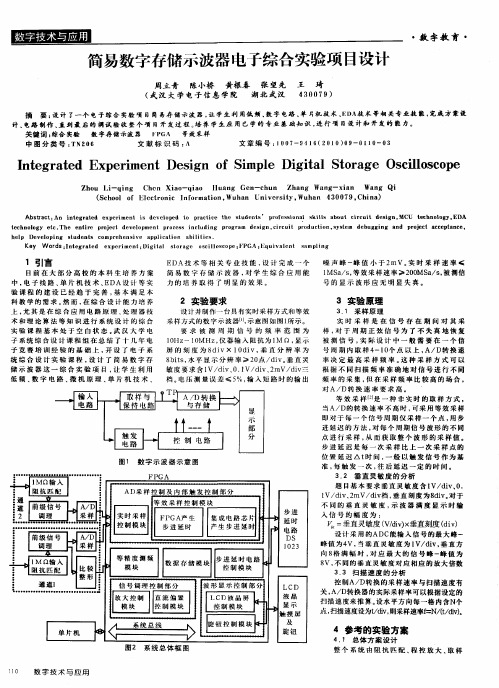

设 计 并 制 作 一 台 具 有 实 时 采 样 方 式和 等 效 采样方式的数字示 波器_示意 图如图1 示。 1 1 , 所

3 实验原理

3. 采 样 原 理 1

实 时 采 样 是 在 信 号 存 在 期 间 对 其 采

要 求 被 测 周 期 信 号 的 频 率 范 围 为 1 Iz l M Hz, 器 输 入 阻 抗 为 1 0 , 示 O ~ 0 I 仪 M 显 屏 的 刻 度 为 8 V× l d V, 直 分 辨 率 为 di i 垂 0

.

e in,ic i p o u to sse d b g i g nd r jc a c pa c tc n lg e c Th e tr p oe t e eo me p oe s n l d n p o a e h oo y t . e n ie rj c d v lp nt r cs i cu i g rgrm d sg cr u t r d cin, yt m e u g n a p oe t ce tn e,

ห้องสมุดไป่ตู้

计, 电路 制 作 、 到 最 后 的 调 试 验 收 整 个 项 目开 发 过 程 。 养 学 生 应 用 已 学 的 专 业 基 础 知 识 , 行 项 目设 计 和 开 发 的 能 力 。 直 培 进 关 键 词 : 合 实验 数 字 存 储 示 波 器 FP 等 效采 样 综 GA 中 图 分 类 号 : 20 TN 6 文 献 标 识 码 : A

he p Devel l opi s udent c ng t s ompr ehens ve app i at or abi i i s. i l i l c Ite

K y W o d I t g a e e p r me t Di t l s o a e o c lo c p FP e r s: n e r t d x e t n ; gia t r g s il s o e; GA ; u va e t Eq i l n

简易数字存储示波器设计报告[]

![简易数字存储示波器设计报告[]](https://img.taocdn.com/s3/m/149a33a32b160b4e777fcfb1.png)

简易数字存储示波器设计报告摘要本设计分为四个模块,分别是:信号前向调整模块,数据采集模块,数据输出模块和控制模块。

信号前向调整模块采用高速低噪音模拟开关(MAX4545)和宽带运算放大器(MAX817)构成可编程运算放大器,对幅度不等的输入信号分别进行不同等级的放大处理.数据采集模块采用可编程器件(EPM7128SLC84—15)控制高速A/D(TLC5510)对不同频率的输入信号分别以相应的采样速度予以采样,并将采样数据存在双口RAM(IDT7132)中.数据输出模块采用另一片可编程器件(EPM7128SLC84—15)控制两片D/A(DAC0800)分别输出采样信号和锯齿波,在示波器上以X-Y的方式显示波形.控制模块以AT89C52单片机为控制核心,协调两片可编程器件的工作,并完成其它的测量,计算及控制功能.一.总体方案设计与论证:方案一:数字示波器采用数字电路,将输入信号先经过A/D变换器,把模拟波形变换成数字信息,暂存于存储器中。

显示时通过D/A变换器将存储器中的数字信息变换成模拟波形显示在模拟示波器的示波管上。

对于存储器的地址计数及数据存取可通过数字电路对时钟脉冲计数产生地址,并选通存储器来实现;对输入信号何时触发采集可通过模拟比较器及其它简单的模拟电路实现。

但是,这种方法的硬件电路过于复杂,调试起来也不方便,不利于系统的其它功能扩展,因而不可采取。

方案二:采用AT89C52单片机。

单片机软件编程灵活,自由度大。

可通过软件编程实现对模拟信号的采集,存储数据的输出以及各种测量,逻辑控制等功能。

但是,系统要求的频带上限为50KHZ,根据采样定理,采样速度的下限为100KHZ,需要用高速A/D进行采样.假设单片机系统用12M的晶体振荡器作为系统时钟,那麽一条指令就需要1us或2us,根本无法控制A/D高速工作.因此,单纯用软件是不可能实现该系统的。

方案三:采用AT89C52单片机作为控制核心,采用可编程器件(ALTERA公司的EPM7128SLC84—15)来实现对数字系统的控制。

简易数字存储示波器设计

简易数字存储示波器设计数字存储示波器是一款用于测量电信号的仪器,它可以将收集到的信号进行数字化处理,并将结果显示在屏幕上。

本文将介绍一个简易的数字存储示波器的设计。

1. 设计目标设计一个简易的数字存储示波器,使其能够接收并显示电信号的波形,并具备一定的存储功能。

该示波器需要具备以下功能:能够调节触发电平、可以调节扫描速度、能够通过按钮进行保存和回放存储的波形。

设计需要保证简易、易于操作、能够满足基本的测量需求。

2. 硬件设计(1)电路板设计:设计一个电路板用于信号的采集和存储。

该电路板包括模拟前端电路用于信号的采集,数字转换电路将模拟信号转换为数字信号,以及存储器用于存储采集到的数据。

(2)显示屏和按键:电路板上需要配备一个液晶显示屏,用于显示采集到的波形图像。

同时,设计按键用于调节触发电平、扫描速度以及保存和回放。

3. 软件设计(1)数据采集:通过模拟前端电路采集信号,并使用数字转换电路将模拟信号转换为数字信号。

采用适当的采样率,将数据进行采样,并存储到存储器中。

(2)数据显示:通过显示屏将存储器中的数据显示为波形图像。

根据采样率和扫描速度,将存储器中的数字信号转换为波形,并在屏幕上显示。

(3)触发控制:通过按键调节触发电平,设置触发条件,使得波形显示能够达到最佳效果。

设计合适的触发电路用于触发信号。

(4)数据存储和回放:设计按键和存储器用于保存和回放采集到的波形。

按下保存键后,将当前的波形数据保存到存储器中,按下回放键后,将存储器中的波形数据重新显示在屏幕上。

4. 使用方法使用该简易数字存储示波器,首先将信号源连接到示波器的输入端,然后通过按键进行触发电平的调节和扫描速度的设置。

在适当的触发条件下,示波器将开始采集并显示信号的波形。

当波形满足要求后,可以通过按键将波形数据保存到存储器中。

保存后的波形可以通过按键进行回放,重新显示在屏幕上。

5. 总结通过以上的设计和实现,可以得到一个简易的数字存储示波器。

简易数字存储示波器设计

3. 部分电路设计及模拟

* 有关解释 程控开关Sn 必须是模拟开关,选择集成开关MAX4501; 增益调节电阻Rnn ,模拟开关的内阻计人其中; 补偿电容 改善通道频响特性

3. 部分电路设计及模拟

3)低通滤波器 * 作用:抗混迭

采样信号的频谱混迭现象及改善方法

* 抗混迭滤波器电路

3. 部分电路设计及模拟

态

校满度

信

号

程控增益和扫描速度

开始写数据 动

停止写数据

态 数据处理

信

启动显示 号

扩展显示

锁存显示

双踪显示

单次触发

用途 输入短路 输入端接0.8V 分别接通增益和选择时钟 RAMa和RAMb地址为 00H RAMa和RAMb地址为 FFH 或1FFH

将零点偏移、满度校准以及光迹分离量计入采集数 据

从RAM读数据至D/A

采用实时采样方式

2. 方案讨论

2.2 控制器的选择

* 对控制器的要求

采集速率: 高达1000kHz(1 μ s), 低至 20ms; (决定于扫描速度)

样点恢复速率:10kHz; 程控增益: 1V/div,0.1V/div,0.01V/div 双踪、扩展… * 三种方案

(1) VLSI 例如 CPLD (2) MUC (3) MUC+CPLD

① 显示器是其外设; ② 与CPLD 的连接是P0、P1口; ③ 键盘中断优线于触发中断; ④ 输出信号恢复和产生扫描电压的数据; ⑤ 单片机的有关设定

P1口,表6.4 内RAM的设定,表6.5 前向通道的控制信号,表6.6 补充说明: 扫描速度为0.2s/div时,每采样一点就显示一次,否则要产生 闪烁现象。

4) 控制器的软件设计 (根据DSO的工作过程编写)

简易数字存储示波器设计

简易数字存储示波器设计【摘要】:该简易数字存储示波器的设计是介绍基于FPGA高速数据实时采集与存储、显示技术,采用FPGA中的A/D采样控制器负责对A/D模拟信号的采样控制,并将A/D转换好的数据送到FPGA的内部RAM中存储;RAM的地址信号由地址发生计数器产生。

当完成1至数个周期的被测信号的采样后,在地址发生计数器的地址扫描下,将存于RAM中的数据通过外部的D/A进入示波器的Y端;与此同时,地址发生计数器的地址信号分配后通过另一个D/A构成锯齿波信号,进入示波器的X端。

从而实现数字存储示波器的功能。

本设计的ADC0809芯片作为高速信号的A/D转换,SRAM6264存储器作为采样后数据的存储,DAC0832芯片作为信号的 D/A转换。

程序设计采用超高速硬件描述语言VHDL描述,对其A/D转换、A/D采样控制器及数据的存储、数字输出进行编程、仿真,完成硬件和软件的设计,以及实验样机的部分调试。

关键词:数字存储示波器,FPGA,0809ADC,0832ADC, S RAM6264存储器Abstract:The simple design of digital storage oscilloscope is to introduce high-speed FPGA-based real-time data acquisition and storage, display technology, the use of FPGA in the A / D sampling controller is responsible for A / D analog signal to control the sampling and A / D conversion to the good data in the FPGA is internal RAM memory; RAM address signal generated by the address counter. Upon the completion of cycle 1 to a few samples of the measured signal, the address counter in the address scan, will keep the data in RAM through the external D / A into the scope of the Y-side; At the same time, address counter After the allocation of the address signal through a D / A constitute a sawtooth signal, the X-side into the oscilloscope. In order to achieve the functions of digital storage oscilloscope.The design of the chip as a high-speed signal ADC0809 the A / D converter, SRAM6264 memory for data storage after sampling, DAC0832 chip as a signal of D / A conversion. Programming using ultra-high-speed hardware description language VHDL description of its A / D conversion, A / D sampling controller and data storage, digital output programming, simulation, the completion of the design of hardware and software, as well as some of the experimental prototype debugging .Key words:digital storage oscilloscope, FPGA, ADC0809, DAC0832, SRAM6264 memory目录【摘要】 1【Abstract】:错误!未定义书签。

简易数字存储示波器电子综合实验项目设计

简易数字存储示波器电子综合实验项目设计

简易数字存储示波器电子综合实验项目设计详述如下:本实验要

求设计一台简易数字存储示波器(以下简称DSO),完成对信号的观察、测量和分析。

DSO在两个不同时间尺度上对电子信号进行测量,以查看

信号的周期性变化。

它的典型用途包括检测波形的工作,分析低频信

号的幅度变化,检测瞬态信号的持续时间,跟踪数字电路的时间变化等。

本实验以AD8009-18G作为DSO的A/D转换器,该模块带有基于CPLD设计的熔丝接口和控制单元,用于控制和监控示波器工作状态。

此外,本实验将使用AT89C51作为微控制器,主要用来提供操作系统,通过HD44780液晶显示屏与用户进行交互,控制数据采集和存储。

另外,为了实现示波器多功能功能,本实验系统中还设有一个键

盘输入单元,用户可以通过该单元输入控制信号,以控制显示器的分

辨率和数据采集的时间等;同时,系统还集成了一个EEPROM,用于存

储系统参数,方便用户查看和修改参数。

本实验的最终目标是通过本实验的设计,使学生能够掌握示波器

所对应的原理,了解数字存储技术,熟悉相关芯片的操作,以及学d

习数字系统设计和控制等方面的知识。

简易数字存储示波器设计

简易数字存储示波器设计任务及要求:1、设计并制作一台用普通示波器显示被测波形的简易数字存储示波器,示意图如下:2、基本要求(1)要求仪器具有单次触发存储显示方式,即每按动一次“单次触发”键,仪器在满足触发条件时,能对被测周期信号或单次非周期信号进行一次采集与存储,然后连续显示。

(2)要求仪器的输入阻抗大于100kΩ,垂直分辨率为32级/div,水平分辨率为20点/div;设示波器显示屏水平刻度为10div,垂直刻度为8div。

(3)要求设置0.2s/div、0.2ms/div、20μs/div三档扫描速度,仪器的频率范围为DC~50kHz,误差≤5%。

(4)要求设置0.1V/div、1V/div二档垂直灵敏度,误差≤5%。

(5)仪器的触发电路用内触发,要求上升沿触发、触发电平可调。

(6)观测波形无明显失真。

3、发挥部分(1)增加连续触发存储显示方式,在这种方式下,仪器能连续对信号进行采集、存储并实时显示,且具有锁存(按“锁存”键即可存储当前波形)功能。

(2)增加双踪示波功能,能同时显示两路被测信号波形。

(3)增加水平移动扩展显示功能,要求存储深度增加一倍,并且能通过操作“移动”键显示被存储信号波形的任一部分。

(4)垂直灵敏度增加0.01V/div档,以提高仪器的垂直灵敏度,并尽力减小输入短路时的输出噪声电压。

方案选择及设计理念:数字存储示波器系统由信号调理电路、采样保持电路、触发电路、A/D、D/A、X输出电路、Y输出电路、控制处理器等组成。

下图所示为数字存储示波器的原理框图。

每隔一端时间对输入的模拟信号进行采样然后经过A/D转换,把这些数字化后的信息按一定的顺序存入RAM中,当采样频率走高时,就可以实现信号的不失真存储。

当需要观察这些信息时,只要以合适的频率把这些信息从存储器RAM中按原顺序取出,经D/A转化和LPF滤波后送至示波器就可以观察到稳定的还原后的波形。

方案讨论:采样方式的选择本题要求的单次信号测量,需采用实时采样;要求最高信号频率为50KHZ,为使该频率下每个周期内有20个采样点,就要求最高采样速率为1MHZ,A/D转换速率1Ms/s,在目前市场条件下满足1MHZ采样速率的A/D无论技术条件还是价格都不是困难的。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

打开+/-12V电源

接上示波器探头,观察 0832输出的波形。

示波器上出现的波形

K 康芯科技 X

对较快速的周期模拟信号 进行采样、存进RAM、并由 0832输出,和示波器观察

K 康芯科技 X

注意源程序中,ADDA=0, 故选通IN0口,模拟信号 可由此口进入!

调协输出幅度

进入0809的IN0口的 模拟信号:64Hz

K 由到I的n-由Sy0s8te0m9采M集em进orFyPCGoAn中tenRt AEMdit的or数观X据察康芯科技

选择模式5

其余设置默认!

K 康芯科技 X

这时将频率选择16384Hz,以便快速 扫描RAM地址,使RAM输出的数据

通过0832在示波器上显示出波形

其余设置默认!

K 康芯科技 X

实验8-3. 数据采集电路和简易存储示波器设计

程序设计与硬件实验

K 康芯科技 X

LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL; ENTITY CNT10B IS

PORT (LOCK0,CLR : IN STD_LOGIC; CLK : IN STD_LOGIC; WE : IN STD_LOGIC;

64Hz是待测模拟信号的频率

K 康芯科技 X

1、先按此键0-1-0,清0一次。

2、再按此键为高电平,允许 采样数据进入RAM中

3、片刻后将键2打为低电平,禁止写入, 允许已16384Hz扫描地址,将存入RAM 的数读出,输给0832。

K 康芯科技 X

由In-System Memory Content Editor观察 到的由0809采集进FPGA中RAM的数据

计数器,由RAM数据口q[7..0]输给DAC0832, 在示波器上形成波形。

此口可接实验系统的0832的 数据口,使之产生波形

采样用ADC0809

K 康芯科技 X

DAC0832模拟模信式号5输中出8个口数码管全部用来显示 频率输出:PIO47—PIO16

波形输出用DAC0832 RAM数据口,与实验箱的DAC0832相接 注意,使用DAC0832,要打开+/-12V电源

模式5的电路结构

由于0809的模拟信号输入口有8个,由

K 3位地址线来选通,但高二位地址线已 康芯科技

在电路上接地,所以最低位地址选通线 X

ADDA=0时,选通IN0口、ADDA=1时, 选通IN1口,0809的ADDA脚由FPGA的

PIO32 (pin73)控制

选通地址锁存控制时钟信号

采样控制状态机时钟,接clock0

K 康芯科技 X

2、此电位器产生电压模 拟信号可进入IN1口!

1、注意源程序中,ADDA=1, 故选通IN1口,模拟信号 可由此口进入!

选择模式5

其余设置默认!

K 康芯科技 X

先选择采样状态机工作时钟Clock0=64Hz

康芯科技 X

3、当电位器旋动时,数码2/1将 直接显示0809的8位数据输出口

引脚锁定

RAM地址计数器清0

采样状态指示信号

采样数据输出允许控制信号 RAM数据写使能,高电平有效 D[7..0]为0809转换好的8位数据输出

RAM数据口,与实验箱的DAC0832相接

选择JTAG模式

文件下载

注意此示例存放的路径

对电位器产生的模拟信号 进行采样、存进RAM、并由 0832输出,和示波器观察

上的采样好的数据。

2、再置此键为高电平:WE=‘1’, 允许RAM中写入数据。

注意,在电位器数据输入结束 后马上按此键,使WE=‘0’,

禁止有其他数据再加入

1、先按此键(CLR):0Æ1Æ0,复位地址计数器

其余设置默认!

这连IN1口用万用表可以在此 点测到电位输出给0809的电压

3、旋转电位器,从0扫到 5V,将这过程中产生的 电压数据存入RAM中

END behav;

此模块与实验8-2的VHDL描述完全一样

K 康芯科技 X

此计数器的计数时钟频率始终等于CLKOUT, 当WE=1时,CLKOUT=LOCK0;这时系统 负责将由0809采样得到的数据存入RAM中; 当WE=0时,CLKOUT=CLK;这时禁止写入 RAM,允许以较高的时钟频率CLK扫描地址

CLK; PROCESS(CLK0,CLR,CQI)

BEGIN IF CLR = '1' THEN CQI <= "0000000000"; ELSIF CLK0'EVENT AND CLK0='1' THEN CQI <= CQI + 1; END IF;

END PROCESS; DOUT <= CQI; CLKOUT <= CLK0;

K 康芯科技 X

1、采样数据输出允许控制信号, 即OE,注意,要拨码后才能将

0809的OE与FPGA的PIO35相接!

2、采样状态指示信号EOC, 注意要拨码开关后才能 使其与FPGA的PIO8连通

注意,此二开关在0809实验 结束后必须向上拨回默认位置!

3、注意,在电位器数据输入结束 后马上按此键,使WE=‘0’, 禁止有其他数据再加入

注意短路帽插“L_F”

K 康芯科技 X

64HZ模拟信号出

设

64HZ脉冲信号进

置

模

拟

信号进入3针座的最

号

上一个端口:IN0

!

其

余

接64HZ(靠 外边的插针)

设

置

示波器由此测0832 输出的波形。

默

认

!

打开+/-12V电源

其余设置默认!

选择模式5

状态机工作时钟和WE=0时RAM地 址扫描时钟都是CLK=16384Hz

CLKOUT : OUT STD_LOGIC; DOUT : OUT STD_LOGIC_VECTOR(9 DOWNTO 0) );

END CNT10B; ARCHITECTURE behav OF CNT10B IS

SIGNAL CQI : STD_LOGIC_VECTOR(9 DOWNTO 0); SIGNAL CLK0 : STD_LOGIC; BEGIN CLK0 <= LOCK0 WHEN WE='1' ELSE

K 康芯科技 X

K 康芯科技 X

进入0809的IN0口的 模拟信号:64Hz

其余设置默认!

K 康芯科技 X

这时将频率选择16384Hz,以便快速 扫描RAM地址,使RAM输出的数据

通过0832在示波器上显示出波形

由0809采样后存储入FPGA内RAM 的数据被读出,并由0832还原的,

示波器显示的波形:64Hz