高速电路设计中的终端匹配技术

文章编号:100021506(2002)0420092205

高速电路设计中的终端匹配技术

王 昕,汪至中

(北方交通大学电气工程学院,北京100044)

摘 要:分析了高速电路设计中由于终端阻抗不匹配而引起的信号反射现象,论述了几种可以

有效的消除或削弱信号反射的终端匹配技术,包括简单的并联终端匹配,戴维南并联终端匹

配,RC 并联终端匹配和串联终端匹配技术.并阐述了不同终端匹配电路的构成和应用及各自

的优点和缺点.

关键词:信号反射;并联终端匹配;串联终端匹配

中图分类号:TN702 文献标识码:A

T erminal 2Matching T echnique in High 2Speed Board Design

W A N G Xi n ,W A N G Zhi 2z hong

(College of Electrical Engineering ,Northern Jiaotong University ,Beijing 100044,China )

Abstract :The paper analyzed the phenomenon that mismatched impedance will cause signals to reflect

back and forth down the transmission line in the high 2speed board design.Several termination techniques

which can effectively eliminate ,or at least reduce the reflections are introduced.T ermination techniques

include the simple parallel termination ,Thevenin parallel termination ,RC parallel termination and serial

termination ,whose structures ,applications ,advantages and disadvantages are expatiated sufficiently.It ’s

essential for high 2speed system to an appropriate termination.

K ey w ords :signal reflection ;parallel termination ;serial termination

美国一家著名的电子系统制造商的工程师们最近十分困惑:一个6年来一直能稳定可靠工作的成熟产品最近却不能正常运行了.设计上未做任何修改,唯一不同的是所采购的电子元器件均采用了新的器件工艺技术,使得现在的每一个芯片都成为高速器件,正是这些高速器件应用中的信号完整性问题导致了其产品的失效.

信号完整性问题的真正起因是不断缩减的信号上升和下降的时间,使得PCB 板上的每一条布线由理想的导线转变成为复杂的传输线.如今,传输线效应已经成为制约高速信号数字系统能否正常工作最关键的因素.高速PCB 板中的互联信号线构成了传输线,在PCB 互联信号线上如果有阻抗不匹配的地方就会出现信号的反射.在典型的数字系统中,驱动器的输出阻抗Z S 通常小于PCB 互联信号线的特征阻抗Z 0,而PCB 互联信号线的Z 0也总是小于接收器的输入阻抗Z L [1].这种阻抗的不匹配就会导致设计系统中信号反射的出现,并可能引起错误的触发从而导致最终数据的错误.

1 信号的反射

111 反射系数[2]

高速PCB 板中的PCB 互联信号线构成传输线,信号在负载端反射的大小取决于传输线的Z 0和负载的Z L 之间的差.信号被反射的大小用反射系数K R 来表示,负载端的反射系数

收稿日期:2001205216;修回日期:2002205225

作者简介:王昕(1974—

),女,湖南株洲人,讲师,硕士.em ail :wangxin0299@https://www.360docs.net/doc/189112110.html, 第26卷第4期2002年8月 北 方 交 通 大 学 学 报JOURNAL OF NORTHERN J IAO TON G UN IV ERSIT Y Vol.26No.4Aug.2002

K RL =(Z L -Z 0)/(Z L +Z 0)

(1)对于开路负载,K RL =1;对于短路负载,K RL =-1.可见,对于开路和短路负载,信号被100%反射回来了.K RL 为负值表明被反射的信号与原信号方向相反.

同样,信号在源端反射的大小用源端的反射系数

K RS =(Z S -Z 0)/(Z S +Z 0)(2)

112 信号反射的具体分析

设某驱动器的标准输出低电平为0.2V ,电流为24mA ,则其输出阻抗Z S 约为8.3Ω.设负载的输入阻抗Z L 大于100k Ω,远大于Z 0(约为67Ω),则负载端的K RL =1,信号在负载端会被100%反射.源端的K RS =-0.78.

现具体分析驱动器产生一个从3.5V 切换至0.2V 的信号的反射过程.

首先,根据驱动器输出阻抗Z S 与Z 0组成分压器的原理,Z 0上产生的信号ΔV 为-2.94V.由此,在源端得到的信号V S 为0.56V.当这个信号到达负载端时,V L 由于最初的传输减小了2.94V ,又由于反射减小了2.94V ,V L 最初为3.5V ,所以现在它为-2.38V.

开始时源端的信号V S 为0.56V.现在,信号又被反射回到源端,产生第二次反射,反射信号电压的大小为

V R =K RS ×

ΔV =2.29V 此时,源端信号电压V S 等于开始时的信号、第一次反射的信号和第二次反射的信号三者之和,即

V S =0.56+ΔV +V R =0.56+(-2.94)+2.29=-0.09V.

然后,第二次反射的信号又回到负载端电压为

V L =-2.38+V R +V R =-2.38V +2.29V +2.29V =2.20V.

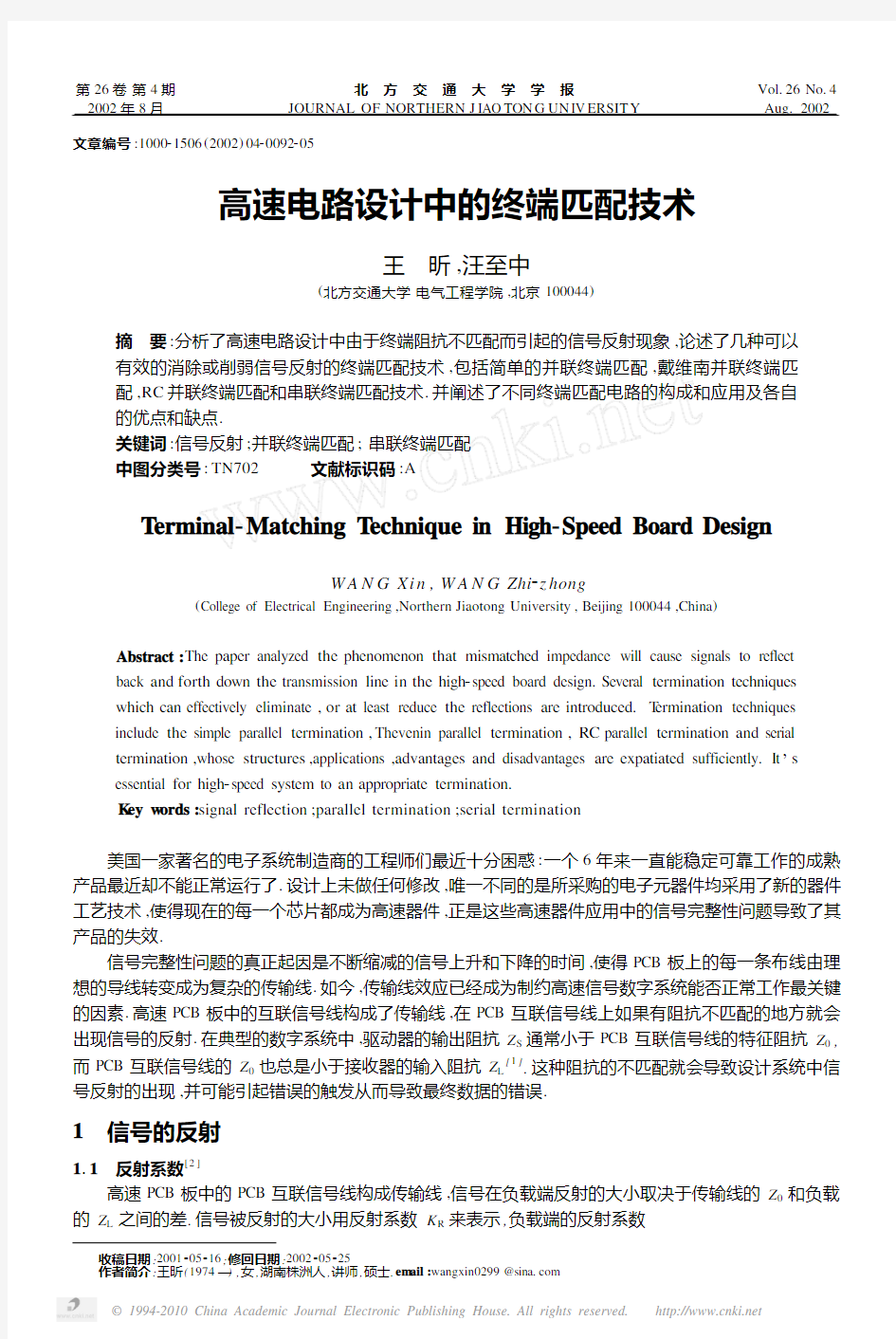

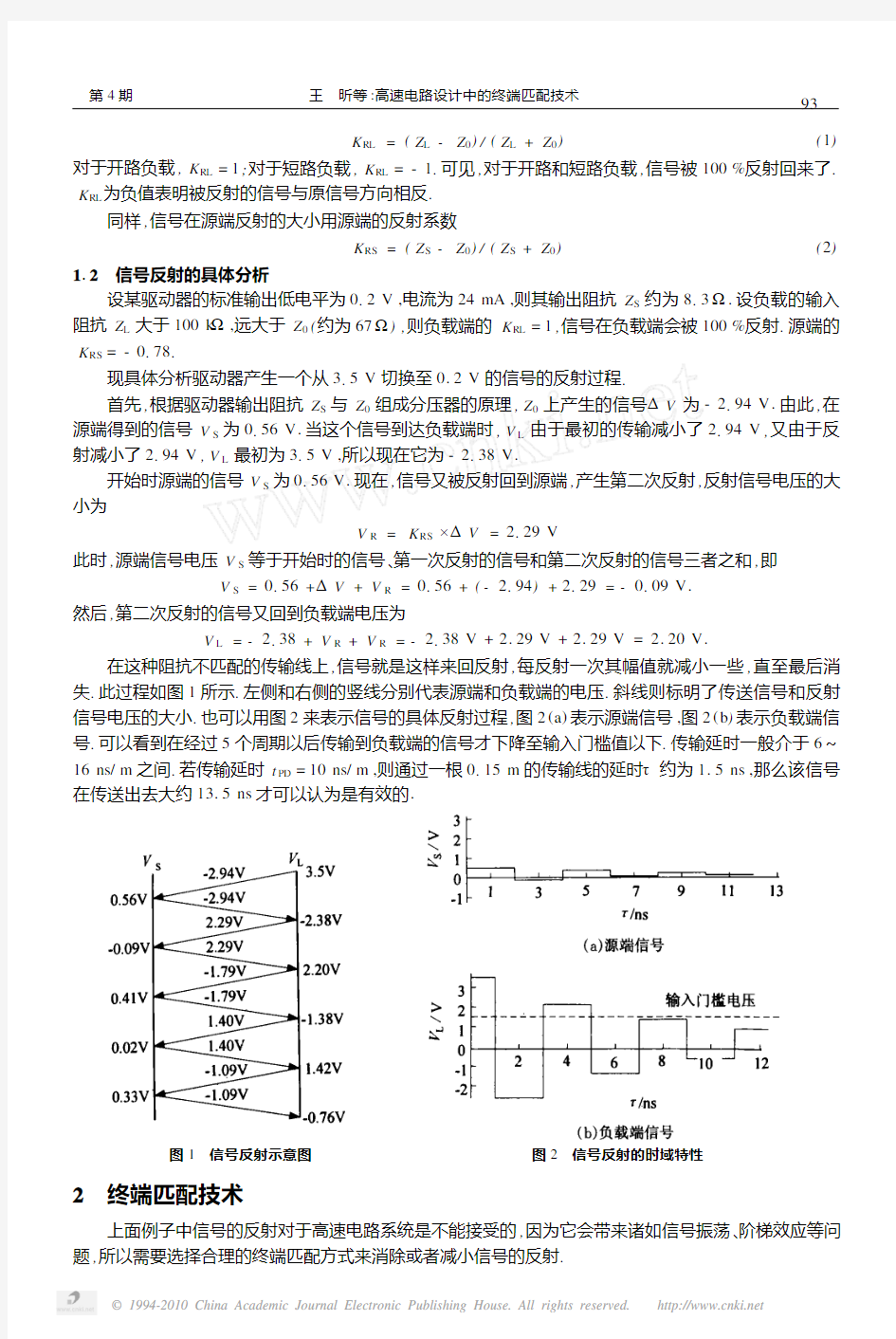

在这种阻抗不匹配的传输线上,信号就是这样来回反射,每反射一次其幅值就减小一些,直至最后消失.此过程如图1所示.左侧和右侧的竖线分别代表源端和负载端的电压.斜线则标明了传送信号和反射信号电压的大小.也可以用图2来表示信号的具体反射过程,图2(a )表示源端信号,图2(b )表示负载端信号.可以看到在经过5个周期以后传输到负载端的信号才下降至输入门槛值以下.传输延时一般介于6~16ns/m 之间.若传输延时t PD =10ns/m ,则通过一根0.15m 的传输线的延时τ约为1.5ns ,那么该信号在传送出去大约13.5ns 才可以认为是有效的

.

图1 信号反射示意图图2 信号反射的时域特性

2 终端匹配技术

上面例子中信号的反射对于高速电路系统是不能接受的,因为它会带来诸如信号振荡、阶梯效应等问题,所以需要选择合理的终端匹配方式来消除或者减小信号的反射.

3

9第4期 王 昕等:高速电路设计中的终端匹配技术

由于大多数器件的输入阻抗都很大,双极性器件约为10k Ω,CMOS 器件约为100k Ω,而驱动器的输出阻抗又很低,所以有两种方法可实现终端的匹配.一种是减小负载端的输入阻抗Z L 至Z 0以消除信号在负载端的一次反射,只需在负载上并联一个电阻即可,此方法称为并联终端匹配技术.另一种为增大驱动器的输出阻抗Z S 至Z 0以消除源端的二次反射,只需在源端串联一个电阻即可,此方法称为串联终端匹配技术.并联终端又分为简单的并联终端、戴维南并联终端和RC 并联终端3种电路.下面分析不同终端匹配电路的构成和应用及各自的优点和缺点.

211 简单的并联终端匹配

简单的并联终端匹配是最简单的终端匹配技术:通过一个电阻R T 将传输线的末端接到地或者接到V CC 上,如图3所示.电阻R T 的值必须同传输线的特征阻抗Z 0匹配,以消除信号的反射.在数字电路系统设计中,泄放到返回通路上的电流通常都大于系统中供电电源提供的电流.终端匹配到V CC 可以提高驱动器的驱动能力,而终端匹配到地则可以提高电流的吸收能力.所以,对于50%占空比的信号而言,终端匹配到V CC 要优于终端匹配到地.

简单并联终端匹配技术突出的优点就是这种类型终端匹配技术的设计和应用简便易行,在这种技术中仅需要一个额外的元器件.这种技术的缺点在于终端匹配电阻会带来直流功率消耗,终端匹配电阻的阻值通常在50Ω到150Ω范围之间,所以在逻辑高和逻辑低状态下都会有恒定的直流电流从驱动器流入其直流负载中.另外这种终端匹配技术也会使信号的逻辑高输出电平下降.将TTL 输出终端匹配到地会降低V OH 的电平值,

.

图3 简单的并联终端匹配

在容性负载情况下,相对于没有实现终端匹配的信号线来说,并联终端匹配同时也会导致更低的信号回转速率.在并联终端匹配技术中如果信号线的阻抗小于100Ω,TTL 电平的器件需要有24mA 的直流输出电流,这是因为V OH (min )=2.4V.基于以上的原因,在电池供电的系统中不建议使用这种并联终端匹配技术.另外,终端匹配电阻的功率消耗还取决于信号的占空比:较低占空比的信号通过终端匹配电阻连接到地会消耗更少的能量,而较高占空比的信号通过终端匹配电阻连接到V CC 会消耗更少的能量.212 戴维南并联终端匹配

戴维南终端匹配技术采用一个戴维南分压器,如图4所示.要求R 1和R 2的并联与传输线的特征阻抗Z 0匹配,即[3]

R TH =R 1∥R 2=R 1R 2R 1+R 2=Z 0(3)

戴维南电压V TH 为

V TH =V R 2=R 2R 1+R 2?V CC (4

)

图4 戴维南并联终端匹配

49北 方 交 通 大 学 学 报 第26卷

V TH 的选择必须确保驱动器的输出高电平I OH 和低电平的I OL 电流在驱动器的性能指标范围以内,其值可

按下式确定V TH =V OH (min )-I OH (max )3(Z S +Z 0)

(5)由式(3,4)可得R 1=

Z 0V CC V TH , R 2=Z 0V CC V CC -V TH .R 1的作用是帮助驱动器更加容易到达逻辑高状态,这就需通过从V CC 向负载注入电流来实现.R 2的作用是帮助驱动器更加容易到达逻辑低状态,这通过R 2向地释放电流来实现.恰当地选取R 1和R 2的值可以加强驱动器的扇出能力,并且淡化由于信号占空比不一致而导致的功耗的改变.

戴维南终端匹配技术的优势在于,在这种匹配方式下,终端匹配电阻同时还作为上拉电阻和下拉电阻来使用,因而提高了系统的噪声容限.

戴维南终端匹配的一个缺点就是无论逻辑状态是高还是低,在V CC 到地之间都会有一个常量的直流电流存在,因而会导致终端匹配电阻中有静态的直流功耗.信号负载为电容时,相对于没有匹配的信号线而言,戴维南终端匹配技术同样会改善信号的质量,使得信号的摆动缩小.

213 RC 终端匹配技术

RC 终端匹配技术,由一个电阻R T 和一个电容C 组成,电阻R T 和电容C 连接在传输线的负载一端,如图5所示.电阻R T 的值必须同传输线的特征阻抗Z 0的值匹配才能消除信号的反射.电容C 为[3]

C =t P

D Z 0?ln Z 0

Z 0-Z S =t PD Z 0?ln 1-K RS -2K RS

,由式(2)可得Z 0/(Z 0-

Z S )=(1-K RS )/(-2K RS ).

图5 RC 终端匹配

可见电容C 的选择很复杂.电容值太小会导致RC 时间常数过小,这样一来该RC 电路就类似于一个尖锐信号沿发生器,从而引入信号的过冲与下冲,一般电容值需大于100p F.另一方面,较大的电容值会带来更大的功率消耗.通常情况下,要确保RC 时间常数大于该传输线负载延时的两倍,即

τ=R C >2t PD 1+C D /C 0.

其中,C D 为接收器的分布电容,C 0为PCB 传输线的内在电容.

RC 终端匹配技术的优势在于终端匹配电容阻隔了直流通路,因此节省了较大的功率消耗,此技术也称为AC 终端匹配技术.同时恰当地选取匹配电容的值,可以确保负载端的信号波形接近理想的方波,而信号的过冲与下冲又都很小.

RC 终端匹配技术的一个缺点是信号线上的数据可能出现时间上的抖动.标准的RS 2422接口协议不建议使用RC 终端匹配技术.同样,电流模式的驱动器也不能采用RC 终端匹配技术.

214 串联终端匹配

不同于以上介绍的并联终端匹配技术,串联终端匹配技术是信号源端的终端匹配技术,它由连接在驱动器输出端和信号线之间的一个电阻R T 组成,如图6所示.驱动器输出阻抗Z S 与电阻R T 的串联必须同信号线的特征阻抗Z 0匹配,即

R T =Z 0-Z S .

若前面的例子中采用这种串联终端匹配方式,已知Z 0=67Ω,Z S =8.3Ω,则匹配电阻R T =58.7Ω.若驱动器产生一个从3.5V 切换至0.2V 的信号,分析此过程中信号的传送如下:根据Z S 与R T 的串联

59第4期 王 昕等:高速电路设计中的终端匹配技术

图6 串联终端匹配

与Z 0组成分压器的原理,可计算出Z 0上产生的信号ΔV 为-1.65V.也就是说加在信号线上的电压实际只有一半的信号电压.由此,在源端得到的信号V S 为1.85V.若负载端开路,由于负载端阻抗不匹配,K RL =1,当这个1.85V 的信号到达负载端时,就被100%反射回来,此时

V L =V S +ΔV =1.85-1.65=0.2V .

当反射信号回到源端时,由于源端的Z S 已通过R T 与Z 0匹配,即K RS =0,所以不会产生新的信号反射了,此时

V S =1.85+ΔV +0=0.2V .

可见,采用串联终端匹配技术后信号只反射了一次.但是与并联终端匹配消除第一次反射相比,串联终端匹配只消除了信号的二次反射,故只有等到两倍的信号在传输线上的传输延时后(此例为2τ=2ns ),才能

在驱动端看到变化后的完整的信号幅度.此过程可用图7表示.

(a )源端信号(b )负载端信号

图7 采用串联终端匹配的信号时域特性

串联终端匹配技术的缺点是采用这种匹配技术时,很难将串联匹配电阻调整到一个非常合适的值.因为许多驱动器都是非线性的,如TTL 器件,其输出阻抗随着器件逻辑状态的变化而变化,所以串联匹配电阻只能选择一个适中的值.

串联终端匹配技术的优点是这种匹配技术仅仅为系统中的每一个驱动器增加一个电阻元件,而且相对于其它的电阻类型终端匹配技术来说,串联终端匹配技术中匹配电阻的功耗是最小的,而且串联终端匹配技术不会给驱动器增加任何额外的直流负载,也不会在信号线与地之间引入额外的阻抗.

3 说明

适合于所有的终端匹配技术的一点是:由于布局布线过程的进展和多点连接环境下的负载传输线的有效阻抗Z 0会减少.实际的带负载的特征阻抗Z 0′是[3]

Z 0′=Z 01+C D /C 0

这里C 0是PCB 线的内在电容值,而C D 是接收器件的分布电容(总的负载电容除以PCB 线的长度).所以传输线上的分布式电容负载会减小该特征阻抗的值.对特征阻抗Z 0的这一校正系数适合于所有可能的终端匹配技术,取决于总的综合的系统结构.

参考文献:

[1]Sherman Lee ,Mark McClain ,Dave Stoenner.Am29000322Bit Stramlined.Instruction Processor Memory Design Handbook

[A ].Advanced Micro Devices Inc.,Sunnyvale[C].CA :Appendix A ,Memory Array Loading Calculations ,1985.

[2]Ramo ,Whinnery ,Van Duzer.Fields and Waves in Communications Electronics[M ].Jonn :Whilley &S ons ,1965.

[3]Knack ,K ella.Debunking High 2Speed PCB Design Myths.ASIC &EDA[M ].Los Altos :James C.Uh1,J uly 1993.

69北 方 交 通 大 学 学 报 第26卷

今天终于弄懂了PCB高速电路板设计的方法和技巧

[讨论]今天终于弄懂了PCB高速电路板设计的方法和技巧受益匪浅啊 电容, 最大功率, 技巧 高速电路设计技术阻抗匹配是指负载阻抗与激励源内部阻抗互相适配,并且得到最大功率输出的一种工作状态。高速PCB布线时,为了防止信号的反射,要求线路的阻抗为50Ω。这是个大约的数字,一般规定同轴电缆基带50Ω,频带75Ω,对绞线则为100Ω,只是取整数而已,为了匹配方便。根据具体的电路分析采用并行AC端接,使用电阻和电容网络作为端接阻抗,端接电阻R要小于等于传输线阻抗Z0,电容C必须大于100pF,推荐使用0.1UF的多层陶瓷电容。电容有阻低频、通高频的作用,因此电阻R不是驱动源的直流负载,故这种端接方式无任何直流功耗。 串扰是指当信号在传输线上传播时,因电磁耦合对相邻的传输线产生不期望的电压噪声干扰。耦合分为容性耦合和感性耦合,过大的串扰可能引起电路的误触发,导致系统无法正常工作。根据串扰的一些特性,可以归纳出几种减小串扰的方法: 1、加大线间距,减小平行长度,必要时采用jog 方式布线。 2、高速信号线在满足条件的情况下,加入端接匹配可以减小或消除反射,从而减小串扰。 3、对于微带传输线和带状传输线,将走线高度限制在高于地线平面范围要求以内,可以显著减小串扰。 4、在布线空间允许的条件下,在串扰较严重的两条线之间插入一条地线,可以起到隔离的作用,从而减小串扰。传统的PCB设计由于缺乏高速分析和仿真指导,信号的质量无法得到保证,而且大部分问题必须等到制版测试后才能发现。这大大降低了设计的效率,提高了成本,在激烈的市场竞争下显然是不利的。于是针对高速PCB设计,业界人士提出了一种新的设计思路,成为“自上而下”的设计方法,经过多方面的方针分析和优化,避免了绝大部分可能产生的问题,节省了大量的时间,确保满足工程预算,产生高质量的印制板,避免繁琐而高耗的测试检错等。利用差分线传输数字信号就是高速数字电路中控制破坏信号完整性因素的一项有效措施。在印制电路板(PCB抄板)上的差分线,等效于工作在准TEM模的差分的微波集成传输线对。其中,位于PCB顶层或底层的差分线等效于耦合微带线,位于多层PCB内层的差分线,等效于宽边耦合带状线。数字信号在差分线上传输时是奇模传输方式,即正负两路信号的相位差是180,而噪声以共模的方式在一对差分线上耦合出现,在接受器中正负两路的电压或电流相减,从而可以获得信号消除共模噪声。而差分线对的低压幅或电流驱动输出实现了高速集成低功耗的要求。

高速电路设计的经典案例

该文章版权归 smarteebit 所有。若有疑问,请联系 songmin2@https://www.360docs.net/doc/189112110.html,

高速数字设计的经典案例若干则

【摘要】 随着这些年半导体工艺突飞猛进的发展, “高速数字设计”对广大硬件工程师来说,已经不再是一 个陌生的词。从航空、雷达到汽车电子,从无线通信到有线接入,甚至在一些低端的嵌入式系统上,高 速数字电路都已经在大行其道。 目前行业内已经有不少关于高速数字电路理论的好文章, 笔者就不在这 上面掺和了。 本文着眼于理论和实际相结合, 所用的素材都来自笔者亲历过的案例, 相信活生生的事实, 比空洞的理论更有说服力,也希望能使入行不久的硬件工程师们得到他们想要的信息,今后少走弯路。 由于不会对理论作过多的阐述, 因此, 本文的阅读对象应该具有一点点高速数字设计的理论基础, 请知。 【关键词】 高速数字设计 高速数字电路 案例

1 信号完整性

什么词汇在高速数字设计中出现得最多?对了,SI(Signal Integrity),也就是信号完整性。信 号完整性问题的表现形式多种多样,主要有如下种类:

图 1 过冲(OVERSHOOT)

图 2 振铃(RING)

图 3 非单调性(NON MONOTONIC)

过冲: 当较快的信号沿驱动一段较长的走线, 而走线拓扑上又没有有效的匹配时, 往往会产生过冲。 过冲带来的问题主要是“1”电平高于接收端器件的输入最大电压值(VIHmax),或“0”电平低于接收端 器件的输入最小电压值(VILmin),这样可能给器件带来潜在的累积性伤害,缩短其工作寿命,从而影响 产品的长期稳定性。

Smarteebit

Page 1 of 17

综合电路设计报告模板教材

综合电路设计报告 院部:信息工程学院 专业班级:14电子一班 学号:21406021028 姓名:孙双元 指导教师:宁仁霞 黄山学院电子信息教研室

设计内容一:多路信号发生器的设计与制作 【要求:正文部分字体为宋体小四,段落行距单倍】提交时,该部分内容删除,以下红色部分的说明文字,提交时删除 1.设计目的 研究目的 信号发生器用来产生频率为20Hz~200kHz的正弦信号(低频)。除具有电压输出外,有的还有功率输出。所以用途十分广泛,可用于测试或检修各种电子仪器设备中的低频放大器的频率特性、增益、通频带,也可用作高频信号发生器的外调制信号源。另外,在校准电子电压表时,它可提供交流信号电压。低频信号发生器的原理:系统包括主振级、主振输出调节电位器、电压放大器、输出衰减器、功率放大器、阻抗变换器(输出变压器)和指示电压表。 信号发生器的种类繁多,而多路信号发生器具有体积小、价格低、性能稳定的优点,所以实用性很好。该信号发生器,产生正弦波、方波、三角波三种信号,并且信号的频率、幅值、占空比、相位可调,产生的信号可以用实际的示波器显示,也可通过DAQ采集卡进行采集再显示。对于庞大的工厂来说,它不但节约了大量的硬件仪器所需要的费用,还给操作人员带来了方便 多路信号发生器有两个按键,一个按键控制信号类型,按下键一依次改变信号类型和停止产生波形;另一个按键改变信号频率。通过设计让我们更深入了解虚拟仪器的基本原理及观念,掌握利用相关的软、硬件平台完成虚拟仪器设计的方法和步骤。在设计时,运用到单片机、74LS138译码电路、DAC0832转换电路知识,并且能够熟练掌握电路的分析及设计 2.设计内容和要求 1.输出波形:正弦波方波三角波等; 2.频率范围:1KHZ-10KHZ,10KHZ-100KHZ; 3.输出电压:方波Up-p=24V,三角波Up-p=8V,正弦波Up-p>1V; 4.波形特征:方波tr<10s,三角波失真系数THD<2%,正弦波失真系数5%. 3.设计结果

日本的电子工程师们写的一套书

以下是日本的电子工程师们写的一套书,相当好,堪称电子系统设计里面的经典之作!!! 不管你们搞不搞电子设计,能精读其中的几本,也会使你们能像工程师那样思考问题,变得更专业!!! 最重要的是,这套书非常精简,有一定的理论解释,同时更偏重于工程应用和设计实例,比较适合广大电子类工科学生和电子设计爱好者们!!! 电子系统设计,模拟电路很重要,也是每个电子系统设计者必备的基础知识和基本技能,模拟电路的设计水平往往决定了电路系统的整体指标和整体性能,因此希望你们不管自己偏向于数字方向、嵌入式方向还是模拟电路方向,都要最起码了解模拟电路的基本原理和常见电路形式。 当然,这些书都是希望大家在学有余力的情况下,根据自己的喜好和方向选择性阅读,切不可耽误自己正常上课的时间和精力。因为本人是做仪器仪表和信号类方向,考虑到模拟电路的重要性,只推荐几本信号相关的模拟电路书籍(红色标记),供大家课余时间阅读。 张军,拜上。写于2010年10月8号,电子科大清水河校区。

一、实用电子电路设计丛书(系列) 1、晶体管电路设计(上) 2、晶体管电路设计(下) 3、数字逻辑电路和ASIC设计 4、数字系统设计 5、OP放大电路设计 6、振荡电路的设计与应用 二、图解实用电子技术丛书(系列) 1、OP放大器应用技巧100例 2、模拟技术应用技巧101例 3、传感器应用技巧141例 4、存储器IC的应用技巧 5、电子元器件应用技术 6、锁相环PLL电路设计与应用 7、电子元器件的选择与应用 8、LC滤波器设计与制作 9、高频电路设计 10、高低频电路设计与制作—从放大电路的设计到安装 技巧 11、数字电路设计 12、高频电路设计与制作

高速电路设计

目 录 34 1.10.3电容耦合和电感耦合的比值 (33) 1.10.2翻转磁耦合环 (30) 1.10.1共模电感和串扰的关系 (28) 1.10共模电感 (27) 1.9.2终端电阻之间的共模电容 (26) 1.9.1共模电容和串扰的关系 (25) 1.9共模电容 (25) 1.8.2图1.15的应用 (23) 1.8.1在响应曲线下测试覆盖面积 (23) 1.8估算衰减时间的一个更好的方法 (18) 1.7普通电感 (12) 1.6普通电容 (10) 1.5四种类型的电抗 (9) 1.4关于3-dB 和 频率均方根值 的注意点 (8) 1.3集中式系统和分布式系统 (7) 1.2时间和距离 (3) 1.1 频率和时间 (3) 第 1 章 基本原理 (1) 前言.............................................................................

前言 这本书是专门为电路设计工程师写的。它主要描述了模拟电路原理在高速数字电路设计中的分析应用。通过列举很多的实例,作者详细分析了一直困扰高速电路路设计工程师的铃流、串扰和辐射噪音等问题。 所有的这些原理都不是新发现的,这些东西在以前时间里大家都是口头相传,或者只是写成应用手册,这本书的作用就是把这些智慧收集起来,稍作整理。在我们大学的课程里面,这些内容都是没有相应课程的,因此,很多应用工程师在遇到这些问题的时候觉得很迷茫,不知该如何下手。我们这本书就叫做“黑宝书”,它告诉了大家在高速数字电路设计中遇到这些问题应该怎么去解决,他详细分析了这些问题产生的原因和过程。 对于低速数字电路设计,这本书没有什么用,因为低速电路中,'0'、'1' 都是很干净的。 但是在高速数字电路设计中,由于信号变化很快,这时候模拟电路中分析的那些影响会产生很大的作用,使得信号失真、变形,或者产生毛刺、串扰等,作为高速数字电路的设计者,必须知道这些原理。这本书就详细的解释了这些现象产生的原理以及他们在电路设计中的应用。 书本中的公式和例子对于那些没有受过专业模拟电路设计训练的读者也是有用的。在线性电路原理理论课程中只接受了第一年的培训的读者,也许能更好地掌握本书的内容。 第1章——第3章分别介绍了模拟电路术语、逻辑门高速特性和标准高速电路测量方法和技巧等内容。这三章内容构成了本书的核心,应该包括在任何高速逻辑设计的学习中。 其余章节,第4章——第12章,每一章都讲述了一个高速逻辑设计中的专门问题,我们可以按照自己的需要选择学习。 附录A收集了本书各部分的要点,列出了所提出的最重要的思想和概念。它可以作为我们进行系统设计时的一个检查要点(CHECKLIST),或者碰到问题时可作为本书内容的索引。 附录B详细给出了各种上升时间测量形式背后的数学假设。它有助于把本书的结论跟相关术语的标准及来源联系起来。 附录C是列举物理结构中的电阻、电容和电感计算的标准公式。这些公式已经在MathCad上实现并可以从作者处获得。

控制系统数字仿真

现代工程控制理论 实验报告 实验名称:控制系统数字仿真技术 实验时间: 2015/5/3 目录 一、实验目的 (3) 二、实验内容 (3)

三、实验原理 (3) 四、实验方案 (6) 1、分别离散法; 6 2、整体离散法; 7 3、欧拉法 9 4、梯形法 10 5、龙格——库塔法 11 五、实验结论 (12) 小结: (14) 一、实验目的

1、探究多阶系统状态空间方程的求解; 2、探究多种控制系统数字仿真方法并对之进行 精度比较; 二、实验内容 1、对上面的系统进行仿真,运用分别离散法进 行分析; 2、对上面的系统进行仿真,运用整体离散法进 行分析; 3、对上面的系统进行仿真,运用欧拉法进行分 析; 4、对上面的系统进行仿真,运用梯形法进行分 析; 5、对上面的系统进行仿真,运用龙泽——库塔法进行分 析; 6、对上面的几种方法进行总计比较,对他们的 控制精度分别进行分析比较; 三、实验原理 1、控制系统状态空间方程整体离散法的求解;

控制系统的传递函数一般为 x Ax Bu Y Cx Du ? =+ =+ 有两种控制框图简化形式如下: KI控制器可以用框图表示如下: p K i K1 s 惯性环节表示如下: K T 1 s 1T - 高阶系统(s) (1)n K G T = + 的框图如下 对于上面的框图可以简写传递函数 x Ax Bu Y Cx Du ? =+ =+

根据各环节间的关系可以列写出式子中出现的系数A 、B 、C 和D ,下面进行整体离散法求传递函数的推导 00 ()0 ...*()...()(t)(0)...*(t)(0)(t)(0)()(0)At At At At At t t At t t A AT t AT A At t t At At A At A t x Ax Bu e e x e Ax e Bu d e x dt Bue dt dt e x Bue dt e x x Bue d e x x e e Bue d x x e Bue d t KT x kT x e τ ττ τττττ ? -? -----------=+=+=?=?=+=+?=+==????? ?①①得②③ ③得令()0 (1)(1)[(1)]0 (1)[(1)]0 ...(1)[(1)](0)...*(1)()(1)T (1)()()() ,kT A kT A kT k T A k T A k T AT k T AT A k T kT T T AT At AT At AT Bue d t K T x k T x e Bue d e x k e x k Bue d k t x k e x k e Budt e x k e Bdt u k e ττττττ τ?-+?++-++-+=++=+-+-=+-=+=+=+?Φ=? ? ? ??④ 令⑤ ⑤④得令令0 (1)()(1) T At m m e Bdt x k x k x k Φ=+=Φ?+Φ?+?得 这样,如果知道系数,就可以知道高阶系统的传递函数和状态空间方程。 2、 在控制系统的每一个环节都加一个采样开

模拟电路_Multisim软件仿真教程

第13章Multisim模拟电路仿真本章Multisim10电路仿真软件, 本章节讲解使用Multisim进行模拟电路仿真的基本方法。 目录 1. Multisim软件入门 2. 二极管电路 3. 基本放大电路 4. 差分放大电路 5. 负反馈放大电路 6. 集成运放信号运算和处理电路 7. 互补对称(OCL)功率放大电路 8. 信号产生和转换电路 9. 可调式三端集成直流稳压电源电路 13.1 Multisim用户界面及基本操作 13.1.1 Multisim用户界面 在众多的EDA仿真软件中,Multisim软件界面友好、功能强大、易学易用,受到电类设计开发人员的青睐。Multisim用软件方法虚拟电子元器件及仪器仪表,将元器件和仪器集合为一体,是原理图设计、电路测试的虚拟仿真软件。 Multisim来源于加拿大图像交互技术公司(Interactive Image Technologies,简称IIT公司)推出的以Windows为基础的仿真工具,原名EWB。 IIT公司于1988年推出一个用于电子电路仿真和设计的EDA工具软件Electronics Work Bench(电子工作台,简称EWB),以界面形象直观、操作方便、分析功能强大、易学易用而得到迅速推广使用。 1996年IIT推出了EWB5.0版本,在EWB5.x版本之后,从EWB6.0版本开始,IIT对EWB进行了较大变动,名称改为Multisim(多功能仿真软件)。 IIT后被美国国家仪器(NI,National Instruments)公司收购,软件更名为NI Multisim,Multisim经历了多个版本的升级,已经有Multisim2001、Multisim7、Multisim8、Multisim9 、Multisim10等版本,9版本之后增加了单片机和LabVIEW虚拟仪器的仿真和应用。 下面以Multisim10为例介绍其基本操作。图13.1-1是Multisim10的用户界面,包括菜单栏、标准工具栏、主工具栏、虚拟仪器工具栏、元器件工具栏、仿真按钮、状态栏、电路图编辑区等组成部分。

高速电路设计参考(包含器件选择以及走线)

高速电路设计规则参考(初稿) 张工 2015/3/8 高速电路完整性分析: 信号完整性是指在电路设计中互连线引起的所有问题,它主要研究互连线的电气特性参数与数字信号的电压电流波形相互作用后,如何影响到产品性能的问题。主要表现在对时序的影响、信号振铃、信号反射、近端串扰、远端串扰、开关噪声、非单调性、地弹、电源反弹、衰减、容性负载、电磁辐射、电磁干扰等。(引用于博士对信号完整性的理解)同时,归根到底,信号失真源自于信号传输过程的阻抗变化,因此假如一个信号的传输途径处处阻抗匹配且均衡,这信号的质量可以很好保留,不过实际中不能完全做到,但可以通过注意这些问题从而是信号质量有所改善,另外在多次阻抗改变和跌落之后信号会出现信号振铃、信号反射、上冲以及下冲等现象,此时可以通过一些有效的方法避免。 以下将从信号完整性的层面出发,介绍以下一些高速电路的设计规则参考: 一、器件选型及布局 1电容选型 1.1不同容值电容搭配 通常情况下有经验的工程师都知道一般电源入口处都会搭配容量大小不一样的 电容进行去耦或储能,但经常一知半解,因为从理论计算,大小电容并联就是两 个电容的容值相加,没有什么作用。不过现实中由于制作工艺以及封装的不同, 不同容值的电容其ESL和ESR是不同的,其谐振频率也不同。 因此在信号频率小于其器件的谐振频率时电容表现出容性,当信号频率大于器件的 谐振频率时电容表现为感性,因此高速电路中大电容常常由于谐振频率较低,表现 出感性特性,此时电路中的电容将被大大削弱了去耦特性。因此通过搭配不同容值 的电容可以在较大范围内满足电路的需求。同时尽量选用小ESL的电容。

通常设计中可以通过搭配不同数量级的电容改善去耦效果。 1.2电容封装 同样容量的不同封装形式的电容其谐振频率也不同,通常小封装的电容等效串联电感更低,效串联电感基本相同电容有更低的等效串联电感。某型号陶瓷电容的ESL和ESR 测量值如下: 因此高速电路中尽量选用小封装的器件进行设计。 2电容的布局 2.1电容去耦半径和电容的摆放位置 有经验的工程师都会知道电容布局时小电容需要尽量靠近电源入口,大电容就可以放的远一点,这是因为电容对电源进行去耦时其存在一个去耦范围,即“去耦半径”。超过该电容的去耦半径时的其将起不到去耦半径。同时大容值的电容的去耦半径大,小电容的去耦半径小。例如某电路中0.001UF的陶瓷电容的去耦半径大概为2.4厘米。其去耦半径大小不仅与器件本身,同时还跟焊接的电路有关,不过起主导作用的是容值。 2.2降低EMI时电容的连线 随着工作频率升高,滤波器件的感抗和PCB线路感抗开始呈现,且频率越高感抗越大,对供电回路的纹波影响越明显,因此需要选用感抗小的小容量电容提供良好的去耦。同时还应缩短滤波电容两端到负载的电源与地的距离,尽可能将去耦电容和负载器件放置在同一层。为降低EMI,也应尽量减小电源线和地回路之间包围的面积。 以下图例都是说明如何设计良好的去耦电路拓扑结构和布线策略。

怎样利用电路仿真软件进行模拟电路课程的学习

怎样利用电路仿真软件进行模拟电路课程的学习电路分析实验报告 实验二 学习用multisim软件对电路进行仿真 一.实验要求与目的 1.进一步熟悉multisim软件的各种功能。 2.巩固学习用multisim软件画电路图。 3.学会使用multisim里面的各种仪器分析模拟电路。 4.用multisim软件对电路进行仿真。 二、实验仪器 电脑一台及其仿真软件。 三.实验内容及步骤

(1)在电子仿真软件Multisim 基本界面的电子平台上组建如图所示的仿真电路。双击电位器图标,将弹出的对话框的“Valve”选项卡的“Increment”栏改成“1”,将“Label”选项卡的“RefDes”栏改成“RP。 ” 2)调节RP大约在35%左右时,利用直流工作点分析方法分析直 流工作点的值。直流工作点分析(DC Operating Point Analysis)是用来分析和计算电路静态工作点的,进行分析时,Multisim 自动将电路分析条件设为电感、交流电压源短路,电容断开。 单击Multisim 菜单“Simulate/Analyses/DC operating Point…”,在弹出的对话框中选择待分析的电路节点,如2图所示。单击Simulate 按钮进行直流工作点分析。分析结果如图3所示。列出了

单级阻容耦合放大电路各节点对地电压数据,根据各节点对地电压数据,可容易计算出直流工作点的值,依据分析结果,将测试结果填入表1中,比较理论估算与仿真分析结果。 表1 静态工作点数据 电压放大倍数测试 (1)关闭仿真开关,从电子仿真软件Multisim 10基本界面虚拟仪器工具条中,调出虚拟函数信号发生器和虚拟双踪示波器,将虚拟函数信号发生器接到电路输入端,将虚拟示波器两个通道分别接到电路的输入端和输出端,如图4所示。 (2)开启仿真开关,双击虚拟函数信号发生器图标“XFG1”,将打开虚拟函数信号发生器放大面板,首确认“Waveforms”栏下选取的是正弦信号,然后再确认频率为1kHZ”;再确认幅度为 10mVp,如图5所示。 四.仿真分析 动态测量仿真电路

数字电路课程设计

数字电路课程设计 一、概述 任务:通过解决一两个实际问题,巩固和加深在课程教学中所学到的知识和实验技能,基本掌握常用电子电路的一般设计方法,提高电子电路的设计和实验能力,为今后从事生产和科研工作打下一定的基础。为毕业设计和今后从事电子技术方面的工作打下基础。 设计环节:根据题目拟定性能指标,电路的预设计,实验,修改设计。 衡量设计的标准:工作稳定可靠,能达到所要求的性能指标,并留有适当的裕量;电路简单、成本低;功耗低;所采用的元器件的品种少、体积小并且货源充足;便于生产、测试和维修。 二、常用的电子电路的一般设计方法 常用的电子电路的一般设计方法是:选择总体方案,设计单元电路,选择元器件,计算参数,审图,实验(包括修改测试性能),画出总体电路图。 1.总体方案的选择 设计电路的第一步就是选择总体方案。所谓总体方案是根据所提出的任务、要求和性能指标,用具有一定功能的若干单元电路组成一个整体,来实现各项功能,满足设计题目提出的要求和技术指标。 由于符合要求的总体方案往往不止一个,应当针对任务、要求和条件,查阅有关资料,以广开思路,提出若干不同的方案,然后仔细分析每个方案的可行性和优缺点,加以比较,从中取优。在选择过程中,常用框图表示各种方案的基本原理。框图一般不必画得太详细,只要说明基本原理就可以了,但有些关键部分一定要画清楚,必要时尚需画出具体电路来加以分析。 2.单元电路的设计 在确定了总体方案、画出详细框图之后,便可进行单元电路设计。 (1)根据设计要求和已选定的总体方案的原理框图,确定对各单元电路的设计要求,必要时应详细拟定主要单元电路的性能指标,应注意各单元电路的相互配合,要尽量少用或不用电平转换之类的接口电路,以简化电路结构、降低成本。

关于高速电路设计的几个热门(困惑)观点

关于高速电路设计的几个热门(困惑)观点这一期和大家聊一聊高速电路设计中常见的几个设计观点,当然,对于这一部分可能会有一些工程师有不一样的观点,毕竟每一个人的理解都也不太一样,这也是就本人做过的或者了解到一些其他比较优秀公司的经验和设计习惯做这次分享。主要是总结高速线布线的一些情况。 1、关于松耦合还是紧耦合。只要了解高速电路的工程师都知道,差分线有紧耦合和松耦合之分,很多工程师在此都会纠结。一般SI工程师都会说这要看情况,我也会这么讲。但是从很多产品经验来看,对于差分走线,尽可能使用紧耦合会比较好。但是也有例外的情况,如果整个链路的布线有比较长一段距离无法达到紧耦合的话,这时就最好使用松耦合。图1显示了一对高速差分走线,采用了松耦合。由于最小间隔距离要求(受到SMA连接器的结构限制),在器件下无法采用紧耦合。如果内层采用紧耦合,信号会从紧耦合瞬变成松耦合,这会引起阻抗不连续。 图1. 松耦合和地参考实例 2、关于使用微带线还是带状线。通常,PCB布线分为微带线和带状线。很多资料都在讨论高速信号到底是使用微带线还是带状线,个人认为,布线在哪一层都是可以的,根据需要,如果布线长度较长,那么建议布线在内层(带状线)比较好(损耗和串扰都非常有优势),当然,内层会使信号换层,增加via。带状线还有将信号与其他噪声源相屏蔽的优势。

3、关于布线为圆弧角。现在设计工程师经常流传说高速信号线在设计时,都要使用圆角布线,其实不一定,我们之前做过很多实验,对于不超过10Gbps的信号设计,45°角布线完全可以满足设计要求(SI/EMC),当然,建议不要使用90°拐角,这会带来阻抗不连续性。当然,要是你还是不相信,那么你就去绕圆弧线吧。 4、关于跨分割。大家在学习高速电路设计的时候,不要让高速信号跨过平面分割层。当然,谁又不想有一个完整的平面,但是,当你遇到HDI板的时候,就会遇到不得不跨分割的情况,那么,请大胆的跨吧。记得让布线尽快的跨过gap区域(如图2),切忌在gap上绕线(如图3);如果可以,请就近加一颗合适的电容(猜一猜为什么要一个电容?)。(记住,这是在逼不得已的情况再跨,切记不要胡乱的来回跨,毕竟跨分割会增加返回通路,导致布线电感增加,阻抗变化,进而影响信号完整性) 图2 跨分割平面

Matlab第五章 Simulink模拟电路仿真

第五章Simulink模拟电路仿真 武汉大学物理科学与技术学院微电子系常胜

§5.1 电路仿真概要 5.1.1 MATLAB仿真V.S. Simulink仿真 利用MATLAB编写M文件和利用Simulink搭建仿真模型均可实现对电路的仿真,在实现电路仿真的过程中和仿真结果输出中,它们分别具有各自的优缺点。 武汉大学物理科学与技术学院微电子系常胜

ex5_1.m clear; V=40;R=5;Ra=25;Rb=100;Rc=125;Rd=40;Re=37.5; R1=(Rb*Rc)/(Ra+Rb+Rc); R2=(Rc*Ra)/(Ra+Rb+Rc); R3=(Ra*Rb)/(Ra+Rb+Rc); Req=R+R1+1/(1/(R2+Re)+1/(R3+Rd)); I=V/Req 武汉大学物理科学与技术学院微电子系常胜

ex5_1 武汉大学物理科学与技术学院微电子系常胜

武汉大学物理科学与技术学院微电子系常胜

注意Simulink仿真中imeasurement模块 /vmeasurement模块和Display模块/Scope模块的联合使用 Series RLC Branch模块中R、C、L的确定方式 R:Resistance设置为真实值Capacitance设置为inf(无穷大)Inductance设置为0 C:Resistance设置为0 Capacitance设置为真实值Inductance设置为0 L:Resistance设置为0Capacitance设置为inf Inductance设置为真实值 武汉大学物理科学与技术学院微电子系常胜

高速电路设计技术

咼速数字电路设计技术探讨 宏碁计算机桌上型计算机研展处工程师■苏家弘 关于高速数字电路的电气特性,设计重点大略可分为三项:正时(Timing )、信号质量(Signal Quality )与电磁干扰(EMI )的控制。在正时方面,由于数字电路大多依据频率信号来做信号间的同步工作,因此频率本身的准确度与各信号间的时间差都需配合才能正确运作。在高速的世界 里,时间失之毫厘差以千里,严格的控制线长,基版材质等都成为重要的工作。在信号质量方面, 高速电路已不能用传统的电路学来解释。随着频率变高,信号线长已逐渐逼近电磁波长,此时诸 如传输线原理(Tra nsmission Line )的分布电路(Distribute circuit )的概念,需加以引进才能解释并改进信号量测时所看到的缺陷。在电磁干扰方面,则需防范电路板的电磁波过强而干扰到 其它的电器用品。本文将依序介绍这些设计上的重点。 正时(Timing) 如图1,来源(source )芯片(A)发岀一个频率长度(T)的信号a给目标(target)芯片B< 对A的内部机制而言,他发岀或收起信号a是在频率上升一段时间之后,这就是有效持续时间valid delay )。在最坏的情形下,a信号只能持续T-(Tmax-Tmin)的时间。而B芯片,必须在这段持续时间内读入a,那就必须在频率B上升之前,a已存在一段设置时间(setup time ),在上升之后,再持续一段保存时间( hold time )。 要考虑的有以下几点: 1. A与B所收到的频率信号CLK_A与CLK_B是否不同步?亦即是否有频率歪斜( clock skew ) 的现象。 2. 信号a从A传至B所用的传导时间(flight time )需要多少? 3. 频率本身的不稳度(clock jitter )有多少?我们所设计的设置时间与保存时间能否容忍这个误差?传输速度的计算就1、2两点,我们都必须计算信号在电路板上的传导速度才行,但这又和许多系数息息相关, 包括导体(通常为铜箔)的厚度与宽度,基板厚度与其材质的电介系数( permittivity )。尤其以 基板的电介系数的影响最大:一般而言,传导速度与基板电介系数的平方根成反比。 以常见的FR-4而言,其电介系数随着频率而改变,其公式如下: £ =4.97-0.257log 但须注意,此处的参数f不是频率的频率,而是信号在傅立叶转换后所占的频宽。 以Pentium n的频率信号为例,其上升或下降缘速率典型值约在2V/ns,对2.5V的频率信号而言, 从10%到90%的信号水平约需1ns的时间,依公式: BW=0.35/T 可知频宽为350MHz。代入公式可知电介系数大约是 4.57。 如果传导的是两片无穷大的导体所组成的完美传输线,那么传输的速度应为亦即 1.38xm/sec, 或者5.43 in ch/ns。

控制系统仿真

《控制系统计算机仿真—课程设计作业》 姓名: 专业: 学号: 1. 构造矩阵 (1)试将.*A B 与B A *的 结果相加,并找出相加后新矩阵中绝对值大于10的元素。 (2)组合成一个43的矩阵,第一列为按列顺序排列的A 矩阵元素,第二列为按列顺序排列的B 矩阵元素,第三列为按列顺序排列的C 矩 阵元素。 (1)matlab : A=[-7 1;8 -3]; B=[4 2;5 7]; C=[5 9;6 2]; D=A.*B+A*B num=find(abs(D)>10); D(num) 结果:D = -51 -5 57 -26 ans = -51 57 -26 (2)matlab :NEW=[A(1,:),A(2,:);B(1,:),B(2,:);C(1,:),C(2,:)]’ 结果:NEW = -7 4 5 1 2 9 8 5 6 714259,,835762A B C -??????===??????-??????

-3 7 2 2. 绘制函数曲线,要求写出程序代码 (1)在区间[0,2]π均匀的取50个点,构成向量X。 (2)在同一窗口绘制曲线y1=sin(2*t-0.3); y2=3cos(t+0.5);要求y1曲线为红色点划线,标记点为圆圈;y2为蓝色虚线,标记点为星号。 程序代码: t=linspace(0,2*pi,50); y1=sin(2*t-0.3); y2=3*cos(t+0.5); plot(t,y1,'r.',t,y2,'b-'); hold on plot(t,y1,'o',t,y2,'*'); hold off 3. 写出生成下图所示波形的MA TLAB 程序。图中三个波形均为余弦波,x范围为[pi/2 ~ 7*pi/2] 。要求它的正半波被置零;且在 24 [,] 33 ππ 和 810 [,] 33 ππ 处被削顶。 程序:x=linspace(pi/2,7*pi/2,100); y1=cos(x); figure(1) plot(x,y1) y1(find(y1>0))=0; figure(2) plot(x,y1) n=find((x>2*pi/3&x<4*pi/3)|(x>8*pi/3&x<10*pi/3)); y1(n)=cos(2*pi/3); figure(3) plot(x,y1) 4对于x=[-2π,2π],y1=sinx、y2=cosx、y3=sin2x、y4=cos2x ①用MATLAB语言分四个区域分别绘制的曲线,并且对图形标题及横纵坐标轴进行标注。 ②另建一个窗口,不分区,用不同颜色、线型绘出四条曲线,并标注图例注解。Matlab:x=linspace(-2*pi,2*pi,1000); y1=sin(x);

030442003高速电路板设计与仿真

《高速电路板设计与仿真》课程教学大纲 课程代码:030442003 课程英文名称:High Speed Printed Circuit Board Design and Emulation 课程类别:专业基础课 课程性质:选修 适用专业:电子科学与技术 课程总学时:40 讲课:40 实验:0 上机:0 大纲编写(修订)时间:2011.7 一、大纲使用说明 (一)课程的地位及教学目标 本课程是电子科学与技术专业的专业任选课, 属于专业技术基础课,是一门重要的实践课程。通过本课程的学习,学生能够利用先进的高端软件设计高速电路板,绘制出具有实际意义的原理图和印刷电路板图,具有对设计中的信号完整性、电磁兼容性、电源完整性等问题的分析能力,熟悉一定的电子工艺和印刷电路板的布局布线知识,为今后从事高端设计工作打下一定的基础。 (二)知识、能力及技能方面的基本要求 在知识方面,要求学生具有初步的半导体工艺、印制电路、芯片封装等方面的知识,还要了解信号完整性、电磁兼容性、电源完整性等方面的基本概念,如此才能设计出高质量的高速PCB。在能力方面,要求学生具备一些计算机方面的操作技能。 (三)实施说明 1.教学内容:包括原理图设计、PCB设计、高速信号仿真三部分,其中PCB设计为重点内容。应突出高速和高质量PCB的讲解,以适应高端设计要求。讲课要理论联系实际,设计具有实际意义的原理图和印刷电路板图,而不只是空讲理论知识。 2.教学方法:采用启发式教学,提高学生分析问题和解决问题的能力。鼓励学生通过实践和自学获取知识,培养学生的自学能力,调动学生自行设计的学习积极性和创新能力。 3.教学手段:本课程属于技术基础课,在教学中可采用电子教案、CAI课件及多媒体教学系统等先进教学手段,以确保在有限的学时内,全面、高质量地完成课程教学任务。 4.大纲实施时应贯彻学院工程训练与工程教育相结合的特点,注重学生的能力培养和专业素质的提高,尤其是培养学生的实际动手设计和操作的能力。 (四)对先修课的要求 本课程的先修课为电路、模拟电子电路、数字电子电路、计算机基础知识。 (五)对习题课、实践环节的要求 每次课后留有一定量的操作练习,要求学生课后在自己的电脑上学习操作。本课程无实验。 (六)课程考核方式 1.考核方式:考查 2.考核目标:考核学生是否掌握了软件的基本操作方法,重点考核学生的原理图绘制和印刷电路板的设计能力,所设计的项目是否具有实际意义。 3.成绩构成:本课程的总成绩由两部分组成:平时成绩(包括平时自行练习、出勤等)占20%,期末验收成绩(以综合作业完成情况给出成绩)占80%。按优、良、中、及格、不及格五级给出最后成绩。 (七)参考书目 《Cadence SPB 15.7工程实例入门》于争著,电子工业出版社, 2010.5.

SI高速电路设计

SI高速电路设计:EMI抑制 4.3 EMI的控制我们知道,造成设备性能降低或失效的电磁干扰必须同时具备三个要素,首先是有一个电磁场所,其次是有干扰源和被干扰源,最后就是具备一条电磁干扰的耦合通路,以便把能量从干扰源传递到受干扰源。因此,为解决设备的电磁兼容性,必须围绕这三点来分析。一般情况下,对于EMI的控制,我们主要采用三种措施:屏蔽、滤波、接地。这三种方法虽然有着独立的作用,但是相互之间是有关联的,良好的接地可以降低设备对屏蔽和滤波的要求,而良好的屏蔽也可以使滤波器的要求低一些。下面,我们来分别介绍屏蔽、滤波和接地。屏蔽能够有效的抑制通过空间传播的电磁干扰。采用屏蔽的目的有两个,一个是限制内部的辐射电磁能量外泄出控制区域,另一个就是防止外来的辐射电磁能量入内部控制区。按照屏蔽的机理,我们可以将屏蔽分为电场屏蔽、磁场屏蔽、和电磁场屏蔽。4.3.1.1 电场屏蔽一般情况下,电场感应可以看成是分布电容间的耦合,图1-4-4是一个电场感应的示意图。图1-4-4 电场感应示意图其中A为干扰源,B为受感应设备,其中Ua和Ub之间的关系为Ub=C1*Ua/(C1+C2)C1为A、B之间的分布电容;C2为受感应设备的对地电容。根据示意图和等式,为了减弱B上面的地磁感应,使用的方法有 EMI 控制技术 现有的系统级 EMI控制技术包括: 1.将电路封闭在一个 FARADAY(法拉第)盒中(注意包含电路的机械封装应 该密封)来实现 EMI屏蔽; 2.在电路板或者系统的 I/O端口采取滤波和衰减技术来实现 EMI 控制; 3.实现电路的电场和磁场的严格屏蔽,或者在电路板上采取适当的设计技术 严格控制 PCB 走线和电路板层(自屏蔽)的电容和电感,从而改善 EMI 性能。 一般来说,越接近 EMI源,实现 EMI控制所需的成本就越小。PCB 的集成电路芯片是EMI 最主要的能量来源,因此如果能够深入了解集成电路芯片的内部特征,可以简化 PCB和系统级设计中的 EMI控制。 EMI 的来源 数字集成电路从逻辑高到逻辑低之间的转换或者从逻辑低到逻辑高之间的转换过程,输出端产生的方波信号频率并不是导致 EMI 的唯一频率成分。该方波中包含频率范围宽广的正弦谐波分量,这些正弦谐波分量构成工程师所关心的 EMI频率成分。最高的 EMI频率也称为 EMI发射带宽,它是信号上升时间而不是信号频率的函数。计算 EMI发射带宽的公式为: F=0.35/Tr,其中:F 是频率,单位是 GHz;Tr 是单位为 ns(纳秒)的信号上

模拟集成电路设计经典教材

1、 CMOS analog circuit design by P.E.ALLEN 评定:理论性90 实用性70 编写 100 精彩内容:运放的设计流程、比较器、 开关电容 这本书在国内非常流行,中文版也 翻译的很好,是很多人的入门教材。 建议大家读影印版,因为ic 领域 的绝大部分文献是以英文写成的。 如果你只能读中文版,你的学习资料 将非常有限。笔者对这本书的评价 并不高,认为该书理论有余,实用性 不足,在内容的安排上也有不妥的地 方,比如没有安排专门的章节讲述反 馈,在小信号的计算方面也没有巧方法。本书最精彩的部分应该就是运放的设计流程了。这是领域里非常重要的问题,像Allen 教授这样将设计流程一步一步表述出来在其他书里是没有的。这正体现了Allen 教授的治学风格:苛求理论的完整性系统性。但是,作为一项工程技术,最关键的是要解决问题,是能够拿出一套实用的经济的保险的方案。所以,读者会发现,看完最后一章关于ADC/DAC 的内容,似乎是面面俱到,几种结构的ADC 都提到了,但是当读者想要根据需求选择并设计一种ADC/DAC 时,却无从下手。书中关于比较器的内容也很精彩,也体现了Allen 教授求全的风格。不过,正好其它教科书里对比较器的系统讲述较少,该书正好弥补了这一缺陷。Allen 教授是开关电容电路和滤波器电路的专家。书中的相关章节很适合作为开关电容电路的入门教材。该书的排版、图表等书籍编写方面的工作也做的很好。像Allen 这样的理论派教授不管在那所大学里,大概都会很快的获得晋升吧。另外,Allen 教授的学生Rincon Moca 教授写的关于LDO 的书非常详尽,值得一读。 2、 CMOS Circuit Design Layout and Simulation CMOS Mixed-Signal Circuit Design by R.J.Baker 评定:理论性80 实用性100 编写80 精彩内容:数据转换器的建模和测量、hspice 网表这本书的风格和Allen 的书刚好相反: 理论的系统性不强,但是极为实用,甚至给出 大量的电路仿真网表和hspice 仿真图线。 这本书的中文版翻译的也很好。最近出了第二 版,翻译人员换了,不知道翻译的水平如何。 不过,第二版好贵啊~~ Baker 教授在工业界 的实战经验丰富,曾经参加过多年的军方项目 的研发,接收器,锁相环,数据转换器,DRAM 等曾设计过。所以,书中的内容几乎了包含 了数字、模拟的所有重要电路,Baker 教授

模拟电子技术课程设计(Multisim仿真)

《电子技术Ⅱ课程设计》 报告 姓名 xxx 学号 院系自动控制与机械工程学院 班级 指导教师 2014 年 6 月18日

目录 1、目的和意义 (3) 2、任务和要求 (3) 3、基础性电路的Multisim仿真 (4) 3.1 半导体器件的Multisim仿真 (4) 3.11仿真 (4) 3.12结果分析 (4) 3.2单管共射放大电路的Multisim仿真 (5) 3.21理论计算 (7) 3.21仿真 (7) 3.23结果分析 (8) 3.3差分放大电路的Multisim仿真 (8) 3.31理论计算 (9) 3.32仿真 (9) 3.33结果分析 (9) 3.4两级反馈放大电路的Multisim仿真 (9) 3.41理论分析 (11) 3.42仿真 (12) 3.5集成运算放大电路的Multisim仿真(积分电路) (12) 3.51理论分析 (13) 3.52仿真 (14) 3.6波形发生电路的Multisim仿真(三角波与方波发生器) (14) 3.61理论分析 (14) 3.62仿真 (14) 4.无源滤波器的设计 (14) 5.总结 (18) 6.参考文献 (19)

一、目的和意义 该课程设计是在完成《电子技术2》的理论教学之后安排的一个实践教学环节.课程设计的目的是让学生掌握电子电路计算机辅助分析与设计的基本知识和基本方法,培养学生的综合知识应用能力和实践能力,为今后从事本专业相关工程技术工作打下基础。这一环节有利于培养学生分析问题,解决问题的能力,提高学生全局考虑问题、应用课程知识的能力,对培养和造就应用型工程技术人才将能起到较大的促进作用。 二、任务和要求 本次课程设计的任务是在教师的指导下,学习Multisim仿真软件的使用方法,分析和设计完成电路的设计和仿真。完成该次课程设计后,学生应该达到以下要求: 1、巩固和加深对《电子技术2》课程知识的理解; 2、会根据课题需要选学参考书籍、查阅手册和文献资料; 3、掌握仿真软件Multisim的使用方法; 4、掌握简单模拟电路的设计、仿真方法; 5、按课程设计任务书的要求撰写课程设计报告,课程设计报告能正确反映设计和仿真结果。