Nand Flash存储结构及控制方法

nandflash的原理及运行时序

nandflash的原理及运行时序NAND Flash(非与非闪存)是一种主要用于存储数据的闪存类型,广泛应用于各种存储设备中,如固态硬盘(SSD)、USB闪存驱动器(U盘)以及移动设备中的存储卡等。

NAND Flash的原理:NAND Flash中的基本存储单元是晶体管,每个晶体管可以存储一个或多个bit的数据,通过对晶体管的电荷状态进行读取和写入来实现数据的存储和读取。

NAND Flash的存储单元结构主要有两种类型:单栅结构和多栅结构。

单栅结构中每个晶体管只有一个控制栅(Control Gate)和一个栅介电层(Oxide Layer),而多栅结构中每个晶体管有一个控制栅和多个叠加的栅介电层。

NAND Flash的存储单元编址是按行和列进行的。

每一行包含一个选择门(Word Line),每一列包含一个位线(Bit Line)。

数据的读取和写入都是通过对选择门和位线的控制来实现的。

NAND Flash的运行时序:1.写入时序:(1)输入地址:将要写入的存储单元的地址输入到NAND Flash中。

(2)擦除块的选择:选择需要写入数据的块进行擦除。

(3)擦除块的擦除:对选择的块进行擦除操作,将存储单元中的数据清除。

(4)写入数据:将要写入的数据输入到NAND Flash中。

(5)写入选择门:通过选择门将输入的数据写入到相应的存储单元中。

2.读取时序:(1)输入地址:将要读取的存储单元的地址输入到NAND Flash中。

(2)读取选择门:通过选择门将存储单元中的数据读出。

(3)读取数据:将读取的数据输出。

需要注意的是,NAND Flash的擦除操作是以块为单位进行的,而写入操作是以页为单位进行的。

擦除块的大小通常为64KB或128KB,一页的大小通常为2KB或4KB。

此外,NAND Flash还包含了一些管理区域,用于存储元数据和管理信息。

总结:NAND Flash是一种基于晶体管的闪存类型,通过对晶体管的电荷状态进行读取和写入来实现数据的存储和读取。

NAND_Flash结构与驱动分析

一、NANDflash的物理组成NANDFlash的数据是以bit的方式保存在memorycell,一般来说,一个cell中只能存储一个bit。

这些cell以8个或者16个为单位,连成bitline,形成所谓的byte(x8)/word(x16),这就是NANDDevice的位宽。

这些Line会再组成Page,(NANDFlash有多种结构,我使用的NANDFlash是K9F1208,下面内容针对三星的K9F1208U0M),每页528Bytes(512byte(MainArea)+16byte(SpareArea)),每32个page形成一个Block(32*528B)。

具体一片flash上有多少个Block视需要所定。

我所使用的三星k9f1208U0M具有4096个block,故总容量为4096*(32*528B)=66MB,但是其中的2MB是用来保存ECC校验码等额外数据的,故实际中可使用的为64MB。

NANDflash以页为单位读写数据,而以块为单位擦除数据。

按照这样的组织方式可以形成所谓的三类地址:ColumnAddress:StartingAddressoftheRegister.翻成中文为列地址,地址的低8位PageAddress:页地址BlockAddress:块地址对于NANDFlash来讲,地址和命令只能在I/O[7:0]上传递,数据宽度是8位。

二、NANDFlash地址的表示512byte需要9bit来表示,对于528byte系列的NAND,这512byte被分成1sthalfPageRegister和2ndhalfPageRegister,各自的访问由地址指针命令来选择,A[7:0]就是所谓的columnaddress(列地址),在进行擦除操作时不需要它,why?因为以块为单位擦除。

32个page需要5bit来表示,占用A[13:9],即该page在块内的相对地址。

A8这一位地址被用来设置512byte的1sthalfpage还是2ndhalfpage,0表示1st,1表示2nd。

NANDFlash原理和使用

NANDFlash原理和使用一、NAND Flash的原理NAND Flash基于浮栅效应晶体管(Floating Gate Field Effect Transistor)的工作原理进行存储数据。

每个存储单元包含一个浮动栅和一个控制栅,通过对控制栅施加电压,可以改变浮动栅中电子的分布状态。

当浮动栅的电荷状态表示0时,电子充分存储在浮动栅中;而当浮动栅的电荷状态表示1时,几乎没有电子存储在浮动栅中。

数据的写入和擦除是NAND Flash的两个重要操作。

写入数据时,首先需要根据所需的数据位序列确定相应的单元位置,然后通过施加一定的电压对浮动栅进行充、放电,以改变电子的位状态。

擦除数据时,需要对整个块进行一次性的擦除操作,将所有存储单元的电子位状态恢复为0。

同时,为了提高存储密度和读写性能,NAND Flash还使用了一些技术,如多层单元(Multi-Level Cell,MLC)和三层单元(Triple-Level Cell,TLC)来实现在每个存储单元中存储多位数据。

二、NAND Flash的使用1. 存储器层面:NAND Flash因其非易失性和快速读写性能被广泛应用于存储器中,取代了传统的硬盘驱动器。

固态硬盘(SSD)是其中的典型应用,它不仅在电脑中使用,也可以用于服务器、云存储等领域。

2. 智能手机和平板电脑:NAND Flash被广泛应用于智能手机和平板电脑中的存储器,用于存储操作系统、应用程序和用户数据。

由于NAND Flash具有快速的读写速度和较小的体积,可实现轻薄设计,因此非常适合移动设备。

3. 数字相机和摄像机:NAND Flash也用作数码相机和摄像机中的存储媒介,用于保存拍摄的照片和视频。

相比于传统的存储卡,NAND Flash 存储器具有更高的读写速度和更大的容量,可以满足高清拍摄的需求。

4. 汽车电子:随着汽车电子的普及,NAND Flash也开始在汽车的娱乐系统、导航系统和车载电子控制单元中得到应用。

nand flash 工作原理

nand flash 工作原理NAND Flash是一种非易失性存储器,它广泛应用于各种电子设备中,如手机、平板电脑和SSD(固态硬盘)等。

NAND Flash的工作原理是基于电子存储的机制。

NAND Flash由一系列的电晶体管和电容组成。

每个电晶体管和电容对应存储一个比特(bit)的信息。

具体而言,NAND Flash使用了一种特殊的电荷存储方法,即通过控制电荷在电晶体管的栅极和基极之间的移动来表示不同的信息。

当存储数据时,NAND Flash首先将接收到的数据按照一定的组织方式进行存储。

常见的组织方式包括页(Page)、块(Block)和平面(Plane)。

一页通常包含多个字节或千字节的数据。

一个块则包含多个页。

而一个平面则包含多个块。

在写入操作时,NAND Flash首先将电容的栅极充电,储存电荷。

之后,利用高电压作用在晶体管的源极和前级极上,将电荷保持在电容内,实现数据的写入。

在读取操作时,NAND Flash通过将电容的栅极与源极之间的电压进行测量,来判断电容中的电荷量。

通过测量电场的强弱,可以确定电容中是否存储了电荷,从而读取相应的信息。

除了读写操作外,擦除也是NAND Flash的一个重要操作。

擦除操作时,NAND Flash会一次性清除整个块的数据,以便重新写入新的数据。

由于擦除操作会造成数据块的磨损,NAND Flash会根据需要和状态进行智能的块管理,以延长其寿命。

总体而言,NAND Flash工作原理基于电子存储的机制。

通过控制电荷在电晶体管的栅极和基极间的移动,NAND Flash实现了数据的存储和读取。

它具有快速读取速度、非易失性和较高的密度等优点,成为了现代电子设备中非常重要的存储介质。

闪存Nand Flash存储结构浅析

闪存Nand Flash存储结构浅析NandFlash存储器由多个Block组成,每一个Block又由多个Page组成,Page的大小一般为2K+64Bytes或512+16Bytes。

Page是读取和编程的基本单位,而擦除的基本单位是Block。

NAND Flash的页,包含主区(Main Area)和备用区(Spare Area)两个域,“主区”中有512*8(或256*16)或2048*8(或1024*16)个位,“备用区”中有16*8(或8*16)或64*8(或32*16)个位,这样每一页总共有528*8(264*16)或2112*8(或1056*16)个位。

备用区是保留区域,用来标记坏块(bad block)和存放ECC的值,因此对于用户来说只有“主区”是可用的。

图1NAND Flash的存储结果上图是MT29F2G08AxB的结构图,它的读取和编程都以Page为基本单位,所以它的Cache Register和Data Register都是一个Page的规格。

NandFlash的特别之处就在于页结构,它分成数据区和备用区两个部分,数据区和备用区按页的形式一一对应,因此读取和编程的数据流也需要按页的结构进行组织和分解。

图1所示的MT29F2G08AxB芯片的数据区为2048字节,备用区为64字节。

在实际应用中,备用区一般用于数据区的检错和纠错。

NAND flash在出厂时可能含有无效的块,在使用过程中也可能会出现其他无效的块。

无效的块即为包含一个或多个坏位的块。

每一片芯片在出厂前都经过测试和擦除,并标识了坏块,禁止对在出厂时作了标记的坏块进行擦除或编程。

因此在应用中和编程时,都需要能够对坏块进行识别和处理。

NandFlash的第一块保证是可用的。

另外,Micron NandFlash具有10个页的OTP区域,这个区域不能被擦除,只能编程一次,而且如果被保护,即使是把1编程为0也是禁止的。

NandFlash结构与读写分析及NandFlash寻址方式

NandFlash结构与读写分析及NandFlash寻址方式NAND Flash是一种常用的非易失性存储器,用于存储大量的数据。

它具有高密度、快速读写、低功耗和可擦写的特点,因此被广泛应用于手机、相机、电脑和其他电子设备中。

本文将介绍NAND Flash的结构与读写分析,并详细讨论NAND Flash的寻址方式。

首先,我们来看一下NAND Flash的结构。

NAND Flash由一系列的存储单元组成,每个存储单元被称为“页”。

每个页都包含了一定数量的数据位,通常为2KB到16KB。

NAND Flash通常以块的形式进行读写操作,一个块包含了一定数量的页,通常为32页到128页。

每个块都有一个唯一的地址,用于寻址和访问。

所有的块集合起来构成了一个NAND Flash 芯片。

接下来,我们将分析NAND Flash的读写过程。

首先是写操作。

当要向NAND Flash写入数据时,控制器将数据分成适当的大小并进行编码,然后将其发送到NAND Flash芯片。

芯片会将数据写入到一个可用的空闲块中的空闲页中,并更新一些关于数据的元数据信息,比如页状态和块状态。

为了提高写入速度,NAND Flash通常使用了一种称为“写入放大”的技术,即将多个写入操作合并在一起,一次性写入多个页。

然后是读操作。

当要从NAND Flash中读取数据时,控制器将发送读命令和所需的地址给芯片。

芯片会根据地址找到对应的页,并将数据读取出来发送给控制器。

为了提高读取速度,NAND Flash通常使用了一种称为“读取放大”的技术,即一次读取多个页的数据,然后通过多路复用器将这些数据发送给控制器。

最后,我们讨论NAND Flash的寻址方式。

NAND Flash的寻址方式可以分为两种:页级寻址和块级寻址。

在页级寻址中,每个页都有一个唯一的地址,通过页地址可以直接访问到特定的页。

这种方式简单直接,但会带来额外的寻址开销。

在块级寻址中,每个块有一个唯一的地址,通过块地址可以访问到整个块的所有页。

NANDFlash的底层结构和解析

NANDFlash的底层结构和解析NAND Flash(Negative-AND Flash)是一种非易失性存储器,常用于各种电子设备,如USB闪存驱动器,固态硬盘(SSD)和智能手机中。

它的底层结构以及工作原理,均与传统的 NOR Flash 存储器相比有所不同。

本文将详细解析 NAND Flash 的底层结构和工作原理。

首先,让我们了解下 NAND Flash 存储器的基本构造。

NAND Flash存储器由许多相互连接的存储单元组成,每个存储单元可以存储一个或多个位信息,并且每个存储单元都有一个地址。

与 NOR Flash 存储器不同的是,NAND Flash 存储器以页面为单位进行读写操作,其中一个页面通常包含数百个字节的数据。

NAND Flash 存储器的底层结构由若干个存储单元组成,每个存储单元都由一对非常接近的、临时连接的源/漏(Source/Drain)形成。

这种结构允许在非常小的面积内存储大量存储单元,从而实现高密度的存储。

每个存储单元内通常包含一个浮动栅(Floating Gate),以及一个控制栅(Control Gate)。

当浮动栅中没有电子时,存储单元被认为是处于“擦除”状态。

当我们给浮动栅充电时(向存储单元中注入电子),则会将存储单元的状态切换为“写入”状态。

要读取存储单元中的数据,我们需要在控制栅上加上一定的电压,并通过源/漏区域中的电流测量来检测存储单元中的电子是否存在。

在 NAND Flash 存储器中,数据的读取和写入操作是通过以下步骤进行的:1. 擦除(Erasure)操作:擦除操作是将存储单元的状态从“写入”状态切换为“擦除”状态的过程。

这通常是通过向特定的存储块施加高电压来实现的,该存储块通常包含数百个页面。

擦除操作是不可逆的,即一旦执行擦除操作,就无法恢复存储单元中的数据。

2. 写入操作:写入操作是将数据从外部设备写入 NAND Flash 存储器的过程。

Nand-Flash详述(绝对经典)

NandFlash详述1. 硬件特性:【Flash的硬件实现机制】Flash全名叫做Flash Memory,属于非易失性存储设备(Non-volatile Memory Device),与此相对应的是易失性存储设备(Volatile Memory Device)。

这类设备,除了Flash,还有其他比较常见的如硬盘,ROM等,与此相对的,易失性就是断电了,数据就丢失了,比如大家常用的内存,不论是以前的SDRAM,DDR SDRAM,还是现在的DDR2,DDR3等,都是断电后,数据就没了。

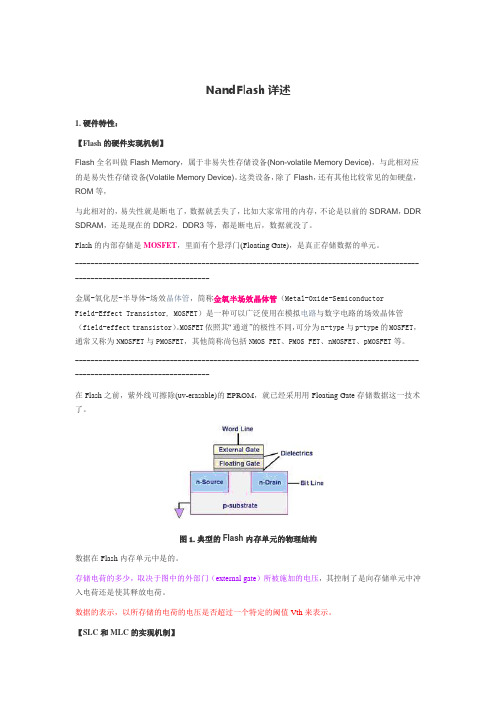

Flash的内部存储是MOSFET,里面有个悬浮门(Floating Gate),是真正存储数据的单元。

-------------------------------------------------------------------------------------------------------------------------金属-氧化层-半导体-场效晶体管,简称金氧半场效晶体管(Metal-Oxide-SemiconductorField-Effect Transistor, MOSFET)是一种可以广泛使用在模拟电路与数字电路的场效晶体管(field-effect transistor)。

MOSFET依照其“通道”的极性不同,可分为n-type与p-type的MOSFET,通常又称为NMOSFET与PMOSFET,其他简称尚包括NMOS FET、PMOS FET、nMOSFET、pMOSFET等。

-------------------------------------------------------------------------------------------------------------------------在Flash之前,紫外线可擦除(uv-erasable)的EPROM,就已经采用用Floating Gate存储数据这一技术了。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Nand Flash存储结构及控制方法(K9F1G08)

2011-02-26 15:05:59| 分类:默认分类 | 标签:

mini2440nandflash k9f1g08 |字号订阅

一、NAND Flash介绍和NAND Flash控制器的使用

NAND Flash在嵌入式系统中的作用,相当于PC上的硬盘

常见的Flash有NOR Flash和NAND Flash,NOR Flash上进行读取的效率非常高,但是擦除和写操作的效率很低,容量一般比较小;NAND Flash进行擦除和写操作的效率更高,并且容量更大。

一般NOR Flash用于存储程序,NAND Flash 用于存储数据。

1)NAND Flash的物理结构

笔者用的开发板上NAND Flash型号是K9F1G08,大小为128M,下图为它的封装和外部引脚

I/O0-I/O7 数据输入/输出

CLE 命令锁存使能

ALE 地址锁存使能

CE 芯片使能

RE 读使能

WE 写使能

WP 写保护

R/B 就绪/忙输出信号

Vcc 电源

Vss 地

N.C 不接

K9F1G08功能结构图如下

K9F1G08内部结构有下面一些功能部件

①X-Buffers Latches & Decoders:用于行地址

②Y-Buffers Latches & Decoders:用于列地址

③Command Register:用于命令字

④Control Logic & High Voltage Generator:控制逻辑及产生Flash所需高压

⑤Nand Flash Array:存储部件

⑥Data Register & S/A:数据寄存器,读、写页时,数据存放此寄存器

⑦Y-Gating

⑧I/O Buffers & Latches

⑨Global Buffers

⑩Output Driver

NAND Flash 存储单元组织结构图如下:

K9F1G08容量为1056Mbit,分为65536行(页)、2112列,每一页大小为2kb,外加64字节的额外空间,这64字节的额外空间的列地址为2048-2111 命令、地址、数据都通过IO0-IO7输入/输出,写入命令、地址或数据时,需要将WE、CE信号同时拉低,数据在WE信号的上升沿被NAND FLash锁存;命令锁存信号CLE、地址锁存信号ALE用来分辨、锁存命令或地址。

K9F1G08有128MB的存储空间,需要27位地址,以字节为单位访问Flash时,需要4个地址序列

2)NAND Flash访问方法

NAND Flash硬件连接如下图:

NAND Flash和S3C2440的连线包括,8个IO引脚,5个使能信号(nWE、ALE、CLE、nCE、nRE)、1个状态引脚(R/B)、1个写保护引脚(nWP)。

地址、数据和命令都是在这些使能信号的配合下,通过8个IO引脚传输。

写地址、数据、命令时,nCE、nWE信号必须为低电平,它们在 nWE信号的上升沿被锁存。

命令锁存使能信号CLE和地址锁存使能信号ALE用来区别IO引脚上传输的是命令还是地址。

命令字及操作方法

操作NAND Flash时,先传输命令,然后传输地址,最后读写数据,这个期间要检查Flash的状态。

K9F1G08容量为128MB,需要一个27位的地址,发出命令后,后面要紧跟着4个地址序列。

下图为K9F1G08的命令字

下图为K9F1G08的地址序列

K9F1G08有2112列,所以必须使用A0-A11共12位来寻址,有65535行,所以必须使用A12-A27共16位来寻址。

3)S3C2440 NAND Flash控制器介绍

NAND Flash的读写操作次序如下:

①设置NFCONF配置NAND Flash

②向NFCMD寄存器写入命令

③向NFADDR寄存器写入地址

④读写数据:通过寄存器NFSTAT检测NAND Flash的状态,在启动某个操作后,应该检测R/nB信号以确定该操作是否完成、是否成功。

下面介绍这些寄存器:

①NFCONF:配置寄存器

用来设置NAND Flash的时序参数,设置数据位宽,设置是否支持其他大小的页等。

②NFCONT:控制寄存器

用来使能NAND Flash控制器、使能控制引脚信号nFCE、初始化ECC,锁定NAND Flash等功能

③NFCMD:命令寄存器

用来发送Flash操作命令

④NFADDR:地址寄存器

用来向Flash发送地址信号

⑤NFDATA:数据寄存器

读写此寄存器启动对NAND Flash的读写数据操作

⑥NFSTAT:状态寄存器

0:busy,1:ready

二、NAND Flash控制器操作实例:读Flash

1)读NAND Flash的步骤

①设置NFCONF

在HCLK=100Mhz的情况下,TACLS=0,TWRPH0=3,TWRPH1=0,则

NFCONF = 0x300

使能NAND Flash控制器、禁止控制引脚信号nFCE,初始化ECC

NFCONT = (1<<4) | (1<<1) | (1<<0)

②操作NAND Flash前,复位

NFCONT &= ~(1<<1) 发出片选信号

NFCMD = 0xff reset命令

然后循环查询NFSTAT位0,直到等于1,处于就绪态

最后禁止片选信号,在实际使用时再使能

NFCONT |= 0x2 禁止NAND Flash

③发出读命令

NFCONT &= ~(1<<1) 发出片选信号

NFCMD = 0 读命令

④发出地址信号

⑤循环查询NFSTAT,直到等于1

⑥连续读NFDATA寄存器,得到一页数据

⑦最后禁止NAND Flash片选信号

NFCONT |= (1<<1)。