硬件工程师EMC手册

EMC设计指导书

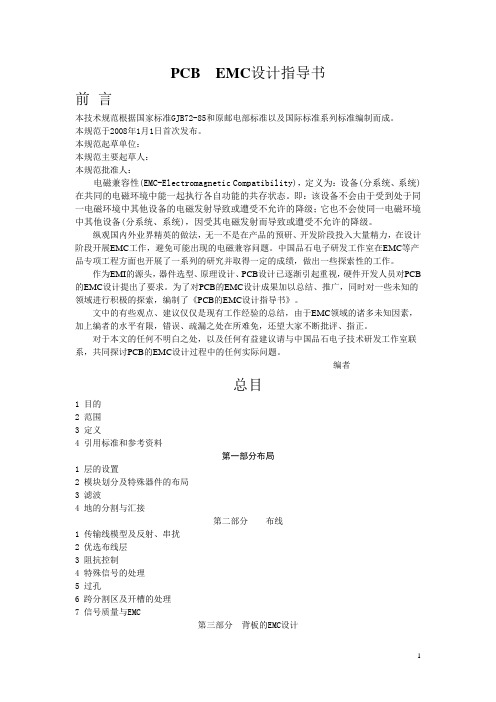

PCB EMC设计指导书前言本技术规范根据国家标准GJB72-85和原邮电部标准以及国际标准系列标准编制而成。

本规范于2008年1月1日首次发布。

本规范起草单位:本规范主要起草人:本规范批准人:电磁兼容性(EMC-Electromagnetic Compatibility),定义为:设备(分系统、系统)在共同的电磁环境中能一起执行各自功能的共存状态。

即:该设备不会由于受到处于同一电磁环境中其他设备的电磁发射导致或遭受不允许的降级;它也不会使同一电磁环境中其他设备(分系统、系统),因受其电磁发射而导致或遭受不允许的降级。

纵观国内外业界精英的做法,无一不是在产品的预研、开发阶段投入大量精力,在设计阶段开展EMC工作,避免可能出现的电磁兼容问题。

中国品石电子研发工作室在EMC等产品专项工程方面也开展了一系列的研究并取得一定的成绩,做出一些探索性的工作。

作为EMI的源头,器件选型、原理设计、PCB设计已逐渐引起重视,硬件开发人员对PCB 的EMC设计提出了要求。

为了对PCB的EMC设计成果加以总结、推广,同时对一些未知的领域进行积极的探索,编制了《PCB的EMC设计指导书》。

文中的有些观点、建议仅仅是现有工作经验的总结,由于EMC领域的诸多未知因素,加上编者的水平有限,错误、疏漏之处在所难免,还望大家不断批评、指正。

对于本文的任何不明白之处,以及任何有益建议请与中国品石电子技术研发工作室联系,共同探讨PCB的EMC设计过程中的任何实际问题。

编者总目1 目的2 范围3 定义4 引用标准和参考资料第一部分布局1 层的设置2 模块划分及特殊器件的布局3 滤波4 地的分割与汇接第二部分布线1 传输线模型及反射、串扰2优选布线层3阻抗控制4 特殊信号的处理5 过孔6跨分割区及开槽的处理7 信号质量与EMC第三部分背板的EMC设计1 背板槽位的排列2 背板的EMC设计第四部分射频PCB的EMC设计1 板材2 隔离与屏蔽3滤波4 接地5布线6 其它设计考虑:第五部分附录1 PCB设计中的安规考虑目录1 目的2 范围3 定义4 引用标准和参考资料第一部分布局1 层的设置1.1 合理的层数1.1.1 Vcc、GND的层数1.1.2 信号层数1.2 单板的性能指标与成本要求1.3 电源层、地层、信号层的相对位置1.3.1 Vcc、GND 平面的阻抗以及电源、地之间的EMC环境问题1.3.2 Vcc、GND 作为参考平面,两者的作用与区别1.3.3 电源层、地层、信号层的相对位置2 模块划分及特殊器件的布局2.1 模块划分2.1 .1 按功能划分2 .1.2 按频率划分2.1.3 按信号类型分2.1.4 综合布局2.2 特殊器件的布局2.2.1 电源部分2.2.2 时钟部分2.2.3 电感线圈2.2.4 总线驱动部分2.2.5 滤波器件3 滤波3.1 概述3.2 滤波器件3.2.1 电阻3.2.2 电感3.2.3 电容3.2.4 铁氧体磁珠3.2.5 共模电感3.3 滤波电路3.3.1 滤波电路的形式3.3.2 滤波电路的布局与布线3.4 电容在PCB的EMC设计中的应用3.4.1 滤波电容的种类3.4.2 电容自谐振问题3.4.3 ESR对并联电容幅频特性的影响3.4.4 ESL对并联电容幅频特性的影响3.4.5 电容器的选择3.4.6 去耦电容与旁路电容的设计建议3.4.7 储能电容的设计4 地的分割与汇接4.1接地的含义4.2 接地的目的4.3 基本的接地方式4.3.1 单点接地4.3.2 多点接地4.3.3 浮地4.3.4 以上各种方式组成的混合接地方式4.4 关于接地方式的一般选取原则:4.4.2 背板接地方式4.4.3 单板接地方式第二部分布线1 传输线模型及反射、串扰1.1 概述:1.2 传输线模型1.3 传输线的种类1.3.1 微带线(microstrip)1.3.2 带状线(Stripline)1.3.3嵌入式微带线1.4 传输线的反射1.5 串扰2优选布线层2.1 表层与内层走线的比较2.1.1 微带线(Microstrip)2.1.3 微带线与带状线的比较2.2 布线层的优先级别3 阻抗控制3.1 特征阻抗的物理意义3.1.1 输入阻抗:3.1.2 特征阻抗3.1.3 偶模阻抗、奇模阻抗、差分阻抗3.2 生产工艺对对阻抗控制的影响3.3 差分阻抗控制3.3.1 当介质厚度为5mil时的差分阻抗随差分线间距的变化趋势3.3.2 当介质厚度为13 mil时的差分阻抗随差分线间距的变化趋势3.3.3 当介质厚度为25 mil时的差分阻抗随差分线间距的变化趋势3.4 屏蔽地线对阻抗的影响3.4.1 地线与信号线之间的间距对信号线阻抗的影响3.4.2 屏蔽地线线宽对阻抗的影响3.5 阻抗控制案例4 特殊信号的处理5 过孔5.1 过孔模型5.1.1 过孔的数学模型5.1.2 对过孔模型的影响因素5.2 过孔对信号传导与辐射发射影响5.2.1 过孔对阻抗控制的影响5.2.2 过孔数量对信号质量的影响6 跨分割区及开槽的处理6.1 开槽的产生6.1.1 对电源/地平面分割造成的开槽6.2 开槽对PCB板EMC性能的影响6.2.1 高速信号与低速信号的面电流分布6.2.2 分地”的概念6.2.3 信号跨越电源平面或地平面上的开槽的问题6.3 对开槽的处理6.3.1 需要严格的阻抗控制的高速信号线,其轨线严禁跨分割走线6.3.2 当PCB板上存在不相容电路时,应该进行分地的处理6.3.3 当跨开槽走线不可避免时,应该进行桥接6.3.4 接插件(对外)不应放置在地层隔逢上6.3.5 高密度接插件的处理6.3.6 跨“静地”分割的处理7 信号质量与EMC7.1 EMC简介7.2 信号质量简介7.3 EMC与信号质量的相同点7.4 EMC与信号质量的不同点7.5 EMC与信号质量关系小结:第三部分背板的EMC设计1 背板槽位的排列1.1 单板信号的互连要求1.2 单板板位结构1.2.1 板位结构影响;1.2.2 板间互连电平、驱动器件的选择2 背板的EMC设计2.1 接插件的信号排布与EMC设计2.1.1 接插件的选型2.1.2 接插件模型与针信号排布2.2 阻抗匹配2.3 电源、地分配2.3.1 电源分割及热插拔对电源的影响2.3.2 地分割与各种地的连接2.3.3屏蔽层第四部分射频PCB的EMC设计1 板材1.1 普通板材1.2 射频专用板材2 隔离与屏蔽2.1 隔离2.2 器件布局2.3 敏感电路和强辐射电路2.4 屏蔽材料和方法2.5 屏蔽腔的尺寸3滤波3.1 电源和控制线的滤波3.2 频率合成器数据线、时钟线、使能线的滤波4 接地4.1 接地分类4.2 大面积接地4.3 分组就近接地4.4 射频器件接地4.4 接地时应注意的问题4.5 接地平面的分布5布线5.1 阻抗控制5.2 转角5.3 微带线布线5.4 微带线耦合器5.5 微带线功分器5.6 微带线基本元件5.7 带状线布线5.8 射频信号走线两边包地铜皮6 其它设计考虑:第五部分附录1 PCB设计中的安规考虑1.1 引言1.2 安全标识1.2.1 对安全标识通用准则1.2.2 电击和能量的危险1.2.4 可更换电池1.3 爬电距离与电气间隙1.4 涂覆印制板1.4.1 PCB板的机械强度1.4.2 印制板材料的阻燃等级1.4.3 热循环试验与热老化试验1.4.4 抗电强度试验1.4.5 耐划痕试验1.5 布线和供电工作室技术规范1 目的本指导书旨在指导PCB的EMC设计,将电路EMC设计要求在PCB中得以实现。

硬件EMC设计规范

目录前言 (2)8 电路设计 (3)8.1电源电路 (3)8.1.1电源输入部分的EMC设计 (4)8.1.2电源输出部分的EMC设计 (5)8.1.3电源转换芯片的EMC设计 (7)8.2接口电路 (7)8.2.1 RS485/CAN接口设计 (8)8.2.2 RS232接口设计 (8)8.2.3 USB接口设计 (9)8.2.4 S_VIDEO接口设计 (9)8.2.5 以太网接口设计 (10)8.3 时钟晶体电路 (11)8.3.1 无源晶体 (11)8.3.2 有源震荡器 (11)8.4 面板电路 (12)8.5 数字总线电路 (12)前言本规范的其他系列规范:无与对应的国际标准或其他文件的一致性程度:无规范代替或作废的全部或部分其他文件:无与其他规范或文件的关系:无本规范由工程技术中心提出。

本规范主要起草和解释部门:本规范主要起草人:本规范批准部门:硬件EMC设计规范8 电路设计电路设计中,如按功能划分种类繁多,不胜枚举。

功能电路的设计好坏,在于设计人员的理论知识和实践经验,在此不做讨论。

由于各类认证中,对电磁兼容要求越来越重视,就此需要重点关注的电路设计大致可分为以下几类:8.1电源电路电源电路设计中,功能性设计主要考虑温升和纹波大小。

温升大小由结构散热和效率决定;输出纹波除了采用输出滤波外,输出滤波电容的选取也很关键:大电容一般采用低ESR电容,小电容采用0.1UF和1000pF共用。

电源电路设计中,电磁兼容设计是关键设计。

主要涉及的电磁兼容设计有:传导发射和浪涌。

传导发射设计一般采用输入滤波器方式。

外部采购的滤波器内部电路一般采用下列电路:Cx1和Cx2为X电容,防止差模干扰。

差模干扰大时,可增加其值进行抑制;Cy1和Cy2为Y电容,防止共模干扰。

共模干扰大时,可增加其值进行抑制。

需要注意的是,如自行设计滤波电路,Y电容不可设计在输入端,也不可双端都加Y电容。

浪涌设计一般采用压敏电阻。

EMC使用手册

04.AND R,A A&R->R

05.CLR R 0->R

06.CLRA 0->A

R /R->R

A R /R->A

09.DAA A寄存器调整为BCD值

49.NOP 空指令

50.OR A,K A OR K->A

51.RET [堆栈顶端]-》PC

52.RETI [堆栈顶端]-》PC使能中断

53.RETL K K->A [堆栈顶端]-》PC

54.SLEP 0->WDT, 振荡器停止振荡

7 6 5 4 3 2 1 0

DH7 PH6 PH5 PH4 PH3 PH2 PH1 PH0

7.IOCE_WTD控制寄存器

7 6 5 4 3 2 1 0

WTDE EIS - ROC - - - -

8.IOCF_中断屏蔽寄存器

7 6 5 4 3 2 1 0

- - - - - EXIE ICIE TCIE

三、指令

01.ADD A,R A+R->A

02.ADD R,A A+R->R

DP7 PD6 PD5 PD4 - PD2 PD1 PD0

5.IOCC_集电极开路控制寄存器

7 6 5 4 3 2 1 0

0D7 0D6 0D5 0D4 0D3 0D2 0D1 0D0

6.IOCD_上拉控制寄存器

6.R5—R6_分别为口5、口6的输入/输出寄存器

7.RF_中断状态寄存器

7 6 5 4 3 2 1 0

- - - - - EXIF ICIF TCIF

EMC日常维护手册

E M C日常维护手册(v20131108)版本说明目录目录版本说明 ......................................................................................................................................... 错误!未指定书签。

1硬件部分 ...................................................................................................................................... 错误!未指定书签。

1.1ClariionCX系列产品硬件介绍........................................................................................... 错误!未指定书签。

1.2如何用Navisphere看存储的状态 ................................................................................... 错误!未指定书签。

1.3客户发现Clariion出现问题,应如何报修? ................................................................. 错误!未指定书签。

1.4EMCClariionCX系列开关机注意事项及详细步骤 ........................................................... 错误!未指定书签。

1.5Clariion主动性售后支持及call-home的介绍 ................................................................. 错误!未指定书签。

2020年(建筑工程管理)硬件工程师手册

(建筑工程管理)硬件工程师手册硬件工程师手册目录第一章概述----------------------------------------------------------- - 5 -第一节硬件开发过程简介 --------------------------------------------- - 5 -§1.1.1 硬件开发的基本过程 ----------------------------------------------- - 5 -§1.1.2 硬件开发的规范化-------------------------------------------------- - 6 -第二节硬件工程师职责与基本技能 ------------------------------------ -6-§1.2.1 硬件工程师职责---------------------------------------------------- - 6 -§1.2.1 硬件工程师基本素质与技术 ---------------------------------------- - 6 -第二章硬件开发规范化管理 ------------------------------------------- - 7 -第一节硬件开发流程 -------------------------------------------------- -7-§3.1.1 硬件开发流程文件介绍 --------------------------------------------- - 7 -§3.2.2 硬件开发流程详解-------------------------------------------------- - 8 -第二节硬件开发文档规范----------------------------------------------11-§2.2.1 硬件开发文档规范文件介绍 --------------------------------------- - 12 -§2.2.2 硬件开发文档编制规范详解 --------------------------------------- - 12 -第三节与硬件开发相关的流程文件介绍--------------------------------14-§3.3.1 项目立项流程:--------------------------------------------------- - 14 -§3.3.2 项目实施管理流程: ---------------------------------------------- - 15 -§3.3.3 软件开发流程:--------------------------------------------------- - 15 -§3.3.4 系统测试工作流程: ---------------------------------------------- - 15 -§3.3.5 中试接口流程 ----------------------------------------------------- - 15 -§3.3.6 内部验收流程 ----------------------------------------------------- - 16 -第三章硬件EMC设计规范-------------------------------------------- - 16 -第一节CAD辅助设计 --------------------------------------------------17-第二节可编程器件的使用----------------------------------------------22-§3.2.1 FPGA产品性能和技术参数 ---------------------------------------- - 22 -§3.2.2 FPGA的开发工具的使用: ---------------------------------------- - 25 -§3.2.3 EPLD产品性能和技术参数----------------------------------------- - 26 -§3.2.4 MAX + PLUS II开发工具------------------------------------------ - 29 -§3.2.5 VHDL语音 -------------------------------------------------------- - 37 -第三节常用的接口及总线设计 -----------------------------------------45-§3.3.1 接口标准: ------------------------------------------------------- - 45 -§3.3.3 并口设计及总线设计: -------------------------------------------- - 46 -§3.3.4 RS-232接口总线------------------------------------------------- - 46 -§3.3.5 RS-422和RS-423标准接口联接方法 ---------------------------- - 47 -§3.3.6 RS-485标准接口与联接方法 ------------------------------------- - 48 -§3.3.7 20mA电流环路串行接口与联接方法------------------------------- - 48 -第四节单板硬件设计指南----------------------------------------------49-§3.4.1 电源滤波: ------------------------------------------------------- - 49 -§3.4.2 带电插拔座: ----------------------------------------------------- - 50 -§3.4.3 上下拉电阻: ----------------------------------------------------- - 50 -§3.4.4 ID的标准电路 ----------------------------------------------------- - 51 -§3.4.5 高速时钟线设计--------------------------------------------------- - 51 -§3.4.6 接口驱动及支持芯片 ---------------------------------------------- - 52 -§3.4.7 复位电路---------------------------------------------------------- - 52 -§3.4.8 Watchdog电路 --------------------------------------------------- - 53 -§3.4.9 单板调试端口设计及常用仪器 ------------------------------------- - 53 -第五节逻辑电平设计与转换 -------------------------------------------54-§3.5.1 TTL、ECL、PECL、CMOS标准 ----------------------------------- - 55 -§3.5.2 TTL、ECL、MOS互连与电平转换 --------------------------------- - 64 -第六节母板设计指南 --------------------------------------------------65-§3.6.1 公司常用母板简介------------------------------------------------- - 66 -§3.6.2 高速传线理论与设计 ---------------------------------------------- - 67 -§3.6.3 总线阻抗匹配、总线驱动与端接----------------------------------- - 71 -§3.6.4 布线策略与电磁干扰 ---------------------------------------------- - 74 -第七节单板软件开发 --------------------------------------------------75-§3.7.1 常用CPU介绍 ------------------------------------------------------ - 75 -§3.7.2 开发环境----------------------------------------------------------- - 75 -§3.7.3 单板软件调试 ------------------------------------------------------ - 76 -§3.7.4 编程规范----------------------------------------------------------- - 76 -第八节硬件整体设计 --------------------------------------------------83-§3.8.1 接地设计---------------------------------------------------------- - 83 -§3.8.2 电源设计---------------------------------------------------------- - 86 -第九节时钟、同步与时钟分配 -----------------------------------------91-§3.9.1 时钟信号的作用--------------------------------------------------- - 91 -§3.9.2 时钟原理、性能指标、测试 --------------------------------------- - 95 -第十节DSP技术 -------------------------------------------------------99-§3.10.2 DSP的特点与应用 --------------------------------------------- - 100 -§3.10.3 TMS320 C54X DSP硬件结构 -------------------------------- - 101 -§3.10.4 TMS320C54X的软件编程 ------------------------------------- - 104 -第四章常用通信协议及标准 ----------------------------------------- - 107 -第一节国际标准化组织 ----------------------------------------------- - 108 -§4.1.1 ISO -------------------------------------------------------- - 108 -§4.1.2 CCITT及ITU-T ---------------------------------------------- - 108 -§4.1.3 IEEE -------------------------------------------------------- - 108 -§4.1.4 ETSI -------------------------------------------------------- - 109 -§4.1.5 ANSI ------------------------------------------------------- - 109 -§4.1.6 TIA/EIA ---------------------------------------------------- - 109 -§4.1.7 Bellcore ---------------------------------------------------- - 109 -第二节硬件开发常用通信标准 ---------------------------------------- - 110 -§4.2.1 ISO开放系统互联模型 -------------------------------------- - 110 -§4.2.2 CCITT G系列建议----------------------------------------- - 110 -§4.2.3 I系列标准 ------------------------------------------------------- - 112 -§4.2.4V系列标准--------------------------------------------------- - 112 -§4.2.5 TIA/EIA 系列接口标准 ------------------------------------- - 115 -§4.2.5 CCITT X系列建议 ----------------------------------------- - 116 -参考文献 ---------------------------------------------------------------- - 119 -第五章物料选型与申购--------------------------------------------- - 119 -第一节物料选型的基本原则--------------------------------------------- - 119 -第二节IC的选型 -------------------------------------------------------- - 121 -第三节阻容器件的选型 ------------------------------------------------- - 124 -第四节光器件的选用---------------------------------------------------- - 129 -第五节物料申购流程---------------------------------------------------- - 131 -第六节接触供应商须知 ------------------------------------------------- - 132 -第七节MRPII及BOM基础和使用---------------------------------------- - 134 -第一章概述第一节硬件开发过程简介§1.1.1 硬件开发的基本过程产品硬件项目的开发,首先是要明确硬件总体需求情况,如CPU处理能力、存储容量及速度,I/O端口的分配、接口要求、电平要求、特殊电路(厚膜等)要求等等。

emc规划手册(阵列适用)

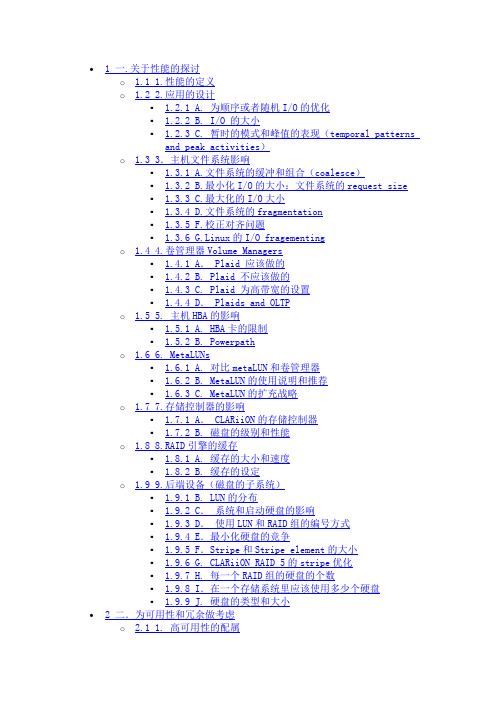

∙ 1 一.关于性能的探讨o 1.1 1.性能的定义o 1.2 2.应用的设计▪ 1.2.1 A. 为顺序或者随机I/O的优化▪ 1.2.2 B. I/O 的大小▪ 1.2.3 C. 暂时的模式和峰值的表现(temporal patterns and peak activities)o 1.3 3.主机文件系统影响▪ 1.3.1 A.文件系统的缓冲和组合(coalesce)▪ 1.3.2 B.最小化I/O的大小:文件系统的request size▪ 1.3.3 C.最大化的I/O大小▪ 1.3.4 D.文件系统的fragmentation▪ 1.3.5 F.校正对齐问题▪ 1.3.6 G.Linux的I/O fragementingo 1.4 4.卷管理器Volume Managers▪ 1.4.1 A. Plaid 应该做的▪ 1.4.2 B. Plaid 不应该做的▪ 1.4.3 C. Plaid 为高带宽的设置▪ 1.4.4 D. Plaids and OLTPo 1.5 5. 主机HBA的影响▪ 1.5.1 A. HBA卡的限制▪ 1.5.2 B. Powerpatho 1.6 6. MetaLUNs▪ 1.6.1 A. 对比metaLUN和卷管理器▪ 1.6.2 B. MetaLUN的使用说明和推荐▪ 1.6.3 C. MetaLUN的扩充战略o 1.7 7.存储控制器的影响▪ 1.7.1 A. CLARiiON的存储控制器▪ 1.7.2 B. 磁盘的级别和性能o 1.8 8.RAID引擎的缓存▪ 1.8.1 A. 缓存的大小和速度▪ 1.8.2 B. 缓存的设定o 1.9 9.后端设备(磁盘的子系统)▪ 1.9.1 B. LUN的分布▪ 1.9.2 C.系统和启动硬盘的影响▪ 1.9.3 D.使用LUN和RAID组的编号方式▪ 1.9.4 E.最小化硬盘的竞争▪ 1.9.5 F.Stripe和Stripe element的大小▪ 1.9.6 G. CLARiiON RAID 5的stripe优化▪ 1.9.7 H. 每一个RAID组的硬盘的个数▪ 1.9.8 I.在一个存储系统里应该使用多少个硬盘▪ 1.9.9 J. 硬盘的类型和大小∙ 2 二.为可用性和冗余做考虑o 2.1 1. 高可用性的配属o 2.2 2. RAID-level的考虑▪ 2.2.1 A. RAID 5▪ 2.2.2 B. RAID 1/0▪ 2.2.3 C. RAID 3▪ 2.2.4 D. 热备份(Hot spares)o 2.3 3. 把RAID组通过总线和DAE绑定▪ 2.3.1 A. 跨DAE来绑定硬盘▪ 2.3.2 B. 跨后端总线绑定硬盘▪ 2.3.3 C. 通过DPE磁盘绑定▪ 2.3.4 D. 热备份的策略o 2.4 4. 数据复制的持续性一.关于性能的探讨性能调优有多重要呢?在一个Raid 5的阵列组中使用5-9块硬盘和使用默认的设置,CLARiiON光纤储系统能发挥极好的性能----这是EMC在性能测试实验室里测试自己的CLARiiON系统得出来的。

EMC5000网络控制卡硬件手册说明书

EMC5000网络控制卡硬件手册Version 1.3版权说明本手册版权归深圳市浩川自动化技术有限公司所有,未经浩川自动化公司书面许可,任何人不得翻印、翻译和抄袭本手册中的任何内容。

涉及EMC控制器软件的详细资料以及每个指令的介绍和例程,请参阅VBASIC软件手册。

本手册中的信息资料仅供参考。

由于改进设计和功能等原因,浩川自动化公司保留对本资料的最终解释权!内容如有更改,恕不另行通知!调试机器要注意安全!请务必在机器中设计有效的安全保护装置,并在软件中加入出错处理程序,否则所造成的损失,浩川自动化公司没有义务或责任对此负责。

目录EMC5000网络控制卡硬件手册 (1)第一章控制卡简介 (1)1.1 连接配置 (1)1.2 安装和编程 (2)1.3 产品特点 (2)第二章硬件描述 (3)2.1 EMC5000系列型号规格 (3)2.1.1 订货信息: (3)2.2 EMC5000接线 (5)2.2.1 电源接口CN16: (6)2.2.2 CAN接口CN17: (6)2.2.3 RS232接口CN12: (7)2.2.4 通用输入信号: (8)2.2.4.1 输入CN9: (8)2.2.4.2 输入CN11: (9)2.2.5 通用输出 CN10: (10)2.2.6 ADDA信号 CN14 (11)2.2.7 轴接口信号: (11)2.2.7.1 轴0-7 CN1-CN8 (11)2.2.7.2 辅助编码器CN15 (13)2.2.7.3 低速差分脉冲口和编码器接线参考: (14)2.2.7.4 高速差分脉冲口和编码器接线参考: (16)第三章扩展模块 (18)3.1 扩展模块CAN总线、输入输出、电源接线参考: (18)第四章常见问题 (18)第五章硬件安装 (19)5.1 EMC5000安装 (20)第一章控制卡简介EMC是浩川自动化技术推出的网络运动控制卡型号简称。

EMC5000系列控制卡支持最多达16轴直线插补、任意圆弧插补、空间圆弧、螺旋插补、电子凸轮、电子齿轮、同步跟随、虚拟轴、机械手指令等;采用优化的网络通讯协议可以实现实时的运动控制。

硬件工程师手册资料精

:因为光接口板和电接口板可以在子架的支路板位混插,所以这两种类型的接口板采用了相同的防护插;在标准性结构产品(155/622,2500)中,所有单板具有相同的扳手定位孔,除主控板外,各单板的红绿指示灯位置相同,等等。

单板的结构性应该考虑那些因素呢?y单板的尺寸。

对于光接口板,要关注拉手条相连接处;y接插件的位置;对于电接口板,要关注同轴接插件的位置;y指示灯的位置;y防护插的位置;y各个安装孔的位置;y散热器和固定件的空间位置;y屏蔽盒的位置y金属结构件是否要接PGND(保护零线)对于任何一块新开发的单板,一定要从多方面调查考虑确定单板的结构特性,特别要同产品经理讨论商定,并参照结构室提供的单板结构图。

(2)对有编码的器件,要给出ECO清单;相信经过培训的许多员工已经知道公司对于硬件开发人员制作单板的MRPII清单出错有如何严厉处罚的条例,产品转中试时,你只能提供错误率为0的清单,在设计PCB时就养成做清单的习惯也许对你很有帮助。

(3)对无编码的器件(即新选用器件),必须填写《新器件选用表》;新器件还没有通过公司品质认证中心认证,也就没有MRPII编码,以后也做不了清单。

(4)器件的封装信息必须描述清楚;尽量为PCB设计人员提供完备的封装信息去建新器件库,建好的库按1:1比例打印,同实物比较,切记管脚顺序不能搞错!提供给CAD室的原理图必须包含器件封装信息,标准器件封装名称以及相应的封装外形图CAD室可提供(5)下列各点针对于PCB的电气性能方面,作为PCB评审依据。

y如果需要,给出PCB板的层间距要求。

15在高速、高频设计时,要考虑走线的特性阻抗,层间距很关键。

y列出板上所有电源的网络名和最大电流;多层板设计中为了减小干扰采用了平板地、电源层的方式,如果不预先设置,布线后电源、地就会按照等同于连接线,严重影响电气性能。

多层板设计中要注意安排信号层与电源层、地层的分布,信号层最好有一层地层或电源层与其贴近。