数字电路考试试卷

数字电路期末考试题及答案

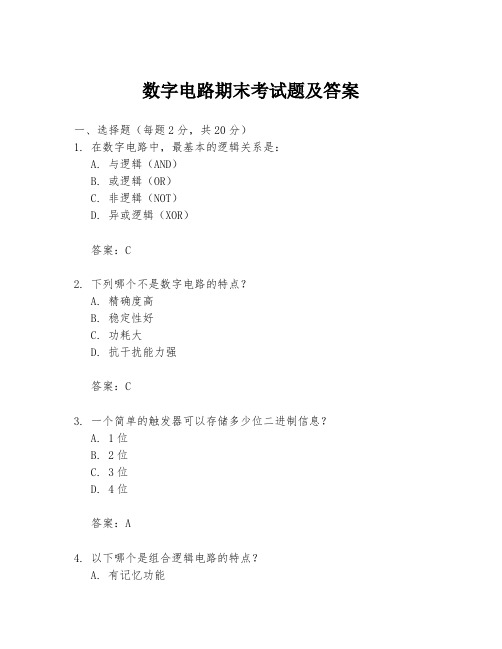

数字电路期末考试题及答案一、选择题(每题2分,共20分)1. 在数字电路中,最基本的逻辑关系是:A. 与逻辑(AND)B. 或逻辑(OR)C. 非逻辑(NOT)D. 异或逻辑(XOR)答案:C2. 下列哪个不是数字电路的特点?A. 精确度高B. 稳定性好C. 功耗大D. 抗干扰能力强答案:C3. 一个简单的触发器可以存储多少位二进制信息?A. 1位B. 2位C. 3位D. 4位答案:A4. 以下哪个是组合逻辑电路的特点?A. 有记忆功能B. 无记忆功能C. 可以进行算术运算D. 可以进行逻辑运算答案:B5. 在数字电路中,同步计数器与异步计数器的主要区别是:A. 同步计数器速度更快B. 同步计数器结构更复杂C. 同步计数器计数更准确D. 异步计数器计数更准确答案:A6. 一个4位二进制计数器最多能计数到:A. 15B. 16C. 8D. 4答案:B7. 以下哪个是数字电路中常用的存储元件?A. 电阻B. 电容C. 电感D. 晶体管答案:D8. 以下哪个不是数字电路中的逻辑门?A. NANDB. NORC. XORD. TRIAC答案:D9. 一个完整的数字电路设计流程包括以下哪些步骤?A. 需求分析B. 电路设计C. 仿真测试D. 所有选项答案:D10. 以下哪个是数字电路中的时序逻辑电路?A. 门电路B. 触发器C. 运算放大器D. 模数转换器答案:B二、简答题(每题5分,共20分)1. 简述数字电路与模拟电路的区别。

答案:数字电路主要处理离散的数字信号,具有逻辑功能,而模拟电路处理连续的模拟信号,主要用于信号放大、滤波等。

2. 解释什么是触发器,并说明其在数字电路中的作用。

答案:触发器是一种具有记忆功能的逻辑电路,能够存储一位二进制信息。

在数字电路中,触发器用于存储数据,实现计数、定时等功能。

3. 什么是组合逻辑电路?请举例说明。

答案:组合逻辑电路是由逻辑门组成的电路,其输出只依赖于当前的输入状态,不具有记忆功能。

(完整版)数字电路试题及参考答案

《数字电路》试卷及答案一、【单项选择题】 ( 本大题共20 小题,每题 2 分,共40 分) 在每题列出的四个选项中只有一个选项是切合题目要求的,请将正确选项前的字母填在答题卷相应题号处。

1、关于钟控 RS触发器,若要求其输出“ 0”状态不变,则输入的RS信号应为( A)。

[A] RS=X0[B] RS=0X[C] RS=X1[D] RS=1X2、以下各电路中,( B)能够产生脉冲准时。

[A]多谐振荡器[B]单稳态触发器[C]施密特触发器[D]石英晶体多谐振荡器3、以下逻辑电路中为时序逻辑电路的是(C)。

[A]变量译码器[B]加法器[C]数码存放器[D]数据选择器4、同步时序电路和异步时序电路比较,其差别在于后者(B)。

[A]没有触发器[B]没有一致的时钟脉冲控制[C]没有稳固状态[D]输出只与内部状态相关5、当用专用输出构造的PAL设计时序逻辑电路时,一定还要具备有(A)。

[A]触发器[B]晶体管[C] MOS 管[D]电容6、能将输出端直接相接达成线与的电路有(C)。

[A] TTL 与门[B]或门[C]三态门[D]三极管非门7、 TTL 与非门的剩余脚悬空等效于(A)。

[A] 1[B] 0[C] Vcc[D] Vee8、以下哪一条不是除去竟争冒险的举措(B)。

[A]接入滤波电路[B]利用触发器[C]加当选通脉冲[D]改正逻辑设计9、主从触发器的触发方式是(D)。

[A] CP=1[B] CP上涨沿[C] CP 降落沿[D]分两次办理10、组合型 PLA 是由( A)组成。

[A]与门阵列和或门阵列[B]一个计数器[C]一个或阵列[D]一个存放器11、以下四个数中,最大的数是(B)。

[A] (AF) 16[B] (001010000010)8421BCD[C] (10100000) 2[D] (198) 1012、触发器有两个稳态,储存8 位二进制信息要(B)个触发器。

[A] 2[B] 8[C] 16[D] 3213、以下门电路属于双极型的是(A)。

《数字电路》期终考试试卷

《数字电路》期终考试试卷题号 一 二 三 四 五 总分 积分人 分数 一、填空题(每空档1分,共28分) 1、半导体数码管的连接方式有 和 。

2、加法器分为和 。

3、三态门有三种输出状态,即: 、 和高阻状态。

4、数字电路在稳态时,二极管、三极管处于 状态。

5、在逻辑电路中,用 和 表示两种对立的逻辑状态。

6、基本逻辑门电路有三种,即 门电路、 门电路和非门电路。

7、按功能译码器可分为 和 两大类。

8、基本RS 触发器中,若S = 0,R = 1时,触发器状态置 。

9、异步计数器是指计数脉冲 加到所有触发器的CP 端,只作用 于 触发器的CP 端。

当计数脉冲到来时,各触发器的翻转时 刻 。

10、同或门和异或门之间的运算是 运算。

11、时序逻辑电路的结构组成通常包含 电路和 电路两部分。

常见时序电路中的存储电路由 构成。

12、JK 触发器Q n+1逻辑函数表达式为: 。

13、计数器除具有计数功能外,还具有 。

14、在优先编码器74LS147中,当输入I 7I 8I 9 = 000时,输出为 。

15、555定时器电路中,当u i1>U R1, u i2>U R2时,基本RS 触发器被置 , 即输出u 0 = ,同时V 导通,电容 。

t p d 。

二、判断题(正确的打“√”,错误的打“×” )(每题3分,共24分)1、具有时钟输入的触发器称为基本RS触发器。

()2、同步RS触发器中,当脉冲到来时,S = 1,R = 0,触发器状态为0态。

()3、优先编码器的工作特点是允许同时输入二个或二个以上的编码信号。

()4、正弦波和方波都是数字信号。

()5、寄存器的功能是统计输入脉冲的个数。

()6、由三个开关并联起来控制一只电灯时,电灯的亮或不亮同三个开关的闭合或断开之间的对应关系属于“或”逻辑关系。

()7、在数字电路中,“1”比“0”大。

()8、在复合门电路中,异或门就是输入端同时为0或同时为1时,输出端为1。

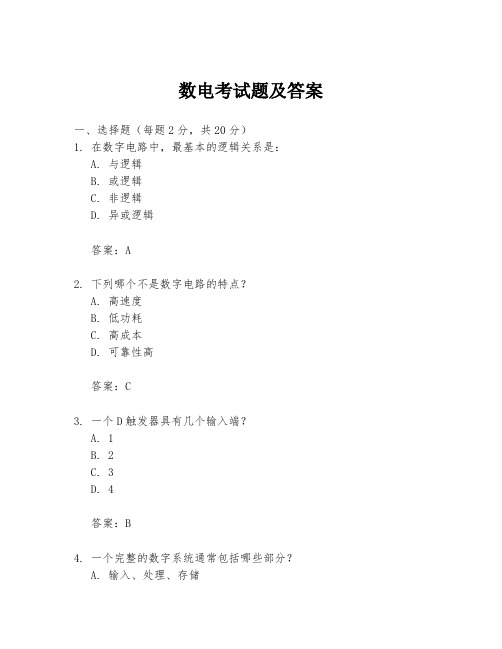

数电考试题及答案

数电考试题及答案一、选择题(每题2分,共20分)1. 在数字电路中,最基本的逻辑关系是:A. 与逻辑B. 或逻辑C. 非逻辑D. 异或逻辑答案:A2. 下列哪个不是数字电路的特点?A. 高速度B. 低功耗C. 高成本D. 可靠性高答案:C3. 一个D触发器具有几个输入端?A. 1B. 2C. 3D. 4答案:B4. 一个完整的数字系统通常包括哪些部分?A. 输入、处理、存储B. 输入、处理、输出C. 输入、存储、输出D. 存储、处理、输出答案:B5. 下列哪个不是组合逻辑电路的特点?A. 输出只依赖于当前输入B. 输出在输入改变后立即改变C. 有记忆功能D. 结构简单答案:C6. 一个4位二进制计数器最多能计数到:A. 15B. 16C. 255D. 1023答案:B7. 在数字电路中,逻辑门的输入端可以连接多少个其他逻辑门的输出端?A. 1个B. 2个C. 3个D. 无限制答案:D8. 一个简单的数字钟电路至少需要几个计数器?A. 1B. 2C. 3D. 4答案:B9. 逻辑门的输出电压通常分为哪两个电平?A. 高电平、低电平B. 正电平、负电平C. 直流电平、交流电平D. 标准电平、非标准电平答案:A10. 下列哪个是数字电路设计中常用的仿真软件?A. MATLABB. AutoCADC. PhotoshopD. SolidWorks答案:A二、填空题(每空2分,共20分)1. 数字电路中最基本的逻辑关系包括______、______和非逻辑。

答案:与逻辑,或逻辑2. 一个3-8译码器有______个输入端,______个输出端。

答案:3,83. 在数字电路中,常用的计数器类型包括二进制计数器、______计数器和______计数器。

答案:十进制,BCD4. 一个8位寄存器可以存储______位二进制数。

答案:85. 触发器的两个稳定状态是______和______。

答案:0,1三、简答题(每题10分,共30分)1. 请简述数字电路与模拟电路的主要区别。

数字电路期末试卷(含答案哦)

《数字电路》试卷一、填空题(每空1分,共20分)1. 有一数码10010011,作为自然二进制数时,它相当于十进制数( ),作为8421BCD 码时,它相当于十进制数( )。

2.三态门电路的输出有高电平、低电平和( )3种状态。

3.TTL与非门多余的输入端应接( )。

4.TTL 集成JK 触发器正常工作时,其d R 和d S 端应接( )电平。

5. 已知某函数⎪⎭⎫ ⎝⎛+⎪⎭⎫ ⎝⎛++=D C AB D C A B F ,该函数的反函数F =( )。

6. 如果对键盘上108个符号进行二进制编码,则至少要( )位二进制数码。

7. 典型的TTL 与非门电路使用的电路为电源电压为( )V ,其输出高电平为( )V ,输出低电平为( )V , CMOS 电路的电源电压为( ) V 。

8.74LS138是3线—8线译码器,译码为输出低电平有效,若输入为A 2A 1A 0=110时,输出 01234567Y Y Y Y Y Y Y Y 应为( )。

9.将一个包含有32768个基本存储单元的存储电路设计16位为一个字节的ROM 。

该ROM 有( )根地址线,有( )根数据读出线。

10. 两片中规模集成电路10进制计数器串联后,最大计数容量为( )位。

11.);Y 3 =( )。

12. 某计数器的输出波形如图1所示,该计数器是( )进制计数器。

13.驱动共阳极七段数码管的译码器的输出电平为( )有效。

二、单项选择题(本大题共15小题,每小题2分,共30分)(在每小题列出的四个备选项中只有一个是最符合题目要求的,请将其代码填写在题后的括号内。

错选、多选或未选均无分。

)1. 函数F(A,B,C)=AB+BC+AC 的最小项表达式为( ) 。

A .F(A,B,C)=∑m (0,2,4) B. (A,B,C)=∑m (3,5,6,7) C .F(A,B,C)=∑m (0,2,3,4) D. F(A,B,C)=∑m (2,4,6,7)2.8线—3线优先编码器的输入为I 0—I 7 ,当优先级别最高的I 7有效时,其输出012Y Y Y ••的值是( )。

数字电路基础-组合逻辑电路和时序逻辑电路考试试卷

数字电路基础-组合逻辑电路和时序逻辑电路考试试卷(答案见尾页)一、选择题1. 数字电路中的基本逻辑门有哪些?A. 或门B. 与门C. 非门D. 异或门E. 同或门2. 下列哪种逻辑电路可以实现时序控制?A. 组合逻辑电路B. 时序逻辑电路C. 计数器D. 编码器3. 在组合逻辑电路中,输出与输入的关系是怎样的?A. 输出总是与输入保持相同的逻辑状态B. 输出仅在输入发生变化时改变C. 输出与输入没有直接关系D. 输出在输入未知时保持不变4. 时序逻辑电路中的时钟信号有何作用?A. 提供时间信息B. 控制电路的工作顺序C. 改变电路的工作频率D. 用于解码5. 下列哪种器件是时序逻辑电路中常见的时序元件?A. 计数器B. 编码器C. 解码器D. 触发器6. 组合逻辑电路和时序逻辑电路的主要区别是什么?A. 组合逻辑电路的输出与输入存在一对一的逻辑关系;时序逻辑电路的输出与输入之间存在时间上的依赖关系。

B. 组合逻辑电路只能处理数字信号;时序逻辑电路可以处理模拟信号。

C. 组合逻辑电路中没有存储单元;时序逻辑电路中存在存储单元(如触发器)。

D. 组合逻辑电路的响应速度较快;时序逻辑电路的响应速度较慢。

7. 在组合逻辑电路中,如果输入信号A和B都为,则输出F将是:A. 0B. 1C. 取决于其他输入信号D. 无法确定8. 在时序逻辑电路中,触发器的时钟信号来自哪里?A. 外部时钟源B. 内部时钟源C. 控制器D. 数据输入端9. 时序逻辑电路的设计通常涉及哪些步骤?A. 确定逻辑功能需求B. 选择合适的触发器C. 设计状态转移方程D. 将设计转换为实际电路E. 对电路进行仿真和验证二、问答题1. 什么是组合逻辑电路?请列举几种常见的组合逻辑电路,并简述其工作原理。

2. 时序逻辑电路与组合逻辑电路有何不同?请举例说明。

3. 组合逻辑电路中的基本逻辑门有哪些?它们各自的功能是什么?4. 什么是触发器?它在时序逻辑电路中的作用是什么?5. 组合逻辑电路设计的基本步骤是什么?请简要说明。

数字电子技术试卷及答案五套

数字电子技术试卷一、选择题:A组:1.如果采用偶校验方式,下列接收端收到的校验码中,( A )是不正确的A、00100B、10100C、11011D、111102、某一逻辑函数真值表确定后,下面描述该函数功能的方法中,具有唯一性的是(B)A、逻辑函数的最简与或式B、逻辑函数的最小项之和C、逻辑函数的最简或与式D、逻辑函数的最大项之和3、在下列逻辑电路中,不是组合逻辑电路的是(D)A、译码器B、编码器C、全加器D、寄存器4、下列触发器中没有约束条件的是(D)A、基本RS触发器B、主从RS触发器C、同步RS触发器D、边沿D触发器5、555定时器不可以组成D。

A.多谐振荡器B.单稳态触发器C.施密特触发器D.J K触发器6、编码器(A)优先编码功能,因而(C)多个输入端同时为1。

A、有B、无C、允许D、不允许7、(D)触发器可以构成移位寄存器。

A、基本RS触发器B、主从RS触发器C、同步RS触发器D、边沿D触发器8、速度最快的A/D转换器是(A)电路A、并行比较型B、串行比较型C、并-串行比较型D、逐次比较型9、某触发器的状态转换图如图所示,该触发器应是( C )A. J-K触发器B. R-S触发器C. D触发器D. T触发器10.(电子专业作)对于VHDL以下几种说法错误的是(A )A VHDL程序中是区分大小写的。

B 一个完整的VHDL程序总是由库说明部分、实体和结构体等三部分构成C VHDL程序中的实体部分是对元件和外部电路之间的接口进行的描述,可以看成是定义元件的引脚D 结构体是描述元件内部的结构和逻辑功能B组:1、微型计算机和数字电子设备中最常采用的数制是--------------------------------( A )A.二进制B.八进制C. 十进制D.十六进制2、十进制数6在8421BCD码中表示为-------------------------------------------------( B )A.0101B.0110C. 0111D. 10003、在图1所示电路中,使__AY 的电路是---------------------------------------------( A )A. ○1B. ○2C. ○3D. ○44、接通电源电压就能输出矩形脉冲的电路是------------------------------------------( D )A. 单稳态触发器B. 施密特触发器C. D触发器D. 多谐振荡器5、多谐振荡器有-------------------------------------------------------------------------------( C )A. 两个稳态B. 一个稳态C. 没有稳态D. 不能确定6、已知输入A、B和输出Y的波形如下图所示,则对应的逻辑门电路是-------( D )A. 与门B. 与非门C. 或非门D. 异或门7、下列电路中属于时序逻辑电路的是------------------------------------------------------( B )A. 编码器B. 计数器C. 译码器D. 数据选择器8、在某些情况下,使组合逻辑电路产生了竞争与冒险,这是由于信号的---------( A )A. 延迟B. 超前C. 突变D. 放大9、下列哪种触发器可以方便地将所加数据存入触发器,适用于数据存储类型的时序电路--------------------------------------------------------------------------------( C )A. RS触发器B. JK触发器C. D触发器D. T触发器10、电路和波形如下图,正确输出的波形是-----------------------------------------------( A )A. ○1B. ○2C. ○3D. ○4C组:1.十进制数25用8421BCD码表示为 B 。

数字电路试题五套(含答案)

《数字电子技术》试卷一一、 填空(每空1分,共25分)1、(10110)2=( )10=( )16(28)10=( )2=( )16 (56)10=( )8421BCD2、最基本的门电路是: 、 、 。

3、有N 个变量组成的最小项有 个。

4、基本RS 触发器的特征方程为_______ ,约束条件是 __.5、若存储器的容量是256×4RAM,该RAM 有 ___存储单元,有 字,字长_____位,地址线 根。

6、用N 位移位寄存器构成的扭环形计数器的模是________.7、若令JK 触发器的J=K=T 则构成的触发器为_______.8、如图所示,Y= 。

9、如图所示逻辑电路的输出Y= 。

10、已知Y=D AC BC B A ++,则Y = ,Y/= 。

11、组合逻辑电路的特点是_________、___________;与组合逻辑电路相比,时序逻辑电路的输出不仅仅取决于此刻的_______;还与电路 有关。

二、 化简(每小题5分,共20分)1、公式法化简(1)Y=ABC ABC BC BC A ++++=+++(2)Y ABC A B C2、用卡诺图法化简下列逻辑函数=+++(1)Y BCD BC ACD ABDY=∑+∑(2)(1,3,4,9,11,12,14,15)(5,6,7,13)m d三、设下列各触发器初始状态为0,试画出在CP作用下触发器的输出波形(10分)四、用74LS161四位二进制计数器实现十进制计数器(15分)五、某汽车驾驶员培训班结业考试,有三名评判员,其中A 为主评判员,B 、C 为副评判员,评判时,按照少数服从多数原则,但若主评判员认为合格也可以通过。

试用74LS138和与非门实现此功能的逻辑电路。

(15分)P Q A Q B Q C Q D C T 74LS161 LD CPQ A 、Q B 、Q C 、Q D :数据输出端; A 、B 、C 、D :数据输入端; P 、T :计数选通端;r C :异步复位端;CP :时钟控制输入端;D L :同步并置数控制端;六、试分析如图电路的逻辑功能,设各触发器的初始状态为0(15分)《数字电子技术》试卷一参考答案一、填空(每空1分,共25分)1、10(22)、16(16);2(11100)、16(1)C ;8421(01010110)BCD 。

数字电路考试题目及答案

数字电路考试题目及答案一、选择题(每题2分,共20分)1. 以下哪个选项是数字电路中的基本逻辑门?A. 与门B. 或门C. 非门D. 所有以上选项答案:D2. 在数字电路中,一个输入为0,另一个输入为1时,或门的输出是什么?A. 0B. 1C. 不确定D. 无输出答案:B3. 一个触发器的初始状态是0,当触发器的时钟信号上升沿到来时,触发器的状态会如何变化?A. 保持不变B. 变为1C. 变为0D. 随机变化答案:B4. 下列哪个不是数字电路中的计数器类型?A. 二进制计数器B. 十进制计数器C. 十六进制计数器D. 模拟计数器答案:D5. 在数字电路中,一个D触发器的Q输出和Q'输出之间的关系是什么?A. 相同B. 相反C. 无关系D. 有时相同有时相反答案:B6. 一个4位二进制计数器能表示的最大数值是多少?A. 15B. 16C. 255D. 256答案:B7. 以下哪个不是数字电路中的编码方式?A. 二进制编码B. 格雷码编码C. 十进制编码D. 模拟编码答案:D8. 在数字电路中,一个异或门的输出为1的条件是什么?A. 输入相同B. 输入不同C. 至少一个输入为0D. 至少一个输入为1答案:B9. 一个3线到8线解码器有多少个输入线?A. 3B. 4C. 5D. 8答案:A10. 在数字电路中,一个锁存器和触发器的主要区别是什么?A. 锁存器可以保持一个稳定的状态,而触发器不能B. 触发器可以保持一个稳定的状态,而锁存器不能C. 两者没有区别D. 两者都是存储设备答案:B二、填空题(每题2分,共20分)1. 在数字电路中,一个3位二进制计数器可以表示的最大数值是__7__。

2. 如果一个触发器的J和K输入都是1,则触发器的状态将会__翻转__。

3. 在数字电路中,一个4位二进制计数器有__16__个不同的状态。

4. 一个D触发器的输出Q在时钟信号的__上升沿__时更新。

5. 一个3线到8线解码器可以产生__8__个输出。

数字电路试卷及答案

数字电路试卷及答案(一)一、填空题(每空1分,共5分)1、CMOS与非门的未用输入端应连接到逻辑( 1 )电平或者输入信号连接端上。

2、DAC的功能是将( 数字)输入成正比地转换成模拟输出。

4 EPROM可存储一个( 9 )输入4输出的真值表。

⨯3、5124、74X163的RCO输出有效条件是:仅当使能信号( ENT )有效,并且计数器的状态是15。

5、已知二进制原码为( 001101) 2 , 问对应的8-bit的补码为( 00001101 )2、二、单项选择题:从以下题目中选择唯一正确的答案。

(每题2分,共10分)1、八路数据分配器的地址输入端有( B )个。

A、 2B、3C、 4D、 52、以下描述一个逻辑函数的方法中( C )只能唯一表示。

A、表达式B、逻辑图C、真值表D、波形图3、实现同一功能的Mealy型同步时序电路比Moore型同步时序电路所需要的( B )。

A、状态数目更多B、状态数目更少C、触发器更多D、触发器更少4、使用移位寄存器产生重复序列信号“1000001”,移位寄存器的级数至少为( D )。

A、 2B、3C、 4D、55、下列各逻辑函数式相等,其中无静态冒险现象的是( D )。

A、F=B’C’+AC+A’BB、F=A’C’+BC+AB’C、F=A’C’+BC+AB’+A’BD、F=B’C’+AC+A’B+BC+AB’+A’C’三、组合电路分析:(共10分)B=BC 最简和之积表达式。

(4分) 解:F+A'BC'+AB=1、求逻辑函数F(2)、已知逻辑函数F=W+XZ+XY,请写出与该函数对应的最小项列表表达式:F=ΣWXYZ( ) (3分)F=ΣWXYZ( 5,6,7,8,9,10,11,12,13,14,15 )数字电路试卷及答案(二)一、【单项选择题】(本大题共20小题,每小题2分,共40分)在每小题列出的四个选项中只有一个选项是符合题目要求的,请将正确选项前的字母填在答题卷相应题号处。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Q2Q 1 Q2 *Q 1*Y

(3 分)

或

状态转换图 (4 分)

A

00

01

10

11

0 1

01/0 10/0 11/0 00/1 11/1 00/0 01/0 10/0

(5)根据状态转换图可知:该电路可以实现可控的加减四进制计数器,当

A=1 时是一个减法计数器,当 A=0 时是一个加法计数器。且该电路能

3

六.电路如下图(a)所示,各电路的 CLK、A、B、C 波形如图(b)所示。要求: (14 分)

(1)写出驱动方程和状态方程; (2)画出 Q1、Q2 的波形。设各触发器的初态均为 0。

(a)

CLK A B C

D1

解:(1 )触发器 FF1

' 驱动方程: D1 (AC)

(1 分)

* ’ 状态方程: Q1 (AC) D1 (1 分)

够实现自启动。 (2 分) 五.请用两片同步 10 进制计数器 74160 和必要的门电路接成 24 进制计数器。

(提示:LD,RD 分别为同步置数、异步置零端,均为低电平有效。控制端 EP=ET=1 时, 计数器工作在计数状态。D3~D0 为数据输入端,C 为进位输出端。 ) (8 分) 评分标准:按照各部分连线情况正确与否酌情给分。

10)触发器三种触发方式分别为: 电平触发 , 脉冲触发(主从触发) , 其中 边沿触发 的触发器抗干扰能力最强。

边沿触发 ,

11)在多谐振荡器,单稳态触发器,施密特触发器中, 施密特触发器 中常用于波形的变 换和整形, 单稳态触发器 常用于定时及延时, 多谐振荡器 图(1-3)中 555 定时器接成的是 施密特触发器 。 常用于产生脉冲波形。

七.已知图(a)电路中的施密特触发器 CMOS 电路 CT1014,图(b)为 CT1014 的电压传输特性曲线。 (10 分) 。 (2)已知 R=20kΩ,C=0.1μF,求 vo 的振荡周期 T。 (5 分) (1)定性画出 vI 和 vo 处的波形(5 分)

解:(1) vI 和 vO 处的波形如图(c)所示。 (根据所画波形酌情给分)图(c) (2) 由图(b)可以看出:VT+=4V,VT-=2V,VOH=5.3V,VOL=0.3V . RC 充电时间: T1 RC ln V C ( ) V C ( 0 ) RC ln V OH V T RC ln 5 .3 2 RC ln 33

(2 分)

4

振荡周期:T=T1+T2=RCln[(33/13)x(37/17)]≈3.42ms

(1 分)

5

三.请设计一组合电路,其输入端为 A,B,C,输出端为 Y,要求其功能为: (14 分) 当 A=1 时,Y=B;当 A=0 时,Y=C。设计内容包括: 1 列出真值表; ②写出 Y 的最简与或表达式; ③用最少的与非门画出逻辑图。 解:① 画出真值表 (5 分) A B C Y 0 0 0 0 0 0 1 1 0 1 0 0 0 1 1 1 1 0 0 0 1 0 1 0 1 1 0 1 1 1 1 1 ② 写出 Y 的最简与或表达式(4 分)

7) RS 触发器的特性方程为: Q*=S+R’Q ,(约束条件:SR=0 ) , T 触发器的特性方程 为: Q*=T’Q+TQ’ 。 。

8) 16 选 1 数据选择器的地址端有 4 位,n 个触发器构成计数器的最大计数长度为 2n 9) 如图(1-1)所示触发器电路中,当 A=1 时,输出状态为____Q=1___, 如图(1-2)所示计数器电路为___6___进制计数器。

V C ( ) V C (T 1) V OH V T 5 .3 4 13

(2 分)

RC 放电时间: T1 RC ln V C ( ) V C ( 0 ) RC ln V OL V T RC ln 0 .3 4 RC ln 37

V C ( ) V C (T 1) V OL V T 0 .3 2 17

D1 Q1 解: (1) 驱动方程: D 2 A Q1 Q 2

Q1 * D1 Q1' (2)状态方程: Q2 * A Q1 Q2

(3 分)

(3 分)

(3)输出方程: )] AQ1Q2 AQ1Q2 Y [( 辑电路

。

,CMOS 与非门: 接高电平或者并联 ((AB)’(BC)’(CA)’)’ 。

。

5) 三态输出门在普通门电路输出状态的基础上增加的状态为__ 高阻态___。 6) TTL 反相器的阈值电压为 VTH= VTH= 5V 。 1.4V 。若 CMOS 反向器的 VDD=10V 则其阈值电压为

一.填空题(1 分/空,共 24 分)

1) 十进制数 (99.375)10=( 1100011. 011 )2 = ( 63.6 )16。 和

√

2) 数字电路按照其结构和工作原理分为两大类: 组合逻辑电路 3) 以下类型门电路多余的输入端应如何处理: TTL 与非门: 接高电平或者悬空或者并联 4)逻辑函数 Y=AB+BC+CA 的与非-与非式为

3) Y ( A, B, C , D) (m3 , m5 , m6 , m7 , m10 ) ,给定约束条件: m0 m1 m2 m4 m8 0 。

CD 00 AB 00 X 01 11 10 X 0 X 01 X 1 0 0 11 1 1 0 0 10 X 1 0 1

根据卡诺图化简可得: Y(A,B,C,D)=A’+B’D’

1

二. 将下列逻辑函数化简为最简与-或形式(方法不限)(每小题 5 分,共 15 分,按步骤酌情给分) 1) Y AC ' ABC ACD 'CD = AC’+ C(AB+AD’+D) = AC’+C(A+D) = AC’+AC+CD = A+CD 2)求 Y= (( A B' )( A'C ))' AC BC 的反函数并化简 Y’ = [(A’B+AC’)’+(A’+C’)](B’+C’) = [(A+B’)(A’+C)+A’+C’](B’+C’) = (AC+A’B’+B’C+A’+C’)(B’+C’) = B’+C’

Y A' B' C A' BC ABC 'ABC A' C AB

③用最少的与非门画出逻辑图 将 Y 的表达式化为与非-与非式(2 分) : 画逻辑图: (3 分)

Y A' C AB ((A' C)'( AB)')'

2

四.试分析图示电路的逻辑功能,写出电路的驱动方程、状态方程和输出方程, 画出电路的状态转换图,检查电路能否自启动。 (15 分)

(2)触发器 FF2

(1 分) 驱动方程: (2 分)

1

J 2 A B (1 分) (1 分) K 2 1

' ( A B )Q2 (2 分)

Q

J2 K2

* ' ' 状态方程: Q2 J 2Q2 K2 Q2

(1 分) (1 分) (1 分) (2 分)

2

RD’

Q

(b)