14针JTAG接口定义引脚名称描述

JTAG各类接口针脚定义及含义

JTAG各类接口针脚定义及含义JTAG(Joint Test Action Group;联合测试工作组)是一种国际标准测试协议(IEEE 1149.1兼容),主要用于芯片内部测试。

现在多数的高级器件都支持JTAG协议,如DSP、FPGA器件等。

标准的JTAG接口是4线:TMS、TCK、TDI、TDO,分别为模式选择、时钟、数据输入和数据输出线。

接口JTAG最初是用来对芯片进行接口编辑JTAG最初是用来对芯片进行测试的,JTAG的基本原理是在器件内部定义一个TAP(Test Access Port;测试访问口)通过专用的JTAG测试工具对内部节点进行测试。

JTAG测试允许多个器件通过JTAG接口串联在一起,形成一个JTAG 链,能实现对各个器件分别测试。

如今,JTAG接口还常用于实现ISP(In-System Programmer,在系统编程),对FLASH等器件进行编程。

JTAG编程方式是在线编程,传统生产流程中先对芯片进行预编程然后再装到板上,简化的流程为先固定器件到电路板上,再用JTAG编程,从而大大加快工程进度。

JTAG接口可对DSP芯片内部的所有部件进行编程。

JTAG引脚定义具有JTAG口的芯片都有如下JTAG引脚定义:TCK——测试时钟输入;TDI——测试数据输入,数据通过TDI输入JTAG口;TDO——测试数据输出,数据通过TDO从JTAG口输出;TMS——测试模式选择,TMS用来设置JTAG口处于某种特定的测试模式。

可选引脚TRST——测试复位,输入引脚,低电平有效。

含有JTAG口的芯片种类较多,如CPU、DSP、CPLD等。

JTAG内部有一个状态机,称为TAP控制器。

TAP控制器的状态机通过TCK和TMS进行状态的改变,实现数据和指令的输入。

JTAG芯片的边界扫描寄存器JTAG标准定义了一个串行的移位寄存器。

寄存器的每一个单元分配给IC芯片的相应引脚,每一个独立的单元称为BSC(Boundary-Scan Cell)边界扫描单元。

JTAG接口定义

JTAG接口定义2009-12-14 17:32什么是jtag接口JTAG(Joint Test Action Group ,联合测试行动小组 ) 是一种国际标准测试协议,主要用于芯片内部测试及对系统进行仿真、调试, JTAG 技术是一种嵌入式调试技术,它在芯片内部封装了专门的测试电路 T AP ( Test Access Port ,测试访问口),通过专用的 JTAG 测试工具对内部节点进行测试。

目前大多数比较复杂的器件都支持 JTAG 协议,如 ARM 、 DSP 、 FPGA 器件等。

标准的 JTAG 接口是 4 线: TMS 、 TCK 、 TDI 、 TDO ,分别为测试模式选择、测试时钟、测试数据输入和测试数据输出。

JTAG 测试允许多个器件通过 JTAG 接口串联在一起,形成一个 JTAG 链,能实现对各个器件分别测试。

JTAG 接口还常用于实现 ISP ( In-System Programmable 在系统编程)功能,如对 FLASH器件进行编程等。

通过 JTAG 接口,可对芯片内部的所有部件进行访问,因而是开发调试嵌入式系统的一种简洁高效的手段。

目前 JTAG 接口的连接有两种标准,即 14 针接口和 20 针接口,其定义分别如下所示。

14 针JTAG 接口定义:14 针 JTAG 接口定义引脚名称描述1 、 13 VCC 接电源2 、 4 、 6 、 8 、 10 、 14 GND 接地3 nTRST 测试系统复位信号5 TDI 测试数据串行输入7 TMS 测试模式选择9 TCK 测试时钟11 TDO 测试数据串行输出12 NC 未连接20 针 JTAG 接口定义引脚名称描述VTref 目标板参考电压,接电源2 VCC 接电源3 nTRST 测试系统复位信号4、6、8、10、12、14、16、18、20 GND 接地5 TDI 测试数据串行输入7 TMS 测试模式选择9 TCK 测试时钟11 RTCK 测试时钟返回信号13 TDO 测试数据串行输出15 nRESET 目标系统复位信号17 、 19 NC 未连接下面以S3C4510B开发板为例说明JTAG接口:在保证电源电路、晶振电路和复位电路正常工作的前提下,可通过JTAG 接口调试S3C4510B,在系统上电前,首先应检测JTAG 接口的 TMS 、 TCK 、 TDI 、TDO 信号是否已与 S3C4510B 的对应引脚相连,其次应检测 S3C4510B 的 nEWA IT 引脚( Pin71 )是否已上拉, ExtMREQ 引脚( Pin108 )是否已下拉,对这两只引脚的处理应注意,作者遇到多起S3C4510B 不能正常工作或无法与JTA G 接口通信,均与没有正确处理这两只引脚有关。

jtag接口是什么

jtag 接口是什么

JTAG(JointTestAcTIonGroup,联合测试行动小组)是一种国际标准测试协议,主要用于芯片内部测试及对系统进行仿真、调试,JTAG 技术是一种

嵌入式调试技术,它在芯片内部封装了专门的测试电路TAP (TestAccessPort,测试访问口),通过专用的JTAG 测试工具对内部节点进行测试。

如今大多数比较复杂的器件都支持JTAG 协议,如ARM、DSP、FPGA 器件等。

标准的JTAG 接口是4 线:TMS、TCK、TDI、TDO,分别为测试模式选择、测试时钟、测试数据输入和测试数据输出。

如今JTAG 接口的连接有两种标准,即14 针接口和20 针接口,其定义分别如下所示。

14 针JTAG 接口

1、13VCC 接电源。

jtag工作原理详解

jtag工作原理详解JTAG(Joint Test Action Group)是一种用于测试和调试集成电路的标准接口。

它是一种通用的、标准化的接口,可以用于连接芯片或电路板上的各种测试和调试设备。

JTAG接口通常由一个标准的20针或14针连接器组成,用于连接测试和调试设备。

本文将详细介绍JTAG的工作原理。

一、JTAG接口的基本原理1.1 JTAG接口的引脚定义:JTAG接口通常由TCK(Test Clock)、TMS(Test Mode Select)、TDI(Test Data Input)、TDO(Test Data Output)四个引脚组成,用于控制和传输测试数据。

1.2 JTAG接口的工作模式:JTAG接口工作时,通过TCK引脚提供时钟信号,通过TMS引脚控制状态机状态转换,通过TDI引脚输入测试数据,通过TDO引脚输出测试结果。

1.3 JTAG接口的链路结构:JTAG接口可以连接多个芯片或电路板,形成一个链路结构,通过JTAG链路可以同时测试和调试多个设备。

二、JTAG接口的工作流程2.1 进入测试模式:在正常工作模式下,JTAG接口处于绕回状态,当需要进行测试时,通过TMS引脚切换到测试模式。

2.2 通过TCK引脚提供时钟信号:一旦进入测试模式,通过TCK引脚提供时钟信号,控制测试数据的传输和状态机的状态转换。

2.3 通过TDI和TDO引脚传输数据:在测试模式下,通过TDI引脚输入测试数据,通过TDO引脚输出测试结果,通过这种方式完成测试和调试过程。

三、JTAG接口的应用领域3.1 芯片生产测试:在芯片生产过程中,可以通过JTAG接口进行芯片的测试和调试,确保芯片的质量和性能。

3.2 电路板调试:在电路板设计和制造过程中,可以通过JTAG接口对电路板进行测试和调试,发现和修复故障。

3.3 嵌入式系统开发:在嵌入式系统开发过程中,可以通过JTAG接口对系统进行测试和调试,确保系统的稳定性和可靠性。

Jtag的各种引脚定义

Jtag的各种引脚定义使用过ARM芯片的人肯定都听过一个仿真器————JLINK,为什么ARM芯片现在能够这么流行?其中恐怕就有一个原因就是很多的ARM芯片都支持使用Jlink进行调试和仿真。

所以你只要有一个Jlink,不管是ARM7、ARM9、ARM11还是最新的ARM Cortex 系统都能下载和调试了。

以前的嵌入式开发者,可能使用什么公司的芯片就得买一个对应芯片的下载和仿真器,这样如果你只使用一种芯片,可能还好,不过恐怕没有那种芯片能够一直引领市场。

Jlink使用的是一种叫做JTAG的协议,JTAG原本是用于芯片内部测试的,现在大多用于芯片的程序下载和调试仿真。

由于现在Jlink用的比较多,所以有些人可能把Jlink就等同于JTAG了,实际上,JTAG是一种协议,只要满足这种协议的就可以叫做JTAG,比如H—JTAG、OpenJTAG、OSJTAG等等。

正版的Jlink是卖的很贵的。

大概是1000到2000RMB吧。

不过,中国的山寨能力是很强的,而且你硬件卖给别人了,你也没办法控制别人说你不许拆开我的东西看里面的电路是怎么样的。

所以Jlink就被破解了,破解之后的Jlink很便宜,网上五六十块钱就能买到一个能用的Jlink。

除了商业版的Jlink和H—JTAG,网上还有一些电子爱好者,他们参照开源软件的模式,设计了开源硬件,比如arduino。

还有人制作了开源版本的JTAG仿真器——OpenJTAG。

而一些芯片的开发商不像那些软件厂商,会给软件做很多的限制,他们对于开源硬件还是比较开明的,所以他们也支持了一些开源硬件。

比如TI公司的MSP430 LaunchPad、ST公司的STM Discovery 等等板子。

还有飞思卡尔公司的USBDM和OSJTAG。

他们把这些硬件的原理图、PCB还有固件都放在了网络上供人自由下载和制作,你也可以根据他的资料进行改进。

这样能使大家对于他们家的芯片有更多的了解,所以,他们也乐于开源一些评估板。

Jtag的各种引脚定义

使用过ARM芯片的人肯定都听过一个仿真器————JLINK,为什么ARM芯片现在能够这么流行?其中恐怕就有一个原因就是很多的ARM芯片都支持使用Jlink进行调试和仿真。

所以你只要有一个Jlink,不管是ARM7、ARM9、ARM11还是最新的ARM Cortex 系统都能下载和调试了。

以前的嵌入式开发者,可能使用什么公司的芯片就得买一个对应芯片的下载和仿真器,这样如果你只使用一种芯片,可能还好,不过恐怕没有那种芯片能够一直引领市场。

Jlink使用的是一种叫做JTAG的协议,JTAG原本是用于芯片内部测试的,现在大多用于芯片的程序下载和调试仿真。

由于现在Jlink用的比较多,所以有些人可能把Jlink就等同于JTAG了,实际上,JTAG是一种协议,只要满足这种协议的就可以叫做JTAG,比如H—JTAG、OpenJTAG、OSJTAG等等。

正版的Jlink是卖的很贵的。

大概是1000到2000RMB吧。

不过,中国的山寨能力是很强的,而且你硬件卖给别人了,你也没办法控制别人说你不许拆开我的东西看里面的电路是怎么样的。

所以Jlink就被破解了,破解之后的Jlink很便宜,网上五六十块钱就能买到一个能用的Jlink。

除了商业版的Jlink和H—JTAG,网上还有一些电子爱好者,他们参照开源软件的模式,设计了开源硬件,比如arduino。

还有人制作了开源版本的JTAG仿真器——OpenJTAG。

而一些芯片的开发商不像那些软件厂商,会给软件做很多的限制,他们对于开源硬件还是比较开明的,所以他们也支持了一些开源硬件。

比如TI公司的MSP430 LaunchPad、ST公司的STM Discovery 等等板子。

还有飞思卡尔公司的USBDM和OSJTAG。

他们把这些硬件的原理图、PCB还有固件都放在了网络上供人自由下载和制作,你也可以根据他的资料进行改进。

这样能使大家对于他们家的芯片有更多的了解,所以,他们也乐于开源一些评估板。

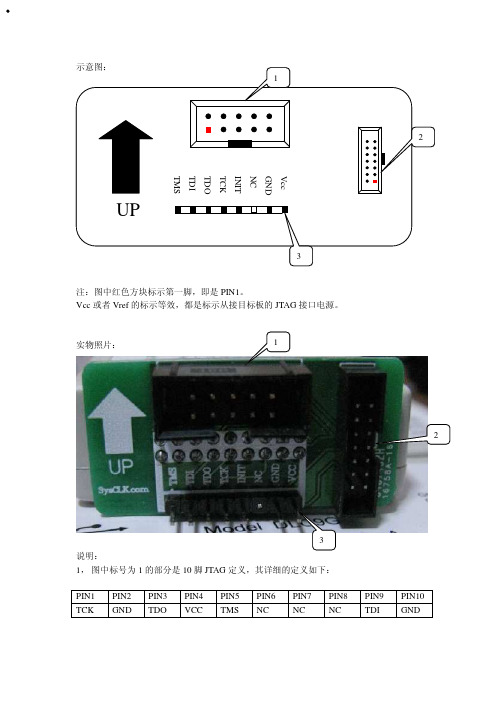

转接板的使用说明

注:图中红色方块标示第一脚,即是PIN1。

Vcc 或者Vref 的标示等效,都是标示从接目标板的JTAG 接口电源。

实物照片:说明:1, 图中标号为1的部分是10脚JTAG 定义,其详细的定义如下: PIN1 PIN2 PIN3 PIN4 PIN5 PIN6 PIN7 PIN8 PIN9 PIN10 TCK GNDTDOVCCTMSNCNCNCTDIGND直观对应图如下:其中两个GND在转接板子以及仿真器内部电路板上都是连接在一起的,可以只用一个GND 。

2, 图中标号为2的部分是14脚2.0MM 针距的JTAG 定义,其引脚定义和下载器本身的14脚2.54MM 定义完全对应,都是完全对应XILINX 的原厂接口定义。

也可以直接直观参照盒子上的标签,请注意PIN1的对应,如下:GND VCC NC NC GND TCKTDOTMSNCTDI3,图中标号为3的部分是分离的单股杜邦线的JTAG定义。

这是一种最为灵活的方式,可以直接接在目标板上的插针或是JTAG座上。

如下图所示:常问问题:1,为什么下载器盒子上的接口是14针的,而转接板背面的插口却是10个孔?答:可以的,18孔左右两面各有2个不连接的孔不插在针上的,只是为了占用那个位置,起到防止接插错位的作用。

插的时候注意先从一面对其,之后悠着用力,就可以接插好。

我们之前采用过14孔的接插件,有顾客反馈容易不对其,这是我们改进后的设计。

接插的时候可能要使点巧劲,但是杜绝了接插错位带来的纠结。

发货前测试过,都是可以接插成功的。

2,在JTAG模式下INIT信号线怎么接?答:INIT只是在SPI模式作为WP(写保护),以及Serial模式下做INIT(初始)用,大多数用户使用的是JTAG模式,在JTAG模式下直接忽略此信号线。

常识附录:1,如何识别常见JTAG插座的针脚序号:我们常说的10PIN实际是10脚,也就是10根插针,同理nPIN就是n脚,n针。

下图是比较常见的10PIN JTAG座实物照片,并且标上针脚号:常见的还有14PIN,20PIN的其样式都是一样的,都会看到有个缺口,为了表示得更明白,我们做个从顶部先下看的抽象示意图,并标上针序:`。

JTAG

6.引脚端口引脚TDI和TCK/SWCLK都是施密特触发器的输入引脚,无上拉电阻。

TMS/SWDIO是施密特触发器的输入/输出引脚,无上拉电阻。

TDO/TRACESWO是输出引脚,输出电压可达到VDDIO,无上拉电阻。

当JTAGSEL引脚高电平有效时,选择JTAG边界扫描。

此引脚集成了一个连接在GNDBU上的15K欧的固定下拉电阻,所以在正常运行时可以悬空。

默认情况下,JTAG调试端口有效。

如果调试器主机想转换到串行线调试端口(SWD),它就必须向TMS/SWDIO和TCK/SWCLK提供一个专用的JTAG序列,以禁止JTAG-DP并允许SW-DP。

当串行线调试(SWD)端口有效时,TDO/TRACESWO引脚可以用于跟踪。

异步TRACE输出引脚(TRACESWO)是和TDO复用的,所以异步跟踪只能和SW-DP一起使用,不能和JTAG-DP一起使用。

所有的JTAG信号都由VDDIO提供电源。

除了JTAGSEL由VDDBU供电外,其它所有的JTAG信号都由VDDIO供电。

6.2引脚高电平有效,用于JTAG边界扫描生产测试或用于进入SAM3U系列的快速编程模式。

TST引脚内部集成了一个连接到地的约15K欧的固定下拉电阻,所以在正常运行时可以悬空。

要进入快速编程模式,TST引脚必须被拉高,该引脚由VDDBU供电,可参考“快速Flash编程接口”章节。

更多关于制造和测试模式的介绍,可参考产品手册的“调试与测试”章节。

6.3引脚是双向引脚。

它可以被片内的复位控制器拉低,从而为外部器件提供复位信号;也可以被外部电路拉低以复位处理器。

它可以复位内核和除了备份区域(RTC,RTT和电源控制器)外的片上外设。

复位脉冲没有持续时间的限制,复位控制器可以保证产生最小长度的脉冲。

NRST引脚内部集成了一个连接到VDDIO上的约100kΩ的固定上拉电阻。

6.4引脚引脚仅能作为输入,当它低电平有效时允许SAM3U系列的异步复位。