逻辑电平转换

逻辑电平转换器

逻辑电平转换器在新一代电子产品设计中,TTL或5V CMOS电平已不再占据逻辑电路统治地位。

随着低电压逻辑的引入,系统内部常常出现输入/输出逻辑不协调的问题,从而提高了系统设计的复杂性。

例如,当1.8V的数字电路与工作在3.3V的模拟电路进行通信时,需要首先解决两种电平转换问题,本文介绍了不同逻辑电平之间的转换方法。

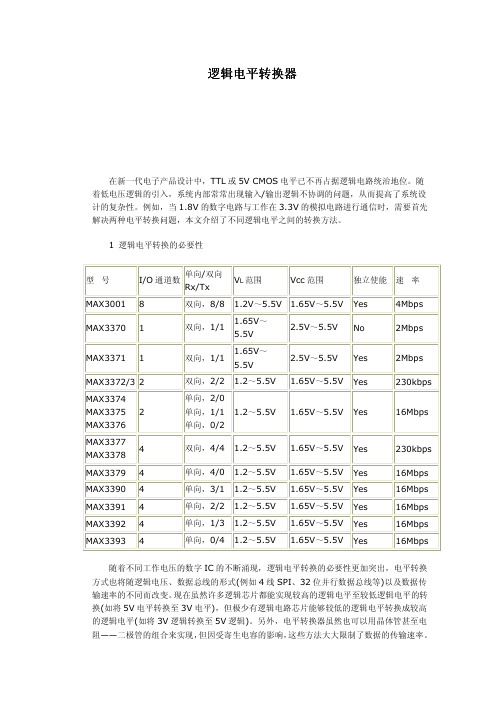

1 逻辑电平转换的必要性型号I/O通道数单向/双向Rx/TxV L范围Vcc范围独立使能速率MAX3001 8 双向,8/8 1.2V~5.5V 1.65V~5.5V Yes 4MbpsMAX3370 1 双向,1/1 1.65V~5.5V2.5V~5.5V No 2MbpsMAX3371 1 双向,1/1 1.65V~5.5V2.5V~5.5V Yes 2MbpsMAX3372/3 2 双向,2/2 1.2~5.5V 1.65V~5.5V Yes 230kbps MAX3374MAX3375 MAX3376 2单向,2/0单向,1/1单向,0/21.2~5.5V 1.65V~5.5V Yes 16MbpsMAX3377MAX33784 双向,4/4 1.2~5.5V 1.65V~5.5V Yes 230kbps MAX3379 4 单向,4/0 1.2~5.5V 1.65V~5.5V Yes 16Mbps MAX3390 4 单向,3/1 1.2~5.5V 1.65V~5.5V Yes 16Mbps MAX3391 4 单向,2/2 1.2~5.5V 1.65V~5.5V Yes 16Mbps MAX3392 4 单向,1/3 1.2~5.5V 1.65V~5.5V Yes 16Mbps MAX3393 4 单向,0/4 1.2~5.5V 1.65V~5.5V Yes 16Mbps 随着不同工作电压的数字IC的不断涌现,逻辑电平转换的必要性更加突出,电平转换方式也将随逻辑电压、数据总线的形式(例如4线SPI、32位并行数据总线等)以及数据传输速率的不同而改变。

485 232 422 ttl互转原理

485 232 422 ttl互转原理标题:[485、232、422 TTL互转原理详解]一、引言在工业自动化和数据通信领域中,RS-232、RS-422与RS-485是三种常见的串行通信接口标准。

其中,TTL(Transistor-Transistor Logic)电平信号广泛应用于集成电路内部的信号传输,而RS-232、RS-422、RS-485则主要用于设备间的长距离通信。

为了实现不同设备间的互联互通,就需要进行TTL与其他标准之间的转换。

本文将详细解析485、232、422与TTL电平互转的原理。

二、TTL电平与RS-232、RS-422、RS-485电平概述1. TTL电平:TTL逻辑电平标准由+5V代表逻辑“1”,0V代表逻辑“0”。

这种电平标准适用于短距离、低速率的集成电路间通信。

2. RS-232电平:RS-232是一种单端通信方式,其逻辑“1”通常为-3V 至-15V,逻辑“0”为+3V至+15V,即采用负逻辑电平,适用于点对点较远距离通信。

3. RS-422电平:RS-422采用差分信号传输,支持全双工通信,能有效抑制共模干扰,每个信号线对包括一条数据发送线和一条数据接收线,逻辑状态由两线间的电压差决定,一般规定当A>B时为逻辑“1”,反之为逻辑“0”。

4. RS-485电平:RS-485与RS-422类似,也是差分信号传输,但允许多个设备连接到同一条总线上,形成多点通信网络,同样以两线间的电压差判断逻辑状态。

三、TTL与其他电平的互转原理1. TTL转RS-232:TTL转RS-232的过程主要通过电平转换芯片实现,如MAX232等。

这类芯片内部集成有电荷泵电路,能够从+5V电源产生±10V左右的电压供给RS-232电平驱动器和接收器使用。

当TTL输出高电平时(+5V),RS-232接收器输出-10V左右;当TTL输出低电平(0V)时,RS-232接收器输出+10V左右,从而完成电平转换。

混合电压系统与板级总线逻辑电平转换

纠 T n c ■ ∞ a ● ∞

1 . 8 V C M O S 器 件 之 间 的 逻 辑 电

No

电 压 系 统 板 级

总 线 传 输 的 重

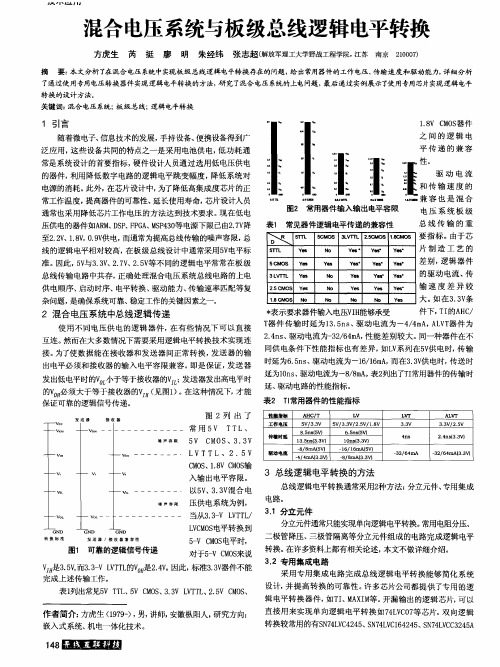

至2 . 2 V .1 . 8 V , 0 . 9 V 供电, 而通常为提高总线传输 的噪声容限, 总 线的逻辑 电平相对 较高, 在板级总线设计 中通常采用5 V 电平标 准。 因此 , 5 v 与3 . 3 V 、 2 . 7 V 、 2 . 5 V 等不 同的逻辑 电平常常在板级 总线传输 电路 中共存 , 正确处理混合电压系统总线 电路 的上电 供 电顺序、 启动时序、 电平转换 、 驱动能力、 传 输速率匹配等复 杂 问题 , 是确保系统可靠 、 稳定工作的关键 因素之一。

4 / 4 mA I 3 3 、 r I

一 8 / 8 mA l 3 . 3 v 1

3 2 / 6 4 r a A

一 3 2 / 6 4 mA( 3 . 3 v l

平 传 递 的 兼 容

性。 驱 动 电 流

和 传 输 速 度 的

1 J ■a啊

兼 容 也 是 混 合

图2 常用器件输 入输出电平容 限

表1 常见器件逻辑电平传递的兼容性

几. L rr L 5CMos 3£ , 7 z YB Ye I Y船 S CMos 3[ , 7 l 2 . 5c I OS 1 . 8C MoS № Y矗 №

— 一

v

l l

— 一 一 一 一一一 一 一. L V T T L、2 . 5 V l C M O S 、 1 . 8 V C M O S 输

逻辑电平介绍TTL,CMOS

逻辑电平介绍TTL,CMOSTTL电平:输出高电平>2.4V,输出低电平<0.4V。

在室温下,一般输出高电平是3.5V,输出低电平是0.2V。

最小输入高电平和低电平:输入高电平>=2.0V,输入低电平<= 0.8V,噪声容限是0.4V。

2,CMOS电平:1逻辑电平电压接近于电源电压,0逻辑电平接近于0V。

而且具有很宽的噪声容限。

3,电平转换电路:因为TTL和COMS的高低电平的值不一样(ttl 5v<==>cmos 3.3v),所以互相连接时需要电平的转换:就是用两个电阻对电平分压,没有什么高深的东西。

哈哈4,OC门,即集电极开路门电路,OD门,即漏极开路门电路,必须外界上拉电阻和电源才能将开关电平作为高低电平用。

否则它一般只作为开关大电压和大电流负载,所以又叫做驱动门电路。

5,TTL和COMS电路比较:1)TTL电路是电流控制器件,而coms电路是电压控制器件。

2)TTL电路的速度快,传输延迟时间短(5-10ns),但是功耗大。

COMS电路的速度慢,传输延迟时间长(25-50ns),但功耗低。

COMS电路本身的功耗与输入信号的脉冲频率有关,频率越高,芯片集越热,这是正常现象。

TTL和CMOS的逻辑电平关系图2-1:TTL和CMOS的逻辑电平图上图为5V TTL逻辑电平、5V CMOS逻辑电平、LVTTL逻辑电平和LVCMOS逻辑电平的示意图。

5V TTL逻辑电平和5V CMOS逻辑电平是很通用的逻辑电平,注意他们的输入输出电平差别较大,在互连时要特别注意。

另外5V CMOS器件的逻辑电平参数与供电电压有一定关系,一般情况下,Voh≥Vcc-0.2V,Vih≥0.7Vcc;Vol≤0. 1V,Vil≤0.3Vcc;噪声容限较TTL电平高。

JEDEC组织在定义3. 3V的逻辑电平标准时,定义了LVTTL和LVCMOS逻辑电平标准。

LVTTL逻辑电平标准的输入输出电平与5V TTL逻辑电平标准的输入输出电平很接近,从而给它们之间的互连带来了方便。

txs0108epwr电平转换器工作原理

txs0108epwr电平转换器工作原理TXS0108EPWR电平转换器是一种常用的逻辑电平转换器,可以实现不同电平之间的转换,使得不兼容的电路之间可以进行正常的通信和连接。

本文将介绍TXS0108EPWR电平转换器的工作原理。

一、引言在现代电子设备中,不同的逻辑电平标准广泛存在。

例如,输入电平高电平标准可能是3.3伏特,而输出电平高电平标准可能是5伏特。

这就导致了不同电路之间的兼容性问题。

TXS0108EPWR电平转换器的出现解决了这个问题。

二、TXS0108EPWR电平转换器概述TXS0108EPWR是一款8位双向逻辑电平转换器,可以将5VTTL/CMOS电平转换为3.3V TTL/CMOS电平,同时还支持3.3VTTL/CMOS电平转换为5V TTL/CMOS电平。

它采用了高速自动方向控制功能,可以提供高达100Mbps的传输速率。

三、工作原理TXS0108EPWR电平转换器的工作原理非常简单。

它包括一个输入端和一个输出端,通过内部的逻辑电路将输入端的电平转换为输出端的电平。

1. 输入端电平转换当输入端电平为高电平时,TXS0108EPWR电平转换器会将其转换为目标电平,例如 3.3V。

转换的过程中,它会检测输入端电平的变化,并根据目标电平的要求,输出相应的电平。

通过适当的电平整形和放大,确保输出端能够正确接收到转换后的电平信号。

2. 输出端电平转换当输出端电平为高电平时,TXS0108EPWR电平转换器会将其转换为原始电平,例如5V。

同样地,它会检测输出端电平的变化,并根据原始电平的要求,输出相应的电平。

在这个过程中,电平整形和放大的作用依然十分重要,以确保输出端能够正常连接到接收端。

综上所述,TXS0108EPWR电平转换器通过内部的逻辑电路将输入端电平转换为输出端电平,实现不同电平标准之间的互通。

其高速自动方向控制功能,保证了信号的快速传输。

四、应用场景由于TXS0108EPWR电平转换器具有高速稳定的特点,广泛应用于各种电子设备中。

逻辑电路中电平转换器

逻辑电路中电平转换器

逻辑电路中的电平转换器,顾名思义,是将不同电平之间的信号进行转换的器件。

在数字电路中尤其重要,因为数字电路中的信号只有两个状态,通常用高电平和低电平表示1和0。

但是,不同的数字电路会采用不同的电平标准,如TTL、CMOS等。

因此,当数字电路之间需要进行数据传输时,有时需要进行电平转换。

电平转换器根据其工作原理的不同,可以分为以下几类:

1. 双向电平转换器

双向电平转换器可以实现两种电平之间的相互转换。

比如,在TTL电平和CMOS电平之间进行转换。

双向电平转换器需要考虑输入和输出端的阻抗匹配,以避免信号反射和干扰。

2. 单向电平转换器

单向电平转换器只能实现单向转换,比如从TTL电平转换到CMOS电平。

单向电平转换器的输入和输出端通常有不同的阻抗。

3. 电平隔离器

电平隔离器可以将两个数字电路之间的信号进行隔离。

它可以使得两个电路之间不发生电气干扰,同时也可以实现电平的转换。

4. CMOS至TTL电平转换器

CMOS至TTL电平转换器将高CMOS电平转换为高TTL电平,同时将低CMOS电平转换为低TTL电平。

这种电平转换器通常用于数字电路之间的数据传输。

5. TTL至CMOS电平转换器

TTL至CMOS电平转换器将高TTL电平转换为高CMOS电平,同时将低TTL电平转换为低CMOS电平。

这种电平转换器通常用于数字电路之间的数据传输。

总之,在数字电路中,电平转换器的作用十分重要。

正确选择并使用电平转换器可以保证数字电路的信号传输质量和稳定性。

txs0108epwr电平转换器工作原理 -回复

txs0108epwr电平转换器工作原理-回复电平转换器(Level Translator)是一种电子装置,广泛应用于电子系统中的电压转换功能。

它可以将一个电路的电平转化为另一个电路所需的电平,实现不同电路之间的互联和数据交换。

txs0108epwr电平转换器是一种常见的电平转换器,它具有高性能和广泛的应用范围。

本文将从工作原理、应用场景和实现方式等方面对txs0108epwr电平转换器进行详细介绍。

一、工作原理txs0108epwr电平转换器主要基于电平转换技术实现不同电平间的转换。

它通过输入端和输出端之间的电路设计,将输入端的电平转换成输出端所需的电平。

其工作原理可简单分为输入端电平检测、电平转换、输出端电平驱动三个步骤。

1. 输入端电平检测txs0108epwr电平转换器通过输入端电路检测输入信号的电平,以确定输入信号的高低电平状态。

一般情况下,输入电路会设计为能够适应不同输入电平范围的自适应电路,以保证输入信号稳定可靠。

2. 电平转换一旦输入信号的电平状态确定,电平转换器会根据输出端所需的电平类型进行相应的转换。

以txs0108epwr为例,它支持1.2V至5.5V的输入电压范围,并能将其转换为1.8V至5.5V的输出电压范围。

转换过程中,电平转换器内部会根据电路设计将输入信号进行电平放大、滤波、反相等处理,以满足输出端的电平要求。

3. 输出端电平驱动最后,txs0108epwr电平转换器会将已经转换后的信号输出至输出端,并根据输出端要求的电平类型进行电平驱动。

输出端通常也会提供自适应电路,以适应不同输出电平的需求。

总之,txs0108epwr电平转换器通过输入端识别输入信号的电平状态,经过电平转换处理后输出符合输出端需求的电平,实现不同电路之间的电平转换和数据交换。

二、应用场景txs0108epwr电平转换器具有广泛的应用范围,特别适用于以下几个场景:1. 逻辑电平转换在数字电路中,不同芯片可能使用不同的逻辑电平标准。

3.3v转10v电平转换电路

3.3V转10V电平转换电路1. 介绍在电子设计中,经常会遇到不同电平之间的转换问题,尤其是在嵌入式系统和传感器应用中。

本文将介绍一种将3.3V电平转换为10V电平的电路设计方案,以供参考和借鉴。

2. 电平转换原理在实际应用中,由于不同器件的工作电压要求不同,所以可能需要将信号从一个电平转换为另一个电平。

在本例中,我们需要将3.3V的逻辑电平转换为10V的模拟电平。

常见的电平转换方式包括电阻分压、运算放大器等。

我们将介绍一种基于运算放大器的电平转换电路设计。

3. 电路设计方案我们可以使用一个非反相运算放大器来实现3.3V到10V的电平转换。

具体电路连接方式如下:3.1 输入端将3.3V的输入信号连接到非反相运算放大器的非反相输入端(+端),将该端接地。

将输入信号通过一个电阻分压网络接入到该端,以便实现对输入信号幅值的放大。

3.2 反馈网络将非反相输入端与反相输入端(-端)通过一个反馈电阻连接起来,以实现放大倍数的控制。

3.3 输出端将非反相运算放大器的输出端连接到一个可调电阻,以便根据需要对输出电平进行微调。

4. 详细设计步骤根据以上电路设计方案,我们可以具体按照以下步骤进行3.3V到10V 电平转换电路的设计和搭建:4.1 选型选择合适的非反相运算放大器器件,确保其工作电压范围和增益等参数符合要求。

4.2 电阻分压设计根据输入信号幅值和放大倍数要求,设计合适的电阻分压网络,以实现对输入信号的放大。

4.3 反馈电阻选择根据所选非反相运算放大器的放大倍数范围,选择合适的反馈电阻,以便实现放大倍数的控制。

4.4 输出端调节电阻选择选择合适的可调电阻,以便对输出电平进行微调。

4.5 电路搭建根据以上设计方案和步骤,进行电路的搭建和连接。

4.6 调试验证对搭建好的电路进行调试和验证,确保输出电平符合预期要求。

5. 注意事项在设计和搭建3.3V到10V电平转换电路时,需要注意以下几个方面的问题:5.1 电压稳定性确保所选非反相运算放大器的电源稳定性和工作温度范围满足要求,以保证输出电平的稳定性。

逻辑电平及电平转换方法

逻辑电平及电平转换方法晶体管+上拉电阻法就是一个双极型三极管或MOSFET,C/D极接一个上拉电阻到正电源,输入电平很灵活,输出电平大致就是正电源电平。

(2)OC/OD器件+上拉电阻法跟1)类似。

适用于器件输出刚好为OC/OD的场合。

(3)74xHCT系列芯片升压(3.3V→5V)凡是输入与5VTTL电平兼容的5VCMOS器件都可以用作3.3V→5V电平转换。

--这是由于3.3VCMOS的电平刚好和5VTTL电平兼容(巧合),而CMOS的输出电平总是接近电源电平的。

廉价的选择如74xHCT(HCT/AHCT/VHCT/AHCT1G/VHCT1G/.)系列(那个字母T就表示TTL兼容)。

(4)超限输入降压法(5V→3.3V,3.3V→1.8V,.)凡是允许输入电平超过电源的逻辑器件,都可以用作降低电平。

这里的"超限"是指超过电源,许多较古老的器件都不允许输入电压超过电源,但越来越多的新器件取消了这个限制(改变了输入级保护电路)。

例如,74AHC/VHC系列芯片,其datasheets明确注明"输入电压范围为0~5.5V",如果采用3.3V供电,就可以实现5V→3.3V电平转换。

(5)专用电平转换芯片最著名的就是164245,不仅可以用作升压/降压,而且允许两边电源不同步。

这是最通用的电平转换方案,但是也是很昂贵的(俺前不久买还是¥45/片,虽是零售,也贵的吓人),因此若非必要,最好用前两个方案。

(6)电阻分压法最简单的降低电平的方法。

5V电平,经1.6k+3.3k电阻分压,就是3.3V。

(7)限流电阻法如果嫌上面的两个电阻太多,有时还可以只串联一个限流电阻。

某些芯片虽然原则上不允许输入电平超过电源,但只要串联一个限流电阻,保证输入保护电流不超过极限(如74HC系列为20mA),仍然是安全的。

(8)无为而无不为法只要掌握了电平兼容的规律。

某些场合,根本就不需要特别的转换。

电平转换原理

电平转换原理

电平转换是指将一个电路或设备的电平信号转换为另一种电平信号的技术。

在电子电路中,不同的电路或设备可能采用不同的电平标准,如TTL(Transistor-Transistor Logic)、CMOS (Complementary Metal-Oxide-Semiconductor)或RS-232(Recommended Standard 232)等。

因此,在不同的电路之间进行连接时,可能需要进行电平转换。

电平转换的原理主要涉及使用适当的信号转换电路,将输入信号的电平调整到输出信号所采用的电平标准范围内。

这通常涉及使用电平转换器、电平适配器或逻辑电平转换器等器件。

其中,电平转换器一般用于将高电平(如5V)转换为低电平(如3.3V)或反之。

它通常由一个电平转换芯片构成,该芯片内部包含电平逻辑门电路,能够将输入信号的电平转换为输出信号。

电平适配器则用于将一种电平标准的信号转换为另一种,例如将TTL信号转换为CMOS信号。

逻辑电平转换器则用于将逻辑电平信号转换为串行或并行数据传输所需的信号电平。

电平转换还可能涉及使用电阻器、电容器、放大器等元件来调整电平。

例如,通过使用电阻分压器可以将输入信号的电压降低到所需的范围内。

通过使用放大器可以增加电压的幅度,从而实现电平转换。

总之,电平转换是一种重要的电子技术,它能够解决不同电路或设备之间的电平不匹配问题,实现信号的正确传输和适应。

通过合理选择和应用适当的电平转换器和元件,能够确保电路和设备间的电平兼容性和互通性,提高系统的性能和可靠性。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

单向高到低电平转换— —输入过压容差

为了将逻辑电平由高向低转换, IC 厂商制造了大 量的声称容许过压输入的器件。具有输入过压保 护的逻辑器件是指能够承受 (不被损坏 )高于其电 源电压的输入电压。这种具有输入保护的器件简 化了从高 VCC 到低 VCC 逻辑的转换任务,同时又 增加了信噪比裕度。 容许过压输入,例如容许 1.8 伏供电的逻辑器件接 受 1.8V 或更高的逻辑电平输入。LVC 逻辑系列的 器件,大部分是输入过压保护的,在需要由高向 低转换的应用中表现良好。但是,相反的情况, 由低到高的转换并不如此简单。由低电压逻辑产 生高电压逻辑的域值电平 (VIH)不切实际。

图 2. 分立 /数字晶体管是实现双向转换的另外一种选择。

当设计的电路由于连接器、高扇出和杂散电容导致 高负载电容时,应注意,对于所有逻辑系列,降低 电源电压也会降低驱动能力。但在 3.3V 的 CMOS 或 TTL (LV,LVT,ALVT,LVC,和 ALVC)与 5V 标准 TTL (H , L , S , HS , LS , ALS) 之间是一 和 个例外。在这些逻辑系列中,3.3V 和 5V 逻辑的触 发点 (VOL,VIL,VIH,VOH)相互匹配。

3.3V

1.8V

R OUTPUT 4.7kΩ CSTRAY APPROX 20pF

INPUT

对逻辑电平转换的需求

越来越多的数字 IC 采用与以往不兼容的电源电 压、更低的 VDD、或者 VCORE 和 VI/O 不同的双电 源供电,这就提出了对于逻辑电平转换的要求。 低电压混合信号 IC 如未能与其配合的数字器件的 发展保持同步,也需要使用逻辑电平转换。 转换方法随着转换电平范围、需要转换的信号线 数 (如,一个 4 线的串行外设接口 (SPITM)与 32 位 数据总线间的转换 )、以及数字信号速率的不同而 不同。许多逻辑 IC 能够将高电平转换成低电平 (如将 5V 转换到 3.3V 逻辑 ),但很少能将低电平转 换成高电平 (如将 3.3V 转换到 5V)。逻辑电平转换 可通过一个分立的晶体管或甚至是一个电阻与二 极管的组合实现。但这些方法固有的寄生电容会 降低数据传输速率。 尽管已有字节宽度的和字宽度的电平转换器件, 但它们对本文讨论的 <20Mbps 的串行总线 (SPI , I2CTM,USB 等)并不理想。封装尺寸大、需要使 用很多引脚和 I/O 方向引脚的转换器对于小型串行 总线和外设接口并不理想。 串行外设接口由单向控制线组成,数据入、数据 出、时钟和片选。数据入和数据出也被称为主入

DVCC RIN CIN DATA OPTIONAL OPTIONAL SHDN* DDRV*

S2 R1 I/O VL S1 R2 I/O VCC

MNSW SPEEDUP GND

GND

* SHDN FOR MAX1840 ONLY; DDRV FOR MAX1841 ONLY.

图 3. 一个带 SPI/QSPI TM/MICROWIRE TM 接口,能够实现高 - 低和 低 -高混合转换的 IC 电平转换器示例。

DVCC

+3.3V IN MAX8867 OUT

MAX8860

SHDN

SET PGND SPI/QSPI/ MICROWIRE SYSTEM VCC RST CLK IO VCC CS SCLK DOUT DIN GND GND

VL

VCC

MAX3370

SYSTEM CONTROLLER

MAX1840 MAX1841

100ns/div

图 9. 此图是一个 MAX3370 高速测试电路满幅驱动输出的例子。

表 1. 多线逻辑电平转换器

Part MAX3000/1 MAX3002/3 MAX3013/23 MAX3014–28 MAX3370/1 MAX3372/3 MAX3374 MAX3375 MAX3376 MAX3377/8 MAX3379 MAX3390 MAX3391 MAX3392 MAX3393 MAX13013/14 No. of I/ O Channels 8 8 8/4 8 1 2 2 4 4 4 4 4 4 1/2 Unidirectional / Bidirectional Rx / Tx Bi, 8 Bi, 8 Bi, 8/4 Uni, full mix Bi, 1 Bi, 2 Uni, 2/0 Uni, 1/1 Uni, 0/2 Bi, 4 Uni, 4/0 Uni, 3/1 Uni, 2/2 Uni, 1/3 Uni, 0/4 Bi, 1/2 VL Range (V) 1.2 to 5.5 1.2 to 5.5 1.2 to (VCC - 0.4) 1.2 to (VCC - 0.4) 1.65 to 5.5 1.2 to 5.5 1.2 to 5.5 1.2 to 5.5 1.2 to 5.5 1.2 to 5.5 1.2 to 5.5 1.2 to 5.5 1.2 to 5.5 1.2 to (VCC - 0.4) VCC Range (V) 1.65 to 5.5 1.65 to 5.5 1.65 to 3.6 1.65 to 3.6 2.5 to 5.5 1.65 to 5.5 1.65 to 5.5 1.65 to 5.5 1.65 to 5.5 1.65 to 5.5 1.65 to 5.5 1.65 to 5.5 1.65 to 5.5 1.65 to 3.6 Separate Enable Yes Yes Yes Yes No/Yes Yes Yes Yes Yes Yes Yes Yes Yes Yes Speeds Up to: (bps) 230k/4M 20M 100M 100M 2M 230k 16M 230k 16M 16M 16M 16M 16M 100M

低 -高和高 -低混合转换

诸如 SPI 总线类的应用要求低 -高和高 -低混合电平 转换。 例如, 在工作于 1.8V 的处理器和工作于 3.3V 的外设之间。尽管可以使用以上方案进行组合, 但也可使用单个芯片,如 MAX1840,MAX1841, 或 MAX3390 满足需求 (见图 3)。

+5.0V

图 4. MAX3370 使用一种传输门方法实现电平转换。

14

引起的偏斜。这使其能够转换由推挽驱动器产生 的数据速率最高达 20MHz 的信号。对源自漏极开 路驱动器的信号转换速率低一些。对于其它的漏

CH1 AMP 5.08V CH2 AMP 1.80V CH2 FREQ 20.14kHz

极开路拓扑,可通过外接上拉电阻提高速率。

15

CH1 AMP 1.68V CH2 AMP 4.86V CH1 FREQ 400.6kHz

CH1 AMP 1.76V CH2 AMP 4.80V CH2 FREQ 400.5kHz

400ns/div

400ns/div

图 7. MAX3370 以 400kHz 速率将 1.8V 转换成 5V 的输出波形图, 容性负载效应被大幅度降低了。

图 8. MAX3370 使用一个 4.7kΩ 上拉电阻以 400kHz 速率输出的波形 图,容性负载效应被大幅度降低了。

RAIL-TO-RAIL DRIVING (RATE = 2Mbps, CLOAD = 10pF, VCC = 3.3V, VL = 1.8V)

I/O VL 0 1V/div I/O VCC 0

2C、1-Wire 总线,需要双向的逻辑 转换。基于集电极或漏极开路单晶体管的简单拓 扑,由于固有的单向性,不能工作于双向总线。

R2

双向收发器方式

GND

对于更大型的字节或字宽度总线而言,由于已有 WR 和 RD 信号,在不同逻辑电平之间传递数据的 方法之一是使用如 74CBTB3384 类的总线开关器 件。这类器件专门针对在 3.3V 和 5V 之间的电压 下工作进行了优化。对小型的 1 线或 2 线的总线, 这种方法有两个问题。首先,需使用独立的使能 引脚控制数据传输方向,这会占用宝贵的端口引 脚资源。其次,需要使用大型 IC,会占用宝贵的 电路板空间。 所有的方案都有其优缺点,但设计者需要一款通 用器件,能工作于所有电平,允许低到高和高到 低的混合转换,还包括进行单向和 / 或双向转换。 下一代双向电平转换器 (MAX3370–MAX3393 IC 系列的 MAX3370) 既能满足这些要求,还能克服 使用其它方案带来的问题。 MAX3370 使用一种传输门方法实现电平转换 (见 图 4) ,依赖外部输出驱动器吸收电流,无论是工 作在低电压还是高电压逻辑范围。这使该器件既 能与漏极开路也能与推挽式输出级一起工作。而 且,传输门相对较低的导通电阻 (小于 135Ω)对转 换速率的影响远小于图 1 中串接的电阻。

逻辑电平转换

自从 TTL 和 5V 的 COMS 成为逻辑电路的主导标准 以来,电子设计已发生了相当大的改变。现代电 子系统日益增加的复杂性导致了低电压逻辑的产 生,但同时又引起在一个系统内部输入输出逻辑 电平不兼容的问题。这并不罕见,例如,当工作 于 1.8V 的数字电路必须和工作于 3.3V 的模拟电路 通信时就会有这个问题。本文分析了逻辑电平的 基本原理,并主要研究了如何在串行数据系统中 不同的逻辑电平范围之间进行转换。

解决速率问题

对其它大多数漏极开路方案,RC 时间常数都会限 制有效数据速率 (见图 5 和 6 )。MAX3370 IC 系列 包括一个专利的加速机构,主动拉升上升沿,从 而最大程度降低了容性负载的影响,如图 7 ,8 和 9 所示。当输入超过预定义的门限时,器件主动 拉升上升沿,从而最大程度降低由外部寄生元件

CH1 AMP 1.66V CH2 AMP 4.56V CH2 FREQ 400.8kHz

CH1 AMP 1.70V CH2 AMP 4.80V CH2 FREQ 100.2kHz

400ns/div

2.00µs/div

(a)

(b)