VHDL双向十进制加减法计数器(代码和截图)

VerilogHDL十进制计数器实验Quartus非常详细的步骤

实验二十进制计数器实验该实验将使用Verilog 硬件描述语言在DE2-70 开发平台上设计一个基本时序逻辑电路——1 位十进制计数器。

通过这个实验,读者可以了解使用Quartus 工具设计硬件的基本流程以及使用Quartus II 内置的工具进行仿真的基本方法和使用SignalTap II 实际观察电路运行输出情况。

SignalTap II 是Quartus 工具的一个组件,是一个片上的逻辑分析仪,可以通过JTAG 电缆将电路运行的实际输出传回Quartus 进行观察,从而省去了外界逻辑分析仪时的很多麻烦。

实验步骤3.1建立工程并完成硬件描述设计1. 打开Quartus II 工作环境,如图3-1 所示。

图3-1 Quartus II工作环境界面2. 点击菜单项File->New Project Wizard 帮助新建工程。

参看图3-2。

图3-2 选择New Project Wizard打开Wizard 之后,界面如图3-3 所示。

点击Next,如图3-3。

第23 页共208 页图3-3 New Project Wizard界面3. 输入工程工作路径、工程文件名以及顶层实体名。

这次实验会帮助读者理解顶层实体名和工程名的关系,记住目前指定的工程名与顶层实体名都是Counter10,输入结束后,如图3-4 所示。

点击Next。

图3-4输入设计工程信息4. 添加设计文件。

界面如图3-5 所示。

如果用户之前已经有设计文件(比如.v 文件)。

第24 页共208 页那么再次添加相应文件,如果没有完成的设计文件,点击Next 之后添加并且编辑设计文件。

图3-5添加设计文件5. 选择设计所用器件。

由于本次实验使用Altera 公司提供的DE2-70 开发板,用户必须选择与DE2-70 开发板相对应的FPGA 器件型号。

在Family 菜单中选择Cyclone II,Package 选FBGA,Pin Count 选896,Speed grade 选6,确认Available devices 中选中EP2C70F896C6,如图3-6。

二位二进制加法器vhdl代码

二位二进制加法器vhdl代码

好的,为你找到一段二位二进制加法器的VHDL代码,希望对你有所帮助:

```vhdl

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity adder is

port (

A, B, Cin : in STD_LOGIC;

S, Cout : out STD_LOGIC

);

end adder;

architecture behavioral of adder is

begin

S <= ((A xor B) xor Cin);

Cout <= ((A xor B) AND Cin) OR (A AND B);

end behavioral;

```

这段代码是一个简单的二位二进制加法器的VHDL实现。

它使用了`IEEE.STD_LOGIC_1164`库中的`STD_LOGIC`数据类型来表示输入和输出信号。

`adder`实体定义了加法器的端口,包括两个二进制输入`A`和`B`,以及一个进位输入`Cin`,还有两个二进制输出`S`和`Cout`。

在`architecture behavioral`中,定义了加法器的行为。

`S <= ((A xor B) xor Cin)`语句实现了二进制数的加法运算,`Cout <= ((A xor B) AND Cin) OR (A AND B)`语句则实现了进位输出的计算。

请注意,这只是一个简单的示例,实际的二位二进制加法器可能需要考虑更多的细节和优化。

在实际应用中,你可能需要根据具体的需求进行修改和扩展。

vhdl通用十进制加法器

湖南人文科技学院课程设计报告课程名称:VHDL语言与EDA课程设计设计题目:通用十进制加法器系别:通信与控制工程系专业:电子信息工程班级:学生姓名:学号:起止日期:指导教师:教研室主任:指导教师评语:指导教师签名:年月日成绩评定项目权重成绩1、设计过程中出勤、学习态度等方面0.22、课程设计质量与答辩0.53、设计报告书写及图纸规范程度0.3总成绩教研室审核意见:教研室主任签字:年月日教学系审核意见:主任签字:年月日摘要随着科技的发展,通用十进制加法器的应用已广泛融入到现实生活中。

EDA 技术的应用引起电子产品及系统开发的革命性变革。

本文采用EDA技术设计,并以VHDL语言为基础制作的通用十进制加法器。

该系统借助于强大的EDA工具和硬件描述语言可实现两个一位以上的十进制数的加法,在输入两个十进制数之后,给出两个数的相加结果。

本设计充分利用VHDL“自顶向下”的设计优点以及层次化的设计概念,提高了设计的效率。

设计主要步骤:首先利用QUARTUS‖来编辑、编译、仿真各个模块;然后以原理图为顶层文件建立工程,再进行引脚锁定、编译、下载,最后采用杭州康芯电子有限公司生产的GW48系列/SOPC/EDA实验开发系统,进行硬件测试。

关键词:通用十进制加法器;EDA技术;VHDL语言; QUARTUS‖目录设计要求 (1)1、方案论证与对比 (1)1.1方案一 (1)1.2方案二 (1)1.3 方案的对比与选择 (2)2、设计原理 (2)3、通用十进制加法器的主要硬件模块 (3)3.1 4位BCD码全加器模块 (3)3.2八加法器的实现框图 (3)4、调试与操作 (4)4.1通用十进制加法器的功能仿真 (4)4.2模式选择与引脚锁定 (4)4.2.1模式选择 (4)4.2.2引脚锁定 (5)4.3设备与器件明细表 (6)4.4调试 (6)4.4.1软件调试 (6)4.4.2硬件调试 (6)5、总结与致谢 (7)5.1总结与思考 (7)5.2致谢 (7)附录 (8)附录一 (8)附录二 (9)参考文献 (11)通用十进制加法器设计要求1、用VHDL 硬件描述语言设计4位的BCD 码全加器;2、以4位BCD 码全加器为模块设计两位十进制数的加法。

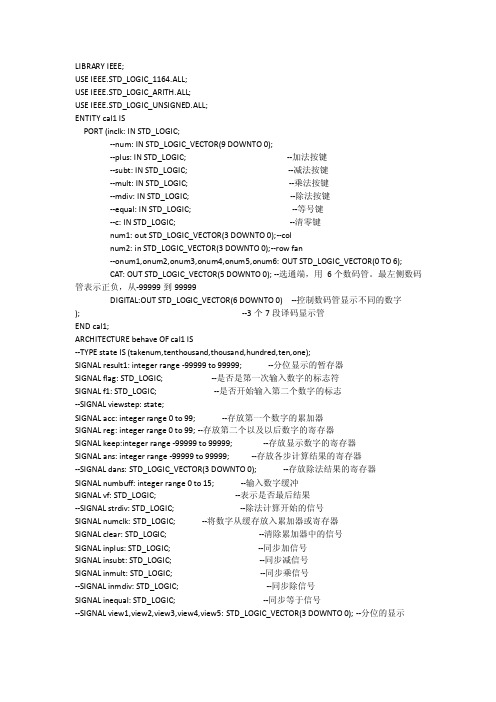

VHDL简易计算器代码

LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY cal1 ISPORT (inclk: IN STD_LOGIC;--num: IN STD_LOGIC_VECTOR(9 DOWNTO 0);--plus: IN STD_LOGIC; --加法按键--subt: IN STD_LOGIC; --减法按键--mult: IN STD_LOGIC; --乘法按键--mdiv: IN STD_LOGIC; --除法按键--equal: IN STD_LOGIC; --等号键--c: IN STD_LOGIC; --清零键num1: out STD_LOGIC_VECTOR(3 DOWNTO 0);--colnum2: in STD_LOGIC_VECTOR(3 DOWNTO 0);--row fan--onum1,onum2,onum3,onum4,onum5,onum6: OUT STD_LOGIC_VECTOR(0 TO 6);CAT: OUT STD_LOGIC_VECTOR(5 DOWNTO 0); --选通端,用6个数码管。

最左侧数码管表示正负,从-99999到99999DIGITAL:OUT STD_LOGIC_VECTOR(6 DOWNTO 0) --控制数码管显示不同的数字); --3个7段译码显示管END cal1;ARCHITECTURE behave OF cal1 IS--TYPE state IS (takenum,tenthousand,thousand,hundred,ten,one);SIGNAL result1: integer range -99999 to 99999; --分位显示的暂存器SIGNAL flag: STD_LOGIC; --是否是第一次输入数字的标志符SIGNAL f1: STD_LOGIC; --是否开始输入第二个数字的标志--SIGNAL viewstep: state;SIGNAL acc: integer range 0 to 99; --存放第一个数字的累加器SIGNAL reg: integer range 0 to 99; --存放第二个以及以后数字的寄存器SIGNAL keep:integer range -99999 to 99999; --存放显示数字的寄存器SIGNAL ans: integer range -99999 to 99999; --存放各步计算结果的寄存器--SIGNAL dans: STD_LOGIC_VECTOR(3 DOWNTO 0); --存放除法结果的寄存器SIGNAL numbuff: integer range 0 to 15; --输入数字缓冲SIGNAL vf: STD_LOGIC; --表示是否最后结果--SIGNAL strdiv: STD_LOGIC; --除法计算开始的信号SIGNAL numclk: STD_LOGIC; --将数字从缓存放入累加器或寄存器SIGNAL clear: STD_LOGIC; --清除累加器中的信号SIGNAL inplus: STD_LOGIC; --同步加信号SIGNAL insubt: STD_LOGIC; --同步减信号SIGNAL inmult: STD_LOGIC; --同步乘信号--SIGNAL inmdiv: STD_LOGIC; --同步除信号SIGNAL inequal: STD_LOGIC; --同步等于信号--SIGNAL view1,view2,view3,view4,view5: STD_LOGIC_VECTOR(3 DOWNTO 0); --分位的显示SIGNAL cou: STD_LOGIC_VECTOR(1 DOWNTO 0); --用力记忆是第几次--计算的信号SIGNAL clk_gg: STD_LOGIC_VECTOR(11 DOWNTO 0); --用于产生分频时钟的信号--SIGNAL CNT : INTEGER RANGE 0 TO 50000;--分频用SIGNAL clk: STD_LOGIC; --分频后的时钟信号--signal ko : integer range 0 to 15;SIGNAL CAT0:INTEGER RANGE 0 TO 10; --数码管显示5位数,共有5个CAT选通端SIGNAL CAT1:INTEGER RANGE 0 TO 10;SIGNAL CAT2:INTEGER RANGE 0 TO 10;SIGNAL CAT3:INTEGER RANGE 0 TO 10;SIGNAL CAT4:INTEGER RANGE 0 TO 10;TYPE TIME_TYPE IS (T1,T2,T3,T4,T5,T6);SIGNAL TIME1:TIME_TYPE;--COMPONENT numdecoder IS --引用数字按键的译码电路--PORT ( reset: IN STD_LOGIC;--inclk: IN STD_LOGIC;--innum: IN STD_LOGIC_VECTOR(9 DOWNTO 0);--outnum: BUFFER STD_LOGIC_VECTOR(3 DOWNTO 0);--outflag: OUT STD_LOGIC );--END COMPONENT;component keyboard ISPORT(--clk:in std_logic; ---时钟信号--row_scan :out STD_LOGIC_vector(3 downto 0); ---行扫描输出信号--col_scan :in std_logic_vector(3 downto 0);---列扫描输入信号--key_output :out std_logic_vector(3 downto 0);--key_down :out std_logic;--keyout :out integer range 0 to 15;--SYS_CLK : in std_logic;-- KEY_ROW : in std_logic_vector(3 downto 0); --4*4键盘扫描4输入--KEY_COL : out std_logic_vector(3 downto 0); --4*4键盘扫描4输出--KEY_DATA : out std_logic_vector(3 downto 0); --输出键值,-- KEY_READY : out std_logicKEY_CLK : in std_logic;KEY_ROW : in std_logic_vector(3 downto 0); --4*4键盘扫描4输入KEY_COL : out std_logic_vector(3 downto 0); --4*4键盘扫描4输出--KEY_DATA : out std_logic_vector(3 downto 0); --输出键值,--KEY_READY : out std_logicKEY_DOWN :out std_logic;KEY_OUT :out integer range 0 to 15);end component;--COMPONENT vdecode IS --引用7段译码器--PORT(indata:IN STD_LOGIC_VECTOR(3 DOWNTO 0);-- outdata:OUT STD_LOGIC_VECTOR(0 TO 6));--END COMPONENT;--COMPONENT diver IS --引用除法器--PORT( a: IN STD_LOGIC_VECTOR(7 DOWNTO 0);-- b: IN STD_LOGIC_VECTOR(3 DOWNTO 0);-- clk: IN STD_LOGIC;--str: IN STD_LOGIC;--s: OUT STD_LOGIC_VECTOR(3 DOWNTO 0);-- y: OUT STD_LOGIC_VECTOR(3 DOWNTO 0)--);--END COMPONENT;BEGIN--inum1: numdecoder port map(c,clk,num,numbuff,numclk);--inum2:keyboard44 port map(clk,num1,num2,numbuff,numclk,ko);inum2:keyboard port map(inclk,num2,num1,numclk,numbuff);clock: PROCESS(inclk,numbuff) --进程clock用于产生分频的时钟,使得12位向量clk_gg不断加1,然后输出12位中的某一位BEGINIF inclk'EVENT AND inclk='1' thenclk_gg(11 DOWNTO 0)<=clk_gg(11 DOWNTO 0)+1;END IF;END PROCESS clock;clk<=clk_gg(11);pacecal: PROCESS(numbuff,clk)BEGINIF (rising_edge(clk) and numbuff=15) theninplus<='0';insubt<='0';inmult<='0';--inmdiv<='0';ELSIF clk'EVENT AND clk='1' thenIF numbuff=10 theninplus<='1'; insubt<='0';inmult<='0';--inmdiv<='0';ELSIF numbuff=11 theninplus<='0';insubt<='1';inmult<='0';--inmdiv<='0';ELSIF numbuff=12 theninplus<='0';insubt<='0';inmult<='1';--inmdiv<='0';-- ELSIF mdiv='1' then-- inplus<='0';insubt<='0';inmult<='0';inmdiv<='1';END IF;END IF;END PROCESS pacecal;ctrflag: PROCESS(numbuff,clk) --用于产生flag信号BEGINIF (rising_edge(clk) and numbuff=15) thenflag<='0';ELSIF clk'EVENT AND clk='1' thenIF inplus='1' OR insubt='1' OR inmult='1' --OR inmdiv='1'THENflag<='1';ELSE flag<='0';END IF;END IF;END PROCESS ctrflag;ctrfirstnum: PROCESS(numbuff,numclk) --用于输入第一个运算数BEGINIF ( numbuff=15) thenacc<=0;ELSIF numclk'EVENT AND numclk='1' thenIF flag='0' thenacc<=acc*10+numbuff;END IF;END IF;END PROCESS ctrfirstnum;ctrsecondnum:PROCESS(numbuff,clear,numclk) --用于输入第二个以后的运算数字BEGINIF ( numbuff=15 OR clear='1')THENreg<=0;f1<='0';ELSIF numclk'event AND numclk='1'THENIF flag='1'THENf1<='1';reg<=reg*10+numbuff;END IF;END IF;END PROCESS ctrsecondnum;ctrclear: PROCESS(numbuff,clk) --用于产生clear信号为什么c和clear不同步反BEGINIF (numbuff=15)thenclear<='0';ELSIF clk'EVENT AND clk='1' thenIF numbuff=10 or numbuff=11 or numbuff=12 thenclear<='1';ELSE clear<='0';END IF;END IF;END PROCESS ctrclear;ctrinequal:PROCESS(numbuff,clk) --用于产生inequal信号BEGINIF (numbuff=15) theninequal<='0';ELSIF clk'EVENT AND clk='1' thenIF numbuff=10 or numbuff=11 or numbuff=12 or numbuff=14 theninequal<='1';ELSE inequal<='0';END IF;END IF;END PROCESS ctrinequal;ctrcou: process (numbuff,inequal) --用于产生cou信号什么意思?BEGINIF (numbuff=15 )thencou<="00";ELSIF inequal'EVENT and inequal='1'thenIF cou="10" thencou<=cou;ELSE cou<=cou+1;END IF;END IF;END PROCESS ctrcou;ctrcal: PROCESS (numbuff,inequal) --用于实现运算BEGINIF ( numbuff=15 ) thenans<=0;--strdiv<='0';ELSIF inequal'EVENT and inequal='1' thenIF flag='1' thenIF inplus='1' thenIF cou="10" thenans<=ans+reg;ELSE ans<=acc+reg;END IF;ELSIF insubt='1'THENIF cou="10"THENans<=ans-reg;ELSE ans<=acc-reg;END IF;ELSIF inmult='1' then--IF acc<="1111111" AND reg<="1111111" then--将乘数和被乘数限制在4位二进制数范围内IF cou="10" thenans<=ans*reg;ELSE ans<=acc*reg;END IF;--ELSE ans<=0;-- END IF;--ELSIF inmdiv='1'THEN--strdiv<='1';END IF;--else strdiv<='0';END IF;END IF;END PROCESS ctrcal;--d1:diver PORT MAP (acc,reg(3 DOWNTO 0),clk,strdiv,dans);--将除法结果放在dans中ctrvf: PROCESS(numbuff,clk) --用来产生vf信号BEGINIF (rising_edge(clk) and numbuff=15) thenvf<='0';ELSIF (rising_edge(clk) and numbuff=14) thenvf<='1';END IF;END PROCESS ctrvf;ctrkeep: process(numbuff,clk) --用于控制keep寄存器BEGINIF (numbuff=15) then --keep寄存器清零keep<=0;ELSIF clk'EVENT AND clk='1' thenIF flag='0' then --输入第二个数以前keep中存放acc中的数keep<=acc;ELSIF flag='1' AND f1='1' AND vf='0' then--输入第二个数以前keep中存放reg中的数keep<=reg;ELSIF flag='1' AND f1='0'AND vf='0'AND cou="10" then--keep中存放ans中的内容keep<=ans;ELSIF flag='1'and vf='1'then --最终的计算结果-- IF inmdiv='0'THENkeep<=ans;-- ELSE-- keep(3 DOWNTO 0)<=dans;--END IF;END IF;END IF;END PROCESS ctrkeep;ctrview:PROCESS(numbuff,clk)BEGINIF (rising_edge(clk) and numbuff=15) THENcat4<=0; cat3<=0;cat2<=0;cat1<=0;cat0<=0;ELSIF clk'EVENT AND clk='1'THENif(keep<0)then result1<=abs(keep);else result1<=keep;end if;if(result1>99999 )then cat4<=10; cat3<=10;cat2<=10;cat1<=10;cat0<=10;end if;if(result1>=90000 and result1<=99999)then cat4<=9;elsif(result1>=80000 and result1<90000)then cat4<=8;elsif(result1>=70000 and result1<80000)then cat4<=7;elsif(result1>=60000 and result1<70000)then cat4<=6;elsif(result1>=50000 and result1<60000)then cat4<=5;elsif(result1>=40000 and result1<50000)then cat4<=4;elsif(result1>=30000 and result1<40000)then cat4<=3;elsif(result1>=20000 and result1<30000)then cat4<=2;elsif(result1>=10000 and result1<20000)then cat4<=1;elsif(result1<10000 )then cat4<=0;end if;if((result1-cat4*10000)>=9000 and (result1-cat4*10000)<10000)then cat3<=9;elsif((result1-cat4*10000)>=8000 and (result1-cat4*10000)<9000)then cat3<=8;elsif((result1-cat4*10000)>=7000 and (result1-cat4*10000)<8000)then cat3<=7;elsif((result1-cat4*10000)>=6000 and (result1-cat4*10000)<7000)then cat3<=6;elsif((result1-cat4*10000)>=5000 and (result1-cat4*10000)<6000)then cat3<=5;elsif((result1-cat4*10000)>=4000 and (result1-cat4*10000)<5000)then cat3<=4;elsif((result1-cat4*10000)>=3000 and (result1-cat4*10000)<4000)then cat3<=3;elsif((result1-cat4*10000)>=2000 and (result1-cat4*10000)<3000)then cat3<=2;elsif((result1-cat4*10000)>=1000 and (result1-cat4*10000)<2000)then cat3<=1;elsif((result1-cat4*10000)<1000)then cat3<=0;end if;if((result1-cat4*10000-cat3*1000)>=900and (result1-cat4*10000-cat3*1000)<1000)then cat2<=9;elsif((result1-cat4*10000-cat3*1000)>=800and (result1-cat4*10000-cat3*1000)<900)then cat2<=8;elsif((result1-cat4*10000-cat3*1000)>=700and (result1-cat4*10000-cat3*1000)<800)then cat2<=7;elsif((result1-cat4*10000-cat3*1000)>=600and (result1-cat4*10000-cat3*1000)<700)then cat2<=6;elsif((result1-cat4*10000-cat3*1000)>=500and (result1-cat4*10000-cat3*1000)<600)thencat2<=5;elsif((result1-cat4*10000-cat3*1000)>=400and (result1-cat4*10000-cat3*1000)<500)then cat2<=4;elsif((result1-cat4*10000-cat3*1000)>=300and (result1-cat4*10000-cat3*1000)<400)then cat2<=3;elsif((result1-cat4*10000-cat3*1000)>=200and (result1-cat4*10000-cat3*1000)<300)then cat2<=2;elsif((result1-cat4*10000-cat3*1000)>=100and (result1-cat4*10000-cat3*1000)<200)then cat2<=1;elsif((result1-cat4*10000-cat3*1000)<100) then cat2<=0;end if;if((result1-cat4*10000-cat3*1000-cat2*100)>=90and(result1-cat4*10000-cat3*1000-cat2*100)<100)then cat1<=9;elsif((result1-cat4*10000-cat3*1000-cat2*100)>=80and(result1-cat4*10000-cat3*1000-cat2*100)<90)then cat1<=8;elsif((result1-cat4*10000-cat3*1000-cat2*100)>=70and(result1-cat4*10000-cat3*1000-cat2*100)<80)then cat1<=7;elsif((result1-cat4*10000-cat3*1000-cat2*100)>=60and(result1-cat4*10000-cat3*1000-cat2*100)<70)then cat1<=6;elsif((result1-cat4*10000-cat3*1000-cat2*100)>=50and(result1-cat4*10000-cat3*1000-cat2*100)<60)then cat1<=5;elsif((result1-cat4*10000-cat3*1000-cat2*100)>=40and(result1-cat4*10000-cat3*1000-cat2*100)<50)then cat1<=4;elsif((result1-cat4*10000-cat3*1000-cat2*100)>=30and(result1-cat4*10000-cat3*1000-cat2*100)<40)then cat1<=3;elsif((result1-cat4*10000-cat3*1000-cat2*100)>=20and(result1-cat4*10000-cat3*1000-cat2*100)<30)then cat1<=2;elsif((result1-cat4*10000-cat3*1000-cat2*100)>=10and(result1-cat4*10000-cat3*1000-cat2*100)<20)then cat1<=1;elsif((result1-cat4*10000-cat3*1000-cat2*100)<10)then cat1<=0;end if;cat0<=result1-cat4*10000-cat3*1000-cat2*100-cat1*10;end if;END PROCESS ctrview;--v1:vdecode PORT MAP (view1,onum1); --7段译码显示百位--v2:vdecode PORT MAP (view2,onum2); --7段译码显示十位--v3:vdecode PORT MAP (view3,onum3); --7段译码显示个位--v4:vdecode PORT MAP (view4,onum4); --7段译码显示十位--v5:vdecode PORT MAP (view5,onum5); --7段译码显示个位xianshi:PROCESS(clk,time1,cat4,cat3,cat2,cat1,cat0)beginIF rising_edge(clk) THENif(keep>=0)thenCASE TIME1 ISWHEN T1 =>CAT <= "101111";CASE CAT4 ISWHEN 0=> DIGITAL <= "1111110";WHEN 1=> DIGITAL <= "0110000";WHEN 2=> DIGITAL <= "1101101";WHEN 3=> DIGITAL <= "1111001";WHEN 4=> DIGITAL <= "0110011";WHEN 5=> DIGITAL <= "1011011";WHEN 6=> DIGITAL <= "1011111";WHEN 7=> DIGITAL <= "1110000";WHEN 8=> DIGITAL <= "1111111";WHEN 9=> DIGITAL <= "1111011";WHEN 10=> DIGITAL <="1001111";END CASE;TIME1 <= T2;WHEN T2 =>CAT <= "110111";CASE CAT3 ISWHEN 0=> DIGITAL <= "1111110";WHEN 1=> DIGITAL <= "0110000";WHEN 2=> DIGITAL <= "1101101";WHEN 3=> DIGITAL <= "1111001";WHEN 4=> DIGITAL <= "0110011";WHEN 5=> DIGITAL <= "1011011";WHEN 6=> DIGITAL <= "1011111";WHEN 7=> DIGITAL <= "1110000";WHEN 8=> DIGITAL <= "1111111";WHEN 9=> DIGITAL <= "1111011";WHEN 10=> DIGITAL <="1000110";END CASE;TIME1 <= T3;WHEN T3 =>CAT <= "111011";CASE CAT2 ISWHEN 0=> DIGITAL <= "1111110";WHEN 1=> DIGITAL <= "0110000";WHEN 2=> DIGITAL <= "1101101";WHEN 3=> DIGITAL <= "1111001"; WHEN 4=> DIGITAL <= "0110011"; WHEN 5=> DIGITAL <= "1011011"; WHEN 6=> DIGITAL <= "1011111"; WHEN 7=> DIGITAL <= "1110000"; WHEN 8=> DIGITAL <= "1111111"; WHEN 9=> DIGITAL <= "1111011"; WHEN 10=> DIGITAL <="1000110"; END CASE;TIME1 <= T4;WHEN T4 =>CAT <= "111101";CASE CAT1 ISWHEN 0=> DIGITAL <= "1111110"; WHEN 1=> DIGITAL <= "0110000"; WHEN 2=> DIGITAL <= "1101101"; WHEN 3=> DIGITAL <= "1111001"; WHEN 4=> DIGITAL <= "0110011"; WHEN 5=> DIGITAL <= "1011011"; WHEN 6=> DIGITAL <= "1011111"; WHEN 7=> DIGITAL <= "1110000"; WHEN 8=> DIGITAL <= "1111111"; WHEN 9=> DIGITAL <= "1111011"; WHEN 10=> DIGITAL <= "1111110"; END CASE;TIME1 <= T5;WHEN T5 =>CAT <= "111110";CASE CAT0 ISWHEN 0=> DIGITAL <= "1111110"; WHEN 1=> DIGITAL <= "0110000"; WHEN 2=> DIGITAL <= "1101101"; WHEN 3=> DIGITAL <= "1111001"; WHEN 4=> DIGITAL <= "0110011"; WHEN 5=> DIGITAL <= "1011011"; WHEN 6=> DIGITAL <= "1011111"; WHEN 7=> DIGITAL <= "1110000"; WHEN 8=> DIGITAL <= "1111111"; WHEN 9=> DIGITAL <= "1111011"; WHEN 10=> DIGITAL <="1000110"; END CASE;TIME1 <= T1;WHEN OTHERS => TIME1 <= T1;END CASE;elsif(keep<0)thenCASE time1 ISWHEN t1 =>cat <= "101111";CASE cat4 ISWHEN 0=> digital <= "1111110";WHEN 1=> digital <= "0110000";WHEN 2=> digital <= "1101101";WHEN 3=> digital <= "1111001";WHEN 4=> digital <= "0110011";WHEN 5=> digital <= "1011011";WHEN 6=> digital <= "1011111";WHEN 7=> digital <= "1110000";WHEN 8=> digital <= "1111111";WHEN 9=> digital <= "1111011";WHEN 10=> DIGITAL <="1001111";END CASE;time1 <= t2;WHEN t2 =>cat <= "110111";CASE cat3 ISWHEN 0=> digital <= "1111110";WHEN 1=> digital <= "0110000";WHEN 2=> digital <= "1101101";WHEN 3=> digital <= "1111001";WHEN 4=> digital <= "0110011";WHEN 5=> digital <= "1011011";WHEN 6=> digital <= "1011111";WHEN 7=> digital <= "1110000";WHEN 8=> digital <= "1111111";WHEN 9=> digital <= "1111011";WHEN 10=> DIGITAL <="1000110";end case;time1 <= t3;WHEN t3 =>cat <= "111011";CASE cat2 ISWHEN 1=> digital <= "0110000"; WHEN 2=> digital <= "1101101"; WHEN 3=> digital <= "1111001"; WHEN 4=> digital <= "0110011"; WHEN 5=> digital <= "1011011"; WHEN 6=> digital <= "1011111"; WHEN 7=> digital <= "1110000"; WHEN 8=> digital <= "1111111"; WHEN 9=> digital <= "1111011"; WHEN 10=> DIGITAL <="1000110"; END CASE;time1 <= t4;WHEN t4 =>cat <= "111101";CASE cat1 ISWHEN 0=> digital <= "1111110"; WHEN 1=> digital <= "0110000"; WHEN 2=> digital <= "1101101"; WHEN 3=> digital <= "1111001"; WHEN 4=> digital <= "0110011"; WHEN 5=> digital <= "1011011"; WHEN 6=> digital <= "1011111"; WHEN 7=> digital <= "1110000"; WHEN 8=> digital <= "1111111"; WHEN 9=> digital <= "1111011"; WHEN 10=> DIGITAL <= "1111110"; END CASE;time1 <= t5;WHEN t5 =>cat <= "111110";CASE cat0 ISWHEN 0=> digital <= "1111110"; WHEN 1=> digital <= "0110000"; WHEN 2=> digital <= "1101101"; WHEN 3=> digital <= "1111001"; WHEN 4=> digital <= "0110011"; WHEN 5=> digital <= "1011011"; WHEN 6=> digital <= "1011111"; WHEN 7=> digital <= "1110000"; WHEN 8=> digital <= "1111111"; WHEN 9=> digital <= "1111011";END CASE;time1 <= t6;when t6=>cat<="011111";digital<="0000001";time1<=t1;WHEN OTHERS => time1 <= t1;END CASE;end if;--end if;--end process;--end lz;end if;end process;END behave;。

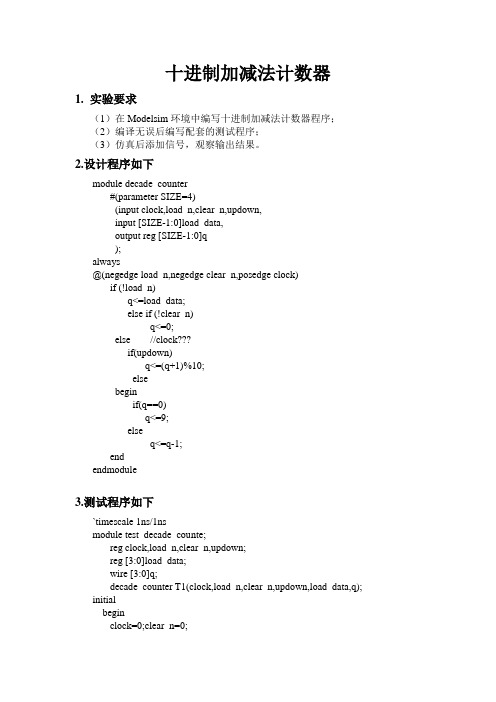

verilog HDL十进制加减法计数器报告

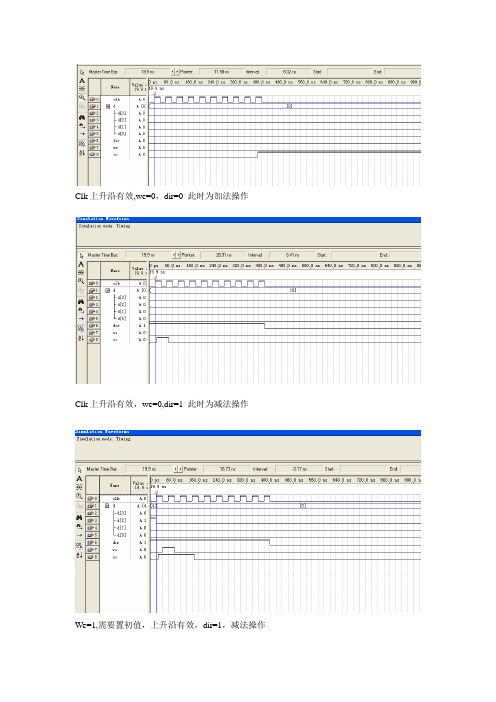

十进制加减法计数器1.实验要求(1)在Modelsim环境中编写十进制加减法计数器程序;(2)编译无误后编写配套的测试程序;(3)仿真后添加信号,观察输出结果。

2.设计程序如下module decade_counter#(parameter SIZE=4)(input clock,load_n,clear_n,updown,input [SIZE-1:0]load_data,output reg [SIZE-1:0]q);always@(negedge load_n,negedge clear_n,posedge clock)if (!load_n)q<=load_data;else if (!clear_n)q<=0;else //clockif(updown)q<=(q+1)%10;elsebeginif(q==0)q<=9;elseq<=q-1;endendmodule3.测试程序如下`timescale 1ns/1nsmodule test_decade_counte;reg clock,load_n,clear_n,updown;reg [3:0]load_data;wire [3:0]q;decade_counter T1(clock,load_n,clear_n,updown,load_data,q);initialbeginclock=0;clear_n=0;#30 clear_n=1;load_n=0;load_data=7;#30 load_n=1;updown=0;#300 updown=1;#300 updown=0;#300 updown=1;#300 $stop;endalways#10 clock=~clock;always@(q)$display("At time%t,q=%d",$time,q);endmodule4.波形如下5.测试结果如下# At time 0,q= 0# At time 30,q= 7# At time 70,q= 6# At time 90,q= 5# At time 110,q= 4# At time 130,q= 3# At time 150,q= 2# At time 170,q= 1# At time 190,q= 0# At time 210,q= 9# At time 230,q= 8# At time 250,q= 7# At time 270,q= 6# At time 290,q= 5# At time 310,q= 4# At time 330,q= 3# At time 370,q= 3 # At time 390,q= 4 # At time 410,q= 5 # At time 430,q= 6 # At time 450,q= 7 # At time 470,q= 8 # At time 490,q= 9 # At time 510,q= 0 # At time 530,q= 1 # At time 550,q= 2 # At time 570,q= 3 # At time 590,q= 4 # At time 610,q= 5 # At time 630,q= 6 # At time 650,q= 7 # At time 670,q= 6 # At time 690,q= 5 # At time 710,q= 4 # At time 730,q= 3 # At time 750,q= 2 # At time 770,q= 1 # At time 790,q= 0 # At time 810,q= 9 # At time 830,q= 8 # At time 850,q= 7 # At time 870,q= 6 # At time 890,q= 5 # At time 910,q= 4 # At time 930,q= 3 # At time 950,q= 2 # At time 970,q= 3 # At time 990,q= 4 # At time 1010,q= 5 # At time 1030,q= 6 # At time 1050,q= 7 # At time 1070,q= 8 # At time 1090,q= 9 # At time 1110,q= 0 # At time 1130,q= 1 # At time 1150,q= 2 # At time 1170,q= 3 # At time 1190,q= 4 # At time 1210,q= 5# At time 1250,q= 7。

用VHDL实现计算器

谢谢观看!

then in3:=in1/in2; t<=in3; end if; end process p1111;

--'*'

p111:process(t) begin case t is when 0=>g<="11111100";--0 when 1=>g<="01100000";--1 when 2=>g<="11011010";--2 when 3=>g<="11110010";--3 when 4=>g<="01100110";--4 when 5=>g<="10110110";--5 when 6=>g<="10111110";--6 when 7=>g<="11100000";--7 when 8=>g<="11111110";--8 when 9=>g<="11110110";--9 when others=>t<="00000010";--错 end case; end process p111;

程序源码

--库的引用 LIBRARY IEEE; --USE IEEE.std_logic_arith.ALL; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL; --use ieee.numeric_bit.all;

--实体声明 entity adder is port( d0,d1,d2,d3,d4,d5,d6,d7,d8,d9,d10,d11,d12,d13,d

VHDL双向十进制加减法计数器(代码和截图)

);

end entity;

architecture rtl of vh is

SIGNAL temp:std_logic_vector(3 downto 0);

begin

process (clk)

begin

if(we='1')then

temp<=d;

elsif(clk'event and clk='1')then

if(dir='0')then

if(temp<9)then

temp<=temp+'1';

co<=ห้องสมุดไป่ตู้0';

else

temp<="0000";

co<='1';

end if;

elsif(dir='1')then

if(temp>0)then

temp<=temp-'1';

co<='0';

else

temp<="1001";

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

USE ieee.std_logic_unsigned.ALL;

entity vh is

port

(

clk: in std_logic;

dir: in std_logic;

we: in std_logic;

d : in std_logic_vector(3 downto 0);

co<='1';

verilog设计十进制计数器(含进位位)

verilog设计⼗进制计数器(含进位位)⼗进制计数器:设计要求:1、每当计数器值为4’b001时,⾃动回到4’b00002、每个时钟沿计数器值加13、进位输出carry应该与4'b1001同周期输出4、异步复位module cnt10 ( clk, rst_n, carry, cnt );input clk, rst_n;output carry;output [3:0] cnt;reg carry;reg [3:0] cnt;always @( posedge clk or negedge rst_n )beginif ( ~rst_n )begincnt <= 4'b0000;endelse if ( cnt == 4'b1001 )begincnt <= 4'b0000;endelsebegincnt <= cnt + 4'b0001;endendalways @(posedge clk or negedge rst_n)beginif(!rst_n)begincarry <= 1'b0;endelse if(cnt == 4'b1000)begincarry <= 1'b1;endelsecarry<= 1'b0;endendmoduleView Code测试程序:`timescale 1ns/1psmodule cnt10_tb();reg clk, rst_n;wire carry;wire [3:0] cnt;always #10 clk = ~clk;cnt10 cnt10_tb(.clk(clk),.rst_n(rst_n),.carry(carry),.cnt(cnt));initialbeginclk = 1'b0;rst_n = 1'b1;#10 rst_n = 1'b0;#10 rst_n = 1'b1;endendmodule波形图:在这个⼗进制计数器中,唯⼀要注意的⼀点就是进位位carry变化的时刻,如果是为了使下⼀级能正确接收到前⼀级的进位位标识,要在计数到九时使进位位有效;如上图波形所⽰。