数字电子时钟源程序

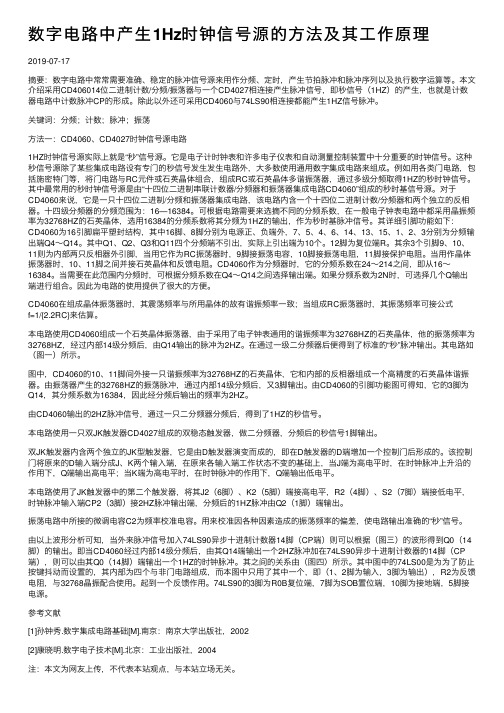

数字电路中产生1Hz时钟信号源的方法及其工作原理

数字电路中产⽣1Hz时钟信号源的⽅法及其⼯作原理2019-07-17摘要:数字电路中常常需要准确、稳定的脉冲信号源来⽤作分频、定时,产⽣节拍脉冲和脉冲序列以及执⾏数字运算等。

本⽂介绍采⽤CD406014位⼆进制计数/分频/振荡器与⼀个CD4027相连接产⽣脉冲信号,即秒信号(1HZ)的产⽣,也就是计数器电路中计数脉冲CP的形成。

除此以外还可采⽤CD4060与74LS90相连接都能产⽣1HZ信号脉冲。

关键词:分频;计数;脉冲;振荡⽅法⼀:CD4060、CD4027时钟信号源电路1HZ时钟信号源实际上就是“秒”信号源。

它是电⼦计时钟表和许多电⼦仪表和⾃动测量控制装置中⼗分重要的时钟信号。

这种秒信号源除了某些集成电路设有专门的秒信号发⽣发⽣电路外,⼤多数使⽤通⽤数字集成电路来组成。

例如⽤各类门电路,包括施密特门等,将门电路与RC元件或⽯英晶体组合,组成RC或⽯英晶体多谐振荡器,通过多级分频取得1HZ的秒时钟信号。

其中最常⽤的秒时钟信号源是由“⼗四位⼆进制串联计数器/分频器和振荡器集成电路CD4060”组成的秒时基信号源。

对于CD4060来说,它是⼀只⼗四位⼆进制/分频和振荡器集成电路,该电路内含⼀个⼗四位⼆进制计数/分频器和两个独⽴的反相器。

⼗四级分频器的分频范围为:16―16384。

可根据电路需要来选摘不同的分频系数,在⼀般电⼦钟表电路中都采⽤晶振频率为32768HZ的⽯英晶体,选⽤16384的分频系数将其分频为1HZ的输出,作为秒时基脉冲信号。

其详细引脚功能如下:CD4060为16引脚扁平塑封结构,其中16脚、8脚分别为电源正、负端外,7、5、4、6、14、13、15、1、2、3分别为分频输出端Q4~Q14。

其中Q1、Q2、Q3和Q11四个分频端不引出,实际上引出端为10个。

12脚为复位端R。

其余3个引脚9、10、11则为内部两只反相器外引脚,当⽤它作为RC振荡器时,9脚接振荡电容,10脚接振荡电阻,11脚接保护电阻。

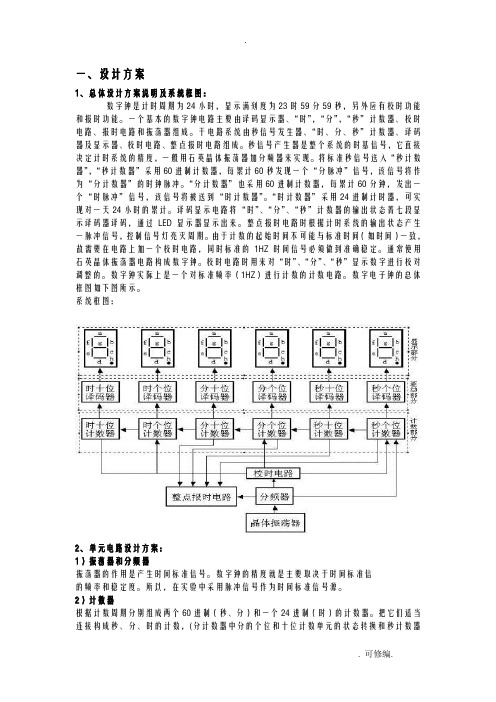

数字电子钟方案及对策

一、设计方案1、总体设计方案说明及系统框图:数字钟是计时周期为24小时,显示满刻度为23时59分59秒,另外应有校时功能和报时功能。

一个基本的数字钟电路主要由译码显示器、“时”,“分”,“秒”计数器、校时电路、报时电路和振荡器组成。

干电路系统由秒信号发生器、“时、分、秒”计数器、译码器及显示器、校时电路、整点报时电路组成。

秒信号产生器是整个系统的时基信号,它直接决定计时系统的精度,一般用石英晶体振荡器加分频器来实现。

将标准秒信号送入“秒计数器”,“秒计数器”采用60进制计数器,每累计60秒发现一个“分脉冲”信号,该信号将作为“分计数器”的时钟脉冲。

“分计数器”也采用60进制计数器,每累计60分钟,发出一个“时脉冲”信号,该信号将被送到“时计数器”。

“时计数器”采用24进制计时器,可实现对一天24小时的累计。

译码显示电路将“时”、“分”、“秒”计数器的输出状态菁七段显示译码器译码,通过LED显示器显示出来。

整点报时电路时根据计时系统的输出状态产生一脉冲信号,控制信号灯亮灭周期。

由于计数的起始时间不可能与标准时间(如时间)一致,故需要在电路上加一个校时电路,同时标准的1HZ时间信号必须做到准确稳定。

通常使用石英晶体振荡器电路构成数字钟。

校时电路时用来对“时”、“分”、“秒”显示数字进行校对调整的。

数字钟实际上是一个对标准频率(1HZ)进行计数的计数电路。

数字电子钟的总体框图如下图所示。

系统框图:2、单元电路设计方案:1)振荡器和分频器振荡器的作用是产生时间标准信号。

数字钟的精度就是主要取决于时间标准信的频率和稳定度。

所以,在实验中采用脉冲信号作为时间标准信号源。

2)计数器根据计数周期分别组成两个60进制(秒、分)和一个24进制(时)的计数器。

把它们适当连接构成秒、分、时的计数,(分计数器中分的个位和十位计数单元的状态转换和秒计数器中的是一样的,只是它要把进位信号传输给时的个位计数单元。

) 实现计时功能。

LED数字显示电子时钟源程序代码

LED数字显示电子时钟源程序代码程序:(注已完全经过调试,达到预期目的)#include<reg51.h>#define uchar unsigned char#define uint unsigned intuchar count=0;sbit LED=P1^0;uchar tab[]={0x3f,0x06,0x5b,0x4f,0x66,0x6d,0x7d,0x07,0x7f,0x6f}; //显示数码管0,1,3,4,5,6,7,8,9 uchar miao=0,fen=0,hour=0;void delay(uint i) //延迟函数{uint j;for(;i>0;i--)for(j=124;j>0;j--);}void init(){ET0=1;TMOD=0x51; //选定定时器0,1和中断0,1TH0=(65536-25000)/256;TL0=(65536-25000)%256; //设定时器0时间为250ms一次ET1=1;TH1=0xff;TL1=0xff; //定时器1为中断EX0=1;IT0=1; //中断0开EX1=1;IT1=1; //中断1开TR0=1; //定时器0开TR1=1; //定时器1开EA=1; //总中断开}void display() //时钟显示函数{P0=tab[hour/10%10];P2=0xfe;delay(1);P0=tab[hour%10];P2=0xfd;delay(1);P0=tab[fen/10%10];P2=0xfb;delay(1);P0=tab[fen%10];P2=0xf7;delay(1);P0=tab[miao/10%10];P2=0xef;delay(1);P0=tab[miao%10];P2=0xdf;delay(1);}void main() //主函数{init();LED=0;while(1){display();}}void T0_int() interrupt 1 //定时器0函数{TH0=(65536-25000)/256;TL0=(65536-25000)%256;count++;if(count==20){count=0;miao= miao +1;LED=~LED;if(sec==60){miao=0;fen= fen +1;if(fen ==60){fen =0;hour=hour+1;if(hour==24)hour=0;}}}}void T1_int() interrupt 3 //定时器1函数控制秒针加1 {TH1=0xff;TL1=0xff;miao=miao+1;if(miao ==60)miao =0;}void I1_int() interrupt 2 //中断1函数控制按键分针加1 {EX0=0;fen= fen +1;if(fen ==60)fen =0;EX0=1;}void I0_int() interrupt 0 //中断函数0控制按键时针加1 {EX1=0;hour=hour+1;if(hour==24)hour=0;EX1=1;}。

多功能数字电子钟_VHDL

四、各功能模块的源程序代码 :

-- CONTOR 模块 library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; use ieee.std_logic_arith.all; entity contor is

1 )“小时” 校时状态: 进入“小时”校时状态后,显示 “小时” 的数码管闪烁,每按动“ k” 键一次,“小时” +1,若不按动“ k”键 则小时数不变,一直按下“ k” 键则小时数一 4Hz 的频率递增计数。

2 )“分”校时状态:进入“分”校时状态后,显示“分”的数 码管闪烁,每按动“ k” 键一次,“分” +1,若不按动“ k”键则分数 不变,一直按下“ k” 键则分数一 4Hz的频率递增计数。

chs,cms,css,f4 :in std_logic; bsg,bmg,bhg,bsd,bmd,bhd :buffer std_logic_vector(3 downto 0); comout :out std_logic); end time_com; architecture time_comx of time_com is begin com:process(hh,mh,sh,hl,ml) begin if(bhg=hh and bhd=hl and bmg=mh and bmd=ml and bsg=sh)then comout<='1'; else comout<='0'; end if; end process; set:process(f4) begin if(f4'event and f4='1')then if(chs='1'and k='0')then if(bhg="0010" and bhd="0011")then bhd<="0000";bhg<="0000"; elsif(bhd="1001")then bhd<="0000";bhg<=bhg+1; elsif(bhd="0000"or bhd="0001" or bhd="0010"or bhd="0011"or bhd="0100"or bhd="0101"or bhd="0110"or bhd="0111"or bhd="1000")then bhd<=bhd+1; end if; end if; end if; end process; process(f4) begin if(f4'event and f4='1')then if(cms='1'and k='0')then if(bmg="0101" and bmd="1001")then

简单的数字时钟(verilog设计)

设计目标与要求

设计一个简单的数字 时钟,能够显示时、 分、秒。

时钟应具有可靠性、 稳定性和可扩展性。

要求使用Verilog语 言实现,并能够在 FPGA或ASIC上实现。

设计思路及流程

• 设计思路:采用模块化设计方法,将数字时钟划分为不同的模 块,如计数器模块、显示模块等。每个模块负责实现特定的功 能,并通过接口与其他模块进行通信。

设计思路及流程

设计流程 1. 确定设计需求和目标。 2. 制定设计方案和计划。

设计思路及流程

3. 编写Verilog代码,实现各个模块的功能。 5. 根据测试结果进行调试和优化。

未来改进方向探讨

提高计时精度

通过改进算法或采用更高 性能的硬件平台,提高数

字时钟的计时精度。

降低资源占用

优化代码结构,减少不 必要的资源占用,提高 时钟系统的运行效率。

增加实用功能

拓展应用领域

考虑增加闹钟、定时器 等实用功能,使数字时 钟更加符合用户需求。

探索将数字时钟应用于 更多领域,如智能家居、

数据类型与运算符

Verilog中的数据类型包括

整型、实型、时间型、数组、结构体等。

Verilog中的运算符包括

算术运算符、关系运算符、逻辑运算符、位运算符等。

顺序语句与并行语句

Verilog中的顺序语句包括

赋值语句、条件语句、循环语句等,用于描述电路的时序行为。

Verilog中的并行语句包括

模块实例化、连续赋值语句、门级电路描述等,用于描述电路的并行行为。

基于C51单片机的数字时钟课程设计(C语言带闹钟)

单片机技术课程设计数字电子钟学院:班级:姓名:学号:教师:摘要电子钟在生活中应用非常广泛,而一种简单方便的数字电子钟则更能受到人们的欢迎。

所以设计一个简易数字电子钟很有必要。

本电子钟采用AT89C52单片机为核心,使用12MHz 晶振与单片机AT89C52 相连接,通过软件编程的方法实现以24小时为一个周期,同时8位7段LED数码管(两个四位一体数码管)显示小时、分钟和秒的要求,并在计时过程中具有定时功能,当时间到达提前定好的时间进行蜂鸣报时。

该电子钟设有四个按键KEY1、KEY2、KEY3、KEY4和KEY5键,进行相应的操作就可实现校时、定时、复位功能。

具有时间显示、整点报时、校正等功能。

走时准确、显示直观、运行稳定等优点。

具有极高的推广应用价值。

关键词:电子钟 AT89C52 硬件设计软件设计目录NO TABLE OF CONTENTS ENTRIES FOUND.一、数字电子钟设计任务、功能要求说明及方案介绍1.1 设计课题设计任务设计一个具有特定功能的电子钟。

具有时间显示,并有时间设定,时间调整功能。

1.2 设计课题的功能要求说明设计一个具有特定功能的电子钟。

该电子钟上电或按键复位后能自动显示系统提示符“d.1004-22”,进入时钟准备状态;第一次按电子钟启动/调整键,电子钟从12时59分0秒开始运行,进入时钟运行状态;按电子钟S5键,则电子钟进入时钟调整状态,此时可利用各调整键调整时间,调整结束后可按S5键再次进入时钟运行状态。

1.3 设计课的设计总体方案介绍及工作原理说明本电子钟主要由单片机、键盘、显示接口电路和复位电路构成,设计课题的总体方案如图1所示:图1-1总体设计方案图本电子钟的所有的软件、参数均存放在AT89C52的Flash ROM和内部RAM 中,减少了芯片的使用数量简化了整体电路也降低了整机的工作电流。

键盘采用动态扫描方式。

利用单片机定时器及计数器产生定时效果通过编程形成数字钟效果,再利用数码管动态扫描显示单片机内部处理的数据,同时通过端口读入当前外部控制状态来改变程序的不同状态,实现不同功能。

纯数字电路数字时钟原理图(免费)

做成时钟,并不难,把十进改成6进就行了如下:1,震荡电路的电容用晶震,记时准确.2, 时:用2块计数器,十位的用1和2(记时脚)两个脚.分:用2块计数器,十位的用1,2,3,4,5,6,(记时脚)6个脚.秒:同分.评论:74系列的集成块不如40系列的,如:用CD4069产生震荡,CD4017记数,译码外加.电压5V.比74LS160 74LS112 74LS00好的.而且CD4069外围元件及少.如有需要我可以做给你.首先需要产生1hz的信号,一般采用CD4060对32768hz进行14分频得到2hz,然后再进行一次分频。

(关于此类内容请参考数字电路书中同步计数器一章)(原文件名:4060.JPG)一种分频电路:(原文件名:秒信号1.JPG)采用cd4518进行第二次分频另一种可以采用cd4040进行第二次分频第三种比较麻烦,是对1mhz进行的分频(原文件名:秒信号2.JPG)介绍一下cd4518:CD4518,该IC是一种同步加计数器,在一个封装中含有两个可互换二/十进制计数器,其功能引脚分别为1~7和9~{15}。

该计数器是单路系列脉冲输入(1脚或2脚;9脚或10脚),4路BCD码信号输出(3脚~6脚;{11}脚~{14}脚)。

此外还必须掌握其控制功能,否则无法工作。

手册中给有控制功能的真值(又称功能表),即集成块的使用条件,如表2所示。

从表2看出,CD4518有两个时钟输入端CP和EN,若用时钟上升沿触发,信号由CP输入,此时EN端应接高电平“1”,若用时钟下降沿触发,信号由EN端输入,此时CP端应接低电平“0”,不仅如此,清零(又称复位)端Cr也应保持低电平“0”,只有满足了这些条件时,电路才会处于计数状态,若不满足则IC不工作。

计数时,其电路的输入输出状态如表3所示。

值得注意,因表3输出是二/十进制的BCD码,所以输入端的记数脉冲到第十个时,电路自动复位0000状态(参看连载五)。

另外,该CD4518无进位功能的引脚,但从表3看出,电路在第十个脉冲作用下,会自动复位,同时,第6脚或第{14}脚将输出下降沿的脉冲,利用该脉冲和EN端功能,就可作为计数的电路进位脉冲和进位功能端供多位数显用。

电子设计自动化(EDA)_数字时钟程序模块(LED数码管显示)_实验报告

电子设计自动化(EDA)—数字时钟LED数码管显示二、实验内容和实验目的1. 6个数码管动态扫描显示驱动2. 按键模式选择(时\分\秒)与闹钟(时\分)调整控制,3. 用硬件描述语言(或混合原理图)设计时、分、秒计数器模块、闹钟模块、按键控制状态机模块、动态扫描显示驱动模块、顶层模块。

要求使用实验箱左下角的6个动态数码管(DS6 A~DS1A)显示时、分、秒;要求模式按键和调整按键信号都取自经过防抖处理后的按键跳线插孔。

实验目的: 1)学会看硬件原理图, 2)掌握FPGA硬件开发的基本技能3)培养EDA综合分析、综合设计的能力三、实验步骤、实现方法(或设计思想)及实验结果主要设备: 1)PC机, 2)硬件实验箱, 3)Quartus II软件开发平台。

1.打开Quartus II , 连接实验箱上的相关硬件资源, 如下图1所示。

2.建立新文件, 选择文本类型或原理图类型。

3. 编写程序。

4.编译5. 仿真, 加载程序到芯片, 观察硬件输出结果(数码管显示)6.结果正确则完成。

若结果不正确, 则修改程序, 再编译, 直到正确。

模24计数器模块LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;ENTITY count24 ISPORT(clk,en:IN STD_LOGIC;cout:OUT STD_LOGIC;hh,hl:OUT STD_LOGIC_VECTOR(3 DOWNTO 0));END count24;ARCHITECTURE arc OF count24 ISSIGNAL a,b:STD_LOGIC_VECTOR(3 DOWNTO 0);BEGINPROCESS(clk,en)BEGINhh<=a;hl<=b;IF(clk'EVENT AND clk='1') THENIF(en='1') THENIF(a="0010" AND b="0011") THENa<="0000";b<="0000";ELSE IF(b="1001") THENa<=a+'1';b<="0000";ELSE b<=b+'1';END IF;END IF;IF(a="0010" AND b="0010") THENcout<='1';ELSE cout<='0';END IF;END IF;END IF;END PROCESS;END arc;模60计数器模块LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;ENTITY count60 ISPORT(clk,en:IN STD_LOGIC;cout:OUT STD_LOGIC;hh,hl:OUT STD_LOGIC_VECTOR(3 DOWNTO 0));END count60;ARCHITECTURE arc OF count60 ISSIGNAL a,b:STD_LOGIC_VECTOR(3 DOWNTO 0);SIGNAL sout:STD_LOGIC;BEGINPROCESS(clk)BEGINhh<=a; hl<=b;IF(clk'EVENT AND clk='1') THENIF(en='1') THENIF(a="0101" AND b="1001") THENa<="0000";b<="0000";ELSE IF(b="1001") THENa<=a+'1';b<="0000";ELSE b<=b+'1';END IF;END IF;END IF;END IF;END PROCESS;sout<='1' WHEN a="0101" AND b="1001" ELSE '0';cout<=sout AND en;END arc;4-7显示译码模块LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY segment4to7 ISPORT(s:IN STD_LOGIC_VECTOR(3 DOWNTO 0);a,b,c,d,e,f,g:OUT STD_LOGIC);END segment4to7;ARCHITECTURE arc OF segment4to7 IS SIGNAL y:STD_LOGIC_VECTOR(6 DOWNTO 0); BEGINa<= y(6);b<= y(5);c<= y(4);d<= y(3);e<= y(2); f<= y(1);g<= y(0);PROCESS(s)BEGINCASE s ISWHEN "0000"=>y<="1111110"; WHEN "0001"=>y<="0110000"; WHEN "0010"=>y<="1101101"; WHEN "0011"=>y<="1111001"; WHEN "0100"=>y<="0110011"; WHEN "0101"=>y<="1011011"; WHEN "0110"=>y<="1011111"; WHEN "0111"=>y<="1110000"; WHEN "1000"=>y<="1111111"; WHEN "1001"=>y<="1111011"; WHEN OTHERS=>y<="0000000"; END CASE;END PROCESS;END arc;带闹钟控制模块LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY mode_adjust_with_alarm ISPORT (adjust,mode,clk1hz: IN STD_LOGIC;clkh,enh,clkm,enm,clks,enha: OUT STD_LOGIC;clkh_a,clkm_a:OUT STD_LOGIC;mode_ss: OUT STD_LOGIC_VECTOR(2 DOWNTO 0));END mode_adjust_with_alarm;ARCHITECTURE arc OF mode_adjust_with_alarm ISTYPE mystate IS (s0,s1,s2,s3,s4,s5);SIGNAL c_state,next_state: mystate;BEGINPROCESS (c_state)BEGINCASE c_state ISWHEN s0=> next_state <= s1; clkh<=clk1hz; clkm<=clk1hz; clks<=clk1hz;enh<='0'; enm<='0'; enha<='0'; clkh_a<= '0'; clkm_a<= '0'; mode_ss <="000";WHEN s1=> next_state <= s2; clkh<=adjust; clkm<= '0'; clks<='0';enh<='1'; enm<='0';enha<='0'; clkh_a<= '0';clkm_a<= '0'; mode_ss <="001";WHEN s2=> next_state <= s3; clkh<= '0'; clkm<=adjust; clks <= '0';enh<='0';enm<='1';enha<='0'; clkh_a<= '0'; clkm_a<= '0'; mode_ss <="010";WHEN s3=> next_state <= s4; clkh<= '0'; clkm<= '0'; clks<=adjust;enh<='0'; enm<='0';enha<='0'; clkh_a<= '0'; clkm_a<= '0'; mode_ss <="011";WHEN s4=> next_state <= s5; clkh<= clk1hz; clkm<= clk1hz; clks<=clk1hz;enh<='0';enm<='0';enha<='1'; clkh_a<=adjust; clkm_a<= '0'; mode_ss <="100";WHEN s5=> next_state <= s0; clkh<= clk1hz; clkm<= clk1hz; clks<=clk1hz;enh<='0'; enm<='0'; enha<='0'; clkh_a<= '0'; clkm_a<=adjust; mode_ss <="101";END CASE;END PROCESS;PROCESS (mode)BEGINIF (mode'EVENT AND mode='1') THENc_state<=next_state ;END IF;END PROCESS;END arc;扫描模块LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY scan ISPORT(clk256hz:IN STD_LOGIC;ss:OUT STD_LOGIC_VECTOR(2 DOWNTO 0));END scan;ARCHITECTURE arc OF scan ISTYPE mystate IS (s0, s1,s2,s3,s4,s5);SIGNAL c_state,next_state: mystate;BEGINPROCESS ( c_state )BEGINCASE c_state ISWHEN s0=> next_state <=s1; ss<="010";WHEN s1=> next_state <=s2; ss<="011";WHEN s2=> next_state <=s3; ss<="100";WHEN s3=> next_state <=s4; ss<="101";WHEN s4=> next_state <=s5; ss<="110";WHEN s5=> next_state <=s0; ss<="111";END CASE;END PROCESS;PROCESS (clk256hz)BEGINIF (clk256hz'EVENT AND clk256hz='1') THENc_state<=next_state ;END IF;END PROCESS;END arc;复用模块LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY mux ISPORT(hh,hl,mh,ml,sh,sl,hha,hla,mha,mla:IN STD_LOGIC_VECTOR(3 DOWNTO 0);ss,mode_ss:IN STD_LOGIC_VECTOR(2 DOWNTO 0);y:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);alarm:OUT STD_LOGIC);END mux;ARCHITECTURE arc OF mux ISSIGNAL a,hhtmp,hltmp,mhtmp,mltmp,shtmp,sltmp:STD_LOGIC_VECTOR(3 DOWNTO 0);BEGINPROCESS(mode_ss)BEGINCASE mode_ss ISWHEN "000"=>hhtmp<=hh; hltmp<=hl; mhtmp<=mh; mltmp<=ml; shtmp<=sh; sltmp<=sl;WHEN "001"=>hhtmp<=hh; hltmp<=hl; mhtmp<=mh; mltmp<=ml; shtmp<=sh; sltmp<=sl;WHEN "010"=>hhtmp<=hh; hltmp<=hl; mhtmp<=mh; mltmp<=ml; shtmp<=sh; sltmp<=sl;WHEN "011"=>hhtmp<=hh; hltmp<=hl; mhtmp<=mh; mltmp<=ml; shtmp<=sh; sltmp<=sl;WHEN "100"=> hhtmp<=hha; hltmp<=hla; mhtmp<=mha; mltmp<=mla; shtmp<=sh; sltmp<=sl;WHEN "101"=> hhtmp<=hha; hltmp<=hla; mhtmp<=mha; mltmp<=mla; shtmp<=sh; sltmp<=sl;WHEN OTHERS=>hhtmp<="0000";hltmp<="0000";mhtmp<="0000";mltmp<="0000";shtmp<="0000";sltmp<="0000"; END CASE;END PROCESS;PROCESS(ss)BEGINCASE ss ISWHEN "010"=> a <=hhtmp;WHEN "011"=> a <=hltmp;WHEN "100"=> a <=mhtmp;WHEN "101"=> a <=mltmp;WHEN "110"=> a <=shtmp;WHEN "111"=> a <=sltmp;WHEN OTHERS => a <="0000";END CASE;y<=a;END PROCESS;alarm<='1' WHEN ((hh=hha)AND(hl=hla)AND(mh=mha)AND(ml=mla)) ELSE '0';END arc;闪烁模块LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY blink_control ISPORT(ss,mode_ss:IN STD_LOGIC_VECTOR(2 DOWNTO 0);blink_en:OUT STD_LOGIC);END blink_control;ARCHITECTURE arc OF blink_control ISBEGINPROCESS (ss,mode_ss)BEGINIF(ss="010" AND mode_ss="001") THEN blink_en<='1';ELSIF(ss="011" AND mode_ss="001") THEN blink_en<='1';ELSIF(ss="100" AND mode_ss="010") THEN blink_en<='1';ELSIF(ss="101" AND mode_ss="010") THEN blink_en<='1';ELSIF(ss="110" AND mode_ss="011") THEN blink_en<='1';ELSIF(ss="111" AND mode_ss="011") THEN blink_en<='1';ELSIF(ss="010" AND mode_ss="100") THEN blink_en<='1';ELSIF(ss="011" AND mode_ss="100") THEN blink_en<='1';ELSIF(ss="100" AND mode_ss="101") THEN blink_en<='1';ELSIF(ss="101" AND mode_ss="101") THEN blink_en<='1';ELSE blink_en<='0';END IF;END PROCESS;END arc;Top文件LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY design3 ISPORT (mode,adjust,clk1hz,clk2hz,clk256hz,clk1khz:IN STD_LOGIC;alarm,a,b,c,d,e,f,g:OUT STD_LOGIC;ss:OUT STD_LOGIC_VECTOR(2 DOWNTO 0));END design3;ARCHITECTURE arc OF design3 ISCOMPONENT mode_adjust_with_alarm PORT (adjust,mode,clk1hz: IN STD_LOGIC;clkh,enh,clkm,enm,clks,enha: OUT STD_LOGIC;clkh_a,clkm_a:OUT STD_LOGIC;mode_ss: OUT STD_LOGIC_VECTOR(2 DOWNTO 0));END COMPONENT;COMPONENT scan PORT (clk256hz:IN STD_LOGIC;ss:OUT STD_LOGIC_VECTOR(2 DOWNTO 0));END COMPONENT;COMPONENT segment4to7 PORT (s: IN STD_LOGIC_VECTOR(3 DOWNTO 0);a,b,c,d,e,f,g: OUT STD_LOGIC);END COMPONENT;COMPONENT mux PORT(hh,hl,mh,ml,sh,sl,hha,hla,mha,mla:IN STD_LOGIC_VECTOR(3 DOWNTO 0);ss,mode_ss:IN STD_LOGIC_VECTOR(2 DOWNTO 0);y:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);alarm:OUT STD_LOGIC);END COMPONENT;COMPONENT blink_control PORT(ss,mode_ss:IN STD_LOGIC_VECTOR(2 DOWNTO 0);blink_en:OUT STD_LOGIC);END COMPONENT;COMPONENT count24 PORT (clk,en:IN STD_LOGIC;cout:OUT STD_LOGIC;hh,hl:OUT STD_LOGIC_VECTOR(3 DOWNTO 0));END COMPONENT;COMPONENT count60 PORT (clk ,en:IN STD_LOGIC;cout:OUT STD_LOGIC;hh,hl:OUT STD_LOGIC_VECTOR(3 DOWNTO 0));END COMPONENT;SIGNALclkh,enh,clkm,enm,clks,clkh_a,clkm_a,coutm,couts,coutm_en,couts_en,cout,vcc,coutma_en,coutma,alarm1,bli nk_en,blink_tmp,enha: STD_LOGIC;SIGNAL mode_ss,ss1:STD_LOGIC_VECTOR(2 DOWNTO 0);SIGNAL hh,hl,mh,ml,sh,sl,hha,hla,mha,mla,y,i:STD_LOGIC_VECTOR(3 DOWNTO 0);BEGINvcc<='1';coutm_en <= enh OR coutm;couts_en <= enm OR couts;coutma_en<= enha OR coutma;blink_tmp<=blink_en and clk2hz;i(3)<=y(3) OR blink_tmp;i(2)<=y(2) OR blink_tmp;i(1)<=y(1) OR blink_tmp;i(0)<=y(0) OR blink_tmp;ss<=ss1;alarm<=alarm1 AND clk1khz;u1:mode_adjust_with_alarmPORT MAP( adjust,mode,clk1hz,clkh,enh,clkm,enm,clks,enha,clkh_a,clkm_a,mode_ss);u2:count24 PORT MAP(clkh,coutm_en,cout,hh,hl);u3:count60 PORT MAP(clkm,couts_en,coutm,mh,ml);u4:count60 PORT MAP(clks,vcc,couts,sh,sl);u5:count24 PORT MAP(clkh_a,coutma_en,cout,hha,hla);u6:count60 PORT MAP(clkm_a,vcc,coutma,mha,mla);u7:mux PORT MAP(hh,hl,mh,ml,sh,sl,hha,hla,mha,mla,ss1,mode_ss,y,alarm1);u8:scan PORT MAP(clk256hz,ss1);u9:blink_control PORT MAP(ss1,mode_ss,blink_en);u10:segment4to7 PORT MAP(i,a,b,c,d,e,f,g);END arc;实验结果:数字钟包括正常的时分秒计时, 实验箱左下角的6个动态数码管(DS6 A~DS1A)显示时、分、秒。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

send(0x0500+(m%10));

*PEDATDIR=0xFF04;delay(1000);*PEDATDIR=0xFF00;}}

if((*PFDATDIR & 0X0004)==0) //按下KEY2,则分钟减

{*T1CON &= ~0x0040;//停止定时器1

{

*PBDATDIR=0xFF00; //IOPB(MAX7219的LOAD引脚)输出低电平

*SPITXBUF=data; //发送一个字符

while((*SPISTS&0x40)!=0x40); //循环,直到SPI有中断,说明发送完毕

data = *SPIRXBUF; //空读SPIRXBUF,以清除SPI中断标志

{*T1CON &= ~0x0040;}//停止定时器1

if((*PFDATDIR & 0X0008)==0) //若按下KEY3,则复位时钟

{*T1CON &= ~0x0040;//停止定时器1

for(n=0;n<8;n++) //显示全0

{send(d[n]);}

k=0;s=30;m=59;h=23 ;}

enable();//允许全局中断

//设置MAX7219到需要的工作状态

send(0x0C01);//关闭Shutdown模式,正常操作

send(0x09FF);//全部8个数字都采用解码模式

send(0x0A08);//亮度17/32

send(0x0B07);//扫描全部8个数码管

send(0x0F00);//关闭测试模式

if((*PFDATDIR & 0X0010)==0) //若按下KEY4

{ *T1CON &= ~0x0040;j++;}

}

while(j==2)

{

if((*PFDATDIR & 0X00010)==0) //若按下KEY4,则继续开启时钟

{*T1CON |= 0x0040;

j=1;k=0;s=s;m=m;h=h;}

*PBDATDIR=0xFF08; //IOPB.3=LOAD = 1,上升沿锁存

}

//INT2中断服务程序

void interrupt GISR2()

{

unsigned int i;

switch(*PIVR)

{

case 0x0027://是定时器1周期中断

*EVAIFRA=*EVAIFRA|0x0080;//清除定时器1周期中断标志k += 1;

}

}

}

{m--;if(m==-1){m=59; h-=1;};

if(h==-1){h=23; };

send(0x0100+(h/10));

send(0x0200+(h%10));

send(0x0400+(m/10));

send(0x0500+(m%10));

*PBDATDIR=0xFF04;delay(1000);*PBDATDIR=0xFF00;}}

void interrupt nothing()

{enable(); return; //允许总中断然后中断返回,因一进入ISR后,总中断就被自动关闭了

}

//主程序

void main(void)

{

unsigned int n;

disable();//关闭全局中断

chushihua();//初始化

dingshi();//初始化定时器1

if((*PFDATDIR & 0X0002)==0) //按下KEY1,则分钟加

{*T1CON &= ~0x0040;//停止定时器1

{m++;if(m>59){m-=60; h+=1;};

if(h>23){h-=24; };

send(0x0100+(h/10));

send(0x0200+(h%10));

*T1PER=0x0270; //(0x0270+1)*64/40 us =1ms

*T1CNT=0; //赋定时器初值

*EVAIFRA=*EVAIFRA; //清除可能存在的定时器1周期中断标志*EVAIMRA=*EVAIMRA|0x0080; //允许定时器1周期中断

}

//用SPI发送一个字符

void send(unsigned int data)

WSGR=0x00; //禁止所有的等待状态

}

//延时子程序

void delay(unsigned int pp)

{

unsigned int k,i;

for(k=0;k<pp;k++)

{

for(i=0;i<3997;i++);//延时1ms}Βιβλιοθήκη }//定时1初始化

void dingshi()

{

*T1CON=0x160C; //停止运行、连续增计数模式

unsigned int d[8] = {0x0100,0x0200,0x030a,0x0400,0x0500,0x060a,0x0700,0x0800};

unsigned int w[8] = {0x0101,0x0204,0x030a,0x0400,0x0503,0x060a,0x0700,0x0804};

#include "2407c.h"//数字电子时钟按Key1启动、Key2暂停、Key3复位、Key4调时

#define disable() asm(" setc INTM")//禁止全局中断

#define enable() asm(" clrc INTM")//允许全局中断

unsigned int k=0,s=30,m=59,h=23,j=1;

send(d[3]+(m/10));

send(d[4]+(m%10));

send(d[6]+(s/10));

send(d[7]+(s%10));

break;

default:

break;

}

enable();//允许总中断,因一进入ISR后,总中断就被自动关闭了

return; //中断返回

}

//其他中断

if(k>999){k-=1000; s+=1;}//超过999ms,需要进位

if(s>59){s-=60; m+=1;}//超过59s,需要进位

if(m>59){m-=60; h+=1;}//超过59m,需要进位

if(h>23){h-=24; }

send(d[0]+h/10);

send(d[1]+(h%10));

//系统初始化子程序

void chushihua (void)

{

asm (" clrc SXM"); //抑制符号位扩展

asm (" clrc OVM"); //累加器正常溢出

asm (" clrc CNF");//B0被配置为数据存储空间

*WDCR=0x00E8; //关闭看门狗

*SCSR1=0X00FC; //CLKIN=10M,CLKOUT=CLK*4=40M

for(n=0;n<8;n++)//显示全0

{send(d[n]);}

while(1)

{

while(j==1)

{

if((*PFDATDIR & 0X0002)==0) //若按下KEY1,则启动定时器1

{*T1CON |= 0x0040;}//启动定时器1

if((*PFDATDIR & 0X0004)==0) //若按下KEY2,则暂停定时器1

*SPICCR=0x0F; //SPI软复位、上升沿输出数据、16位数据长度

*SPICTL=0x0E; //禁止过冲中断、允许TALK(发送)数据、主机模式、禁止SPI中断

//上升沿有延时

*SPIBRR=0x0F; //SPI波特率=SYSCLK/(SPIBRR+1)=2.5M

*SPICCR=*SPICCR|0x80; //SPI恢复操作,准备发送、接收下一个字符

*IMR=0x0002; //开INT2

*IFR=0xFFFF; //清全部中断,写1清0,参见P43

*MCRB=0xFE3C; //启用SPI功能引脚

*MCRA=0; //IOPA、IOPB配置为一般I/O功能

*MCRC=0; //IOPE、IOPF配置为一般I/O功能

*PFDATDIR=0x00FF; //IOPF设置为输入,并上拉