EDA技术实践课程设计--24进制计数器课件

EDA 24进制计数器的设计

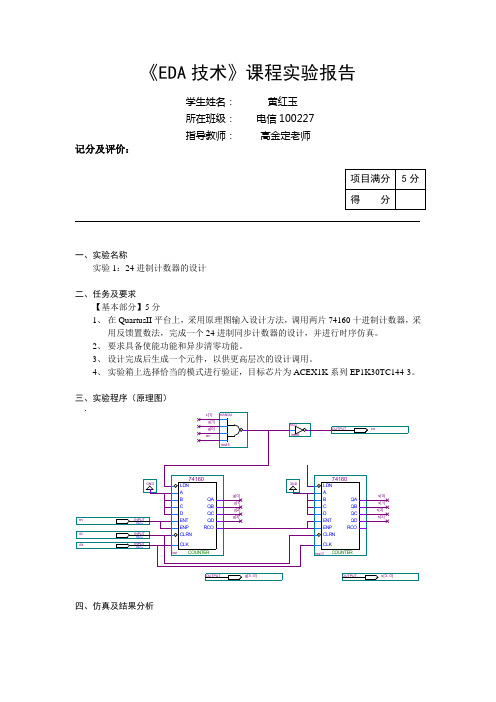

《EDA技术》课程实验报告学生姓名:黄红玉所在班级:电信100227指导教师:高金定老师记分及评价:一、实验名称实验1:24进制计数器的设计二、任务及要求【基本部分】5分1、在QuartusII平台上,采用原理图输入设计方法,调用两片74160十进制计数器,采用反馈置数法,完成一个24进制同步计数器的设计,并进行时序仿真。

2、要求具备使能功能和异步清零功能。

3、设计完成后生成一个元件,以供更高层次的设计调用。

4、实验箱上选择恰当的模式进行验证,目标芯片为ACEX1K系列EP1K30TC144-3。

三、实验程序(原理图)四、仿真及结果分析在QuartusII平台上,采用原理图输入设计方法,调用两片74160十进制计数器,采用反馈置数法,设计一个24进制同步计数器的思路是,一片74160计数器作为个位计数,一片用来十位计数,要实现同步24进制,则个位接成0011,十位接成0010,再用一个四输入(一段接一个使能信号EN)的与非门接到两片74160计数器上的置数端LDN。

把原理图在QuartusII上画成后,进行编译,编译无误后,在新建一个波形文件,添加所有引脚,设置输入引脚的波形,最后在进行波形编译,无误后即可达到想要的24进制。

然后再根据EPF10K30E144芯片引脚对照,输入各个输入输出引脚的引脚号,再链接到试验箱检验,观察数码管的显示结果。

五、硬件验证1、选择模式:模式72、引脚锁定情况表:六、小结经过这次的实验工作,让我知道了许多的东西,也对QuartusII这个软件的一个初步认识及应用,也让我了解了许多在书本上所学不到的知识和技能,这为我们在以后的工作起了非常重要的作用。

EDA技术24进制计数器

《EDA技术》课程实验报告

学生姓名:郑月庭

所在班级:电信1001班

指导教师:高金定老师

记分及评价:

一、实验名称

实验1:24进制计数器的设计

二、任务及要求

【基本部分】5分

1、在QuartusII平台上,采用原理图输入设计方法,调用两片74160十进制计数器,采

用反馈置数法,完成一个24进制同步计数器的设计,并进行时序仿真。

2、要求具备使能功能和异步清零功能。

3、设计完成后生成一个元件,以供更高层次的设计调用。

4、实验箱上选择恰当的模式进行验证,目标芯片为ACEX1K系列EP1K30TC144-3。

三、实验程序(原理图)

四、仿真及结果分析

五、硬件验证

1、选择模式:

模式7

2、引脚锁定情况表:

六、小结

初次接触EDA让自己学到了很多的知识,实验中让自己的思维更加的开阔,对这门课程有了一定的了解,也很感兴趣。

总之的收获了不少的知识。

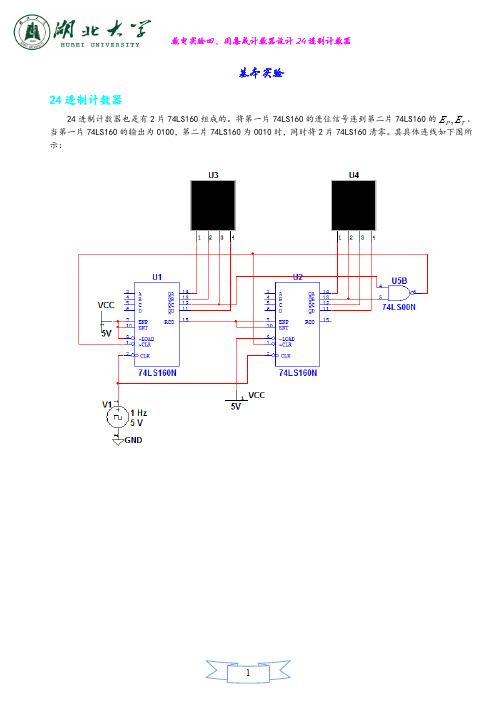

湖北大学 数电实验四、用集成计数器设计24进制计数器

24进制计数器

24进制计数器也是有2片74LS160组成的。

将第一片74LS160的进位信号连到第二片74LS160的。

当第一片74LS160的输出为0100,第二片74LS160为0010时,同时将2片74LS160清零。

其具体连线如下图所

示:

T P E E ,

数字时钟的设计

数字时钟由时、分、秒组成。

进制有60进制、24进制。

60进制计数器设计

60进制计数器由两片74LS160十进制计数器经过一定的方式连接组成。

将第一片74LS160的进位信号连到接到第二片74LS160的,当第二片74LS160的输出为0110时,同时将两片74LS160同时清零。

其具体

连接方式如下:

24进制计数器

24进制计数器也是有2片74LS160组成的。

将第一片74LS160的进位信号连到第二片74LS160的。

当第一片74LS160的输出为0100,第二片74LS160为0010时,同时将2片74LS160清零。

其具体连线如下图所

示:

T P E E , T P E E ,

综合以上设计出数字时钟的电路图如下:。

eda的计数器课程设计

eda的计数器课程设计一、课程目标知识目标:1. 学生能理解EDA(电子设计自动化)的基本概念,掌握计数器的设计原理。

2. 学生能描述不同类型的计数器,并了解它们在实际应用中的区别。

3. 学生能运用所学知识,分析并设计简单的计数器电路。

技能目标:1. 学生能够运用EDA工具进行计数器电路的绘制、仿真和调试。

2. 学生能够通过小组合作,解决设计过程中遇到的问题,提高团队协作能力。

3. 学生能够运用所学知识,独立完成计数器电路的设计与验证。

情感态度价值观目标:1. 学生对电子设计产生兴趣,培养探究精神和创新意识。

2. 学生在小组合作中,学会倾听、尊重他人意见,培养良好的沟通能力和团队精神。

3. 学生能够认识到科技发展对社会进步的重要性,增强社会责任感和使命感。

课程性质:本课程为电子信息科学与技术专业的实践课程,旨在让学生通过实际操作,掌握计数器的设计原理和EDA工具的使用。

学生特点:学生已具备一定的电子基础知识和EDA软件操作能力,具有较强的动手能力和探究欲望。

教学要求:结合学生特点和课程性质,注重理论与实践相结合,强调动手实践和团队合作,提高学生的实际操作能力和创新能力。

通过本课程的学习,使学生能够达到上述课程目标,为后续课程和实际工作打下坚实基础。

二、教学内容本课程教学内容主要包括以下几部分:1. 计数器原理与分类- 计数器的基本概念、功能和分类- 不同类型计数器(同步、异步、Johnson等)的工作原理及应用2. EDA工具使用- 介绍EDA软件的基本操作和功能- 计数器电路的绘制、仿真与调试方法3. 计数器设计实践- 设计简单的同步计数器电路- 设计简单的异步计数器电路- 设计简单的Johnson计数器电路4. 小组讨论与总结- 分析设计过程中遇到的问题及解决方法- 各小组展示设计成果,分享经验和心得教学内容安排与进度:第1周:计数器原理与分类学习,了解EDA工具的基本操作第2周:设计简单的同步计数器电路,进行仿真与调试第3周:设计简单的异步计数器电路,进行仿真与调试第4周:设计简单的Johnson计数器电路,进行仿真与调试第5周:小组讨论与总结,展示设计成果教材章节与内容:第1章 计数器原理与分类第2章 EDA工具使用第3章 计数器设计实践第4章 小组讨论与总结三、教学方法本课程采用以下多样化的教学方法,以激发学生的学习兴趣和主动性:1. 讲授法:教师通过讲解计数器原理、分类及EDA工具的使用方法,为学生奠定理论基础。

eda计数器的课程设计

eda计数器的课程设计一、课程目标知识目标:1. 让学生理解EDA(电子设计自动化)计数器的基本原理和功能;2. 使学生掌握计数器的种类、工作方式及应用场景;3. 帮助学生掌握使用EDA工具进行计数器设计的方法。

技能目标:1. 培养学生运用EDA工具设计简单计数器的能力;2. 培养学生分析计数器电路、调试和优化电路的技能;3. 提高学生团队协作和沟通表达的能力。

情感态度价值观目标:1. 培养学生对EDA技术及电子设计的兴趣和热情;2. 培养学生严谨、细致、勇于探索的科学态度;3. 增强学生的国家认同感和自豪感,认识到我国在EDA技术领域的发展。

课程性质分析:本课程为电子技术专业课程,以实践为主,理论联系实际。

结合学生特点和教学要求,注重培养学生的实际操作能力和团队合作精神。

学生特点分析:学生为高中生,具有一定的电子技术基础和动手能力,对新鲜事物充满好奇心,喜欢探索和实践。

教学要求:1. 理论与实践相结合,注重培养学生的实际操作能力;2. 激发学生的创新意识,提高学生的设计能力;3. 引导学生关注我国EDA技术领域的发展,培养学生的国家认同感。

二、教学内容1. 计数器原理:讲解计数器的基本概念、分类(同步、异步计数器)、工作原理和功能;教材章节:第二章第二节《计数器的基本概念与分类》2. EDA工具使用:介绍常见的EDA工具(如Multisim、Proteus等),学习如何使用这些工具进行计数器设计;教材章节:第三章第一节《电子设计自动化工具介绍》3. 计数器设计:分析简单计数器电路原理,学习使用EDA工具进行设计,包括电路图绘制、仿真测试等;教材章节:第三章第三节《计数器的设计与仿真》4. 电路调试与优化:学习如何对计数器电路进行调试、优化,提高电路性能;教材章节:第四章第二节《电路调试与优化方法》5. 实践操作:分组进行计数器设计实践,培养团队协作能力和实际操作技能;教材章节:第五章《实践操作》6. 总结与拓展:总结计数器设计与实践过程中的经验教训,探讨计数器在其他领域的应用;教材章节:第六章《课程总结与拓展》教学内容安排与进度:1. 计数器原理(1课时)2. EDA工具使用(1课时)3. 计数器设计(2课时)4. 电路调试与优化(1课时)5. 实践操作(3课时)6. 总结与拓展(1课时)总计8课时,确保学生在掌握理论知识的基础上,充分进行实践操作,提高综合运用能力。

24进制计数器课程设计

24进制计数器课程设计一、课程目标知识目标:1. 学生能理解24进制计数原理,掌握24进制与十进制的转换方法;2. 学生能运用24进制进行简单数学运算,如加、减、乘、除;3. 学生了解24进制在实际应用中的优势,例如在时间计算、编码等领域。

技能目标:1. 学生能够独立完成24进制与十进制的相互转换;2. 学生能够运用24进制进行基本的数学运算,解决实际问题;3. 学生通过小组合作,设计并制作一个简单的24进制计数器。

情感态度价值观目标:1. 学生培养对进制转换的兴趣,提高学习数学的积极性;2. 学生养成合作、探究的学习习惯,增强团队协作能力;3. 学生认识到数学在生活中的广泛应用,提高数学素养。

课程性质:本课程属于数学课程,旨在让学生掌握进制转换知识,提高数学应用能力。

学生特点:六年级学生具备一定的数学基础,思维活跃,好奇心强,喜欢探究新知识。

教学要求:注重理论与实践相结合,鼓励学生动手实践,培养实际操作能力;强调小组合作,培养学生的团队协作精神。

通过本课程的学习,使学生能够将所学知识应用于实际生活中,提高解决问题的能力。

二、教学内容1. 24进制计数原理介绍:通过课本知识,讲解24进制的定义,对比十进制,让学生理解进制的概念和转换方法。

- 章节关联:《数学》六年级上册,第三章“数的认识”,第二节“认识进制”。

2. 24进制与十进制的转换:详细讲解转换方法,举例说明,让学生掌握两种进制之间的转换技巧。

- 教学安排:2课时。

3. 24进制数学运算:讲解24进制下的加、减、乘、除运算规则,让学生学会运用24进制进行计算。

- 教学安排:2课时。

4. 实际应用案例分析:分析24进制在实际生活中的应用,如时间计算、编码等,提高学生的实际应用能力。

- 章节关联:《数学》六年级上册,第三章“数的认识”,第四节“进制在实际生活中的应用”。

5. 小组合作制作24进制计数器:分组让学生设计并制作计数器,巩固所学知识,培养学生的动手能力和团队协作精神。

EDA二 4位加法计数器设计

6)可调时钟输出单元底板上ADJ_CLK为4位拨码开关SW17--SW20来控制输出40M分频后的可调时钟具体对应如下SW20 SW19 SW18 SW17 ADJ_CLK1 1 1 1 1Hz0 1 1 1 5Hz1 0 1 1 10Hz0 0 1 1 25Hz1 1 0 1 50Hz0 1 0 1 500Hz1 0 0 1 1KHz0 0 0 1 2.5KHz1 1 1 0 10KHz0 1 1 0 20KHz1 0 1 0 50KHz0 0 1 0 200KHz1 1 0 0 500KHz0 1 0 0 2MHz1 0 0 0 5MHz0 0 0 0 20MHzCLK1 10MHz固定时钟(40MHz分频产生)CLK2 1MHzCLK3 100KHzCLK4 5KHzCLK5 100Hz实验四 4位加法计数器设计一、实验目的学习时序逻辑电路的设计、仿真和硬件测试;加深理解VHDL设计技术。

二、实验原理图4-4-1是一含计数使能、异步复位和计数值并行预置功能的4位加法计数器,其VHDL描述参见例4-4-1。

由图4-4-1所示,图中间是4位锁存器(即D触发器);RST是异步清零信号,高电平有效;CLK是锁存信号;D[3..0]是4位数据输入端;PST是同步并行预置信号,高电平有效,置数值为Data[3:0];Outy[3:0]是计数值输出;Cout是计数溢出信号。

① RST为异步清零信号,高电平有效,一旦RST=1,4位锁存器输出状态复位为“0000”;② ENA为同步计数使能信号,当CLK为上升沿时z当ENA=“1”时,加法计数,CQI= CQI+1;z当ENA=“0”时,保持原数,CQI= CQI;③ PST为同步并行预置信号,当CLK为上升沿时图4-4-1含计数使能、异步复位和计数值并行预置功能的4位加法计数器三、实验内容(1)对例4-4-1含计数使能、异步复位和计数值并行预置功能的4位加法计数器的VHDL设计,说明例中各语句的作用,并详细描述示例的功能特点。

eda24进制计数器设计

EDA24进制计数器设计1. 任务背景计数器是计算机系统中常见的一种电路,用来实现对数字进行计数的功能。

传统的计数器一般是采用二进制表示数字,然而在某些特定的应用场景中,使用其他进制的计数器能够更方便和高效。

EDA24进制计数器是指使用24进制来表示数字的计数器。

24进制是一种特殊的进制,它由24个数字符号(0-23)组成,分别对应于十进制的0-9、字母A-J、字母K-T和字母U-Y。

使用24进制计数器可以更精确地表示某些特定范围内的数字,而且减少了数字的位数和转换过程中的计算复杂度。

本文将介绍如何设计一个EDA24进制计数器,包括计数器的原理、硬件设计和功能实现等方面的内容。

2. 原理介绍EDA24进制计数器的工作原理与传统的计数器类似,主要分为三个部分:计数器状态存储、计数器状态更新和计数器输出。

2.1 计数器状态存储EDA24进制计数器需要使用存储器来保存当前的计数器状态。

由于EDA24进制有24个数字符号,每个符号对应一个存储单元,因此需要一个24位的存储器来存储计数器的状态。

存储器的结构可以采用RAM或者寄存器等形式。

当计数器进行更新时,计数器状态存储器会读取新的计数器状态。

2.2 计数器状态更新EDA24进制计数器的计数逻辑与二进制计数器类似,但需要对进位的处理进行特殊处理。

在24进制下,当某一位达到23时,需要进行进位操作,并将低位的符号进行进位。

例如,当计数器达到23时,进位得到的数字为10(对应K),并将低位的数字进行滚动。

以一个4位的EDA24进制计数器为例,计数范围为0000~2323。

初始状态为0000,当计数值增加时,每一位的变化规律如下:•当个位(最低位)从0~2变化时,直接递增;•当个位达到3时,个位变为0,十位(倒数第二位)递增;•当十位从0~2变化时,直接递增;•当十位达到3时,十位变为0,百位(倒数第三位)递增;•当百位从0~2变化时,直接递增;•当百位达到3时,百位变为0,千位(最高位)递增;•当千位从0~2变化时,直接递增;•当千位达到3时,计数器归零。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

图 4.7 74ls161 完成品

7

EDA 技术实践课程设计 (报告)

4.3 普通元件的添加

双击原理图的任一空白处,会弹出一个元件对话框。在

Name 栏目中输入

,

打开新建设计文件对话框,如下图。选择【 Block Diagram/Schematic File】,点击

OK ,即进入原理图编辑界面。

4

EDA 技术实践课程设计 (报告)

图

图 4.1 新建工程项目

图 4.2 新建设计文件

4.2 宏功能模块的使用

双 击 原 理 图 编 辑 窗 口 , 在 弹 出 的 元 件 选 择 窗 口 的 “ Libraries”栏 中 选 择 “ arithmetic”中的 lpm_counter 元件,如下图所示 ,

( 5)进位输出 C

当计数控制端 T=1,且触发器全为 1 时,进位输出为 1,否则为 0。

4 设计过程

4.1 新文件的建立

建立新项目工程,方法如右图点击: 【File】菜单,选择下拉列表中的【 New

Project Wizard...】命令,打开建立新项目工程的向导对话框。

从 File 菜单中选择【New… 】命令,或直接点击常用工具栏的第一个按钮

4

4.1 新文件的建立 .......................................................

4

4.2 宏功能模块的使用 ..................................................

5

4.3 普通元件的添加 ....................................................

13

EDA 技术实践课程设计 (报告)

1 设计

设计一个二十四进制计数器,计数状态从 0~23,要求有译码显示。

2 方案选择与电路原理图的设计

2.1 24 进制计数器的基本原理

用两个 74ls161 为主,其中一个为输出结果的低四位, 另一个为输出结果的高 4 位,低四位从 0000 到 1001(即十进制的九)然后置 0000 并且高四位加 1,如 此到高四位为 0010,第四位为 0011,这时计数到 23,进位信号输出 1,同时 8 位 输出同时置 0;

图 4.5 参数界面 2

6

EDA 技术实践课程设计 (报告)

弹出定制 lpm_counter 元件对话框 5。可为计数器添加同步或者异步输入控制 端口,如“ Clear(清除)”、“Load(加载)”和“ Set(设置)”。如果不要添加这些 端口,直接单击“ Next>”按钮即可。

图 4.6 参数界面 3

and2 ,我们就得到一个 2 输入的与门。

点击 OK 按钮,将其放到原理图的适当位置。重复操作,放入另外两个 2 输

入与门。也可以通过右键菜单的 Copy 命令复制得到。

图 4.8 普通元件的添加

双击原理图的空白处,打开元件对话框。在 Name 栏目中输入 Input , 我们 便得到一个输入引脚。点击 OK 按钮,放入原理图。同理,在 Name 栏目中输入 output ,我们会得到一个输出引脚。

2.2 设计流程图

开始

查找资料

选定计数器总结仿真与来自试图 2.1 设计流程图

2.3 原理图

由采用两个 74ls161 和一个与非门构成的最基本的 24 进制计数器。

1

EDA 技术实践课程设计 (报告)

图 2.2 24 进制计数器原理图

3 74LS161 元件说明 3.1 简介

74LS161 是常用的四位二进制可预置的同步加法计数器, 它可以灵活地运用在 各种数字电路,以及单片机系统种实现分频器等很多重要的功能

图 4.3 新增宏模块

对 lpm_counter 元件的各种参数进行选择, 定制适合设计需要的模块, NEXT 。 在“How wide should the ‘q’ output b”us此b处e?输入“ 4”位 ; 并选择“Up only”( 为 双边沿有效 ), NEXT 。

5

EDA 技术实践课程设计 (报告)

图 4.9 输入引脚的添加

8

EDA 技术实践课程设计 (报告)

4.4 电路连接

把所用的元件都放好之后,开始连接电路。将鼠标指到元件的引脚上,鼠标会 变成 “十 ”字形状。按下左键, 拖动鼠标,就会有导线引出。 根据我们要实现的逻辑, 连好各元件的引脚。

图 4.10 完成品

5 功能仿真

在【File】菜单下, 点击【New】命令。在随后弹出的对话框中, 切换到【 Other Files】页。选中【 Vector Waveform File】选项,点击 OK 按钮。

( 3)保持功能

在 CR=LD =1 的条件下,当 T*P = 0 时,不管有无 CP 脉冲作用,计数器都将 保持原有状态不变(停止计数) 。

( 4)同步二进制计数功能

当 CR= LD = P= T=1 时, 74LS161 处于计数状态,电路从 0000 状态开始, 连续输入 16 个计数脉冲后, 电路 将从 1111 状态返回到 0000 状态,状态表见表 2。

3.4 74ls161 主要特点

( 1)异步清零功能

3

EDA 技术实践课程设计 (报告)

当 CR= 0 时,不管其他输人端的状态如何(包括时钟信号 的输出全为零。

CP), 4 个触发器

( 2)同步并行预置数功能

在 CR= 1 的条件下,当 LD =0 且有时钟脉冲 CP的上升沿作用时, D3,D2, D1,D0 输入端的数据将分别被 Q3~Q0 所接收。由于置数操作必须有 CP 脉冲上 升沿相配合,故称为同步置数。

1 1X 0XXXXX

保持

1 1 1 1 ↑X X X X

计数

从 74LS161 功能表功能表中可以知道,当清零端 CR=“0”,计数器输出 Q3、 Q2、Q1、Q0 立即为全“ 0”,这个时候为异步复位功能。 当 CR=“ 1”且 LD=“ 0”时, 在 CP 信号上升沿作用后, 74LS161 输出端 Q3、Q2、Q1、Q0 的状态分别与并行 数据输入端 D3 , D2 , D1 , D0 的状态一 样,为同步 置 数功能 。而只有当 CR=LD=EP=ET“= 1”、CP 脉冲上升沿作用后, 计数器加 1。74LS161 还有一个进位 输出端 CO,其逻辑关系是 CO= Q0·Q1·Q2·Q3·CET。合理应用计数器的清零功能 和置数功能,一片 74LS161 可以组成 16 进制以下的任意进制分频器。

基本要求: 1. 熟悉仿真开发软件 Quartus II 的使用; 2. 根据功能要求,用原理图或文本输入方式完成设计; 3. 用 Quartus II 做波形仿真调试; 4. 下载至 EDA 试验仪调试设计。

主要参考资料: [1] 潘松,黄继业 . 《 EDA 技术实用教程》[ M ] . 北京:科学出版社, 2002. [2] 卢杰,赖毅 . 《VHDL 与数字电路设计》[ M ] . 北京:科学出版社, 2001. [3] 张明 . 《 Verilog HDL 实用教程》[ M ]. 成都:电子科技大学出版社, 1999. [4] 郑家龙,王小海,章安元 . 《集成电子技术基础教程》[ M ] . 北京:高等教育出版 社, 2002. [5] 王金明,杨吉斌 . 《数字系统设计与 Verilog HDL 》[ M ] . 北京:电子工业出版社, 2002.

东北石油大学

EDA 技术实践课程设计

课程 题目 院系 专业班级 学生姓名 学生学号 指导教师

EDA 技术实践课程设计 24 进制计数器

电气信息工程学院电气系

年 7 月 25 日

EDA 技术实践课程设计任务书

课程

EDA 技术实践课程设计

题目

24 进制计数器

专业 电气工程及其自动化 姓名

学号

主要内容: 1.熟练掌握 Quartus II 软件的使用。 2.熟练掌握在 QuartusII 平台上用原理图或者 VHDL 语言进行电路设计的方法。 3.学会用例化语句对 EDA 电路设计中顶层电路进行描述。

2

3.3 74ls161 功能表 .....................................................

3

3.4 74ls161 主要特点 ...................................................

3

4 设计过程 ..............................................................

1

3 74LS161 元件说明 ......................................................

2

3.1 简介 ..............................................................

2

3.2 74ls161 管脚图与介绍 ...............................................

3.2 74ls161 管脚图与介绍

管脚图介绍: 时钟 CP 和四个数据输入端 P0~P3 清零 /MR 使能 CEP, CET 置数 PE 数据输出端 Q0~Q3 以及进位输出 TC. (TC=Q0·Q1·Q2·Q3·CET)

2

EDA 技术实践课程设计 (报告)

图 3.1 74ls161 管脚图

8

4.4 电路连接 ..........................................................