基于74LS192的任意进制计数器的设计

任意进制计数器的设计

任意进制计数器的设计【摘要】计数器集成芯片一般有4位二进制、8位二进制或十进制计数器,而在实际应用中,往往需要设计一个任意n进制计数器,本文给出它的设计方法和案例。

【关键词】计数器;清零一、利用反馈清零法获得计数器1 集成计数器清零方式异步清零方式:与计数脉冲cp无关,只要异步清零端出现清零信号,计数器立即被清零。

此类计数器有同步十进制加法计数器ct74ls160、同步4位二进制加法计数器ct74ls161、同步十进制加/减计数器ct74ls192、同步4位二进制加/减计数器ct74ls193等。

同步清零方式:与计数脉冲cp有关,同步清零端获得清零信号后,计数器并不立刻被清零,只是为清零创造条件,还需要再输入一个计数脉冲cp,计数器才被清零。

属于此类计数器有同步十进制加法计数器ct74ls162、同步4位二进制加法计数器ct74ls163、同步十进制加/减计数器ct74ls190、同步4位二进制加/减计数器ct74ls191等。

2 反馈清零法对于异步清零方式:应在输入第n个计数脉冲cp后,利用计数器状态sn进行译码产生清零信号加到异步清零端上,立刻使计数器清零,即实现了n计数器。

在计数器的有效循环中不包括状态sn,所以状态sn只在极短的瞬间出现称为过渡状态。

对于同步清零方式:应在输入第n-1个计数脉冲cp后,利用计数器状态sn-1进行译码产生清零信号,在输入第n个计数脉冲cp 时,计数器才被清零,回到初始零状态,从而实现n计数器。

可见同步清零没有过渡状态。

利用计数器的清零功能构成n计数器时,并行数据输入端可接任意数据,其方法如下:①写出n计数器状态的二进制代码。

异步清零方式利用状态sn,同步清零方式利用状态sn-1。

②写出反馈清零函数。

③画逻辑图。

例1 试用ct74ls160的异步清零功能构成六进制计数器。

解:①写出sn的二进制代码。

sn=s6=0110②写出反馈清零函数。

③画逻辑图。

如图1所示。

74ls192引脚图

74LS192引脚图引言在数字电子技术中,集成电路(IC)扮演着至关重要的角色。

它们通过集成了许多电子元件来实现各种电子功能。

其中,74LS192是一款常用的集成电路,广泛应用于数码逻辑设计中。

本文档将介绍74LS192集成电路的引脚图及其功能。

74LS192简介74LS192是一款四位可编程二进制同步计数器,它可以在特定时钟脉冲的控制下进行计数。

具体来说,它可以以二进制(BCD)或二进制(Binary)模式计数。

该芯片还具有清零、预设、加载和递增/递减计数的能力。

通过正确配置其引脚连接,我们可以实现各种计数需求。

74LS192引脚图下面是74LS192集成电路的引脚图:Vcc ─┐│┌────────┐ ┌────────┐ ┌────────┐ ┌─┴─┐│ CP │ │ MR │ │ PL │ │ PE ││ (6) │ │ (7) │ │ (8) │ │ (10)│└──┬─────┘ └──┬─────┘ └──┬─────┘ └──┬──┘│ │ │ ││ │ │ │┌─┴─┐ ┌─┴─┐ ┌─┴─┐ ▼ ▲│ D │ │ C │ │ B │ ▼ ▲│ (5) │ │ (4) │ │ (3) │ │ │└───┬┘ └───┬┘ └───┬─┘ ┌───┘ └───┐│ BI/RBO │ BCD1 │ │ BCD0 ││ (9) │ (14) │ │ (13) ││ │ │ │ │┌───┴─┐ ┌─┴─┐ ┌─┴─┐ ┌─┴─┐ ┌─┴─┐│ G │ │ F │ │ E │ │ D │ │ C ││ (16) │ │ (15) │ │ (1) │ │ (2) │ │ (12)│└─┬───┘ └─┬───┘ └─┬─┘ └───┬─┘ └───┬─┘│ Vdd │ CARRY/BORROW │ LATCH CLOCK└───────────────┴──────────────┴───────────┘ CLOCK上述引脚图基于74LS192的DIP(双行直插式)封装。

采用74LS192设计的4、7进制计数器

采用74LS192设计的4、7进制计数器《电子设计基础》课程报告设计题目:4/7进制计数器设计学生班级:通信0902学生学号:20095972学生姓名:指导教师:时间:2011. 6.24西南科技大学信息工程学院四、74283加法器每一位的进位信号送给高位作为输入信号,因此,任一位的加法运算必须在低一位的运算完成之后才能进行,这种进位方式成为串行进位,这种加法器的逻辑电路较为简单。

74283管脚图74283原理图一.电路设计及计算1.选择一个方波信号发生器作为输入信号源;CP2利用74LS192,通过清零法设计一个四进制计数器,状态图如下:0000 000101000011 00103、利用74S192通过置数法设计一个从1到7的计数器,状态图如下:0010 0011 0111 0110 0101 0100然后通过减法器在每一个状态的基础上减去一个1,从而实现一个7进制计数器。

减法器电路如图所示U774283NSUM_410SUM_313SUM_14SUM_21C49B411A412B315A314B22A23B16A15C07U8A74LS136D U9B 74LS136DU10C74LS136D U11D74LS136D GNDVCC 5V4、通过一个单刀双掷开关控制信号源,从而进行四进制和七进制之间的转换。

接4进制计数器接7进制计数器接地5、进行四进制计数时,在74LS192后面接一个7447显示译码管,将8421BCD 码转换成十进制,最后通过一个七段显示数码管来显示数据输出状态。

6、在进行七进制计数时,用40192进行置数法计数,预置数为0001,计数到1000后反馈到置数端,循环计数,后面接一个74238加法器构成的减法器,使输出显示数字在0000~0110之间计数,在经过7447译码管将其转化为十进制数0~6,从而实现七进制计数器功能。

五、原理图、仿真图及结果分析、PCB版图原理图如下所示:仿真及结果分析MULTISIM仿真图四进制波形七进制波形PCB板排布2.PCB原理图如下:PCB顶层PCB底层总结:完成这次课程设计之后,我觉得自己在电子设计过程中收获了很多,在这过程中我遇到了很多困难:在电路仿真时候,我觉得原理图是正确的,但运行不出想要的结果,我把74LS192换成了同样是计数器的74LS161,结果可以实现4、7进制的转换,于是我认为时芯片出了问题,找到老师说明了我的问题后,才知道是这个芯片本身特点,要根据它自身的性质来修改原理图;还有,接地的标号中要把Net选项选为GND,不然在PCB制作中将没有接地这一个选项出现;在PCB板制作时,要对元器件不断调整位置来使排版最佳。

基于74LS192的任意进制计数器的设计

基于74LS192的任意进制计数器的设计基于74LS192的任意进制计数器的设计【摘要】利用集成二、十进制计数器采用置数法、置零法设计任意进制计数器,分析设计方法,给出设计案例。

以集成计数器74LS192为例,运用置零法和置数法设计八进制计数器和二十四进制计数器,来讲述任意进制计数器的设计原理与基本方法。

【关键词】集成计数器;任意进制计数器的设计;置数法;置零法一、引言数字系统中的时序电路中,使用最多的电路就是计数器,计数器不仅能用于对时钟脉冲计数,还可以用于分频、定时、产生节拍脉冲和脉冲序列以及进行数字运算等。

集成计数器是运用的最为广泛的一种时序部件。

集成计数器的种类非常多样,如果按计数器中数字的编码方式分类,可分为二进制计数器,十进制计数器等。

集成计数器中,二进制和十进制计数器比较多见,对于任意进制计数器,通常利用现有的二、十进制计数器通过反馈清零或反馈置数来实现。

任意进制计数器在控制系统中经常使用,是数字电子技术教学的重点内容之一,也是学生设计性实验的难点之一,以下就以集成计数器74LS192为例,介绍在已有的计数器基础上设计任意进制计数器的方法。

二、设计依据及举例1.74LS192的管脚图74LS192是同步十进制可逆计数器,它由四个主从T触发器和一些门电路组成。

具有双时钟输入、清零、保持、并行置数、加计数、减计数等功能。

图1为74LS192的管脚图。

图1 74LS192的管脚图图1中:CLR是清零端,高电平有效;UP是递加计数脉冲输入端;DOWN是递减计数脉冲输入端;~LOAD是置数控制端,低电平有效;~CO是进位输出端;~BO是借位输出端。

ABCD是置数端口。

2.任意进制计数器M小于N的情况假定已有的是N进制计数器,需要得到的是M进制计数器。

这时就有M小于N和M大于N两种情况。

例题为用74LS192设计一个八进制计数器:在N进制的计数器的计数顺序中,使计数器的计数状态跳过N-M 的状态,。

74ls192芯片

74ls192芯片74LS192是一种技术较老的逻辑门集成电路(IC),它是一种同步可编程计数器。

该芯片可以实现四位二进制计数,并且可以通过外部的控制信号来实现不同的计数模式和功能。

74LS192具有带锁存功能的四位二进制计数器。

它包含四个独立的计数器,每个计数器都可以通过控制端进行控制。

此外,它还有一个可编程的控制端,可以用来选择计数方向(向上计数或向下计数)以及计数模式(十进制模式、二进制模式等)。

该芯片的引脚图和引脚功能如下:1. CP0 - 输入引脚,用于时钟脉冲的输入。

2. CP1 - 输入引脚,用于时钟脉冲的输入。

3. MR - 输入引脚,用于复位计数器。

4. PC0 - 输入引脚,用于选择计数模式。

5. PC1 - 输入引脚,用于选择计数模式。

6. U/D - 输入引脚,用于选择计数方向。

7. A - 输出引脚,用于输出二进制位的最低位。

8. B - 输出引脚,用于输出二进制位的次低位。

9. C - 输出引脚,用于输出二进制位的次高位。

10. D - 输出引脚,用于输出二进制位的最高位。

11. QA - 输出引脚,用于输出BCD码的最低位。

12. QB - 输出引脚,用于输出BCD码的次低位。

13. QC - 输出引脚,用于输出BCD码的次高位。

14. QD - 输出引脚,用于输出BCD码的最高位。

15. Vcc - 正电源引脚。

16. GND - 接地引脚。

74LS192的工作原理如下:首先,需要将MR引脚置低,从而使计数器复位。

然后,通过CP0和CP1引脚输入时钟信号,控制计数器的计数速度。

U/D引脚用于选择计数方向,当U/D引脚为低电平时,计数器向上计数,当U/D引脚为高电平时,计数器向下计数。

PC0和PC1引脚用于选择计数模式。

当PC1引脚为低电平,PC0引脚为高电平时,计数器工作在二进制模式下。

当PC1引脚为高电平,PC0引脚为低电平时,计数器工作在十进制模式下。

其它的PC1和PC0的组合可以实现更多的计数模式。

74Ls192

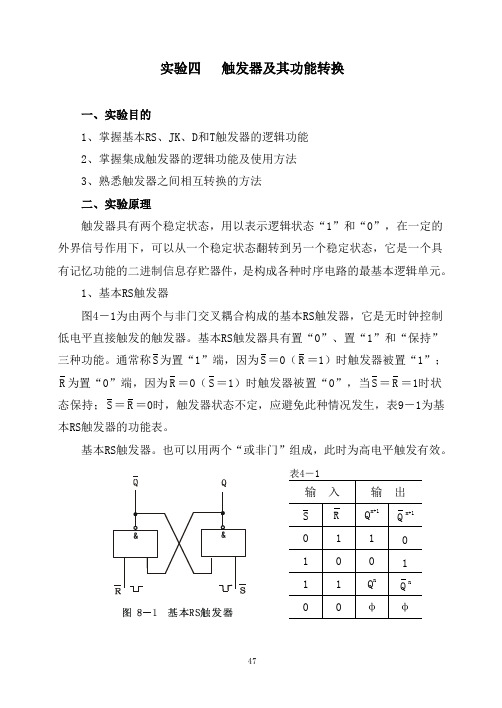

实验四触发器及其功能转换一、实验目的1、掌握基本RS、JK、D和T触发器的逻辑功能2、掌握集成触发器的逻辑功能及使用方法3、熟悉触发器之间相互转换的方法二、实验原理触发器具有两个稳定状态,用以表示逻辑状态“1”和“0”,在一定的外界信号作用下,可以从一个稳定状态翻转到另一个稳定状态,它是一个具有记忆功能的二进制信息存贮器件,是构成各种时序电路的最基本逻辑单元。

1、基本RS触发器图4-1为由两个与非门交叉耦合构成的基本RS触发器,它是无时钟控制低电平直接触发的触发器。

基本RS触发器具有置“0”、置“1”和“保持”三种功能。

通常称S为置“1”端,因为S=0(R=1)时触发器被置“1”;R为置“0”端,因为R=0(S=1)时触发器被置“0”,当S=R=1时状态保持;S=R=0时,触发器状态不定,应避免此种情况发生,表9-1为基本RS触发器的功能表。

基本RS触发器。

也可以用两个“或非门”组成,此时为高电平触发有效。

2、JK触发器在输入信号为双端的情况下,JK触发器是功能完善、使用灵活和通用性较强的一种触发器。

本实验采用74LS112双JK触发器,是下降边沿触发的边沿触发器。

引脚功能及逻辑符号如图4-2所示。

JK触发器的状态方程为Q n+1=J Q n+K Q nJ和K是数据输入端,是触发器状态更新的依据,若J、K有两个或两个以上输入端时,组成“与”的关系。

Q与Q为两个互补输出端。

通常把 Q=0、Q=1的状态定为触发器“0”状态;而把Q=1,Q=0定为“1”状态。

图4-2 74LS112双JK触发器引脚排列及逻辑符号下降沿触发JK触发器的功能如表4-2表4-2注:×— 任意态 ↓— 高到低电平跳变 ↑— 低到高电平跳变Q n (Q n )— 现态 Q n+1(Q n+1 )— 次态 φ— 不定态 JK 触发器常被用作缓冲存储器,移位寄存器和计数器。

3、D 触发器在输入信号为单端的情况下,D 触发器用起来最为方便,其状态方程为 Q n+1=D n,其输出状态的更新发生在CP 脉冲的上升沿,故又称为上升沿触发的边沿触发器,触发器的状态只取决于时钟到来前D 端的状态,D 触发器的应用很广,可用作数字信号的寄存,移位寄存,分频和波形发生等。

数电quartus用74LS192设计3X8和6X4的计数器

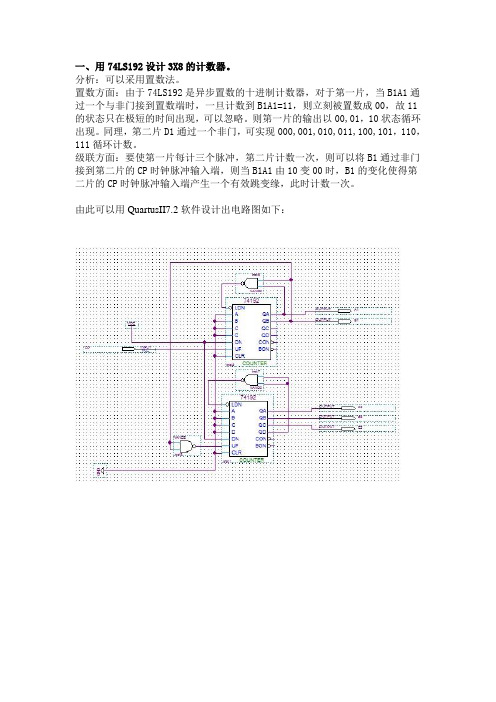

一、用74LS192设计3X8的计数器。

分析:可以采用置数法。

置数方面:由于74LS192是异步置数的十进制计数器,对于第一片,当B1A1通过一个与非门接到置数端时,一旦计数到B1A1=11,则立刻被置数成00,故11的状态只在极短的时间出现,可以忽略。

则第一片的输出以00,01,10状态循环出现。

同理,第二片D1通过一个非门,可实现000,001,010,011,100,101,110,111循环计数。

级联方面:要使第一片每计三个脉冲,第二片计数一次,则可以将B1通过非门接到第二片的CP时钟脉冲输入端,则当B1A1由10变00时,B1的变化使得第二片的CP时钟脉冲输入端产生一个有效跳变缘,此时计数一次。

由此可以用QuartusII7.2软件设计出电路图如下:

仿真结果的波形图如下

由波形图可知,每来三个脉冲,B1A1循环一次,而C2B2A2计数一次,24个脉冲过后,B1A1和C2B2A2均被置数成0,由此可知,用74LS192设计3X8的计数器成功。

二、用74LS192设计6X4的计数器。

分析:用74LS192设计6X4的计数器和设计3X8的计数器相似,只需在置数端和级联端按需求改变一下即可。

由此可以用QuartusII7.2软件设计出电路图如下:

仿真结果的波形图如下

由波形图可知,每来六个脉冲,C1B1A1循环一次,而B2A2计数一次,24个脉冲过后,C1B1A1和B2A2均被置数成0,由此可知,用74LS192设计6X4的计数器成功。

74ls192按键显示电路设计总结

74ls192按键显示电路设计总结

74ls192是一款常用于按键显示的集成电路,其主要功能是将按键输入的数字信号转换为BCD码输出,以便在数码管上显示。

下面是74ls192按键显示电路设计的总结:

1.按键电路设计

按键电路主要是将输入的数字信号转换为二进制信号输入到74ls192中。

设计中可以使用多个按键,将每个按键连接到一个编码器上,将编码器的输出连接到74ls192的输入引脚上。

在按键电路设计中,需要注意保护电路和按键的灵敏度。

2.74ls192电路设计

74ls192集成电路为四位二进制同步上升计数器,可以将二进制输入信号转换为BCD码输出。

在电路设计中,74ls192的各个引脚需要连接好,同时根据实际需要设置时钟信号、清零信号和使能信号。

3.数码管驱动电路设计

数码管驱动电路主要用于将74ls192输出的BCD码信号转换为驱动数码管的控制信号。

设计中需要选择适应的数码管驱动芯片,根据74ls192的输出信号控制数码管的显示。

4.供电电路设计

电路中需要使用适当的电源供电,设计中需要注意选择合适的电源,保证电路的正常工作。

此外,还要根据实际需要设计电路的保护电路,维护电路的稳定性和可靠性。

总之,74ls192按键显示电路设计需要注重各个方面的细节,保证电路的正常运行和可靠性。

设计前需要仔细考虑电路的需求,选择适合的元器件和器件参数,同时在设计过程中遵循相关的设计规范和国家法律法规的要求。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

基于74LS192的任意进制计数器的设计

【摘要】利用集成二、十进制计数器采用置数法、置零法设计任意进制计数器,分析设计方法,给出设计案例。

以集成计数器74LS192为例,运用置零法和置数法设计八进制计数器和二十四进制计数器,来讲述任意进制计数器的设计原理与基本方法。

【关键词】集成计数器;任意进制计数器的设计;置数法;置零法

一、引言

数字系统中的时序电路中,使用最多的电路就是计数器,计数器不仅能用于对时钟脉冲计数,还可以用于分频、定时、产生节拍脉冲和脉冲序列以及进行数字运算等。

集成计数器是运用的最为广泛的一种时序部件。

集成计数器的种类非常多样,如果按计数器中数字的编码方式分类,可分为二进制计数器,十进制计数器等。

集成计数器中,二进制和十进制计数器比较多见,对于任意进制计数器,通常利用现有的二、十进制计数器通过反馈清零或反馈置数来实现。

任意进制计数器在控制系统中经常使用,是数字电子技术教学的重点内容之一,也是学生设计性实验的难点之一,以下就以集成计数器74LS192为例,介绍在已有的计数器基础上设计任意进制计数器的方法。

二、设计依据及举例

1.74LS192的管脚图

74LS192是同步十进制可逆计数器,它由四个主从T触发器和一些门电路组成。

具有双时钟输入、清零、保持、并行置数、加计数、减计数等功能。

图1为74LS192的管脚图。

图1 74LS192的管脚图

图1中:CLR是清零端,高电平有效;UP是递加计数脉冲输入端;DOWN是递减计数脉冲输入端;~LOAD是置数控制端,低电平有效;~CO是进位输出端;~BO是借位输出端。

ABCD是置数端口。

2.任意进制计数器M小于N的情况

假定已有的是N进制计数器,需要得到的是M进制计数器。

这时就有M小于N和M大于N两种情况。

例题为用74LS192设计一个八进制计数器:

在N进制的计数器的计数顺序中,使计数器的计数状态跳过N-M的状态,

就可以得到M进制计数器,如例,74LS192是一个十进制计数器,如想得到八进制计数器,输出状态QAQBQCQD需要从0000—1110状态,跳过0001及1001这两个状态。

实现跳跃的方法有置零法和置数法这两个方法。

置零法的方式为在输入第M个计数脉冲CP后,利用计数器当前的输出状态SM进行译码产生清零信号加到清零端上,使计数器清零,即实现了M进制计数器。

在计数器的有效循环中不包括状态SM,所以状态SM只在极短的时间内出现称为过渡状态。

对于本例题来说,在输入第八个时钟脉冲后,当前的输出状态QAQBQCQD为0001,通过计数器输出端QD的高电平信号给CLR清零端,将计数器置零,回到0000状态。

根据以上原理设计出的逻辑图如图2所示。

图2

置数法方式为通过给计数器置入某个数值的方法跳跃N-M的状态,从而获得M进制计数器,这种方法适用于有预置数功能的集成计数器。

对于本例题来说,QAQBQCQD=0001状态与非门译码产生~LOAD=0的低电平信号,下一个时钟脉冲信号到来时将置数端ABCD=0000状态置入,跳过0001及1001这两个状态因而就实现了八进制。

设计出的逻辑图如图3所示。

图3

3.任意进制计数器M大于N的情况

例题为用74LS192设计一个24进制的计数器。

设计任意进制计数器M大于N的情况时必须要使用两个以上的N进制集成电路进行组合来完成M进制计数器的设计,各个集成电路之间的连接方式可分为串行进位,并行进位,整体置零,整体置数等几种方法。

图4

整体置零法就是将两片N进制计数器级联成大于M进制的计数器,然后在计数器输出到达M状态时,通过输出状态译码出清零信号同时送达两个计数器的清零端,使两个计数器同时清零,从而实现M进制,此方法类似于M小于N 的置零法原理。

对于74LS192来说,就是在两片集成计数器输出端QAQBQCQD 到达0010(第一片低位)0100(第二片高位)状态时,译出清零信号同时送到两个计数器的清零端。

根据以上设计原理设计出下面的逻辑电路图(图4)。

整体置数法的工作原理等同于M小于N的置数法原理,首先就是将两片N 进制计数器联成大于M进制的计数器,然后选定所设计的M进制状态,译码出置数端的有效工作信号,使N进制计数器置入置数输入端规定的信号,跳过剩余的不用的状态,从而实现M进制。

用整体置数法使两片74LS192完成24进制的设计方法可以参考M小于N的置数法以及以上的设计例题。

三、结束语

对于有置数端的集成计数器置数法和置零法均可使用,有的集成计数器只有清零端,这时就要认真考虑怎样将清零信号送达清零端。

在数字电子技术的学习中,要深入了解集成电路的工作原理,充分理解集成电路的功能表,就可能灵活应用集成电路,给我们的学习带来最大的帮助,完成准确高效的电路设计。

参考文献

[1]阎石.数字电子技术基础[M].5版.北京:高等教育出版社,2006.

[2]林涛.巨永锋.任意进制计数器设计方法[J].现代电子技术,2008.。