计算机组成原理第4版CPU子系统指令系统

合集下载

计算机组成原理第4章指令系统课件

4.2 指令的格式

4.2.1 指令的编码格式

操作码OC

AC1

AC2

(1)把保存操作前原来操作数的地址称为源点地址(SS), 把保存指令执行结果的地址称为终点地址或目的地址(DD)。

(2)将源点与终点操作数进行操作码规定的操作后,将 结果存入终点地址。通常二地址指令又称为双操作数指令。

ADD R0,R1表示将R0寄存器的内容和R1寄存器的内容相加以

5 异或XOR

XOR指令对两个操作数进 行按位异或运算。

4.4 指令的种类

4.4.4 移位、循环类指令

CF

位移指令SAL/SHL操作示意图

CF

SAR操作示意图

CF 0

SHR操作示意图

4.4 指令的种类

4.4.4 移位、循环类指令

不带进位标志的循环左移指令ROL MSB 操作数 LSB

CF

不带进位标志的循环右移指令ROR MSB 操作数 LSB

例如:在IBM-PC指令系统中

MOV

AX,05FFH

4.3 寻址方式

4.3.2 常用的寻址方式

2.直接寻址方式

(1)含义: 是指地址字段直接指明操作数在存储器内的位置的寻址 方法。即形式地址等于有效地址。 (2)优缺点: A、优点:简单,不需要进行加法运算。 B、缺点:地址空间指令地址字段长度的限制。

4.2 指令的格式

4.2.3 指令助记符

通常采用一些符号来代表二进制数据,这些符号即指 令助记符。

指令助记符 ADD SUB MUL DIV

助记符示例

含义

指令助记符

相加

AND

相减

OR

相乘

LOAD

相除

STORE

白中英组成原理第四版chp4

指令格式:操作码θ 操作数A

30

2、立即寻址

特点:在取指令时,操作码和操作数被同步取出,不 必再次访问存储器,从而提升了指令旳执行速度。

但是,因为操作数是指令旳一部分,不能被修改; 而且对于定 长指令格式,操作数旳大小将受到指令长

度旳限制,所以这种寻址方式灵活性最差 一般用于给某一寄存器或主存单元赋初值,或者用于

使用时有一点必须注意:指令执行之后,A1中原存 旳内容已经被新旳运算成果替代了。

12

二、地址码

二地址地址根据操作数旳物理位置分为:

SS 存储器-存储器类型 RS 寄存器-存储器类型 RR 寄存器-寄存器类型

慢

13

二、地址码

一地址指令

指令格式为:

θ A1

操作码θ 第一操作数A1

(AC)θ(A1) →A1 (PC)+1→PC 单操作数运算指令,如“+1”、“-1”、“求反” 指令中给出一种源操作数旳地址

器方式和24种变址方式(参照汇编语言教材); Reg或OP(3位)指定另一种操作数(寄存器)或

用作OP旳补充。

操作码 Mod Reg或操作码 R/M S I B 位移量 立即数

1个字节

1个字节

21

七、 Pentium指令格式

S、I、B共1个字节,分别是百分比系数、变址寄存器 号、基址寄存器号,可选。mod-R/M中旳某些编码要 求SIB字节来完毕寻址方式旳指定;

第四章 指令系统

4.1 指令系统旳发展与性能要求 4.2 指令格式与 4.3 操作数类型 4.4 指令和数据旳寻址方式 4.5 经典指令

返回 1

4.1 指令系统旳发展与性能要求

1、指令在计算机系统中旳地位 (1)是软件和硬件分界面旳一种主要标志

30

2、立即寻址

特点:在取指令时,操作码和操作数被同步取出,不 必再次访问存储器,从而提升了指令旳执行速度。

但是,因为操作数是指令旳一部分,不能被修改; 而且对于定 长指令格式,操作数旳大小将受到指令长

度旳限制,所以这种寻址方式灵活性最差 一般用于给某一寄存器或主存单元赋初值,或者用于

使用时有一点必须注意:指令执行之后,A1中原存 旳内容已经被新旳运算成果替代了。

12

二、地址码

二地址地址根据操作数旳物理位置分为:

SS 存储器-存储器类型 RS 寄存器-存储器类型 RR 寄存器-寄存器类型

慢

13

二、地址码

一地址指令

指令格式为:

θ A1

操作码θ 第一操作数A1

(AC)θ(A1) →A1 (PC)+1→PC 单操作数运算指令,如“+1”、“-1”、“求反” 指令中给出一种源操作数旳地址

器方式和24种变址方式(参照汇编语言教材); Reg或OP(3位)指定另一种操作数(寄存器)或

用作OP旳补充。

操作码 Mod Reg或操作码 R/M S I B 位移量 立即数

1个字节

1个字节

21

七、 Pentium指令格式

S、I、B共1个字节,分别是百分比系数、变址寄存器 号、基址寄存器号,可选。mod-R/M中旳某些编码要 求SIB字节来完毕寻址方式旳指定;

第四章 指令系统

4.1 指令系统旳发展与性能要求 4.2 指令格式与 4.3 操作数类型 4.4 指令和数据旳寻址方式 4.5 经典指令

返回 1

4.1 指令系统旳发展与性能要求

1、指令在计算机系统中旳地位 (1)是软件和硬件分界面旳一种主要标志

《计算机组成原理》教程第4章指令系统

4

二 指令的格式

即指令字用二进制代码表示的结构形式

包括 操作码:操作的性质 操作码 地址码:操作数(operand)的存储位置,即参加操作的 operand , 地址码 数据的地址和结果数的地址

操作码域(op) 地址码域(addr)

5

1.操作码 操作码

指令的操作码表示该指令应进行什么性质的操作。 组成操作码字段的位数一般取决于计算机指令系统的 规模。 固定长度操作码:便于译码,扩展性差 . 可变长度操作码:能缩短指令平均长度 操作码的的位数决定了所能表示的操作数,n位操 作码最多表示2n种操作

(2). 堆栈工作过程 .

(一)进栈操作 ① 建立堆栈,由指令把栈顶地址送入SP,指针 指向栈顶。 ② 进栈:(A)→Msp, (sp)-1→SP ;Msp:存储 器的栈顶单元 (二)出栈操作 (SP)+1→SP, (Msp)→A

22

五.指令类型

一个较完善的指令系统应当包括: 数据传送类指令: 例)move、load、store等 算术运算类指令: 例)add、sub、mult、div、comp等 移位操作类指令: 例) shl,shr,srl,srr 逻辑运算类指令: 例)and、or、xor、not等 程序控制类指令: 例)jump、branch、jsr、ret、int等 输入输出指令: 例)in、out等 字符串类指令: 例)如alpha中cmpbge、inswh、extbl等 系统控制类指令: 例)push、pop、test等

18

10) *段寻址方式 段寻址方式 Intel 8086 CPU中采用了段寻址方式(基址寻址的特例)。 由16位段寄存器和16位偏移量产生20位物理地址 11)*自动变址寻址 自动变址寻址 指在变址方式中,每经过一次变址运算时,都自动改变变址寄存 器的内容,以后在PDP-11中详讲.

纪禄平-计算机组成原理(第4版)3(5)-CPU子系统-MIPS-4-多周期-3-控制系统PPT课件

3.5.4 多周期MIPS处理器

(组合逻辑与微程序)

-

1

※多周期CPU所需的控制信号

PCSrc[1:0]

01 00 10

PCWrite

PC

IorD MemWrite

存储器

0 1

Addr

RD

rst

WD

MemRead

IRWrite

<<2

U

RegDst RegWrite

RN1 RD1 A

operation 0 1

F

+4 00

MDR

1 0

WD

RD2 B

01 10

zero

MemtoReg

E

<<2

extend

11 AluSrc_B[1:0]

多路选择器: 4个+2个(2位/个); ALU: 1组(4位); 扩展器: 1个; 存储器: 2个; 寄存器堆: 1个; 专用寄存器: 2个; 共需13种控制信号, 共18位。

SC

Operation extend RegWrite IRWrite MemRead MemWrite PCWrite AluSrc_B AluSrc_A MemtoReg RegDst IorD PCSrc

2 1111 2 111 111 4 4

→00B08001H

-

2

24

❸ 整合所有指令的微程序并存储到Control Store √ T0中取指操作对应的微指令被全部指令共享 √各指令的其余微指令按顺序存储 √各指令的最末一条微指令中的顺序控制字段SC=10

写出各位的输出逻辑式:

PCsrc[1]=j_flag PCsrc[0]=beq_flag·zero PCWrite=FT_flag+beq_flag·zero+j_flag

(组合逻辑与微程序)

-

1

※多周期CPU所需的控制信号

PCSrc[1:0]

01 00 10

PCWrite

PC

IorD MemWrite

存储器

0 1

Addr

RD

rst

WD

MemRead

IRWrite

<<2

U

RegDst RegWrite

RN1 RD1 A

operation 0 1

F

+4 00

MDR

1 0

WD

RD2 B

01 10

zero

MemtoReg

E

<<2

extend

11 AluSrc_B[1:0]

多路选择器: 4个+2个(2位/个); ALU: 1组(4位); 扩展器: 1个; 存储器: 2个; 寄存器堆: 1个; 专用寄存器: 2个; 共需13种控制信号, 共18位。

SC

Operation extend RegWrite IRWrite MemRead MemWrite PCWrite AluSrc_B AluSrc_A MemtoReg RegDst IorD PCSrc

2 1111 2 111 111 4 4

→00B08001H

-

2

24

❸ 整合所有指令的微程序并存储到Control Store √ T0中取指操作对应的微指令被全部指令共享 √各指令的其余微指令按顺序存储 √各指令的最末一条微指令中的顺序控制字段SC=10

写出各位的输出逻辑式:

PCsrc[1]=j_flag PCsrc[0]=beq_flag·zero PCWrite=FT_flag+beq_flag·zero+j_flag

最新计算机组成原理第4章_指令系统_任国林版课件幻灯片

…… 2019 A←A+1

…

2000 …

2010 CALL 2200 2011 A←A+1 ……

2200 …

… CALL ** …

2280 RETURN ……

条件转移操作

无条件转移操作

调用操作

返回操作

注:①条件转移操作的条件由测试条件及转移条件组成;

②调用操作参数有目标指令地址及返回指令地址;

③返回操作参数仅为返回指令地址

出栈:①目标地址←[SP],②SP←(SP)+X

对于入栈时SP递增移动方式,入栈+X、出栈-X

边界不对齐方式

边界对齐方式

整数边界对齐方式:长度为2n个存储字的数据在存储

器中存储时,最小单元地址(N)的最低n位必须为零。

如长度为20、21、22个存储字的N为XXXX、XXX0、XX00

3、数据(常数)在指令中的存放方式

*存放方式:边界—采用边界不对齐方式; (尽量减少指令字长) 次序—与存储器存放次序一致。(方便CPU处理)

操作步骤—入栈:先移动栈顶,再在栈顶写入数据, 出栈:先从栈顶读出数据,再移动栈顶;

B

A

A

A

①空堆栈

②A入栈

③B入栈

④出栈(B)

存取特征—后进先出顺序、不按地址访问,

破坏性读出(只对栈顶操作);

6

18

*寄存器堆栈: --用移位REG实现,面向硬件

组成特征—大小及栈顶固定,CPU用计数器表示“栈底”;

8

1、操作码字段 *功能:用编码指明(约定)操作的性质, 包括操作类型、操作数类型及长度3个方面;

例1—指令系统约定:操作类型≤8种,加法操作需支持8/16 位定点数、单/双精度浮点数,移位操作需支持8/16位定点数, 逻辑非操作只需支持8位逻辑数。操作码字段如何编码?

…

2000 …

2010 CALL 2200 2011 A←A+1 ……

2200 …

… CALL ** …

2280 RETURN ……

条件转移操作

无条件转移操作

调用操作

返回操作

注:①条件转移操作的条件由测试条件及转移条件组成;

②调用操作参数有目标指令地址及返回指令地址;

③返回操作参数仅为返回指令地址

出栈:①目标地址←[SP],②SP←(SP)+X

对于入栈时SP递增移动方式,入栈+X、出栈-X

边界不对齐方式

边界对齐方式

整数边界对齐方式:长度为2n个存储字的数据在存储

器中存储时,最小单元地址(N)的最低n位必须为零。

如长度为20、21、22个存储字的N为XXXX、XXX0、XX00

3、数据(常数)在指令中的存放方式

*存放方式:边界—采用边界不对齐方式; (尽量减少指令字长) 次序—与存储器存放次序一致。(方便CPU处理)

操作步骤—入栈:先移动栈顶,再在栈顶写入数据, 出栈:先从栈顶读出数据,再移动栈顶;

B

A

A

A

①空堆栈

②A入栈

③B入栈

④出栈(B)

存取特征—后进先出顺序、不按地址访问,

破坏性读出(只对栈顶操作);

6

18

*寄存器堆栈: --用移位REG实现,面向硬件

组成特征—大小及栈顶固定,CPU用计数器表示“栈底”;

8

1、操作码字段 *功能:用编码指明(约定)操作的性质, 包括操作类型、操作数类型及长度3个方面;

例1—指令系统约定:操作类型≤8种,加法操作需支持8/16 位定点数、单/双精度浮点数,移位操作需支持8/16位定点数, 逻辑非操作只需支持8位逻辑数。操作码字段如何编码?

计算机组成原理-第4章_指令系统

7. 段寻址方式(Segment Addressing)

方法:E由段寄存器的内容加上段内偏移地址而形成。

应用:微型机采用段寻址方式,20位物理地址为16位 段地址左移四位加上16位偏移量。

分类:① 段内直接寻址; ② 段内间接寻址; ③ 段间直接寻址; ④ 段间间接寻址;

9 堆栈寻址方式

堆栈:是一组能存入和取出数据的暂时存储单元。

*** 指令字长度

概念 指令字长度(一个指令字包含二进制代码的位数) 机器字长:计算机能直接处理的二进制数据的位数。 单字长指令 半字长指令 双字长指令

多字长指令的优缺点

优点提供足够的地址位来解决访问内存任何单元的寻址问题 ; 缺点必须两次或多次访问内存以取出一整条指令,降低了CPU的运 算速度,又占用了更多的存储空间。

*** 指令系统的发展与性能要求

*** 指令系统的发展

指令:即机器指令,要计算机执行某种操作的命令。

指令划分:微指令、机器指令和宏指令。

简单

复杂

指令系统:一台计算机中所有指令的集合;是表征

计算机性能的重要因素。

系列计算机:基本指令系统相同、基本体系结构相同 的一系列计算机。

*** 对指令系统性能的要求

(2)立即数只能作为源操作数,立即寻址主要用来给寄存 器或存储器赋初值。以A~F开头的数字出现在指令中时,前 面要加0。

(3)速度快(操作数直接在指令中,不需要运行总线周期)

(4)立即数作为指令操作码的一部分与操作码一起放在代 码段区域中。

(5)指令的长度(翻译成机器语言后)较长,灵活性较差。

【例】MOV AX, 10H 执行后(AX)=? 其中:这是一条字操作指令,源操作数为立即寻址 方式,立即数为0010H,存放在指令的下两个单元。

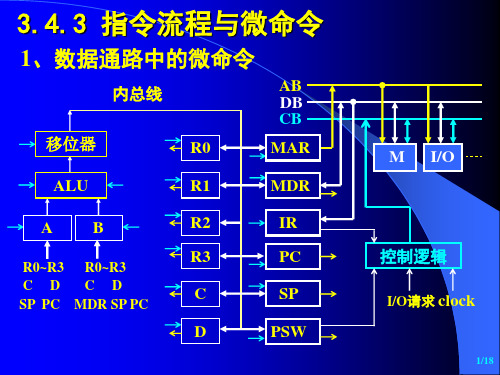

纪禄平-计算机组成原理PPT(第4版)3(4)-CPU子系统-模型机CPU-3-指令流程与微命令

5/18

操作时间表中各微命令的含义:

(1) 控制访存操作的微命令

EMAR, R/W, SIR, … (2) 控制CPU内部数据通路操作微命令 PCA, S3S2S1S0MC0, DM, CPPC, … (3) 控制时序切换的微命令 需要结合控制系统才能表述。ຫໍສະໝຸດ 6/18❶ 传送指令

1)流程图

例1:MOV R0,R1; FT0: M ET0: R1 ET1: PC 例2:MOV(R0),(R1); FT0: M ST0: R1 ST1: M DT0: R0 ET0: C ET1: MDR ET2: PC

→B

17/18

移位器控制信号S:DM、SL、SR、EX 脉冲型微命令CP:无、CPRi\CPRj\CPC\CPD\CPMAR

CPMDR\CPPC\CPSP 访存控制:EMAR\W(EMDR)\R(SMDR)

IR和PSW的辅助控制ST:无,0→PSW[4],1→PSW[4],SIR 上述是直接根据指令流程归纳的微命令,设计控制系统 时需要先对这些微命令编码,见教材。 对比数据通路,其中Ri→A,Rj→B、CPRi和CPRj属于 间接信号,需结合指令中的寄存器编号,才能确定部 件的直接控制信号(见表3-13、3-14)

15/18

❻ 中断隐指令 IT0: 0 IT1: PC IT2: MDR PSW[4], SP-1 MDR M SP/MAR

IT3:形成向量地址→MAR

IT4:M→MDR →PC/MAR

16/18

3、指令集的微命令归纳

指令执行过程所需的微命令,取决于: 数据通路结构; 基于数据通路设计的指令流程;

R0~3/C/D/SP/PC/ MDR →B ALU功能: S3S2S1S0、M、CI 移位选择:

操作时间表中各微命令的含义:

(1) 控制访存操作的微命令

EMAR, R/W, SIR, … (2) 控制CPU内部数据通路操作微命令 PCA, S3S2S1S0MC0, DM, CPPC, … (3) 控制时序切换的微命令 需要结合控制系统才能表述。ຫໍສະໝຸດ 6/18❶ 传送指令

1)流程图

例1:MOV R0,R1; FT0: M ET0: R1 ET1: PC 例2:MOV(R0),(R1); FT0: M ST0: R1 ST1: M DT0: R0 ET0: C ET1: MDR ET2: PC

→B

17/18

移位器控制信号S:DM、SL、SR、EX 脉冲型微命令CP:无、CPRi\CPRj\CPC\CPD\CPMAR

CPMDR\CPPC\CPSP 访存控制:EMAR\W(EMDR)\R(SMDR)

IR和PSW的辅助控制ST:无,0→PSW[4],1→PSW[4],SIR 上述是直接根据指令流程归纳的微命令,设计控制系统 时需要先对这些微命令编码,见教材。 对比数据通路,其中Ri→A,Rj→B、CPRi和CPRj属于 间接信号,需结合指令中的寄存器编号,才能确定部 件的直接控制信号(见表3-13、3-14)

15/18

❻ 中断隐指令 IT0: 0 IT1: PC IT2: MDR PSW[4], SP-1 MDR M SP/MAR

IT3:形成向量地址→MAR

IT4:M→MDR →PC/MAR

16/18

3、指令集的微命令归纳

指令执行过程所需的微命令,取决于: 数据通路结构; 基于数据通路设计的指令流程;

R0~3/C/D/SP/PC/ MDR →B ALU功能: S3S2S1S0、M、CI 移位选择:

纪禄平-计算机组成原理PPT(第4版)3(1)-CPU子系统-概述

1、主要功能

✓处理指令-控制指令的执行顺序; ✓执行操作-产生控制信号控制部件工作; ✓控制时间-控制各步操作的时序; ✓数据运算-算术和逻辑运算;

2、执行指令的流程

✓读取指令-从存储器中读取; ✓指令译码-通过控制器进行、产生控制信号; ✓指令执行-寻址、取数、运算; ✓后续工作-保存结果、响应外部请求等;

9

⑤程序状态字寄存器(PSW)

[主要用途] 仅1个,记录现行程序的运行状态和程序的工作模式。

❖ PSW-特征位 也叫标志位,反映CPU的当前状态。 指令执行时,根据情况自动设置这些特征位,作为后 续操作的判断依据,通常有5类:

进位 溢出 零值

P

…

自动设置(具备该特征,就设置该标志位=1)

10

❖ PSW-编程设定位

PSW中某些位或字段可通过程序来设定,以决定程 序的调试、对中断的响应、程序的运行模式等。

跟踪位

T

允许中断

I

程序优 先级P

运行模式

⑥地址寄存器(MAR)

[主要用途] 只有1个,读写存储器时,先要定位存储单元,因此 设置MAR来存放目标单元的地址码。 先将有效地址送入MAR,再启动后续的读写操作。

数据1 数据0

栈底

堆栈(存储器)

12

4、控制器

[主要作用] 根据指令、时钟信号、外部信号等信息,产生各种 控制信号(微命令),以便控制各种功能部件协同工 作,完成指令的功能。

指令代码

控制单元

时序信号 状态信号

各种控制信号

根据产生微命令的方式,有两类控制单元:

①组合逻辑控制器 组合逻辑硬件电路→控制信号

第3章 CPU子系统

※本章主要介绍:

功能部件

✓处理指令-控制指令的执行顺序; ✓执行操作-产生控制信号控制部件工作; ✓控制时间-控制各步操作的时序; ✓数据运算-算术和逻辑运算;

2、执行指令的流程

✓读取指令-从存储器中读取; ✓指令译码-通过控制器进行、产生控制信号; ✓指令执行-寻址、取数、运算; ✓后续工作-保存结果、响应外部请求等;

9

⑤程序状态字寄存器(PSW)

[主要用途] 仅1个,记录现行程序的运行状态和程序的工作模式。

❖ PSW-特征位 也叫标志位,反映CPU的当前状态。 指令执行时,根据情况自动设置这些特征位,作为后 续操作的判断依据,通常有5类:

进位 溢出 零值

P

…

自动设置(具备该特征,就设置该标志位=1)

10

❖ PSW-编程设定位

PSW中某些位或字段可通过程序来设定,以决定程 序的调试、对中断的响应、程序的运行模式等。

跟踪位

T

允许中断

I

程序优 先级P

运行模式

⑥地址寄存器(MAR)

[主要用途] 只有1个,读写存储器时,先要定位存储单元,因此 设置MAR来存放目标单元的地址码。 先将有效地址送入MAR,再启动后续的读写操作。

数据1 数据0

栈底

堆栈(存储器)

12

4、控制器

[主要作用] 根据指令、时钟信号、外部信号等信息,产生各种 控制信号(微命令),以便控制各种功能部件协同工 作,完成指令的功能。

指令代码

控制单元

时序信号 状态信号

各种控制信号

根据产生微命令的方式,有两类控制单元:

①组合逻辑控制器 组合逻辑硬件电路→控制信号

第3章 CPU子系统

※本章主要介绍:

功能部件

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

① 地址码数据 寄存器编号或者存储器地址,无符号整数。 ② 数值型数据 定点数、浮点数等,一般用补码表示。

③ 字符型数据 通常表示为ASCII码/汉字内码格式。

④ 逻辑型数据 常规二进制代码,不具有数值含义。

计算机组成原理第4版CPU子系统指令系 统

15

5. MIPS32架构的指令格式

RISC 指令字长为:32位 寄存器数量:32个

②不利于VLSI工艺

为实现大量的复杂指令,控制逻辑极不规整,给VLSI工艺 造成很大困难。

③ 主存技术的发展

一般通过保存在控制存储器中的微程序来实现复杂指令, 70年代后期开始用DRAM做主存,使主存与控制存储器的 速度相当,因此很多复杂指令不必再用微程序来实现,可 用简单指令构成的子程序实现等效功能。

3. 地址结构 指令中提供的地址

地址偏移量/立即数 寄存器编号

(1)指令中提供地址的方式

√显式地址方式 →指令中明确指明地址码 (直接/间接给出)

√隐式地址方式

→地址码隐含约定,不在指令中出现。

使用隐式地址,可以减少指令中的地址数量, 从而简化地址结构。

计算机组成原理第4版CPU子系统指令系 统

9

自动修改PC的内容,使PC指向下一条指令

计算机组成原理第4版CPU子系统指令系 统

12

✓ 一地址结构指令

θ A1 源/目的地址

隐含约定

双操作数:A1 U [PC]H→PC 如:J addr

单操作数:

θ(A1) → A1 (PC)+ → PC 如:INC R0

自动修改PC的内容,使PC指向下一条指令

精简指令集计算 随着半导体技术进步,80年代开始逐渐直接通过硬件方 式,而不是扩充指令来实现复杂功能,指令规模逐渐缩 小、指令进一步简化 → 精简指令集

计算机组成原理第4版CPU子系统指令系 统

3

※CISC→RISC的技术背景

①2-8规律

CISC中的不同指令使用频率悬殊: 简单指令(约占20%的)约占80%的使用频率,复杂指令(约 占80%)只占大约20%的使用频率。

计算机组成原理第4版CPU子系统指令系 统

13

✓ 零地址结构指令

θ

功能: ①用于处理机的特殊控制(如HLT, NOP)。 ②针对隐含约定的寄存器,如返回指令:

RST

隐含操作:(SP)→PC; SP+ →SP; 把堆栈栈顶单元保存的返回地址打入PC。

计算机组成原理第4版CPU子系统指令系 统

14

4. 指令可能会涉及到的操作数类型

计算机组成原理第4版CPU子系统指令系 统

4

→CISC的特点:

①指令数量多; ②指令长度可以不固定,指令格式和寻址方式多样; ③很多指令会涉及存储器读写操作,指令周期长; ④一般在通用处理器中使用;

→RISC的特点:

①指令数量少; ②指令长度固定,指令格式和寻址方式种类也少; ③一般只有少量指令(如取数/存数) 才会读写存储 器,其余指令只涉及CPU内部寄存器,指令周期短; ④一般在高端服务器CPU中使用;

计算机组成原Leabharlann 第4版CPU子系统指令系 统7

(3)复合型操作码 基本特征: 操作码分为几段,每段表示一种二级操作。 [例]某机的算术逻辑运算指令格式

15 ~ 13 12 11 10 9 5 ~ 0

1基5 本操作 进位 移位 回送 判跳 操作数

复合型操作码

计算机组成原理第4版CPU子系统指令系 统

8

指令 类型

R型 I型 J型

指令长度(32位定长)

31 ~ 26 25~21 20~16 25~11 10 ~ 6 5 ~ 0

op(6) rs(5) rt(5) rd(5) shamt func

op(6) rs(5) rt(5) address/imm (16)

op(6)

address (26)

计算机组成原理第4版CPU子系统指令系 统

(2) 常见的地址结构类型 ✓ 四地址结构指令

θ A1 A2 A3 A4

操作数 地址

结果 下条指 地址 令地址

功能:(A1)θ(A2)→A3 A4→PC

一般用PC寄存器指示下条指令的地址。

四地址结构指令在RISC中很少会使用。

计算机组成原理第4版CPU子系统指令系 统

10

✓三地址结构指令

θ A1 A2 A3

⊙指令集:instruction set,处理器能执行的全体 指令的集合(CISC、RISC)

√ 决定了 计算机的硬件功能 √ 计算机中软硬件的分界面

⊙ 指令字:用来表示指令的一组二进制代码。

⊙ 指令字长:指令中包含的二进制代码位数

⊙ 机器字长:计算机能够直接处理的二进制数据 的位数 = 寄存器的宽度。

计算机组成原理第4版CPU子系统指令系 统

5

3.2.2 指令格式

指令的基本格式

操作码θ 地址码A /操作数D

1个

1个或几个(广义)

计算机组成原理第4版CPU子系统指令系 统

6

1. 指令字长

定长指令格式 规整、便于控制

变长指令格式 合理利用存储空间、提高取指令

的效率,如超长指令集

2. 操作码结构

(1)定长操作码 各指令θ的位置、位数固定相同。 (2)扩展操作码 各指令θ的位置、位数不固定,根据需要 变化 (设置扩展标志)。

3.2 指令系统

设计CPU的一般过程: 指令系统→ 数据通路→ 控制器→ CPU定型

本节主要分析: √指令格式 √指令涉及的寻址方式 √向用户的指令类型

− 基于MIPS32架构

计算机组成原理第4版CPU子系统指令系 统

1

⊙指令:instruction,计算机执行某类操作的信 息的集合,是CPU工作的主要依据。

操作数 地址

结果 地址

功能:

(A1)θ(A2)→A3

(PC)+ →PC 如:ADD rd, rs, rt

自动修改PC的内容,使PC指向下一条指令

计算机组成原理第4版CPU子系统指令系 统

11

✓二地址结构指令 θ A1 A2

目的地址 源地址

功能: (A1)θ(A2)→A1

(PC)+ →PC

如:ADD R1, R0

计算机组成原理第4版CPU子系统指令系 统

2

3.2.1 指令集类型

1、CISC(Complex Instruction Set Computing)

复杂指令集计算 早期计算机部件昂贵、速度慢,为了扩展硬件功能,不 得不将更多更复杂指令加入到指令系统,以提高计算机 的处理能力 → 复杂指令集

2、RISC(Reduced Instruction Set Computing)

③ 字符型数据 通常表示为ASCII码/汉字内码格式。

④ 逻辑型数据 常规二进制代码,不具有数值含义。

计算机组成原理第4版CPU子系统指令系 统

15

5. MIPS32架构的指令格式

RISC 指令字长为:32位 寄存器数量:32个

②不利于VLSI工艺

为实现大量的复杂指令,控制逻辑极不规整,给VLSI工艺 造成很大困难。

③ 主存技术的发展

一般通过保存在控制存储器中的微程序来实现复杂指令, 70年代后期开始用DRAM做主存,使主存与控制存储器的 速度相当,因此很多复杂指令不必再用微程序来实现,可 用简单指令构成的子程序实现等效功能。

3. 地址结构 指令中提供的地址

地址偏移量/立即数 寄存器编号

(1)指令中提供地址的方式

√显式地址方式 →指令中明确指明地址码 (直接/间接给出)

√隐式地址方式

→地址码隐含约定,不在指令中出现。

使用隐式地址,可以减少指令中的地址数量, 从而简化地址结构。

计算机组成原理第4版CPU子系统指令系 统

9

自动修改PC的内容,使PC指向下一条指令

计算机组成原理第4版CPU子系统指令系 统

12

✓ 一地址结构指令

θ A1 源/目的地址

隐含约定

双操作数:A1 U [PC]H→PC 如:J addr

单操作数:

θ(A1) → A1 (PC)+ → PC 如:INC R0

自动修改PC的内容,使PC指向下一条指令

精简指令集计算 随着半导体技术进步,80年代开始逐渐直接通过硬件方 式,而不是扩充指令来实现复杂功能,指令规模逐渐缩 小、指令进一步简化 → 精简指令集

计算机组成原理第4版CPU子系统指令系 统

3

※CISC→RISC的技术背景

①2-8规律

CISC中的不同指令使用频率悬殊: 简单指令(约占20%的)约占80%的使用频率,复杂指令(约 占80%)只占大约20%的使用频率。

计算机组成原理第4版CPU子系统指令系 统

13

✓ 零地址结构指令

θ

功能: ①用于处理机的特殊控制(如HLT, NOP)。 ②针对隐含约定的寄存器,如返回指令:

RST

隐含操作:(SP)→PC; SP+ →SP; 把堆栈栈顶单元保存的返回地址打入PC。

计算机组成原理第4版CPU子系统指令系 统

14

4. 指令可能会涉及到的操作数类型

计算机组成原理第4版CPU子系统指令系 统

4

→CISC的特点:

①指令数量多; ②指令长度可以不固定,指令格式和寻址方式多样; ③很多指令会涉及存储器读写操作,指令周期长; ④一般在通用处理器中使用;

→RISC的特点:

①指令数量少; ②指令长度固定,指令格式和寻址方式种类也少; ③一般只有少量指令(如取数/存数) 才会读写存储 器,其余指令只涉及CPU内部寄存器,指令周期短; ④一般在高端服务器CPU中使用;

计算机组成原Leabharlann 第4版CPU子系统指令系 统7

(3)复合型操作码 基本特征: 操作码分为几段,每段表示一种二级操作。 [例]某机的算术逻辑运算指令格式

15 ~ 13 12 11 10 9 5 ~ 0

1基5 本操作 进位 移位 回送 判跳 操作数

复合型操作码

计算机组成原理第4版CPU子系统指令系 统

8

指令 类型

R型 I型 J型

指令长度(32位定长)

31 ~ 26 25~21 20~16 25~11 10 ~ 6 5 ~ 0

op(6) rs(5) rt(5) rd(5) shamt func

op(6) rs(5) rt(5) address/imm (16)

op(6)

address (26)

计算机组成原理第4版CPU子系统指令系 统

(2) 常见的地址结构类型 ✓ 四地址结构指令

θ A1 A2 A3 A4

操作数 地址

结果 下条指 地址 令地址

功能:(A1)θ(A2)→A3 A4→PC

一般用PC寄存器指示下条指令的地址。

四地址结构指令在RISC中很少会使用。

计算机组成原理第4版CPU子系统指令系 统

10

✓三地址结构指令

θ A1 A2 A3

⊙指令集:instruction set,处理器能执行的全体 指令的集合(CISC、RISC)

√ 决定了 计算机的硬件功能 √ 计算机中软硬件的分界面

⊙ 指令字:用来表示指令的一组二进制代码。

⊙ 指令字长:指令中包含的二进制代码位数

⊙ 机器字长:计算机能够直接处理的二进制数据 的位数 = 寄存器的宽度。

计算机组成原理第4版CPU子系统指令系 统

5

3.2.2 指令格式

指令的基本格式

操作码θ 地址码A /操作数D

1个

1个或几个(广义)

计算机组成原理第4版CPU子系统指令系 统

6

1. 指令字长

定长指令格式 规整、便于控制

变长指令格式 合理利用存储空间、提高取指令

的效率,如超长指令集

2. 操作码结构

(1)定长操作码 各指令θ的位置、位数固定相同。 (2)扩展操作码 各指令θ的位置、位数不固定,根据需要 变化 (设置扩展标志)。

3.2 指令系统

设计CPU的一般过程: 指令系统→ 数据通路→ 控制器→ CPU定型

本节主要分析: √指令格式 √指令涉及的寻址方式 √向用户的指令类型

− 基于MIPS32架构

计算机组成原理第4版CPU子系统指令系 统

1

⊙指令:instruction,计算机执行某类操作的信 息的集合,是CPU工作的主要依据。

操作数 地址

结果 地址

功能:

(A1)θ(A2)→A3

(PC)+ →PC 如:ADD rd, rs, rt

自动修改PC的内容,使PC指向下一条指令

计算机组成原理第4版CPU子系统指令系 统

11

✓二地址结构指令 θ A1 A2

目的地址 源地址

功能: (A1)θ(A2)→A1

(PC)+ →PC

如:ADD R1, R0

计算机组成原理第4版CPU子系统指令系 统

2

3.2.1 指令集类型

1、CISC(Complex Instruction Set Computing)

复杂指令集计算 早期计算机部件昂贵、速度慢,为了扩展硬件功能,不 得不将更多更复杂指令加入到指令系统,以提高计算机 的处理能力 → 复杂指令集

2、RISC(Reduced Instruction Set Computing)