用ModelSimSE进行功能仿真和时序仿真的方法(ALTERA篇)

用ModelSimSE进行功能仿真和时序仿真的方法(ALTERA篇)

用ModelSimSE进行 功能仿真和时序仿真的方法 (ALTERA篇)黄俊April 2007用ModelSim SE进行功能仿真和时序仿真的方法 (ALTERA篇)软件准备(1) QuartusII,本文截图是QuartusII 6.1界面的。

我个人认为,如果是开发StratixII或CycloneII或MAXII,用QuartusII6.0+SP1+SP2比较稳定。

(2) ModelSim SE. ALTERA仿真库要已经装好,安装仿真库的笔记已记录于《在ModelSimSE中添加ALTERA仿真库的详细步骤》中。

我电脑上装的是ModelSim SE6.1b。

例子程序的制作先在Quartus II里生成一个例子程序,以方便介绍三种仿真的方法。

步骤如下:1、新建一个工程(Project),工程名取lpm_shift, 器件选CycloneII EP2C5Q208C, 第三方的工具暂时都不选。

2、菜单栏上ToolsÆMegaWizard Plug-In Manager, 点Next,在storage中选LPM_SHIFTREG,输出文件格式根据习惯选一种语言,在这里以Verilog的为例,在右边的output file名字中加上lpm_shift。

点Next。

3、这个例子是做一个移位寄存器,调用lpm库,和cycloneII元件库,也正好可以作为对前面建好的ALTERA库的一个验证。

点可以查到该模块的使用说明和详细介绍。

移位寄存器比较简单,就不用细看了。

如下图设置.点Next.4、加上一个异步清零端,点Next,再点Next,最后点Finish.Add/Remove Files in Project…,6、点图标,选中生成的lpm_shift,点打开再点Add都加到项目中去。

7、在这里直接把lpm_shift.v当成顶层文件,就不需要再例化它了。

8、下面写一个简单的TestBench.a)Quartus II工具栏上点图标,选Verilog HDL;b)点,设文件名为top_tb;c)如下所述写一个简单的TestBench.(例子见附件)开始仿真z ModelSim仿真有很多种流程,下面我采用个人感觉比较好一个流程进行仿真验证:基于工程(Project)的流程Step1 新建一个工程Step2 添加文件到工程中去Step3 编译设计文件Step4 启动仿真器,指定顶层设计单元Step5 查看和调试结果z对的设计有三个阶段的仿真。

Modelsim SE 进行时序仿真及altera库的添加

4.编译库

在主菜单中选【compile】→【compile】命令,对altera_primitives.v进行编译。

VHDL文件编译有所不同,LPM库的220model.vhd和220pack.vhd可以同时编译,MegaFunction库的先编译altera_mf_components.vhd文件,后编译altera_mf.vhd文件,Primitiv库先编译altera_primitive_components.vhd文件,后编译altera_primitive.vhd文件,元件库,如cyclone II库先编译cycloneii_atoms.vhd文件,后编译cycloneii_components.vhd文件,如果是其他系列的元件库则只要把对应的cycloneii改成其他系列的名称即可,如cyclone库则文件改为cyclone_atoms.vhd、cyclone_components.vhd或cyclone_atoms.v。

网上的很多教程都是把这些文件一起编译,这样适用于Verilog和VHDL混合仿真,但如果只用一种语言,如Verilog则完全没必要全部编译。这几个文件可分为Verilog组:220model.v、altera_mf.v、altera_primitives.v、cycloneii_atoms.v和VHDL组:220model.vhd、220pack.vhd、altera_mf.vhd、altera_mf_components.vhd,altera_primitives.vhd,altera_primitives_components.vhd,cycloneii_atoms.vhd,cycloneii_components.vhd。

在Modelsim中加入altera的仿真库

虽然这是个老话题了,但总会有刚入门的朋友不知道的。我在这里还是讲讲吧!问什么要这样做?

1、Quartus不支持Testbench

2、调用了megafunction或者lpm库之类的Altera的函数

3、时序仿真要在Modelsim下做仿真,

总会遇到上面这几个问题,因为需要在Modelsim中加入Quartus的仿真库。 Altera公司推荐的具体的做法是: 1、在Modelsim中,File->Change Directory,将工作目录改变到想要存放仿真库的地方,然后点击OK。将来产生的一大堆仿真库要用的文件就存放在这里。 2、Design->Create a New Library,建立一个新的库:Altera,点击OK。 3、Compile ..quartusedasim_lib下面的两个文件,220model.v和altera_mf.v,记得编译的时候上面的library一定是Altera。这样三步以后,就完成了在Modelsim中添加Altera的库!实际中,这样做不方便。我是这样做的。把220model.v和altera_mf.v拷贝到你要编译的文件所在的文件夹里。先编译这两个文件,等于是把Altera的器件加到了work这个library里。然后再在library下编译你要用的文件就可以了。这样方便些。

4 start compilation... ARTUS中调用Modelsim,verilog下,步骤如下,并作一说明。

1 将modelsim启动路径(如:c:modelsimmodeltechwin32;)加入到环境变量path中。

2 在quartus中建立project,并产生所用的testbench

如何在ModelSim里仿真Altera的lpm_rom文件

如何在ModelSim里仿真Altera的lpm_rom文件

By ChinaLeo on July 1st, 2005

<这里我使用的是QuartusII5.0和ModelSim SE Plus 6.0>

1.在QuartusII中生成rom的初始化文件,选择生成hex文件,因为ModelSim不支持mif

文件的转化。

这里要注意一下的是,不要擅自改动Quartus->Tools->Options->Memory Editor中的内容,默认的设置就好,不然生成的hex文件会有地址上的偏差;

2.在ModelSim安装的目录下找到modelsim.ini文件,将其只读属性去掉,在vsim部分里

添加一行“Veriuser = D:/altera/quartus50/eda/mentor/modelsim/convert_hex2ver.dll”,保存文件,将只读属性改回来。

当然,这里的路径要改成实际上您Quartus的安装路径。

其中的convert_hex2ver.dll就是把hex文件转换成ModelSim能认出来的ver文件的动态链接库文件;

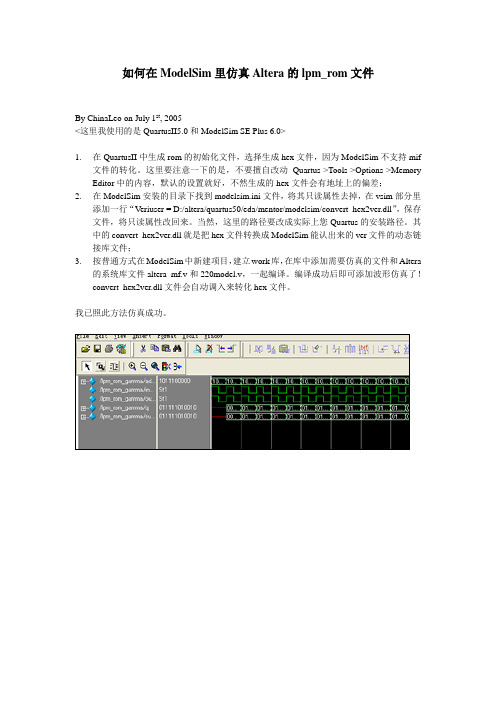

3.按普通方式在ModelSim中新建项目,建立work库,在库中添加需要仿真的文件和Altera

的系统库文件altera_mf.v和220model.v,一起编译。

编译成功后即可添加波形仿真了!

convert_hex2ver.dll文件会自动调入来转化hex文件。

我已照此方法仿真成功。

利用ModelSim SE6.0C实现时序仿真

1) 打开一个工程文件。

2) 打开Settings设置栏,选择EDA Tools Settings下的Simulation栏。

在右边出现的设置栏中将“Toolname”的下拉菜单选择“ModelSim(Verilog)”(如果工程用VHDL语言实现,则可以选择“ModelSim(VHDL)”;如果ModelSim使用的是for Altera的专用版本,则可以选择“ModelSim-Altera(Verilog)”或“ModelSim-Altera(VHDL)”)。

另外在设置栏中还有其他的核选框。

1. 如果选中“Maintain hierarchy”,则表示在做时序仿真时就能看到像在功能仿真的工程文件层次结构,可以找到定义的内部信号。

因为在做后仿时,源文件中的信号名称已经没有了,被映射为软件综合后自己生成的信号名,观察起来很不方便。

这个设置与ISE里综合右键属性的Keep Hierarchy选择YES的功能是一样的。

2. 如果选中“Generate netlist for functional simulation only”,则表示只能做功能仿真。

3) 点击“Start Compilation”按钮编译工程,完成之后在当前的工程目录下可以看到一个名为“Simulation”的新文件夹,下面的“ModelSim”文件夹下包括仿真需要的.vo网表文件和包含延迟信息的.sdo 文件。

4) 打开ModelSim软件(或者在Quartus下“Settings->EDA Tools Setting->Simulation”出现的设置栏中选中“Run this tool automatically after compilation”,直接从Quartus下调用ModelSim软件),可以在当前工程目录下新建一个Project。

在Project标签栏内点击右键,出现在快捷菜单中选择“Add toProject->Existing File…”。

在ModelSimSE中添加ALTERA仿真库的详细步骤

ModelSim学习笔记(二)在ModelSimSE中添加ALTERA仿真库的详细步骤黄俊April 2007以前用的是LATTICE的,ispLEVER有自带了一个OEM版的ModelSim。

要仿真时,不需要添加库,用起来比较方便,自己有点懒,所以就一直凑合着用。

现在转向用ALTERA 了,ALTERA也有OEM版的ModelSim,也不用添加库。

后来听说ModelSim SE的功能更强大,速度更快,所以就决定把ModelSim SE好好摸索一下,再多学习一点关于TestBench 技巧方面的知识。

我的学习资料主要是ModelSim SE自带的教程、ALTERA提供的资料以及edacn上面ModelSim专栏由网友们上传的资料。

因为是初学,加上看到英文资料一大堆,烦都烦死,而有些中文文档可能是有些步骤没有讲清楚,我实际按照文档上面说的一步一步做下来也老是完成不了,花了不少时间。

我于是就想自己摸清楚后,把步骤截图下来,整理清楚,做成笔记。

一方面加深自己的认识,另一方面对初学者也许会有些许用处。

我近期计划陆续整理出以下几个方面的学习笔记:初学ModelSimSE时被迷糊了几天的若干概念在ModelSimSE中添加ALTERA仿真库的详细步骤用ModelSimSE进行功能仿真和时序仿真的方法(ALTERA篇)ModelSimSE中常用到的几个命令及DO文件的学习笔记近来学到的几招TestBench的技巧MSN: paulhuang_sz@E-mail: huangjun5927@Blog: /index.php/2599在ModelSimSE中添加ALTERA仿真库的详细步骤装仿真库前要先了解几个概念1、装ModelSim之前,要先装QuartusII。

安装好QuartusII后,在其安装目录下…\quartus\eda\sim_lib里面存放了所有的仿真原型文件(simulation modelfiles)。

用ISE与Modelsim进行FPGA后仿真(时序仿真)的两种方法

用ISE与Modelsim进行FPGA后仿真(时序仿真)的两种方法作者:毕成炜2012年1月30日星期一我使用的是ISE_12.2,集成MODELSIM_6.5e。

后仿真的方法分为直接和间接两种。

直接是指从ISE上起动MODELSIM。

间接是单独起动MODELSIM,然后使用ISE生成的用于后仿的文件夹netgen。

下面分别叙述。

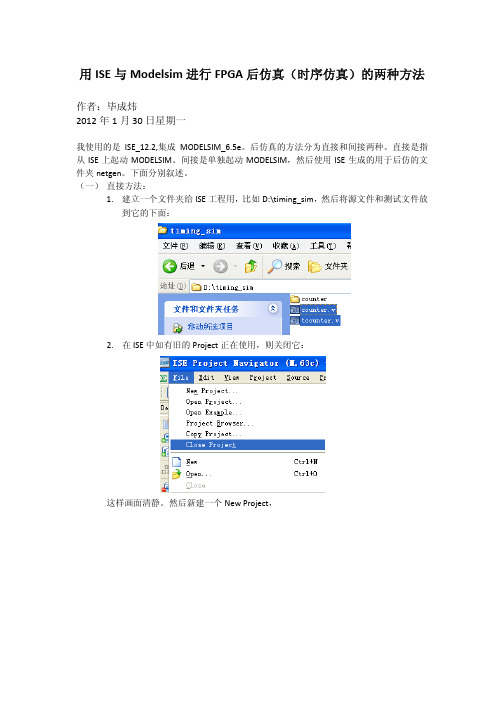

(一) 直接方法:1.建立一个文件夹给ISE工程用,比如D:\timing_sim,然后将源文件和测试文件放到它的下面:2.在ISE中如有旧的Project正在使用,则关闭它:这样画面清静。

然后新建一个New Project,点Next,选好器件和仿真器:点Next,点Finish.为了能够在ISE中直接唤起MODELSIM,还需要一些设置,主要是两处:双击器件:保证下图红圈处选中你要的仿真器:点OK后,在主菜单中点:保证在红圈处指定好MODELSIM执行文件所在的位置编译仿真库可以在这里双击Compile HDL Simulation Libraries,也可以在C:\Xilinx\12.2\ISE_DS\ISE\bin\nt下面找到,双击它,注意红圈处所标的是你的ISE版本所支持的MODELSIM版本,不能低于它。

否则仿真过程可能出问题。

点Next,点Next,选定你针对什么器件编译仿真库,点Next,点Next,注意,ISE可能最初不带modelsim.ini,它在此步会自动生成这个文件,并且是可写的,即它的“只读”属性是已经自动去掉的。

生成仿真库的映射关系自动写入了ISE的这个modelsim.ini,位于C:\Xilinx\12.2\ISE_DS\ISE\bin\nt,但是,它并不会自动去更新MODELSIM软件的modelsim.ini,而且MODELSIM使用的是它自己的modelsim.ini,位于C:\modeltech_6.5e。

所以需要把ISE的modelsim.ini中的映射关系再COPY到MODELSIM自己的modelsim.ini中。

在modelsim se中编译altera仿真库

在Modelsim SE中编译Altera仿真库本文基于Modelsim 6.1 SE版本,详细讲述了如何在Modelsim SE中编译Altera的VHDL 仿真库的过程(Verilog仿真库与此类似)。

然后修改modelsim.ini文件,使得每次新建工程的时候不需要再重新编译Altera仿真库。

1.从主菜执行File→New→Library命令,如图1 新建库所示.图1 新建库2.执行完第一步后,弹出图2对话框。

选中a new library and a logical mapping to it,LibraryName填写altera_mf,Library Physical Name填写$MODEL_TECH\altera_lib\vhdl\altera_mf(注:建议编译后的VHDL库文件存放在Modelsim安装目录\altera_lib\vhdl的文件夹下,本文中的Modelsim安装目录为C 盘根目录)。

如图2 创建库所示。

3.点击OK,如下图所示。

图3. 创建库后的图示4.从主菜单执行Compile→Compile…命令,弹出一个对话框,点中Library下拉菜单,由work改为altera_mf,点中查找范围下拉菜单,指向Quartus II安装目录\quartus60\eda\sim_lib,选中altera_mf.vhd和altera_mf_components.vhd文件,然后点击Compile按钮。

图4 编译altera_mf.vhd和altera_mf_components.vhd文件5.编译结束后,点击Done按钮。

接下来建立库lpm,步骤与1~5类似。

6.从主菜执行File→New→Library命令,如图1 新建库所示.7.执行完上一步后,弹出图2对话框。

选中a new library and a logical mapping to it,LibraryName填写lpm,Library Physical Name填写$MODEL_TECH\altera_lib\vhdl\lpm(注:建议编译后的VHDL库文件存放在Modelsim安装目录\altera_lib\vhdl的文件夹下,本文中的Modelsim安装目录为C盘根目录)。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

用ModelSimSE进行 功能仿真和时序仿真的方法 (ALTERA篇)黄俊April 2007用ModelSim SE进行功能仿真和时序仿真的方法 (ALTERA篇)软件准备(1) QuartusII,本文截图是QuartusII 6.1界面的。

我个人认为,如果是开发StratixII或CycloneII或MAXII,用QuartusII6.0+SP1+SP2比较稳定。

(2) ModelSim SE. ALTERA仿真库要已经装好,安装仿真库的笔记已记录于《在ModelSimSE中添加ALTERA仿真库的详细步骤》中。

我电脑上装的是ModelSim SE6.1b。

例子程序的制作先在Quartus II里生成一个例子程序,以方便介绍三种仿真的方法。

步骤如下:1、新建一个工程(Project),工程名取lpm_shift, 器件选CycloneII EP2C5Q208C, 第三方的工具暂时都不选。

2、菜单栏上ToolsÆMegaWizard Plug-In Manager, 点Next,在storage中选LPM_SHIFTREG,输出文件格式根据习惯选一种语言,在这里以Verilog的为例,在右边的output file名字中加上lpm_shift。

点Next。

3、这个例子是做一个移位寄存器,调用lpm库,和cycloneII元件库,也正好可以作为对前面建好的ALTERA库的一个验证。

点可以查到该模块的使用说明和详细介绍。

移位寄存器比较简单,就不用细看了。

如下图设置.点Next.4、加上一个异步清零端,点Next,再点Next,最后点Finish.Add/Remove Files in Project…,6、点图标,选中生成的lpm_shift,点打开再点Add都加到项目中去。

7、在这里直接把lpm_shift.v当成顶层文件,就不需要再例化它了。

8、下面写一个简单的TestBench.a)Quartus II工具栏上点图标,选Verilog HDL;b)点,设文件名为top_tb;c)如下所述写一个简单的TestBench.(例子见附件)开始仿真z ModelSim仿真有很多种流程,下面我采用个人感觉比较好一个流程进行仿真验证:基于工程(Project)的流程Step1 新建一个工程Step2 添加文件到工程中去Step3 编译设计文件Step4 启动仿真器,指定顶层设计单元Step5 查看和调试结果z对ALTERA的设计有三个阶段的仿真。

一是纯粹的功能仿真;二是综合后的功能仿真;三是布局布线后的时序仿真。

z下面就分别进行介绍。

纯粹的功能仿真1、新建一个工程a)打开ModelSim SE;b)新建工程,FileÆNewÆProject…:c)输入工程名,指定工程保存路径。

为了可以分别清楚地对三种仿真进行验证,我建立了三个文件夹,func、Psyth、 PAR分别来当功能仿真,综合后功能仿真以及布局布线后时序仿真的工程保存文件夹。

在这些文件夹内,我又建立了source文件夹,专门用来存放输入文件。

将前面建立的lpm_shift.v(HDL源文件)和top_tb.v (Testbench文件)拷贝至func/source里面。

将top_tb.v拷贝至Psyth、PAR里的source 文件夹内。

在这里先点Browse…,将工程的保存路径指定到func文件夹内。

d)点Add Existing File,添加输入文件。

e)在Project的空白处,点右键也可以再添加存在的文件的方式添加输入文件。

2、添加文件到工程中去进行功能仿真需要的输入文件:z HDL文件;z TestBench文件;z仿真原型文件(在这时就添加进来)或预编译的库文件(仿真时指定);点Add Existing File添加lpm_shift.v(HDL源文件),top_tb.v (Testbench文件);再到QuartusII安装目录下..\altera\61\quartus\eda\sim_lib里面找到仿真原型文件220model.v;用Reference from current location是链接的方式指定这些输入文件,copyto project directory是把输入文件复制到当前工程目录下。

建议还是用Reference form current location。

3、编译设计文件;选中一个文件,点右键,选择CompileÆCompile All;4、启动仿真器,指定顶层设计单元;a)进SimulateÆStart Simulation…b)展开Work库,指定Testbench,点OK开始仿真;直接在仿真的时候指定就行了。

a)将Wave窗口打开,查看仿真波形:b)将需要查看的信号拖入波形窗口,可以用Ctrl或Shift键多选。

c)运行。

在下面的命令行中输入运行的时间,回车。

d)查看结果:点图标,最大化波形窗口。

e)功能仿真的特点。

点图标,在波形窗口下,按住左键不放,向右下斜拉可以选择一个放大的区域:f)放大后可以看到,完全是没有延时的。

这就是纯粹的功能仿真。

6、ModelSim的其它使用技巧不在本文讨论范围之内,在这里就不介绍了。

在这里只是列出几个常用按钮的作用。

a),,,,,,,,这几个都是非常常见的图标了,分别是新建新的源文件,打开文件对话框,保存,打印,剪切,复制,贴粘,撤消最后一步操作,在当前窗口查找文本。

在这里和下文提到的当前窗口,均可靠点击某窗口的任何位置选择。

当前窗口听标题栏会以亮的蓝色显示。

b),编译,打开文件对话框,选择HDL源文件,把该源文件编译到当前工程的工作库中。

c),全编译。

编译当前工程中的所有文件。

d),仿真。

e),停止仿真。

f),回到上一层。

g),重新仿真。

装载设计,并将仿真复位到零,重新仿真。

h),设定单步仿真步长。

i),运行当前仿真。

在该仿真时间长度内进行仿真。

j),继续仿真,直到仿真结束,或用户停止仿真。

k),运行所有仿真,直到仿真结束或用户停止仿真。

l),添加一条坐标轴。

m),删除一条坐标轴。

综合后功能仿真1、新建一个工程方法前面讲过了,这次将路径保存到…/modelsim/Psyth里。

2、添加文件到工程中去进行综合后功能仿真需要的输入文件:z在QuartusII里面生成的网表文件;z TestBench文件;z仿真原型文件(在这时就添加进来)或预编译的库文件(仿真时指定)。

在QuartusII里面生成网表文件的方法:a)点工具栏上的图标,选EDA Tool Setting, 双击Simulation。

b)设置ModelSim, 输出网表的格式,以及网表文件保存的路径。

c)点,将Generate netlist for functional simulation only设置为ON。

d)点OK,保存。

点工具栏上的图标,进行全编译。

e)检查一下…/modelsim/Psyth/source里面,可以发现,已经生成了一个*.vo文件。

这个就是需要的网表文件。

(VHDL的输出网表是*.vho后缀名的)f)在这里,TestBench文件就继续用前面功能仿真里用的top_tb.v文件;g)我们试一下直接指定预编译的库。

3、编译设计文件(略)4、启动仿真器,指定顶层设计单元方法就不重复了。

指定时参考以下截图。

这次选库的时候选元件库。

5、查看和调试结果可以看到,load在装载时,输出q延时一个时钟周期才输出,但它和输入时钟的边沿还是完全同步的。

布局布线后时序仿真步骤和综合后功能仿真大同小异,有以下几点要注意:(1)进行布线后时序仿真需要的输入文件:z布局布线后网表;z延时文件*.sdo(Verilog)或*_vhd.sdo(VHDL);z TestBench文件;z仿真原型文件(在这时就添加进来)或预编译的库文件(仿真时指定);QuartusII里面设置重新把Generate netlist for functional simulation only设置成OFF。

全编译后,除了生成布局布线后网表文件以外,还会生成延时文件。

(2) 依然要指定库文件的位置;(3) 指定延时文件时,在下图位置指定延时文件。

(4) 需要注意两点:a)对Verilog设计的仿真,延时文件需要复制到ModelSim里面建的Project的根目录下。

这一点,我也搞不明白,试了很久才发现的,可能是我没有设置好的问题,也可能是这个版本本身的Bug。

对VHDL设计,就不需要复制到ModelSim里面建的Project的根目录下。

b)指定Apply to Region里面,还要写TestBench里面例化顶层文件的例化名。

(5) 查看仿真波形,q的输出就显示了延时。

(完)。