时序计算和Cadence 仿真结果的运用

Cadence DDR总线仿真技术

Cadence Allegro Bus Simulation总线仿真——源同步分析孙海峰随着电子设计的快速进步,总线速度的提高在PCB上的实现越来越难,这样就催生了新的不受时钟制约的时序系统,即源同步时序系统。

源同步时序系统最大的优点,就是大大提升了总线的速度,在理论上信号的传送可以不受传输延迟的影响。

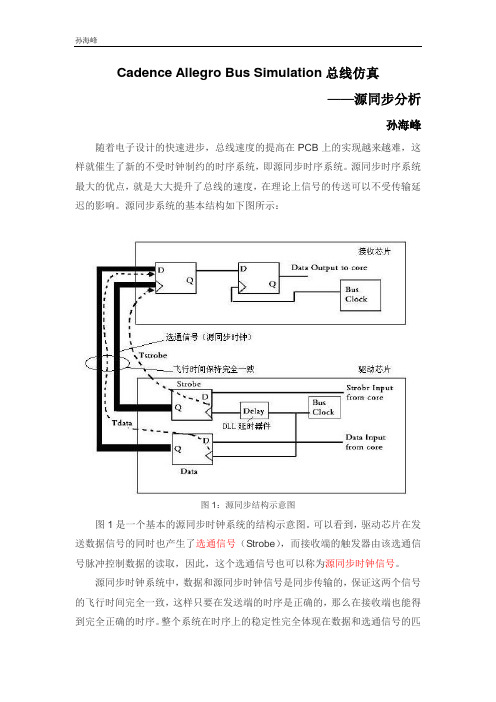

源同步系统的基本结构如下图所示:图1:源同步结构示意图图1是一个基本的源同步时钟系统的结构示意图。

可以看到,驱动芯片在发送数据信号的同时也产生了选通信号(Strobe),而接收端的触发器由该选通信号脉冲控制数据的读取,因此,这个选通信号也可以称为源同步时钟信号。

源同步时钟系统中,数据和源同步时钟信号是同步传输的,保证这两个信号的飞行时间完全一致,这样只要在发送端的时序是正确的,那么在接收端也能得到完全正确的时序。

整个系统在时序上的稳定性完全体现在数据和选通信号的匹配程度上,包括传输延迟的匹配,器件性能的匹配等等,只要两者完全匹配,那么我们就可以保证系统时序的绝对正确,。

然而,在实际的PCB设计中,我们往往不可能观察到总线与选通信号的匹配程度,我们就需要借助新的设计仿真软件,来实现这个功能,就此Cadence 顺应电子设计的大潮流,推出了DDR总线仿真工具Bus Simulation用以进行源同步分析仿真。

那么Cadence软件是如何来实现PCB的源同步时序分析的呢,接下来,我将详细阐述这个过程。

1、进入Cadence Allegro SI仿真界面,如下图所示:2、点击OK进入SI仿真界面,并完成SI仿真基本流程,包括:模型库添加、模型赋予、DC网络值定义等等。

图2:模型库添加与管理图3:模型赋予图4:DC直流网络定义3、完成上述SI仿真基本步骤后,就可以开始进行SI分析,包括:反射、串扰、EMI、通道分析等等,这里就不再赘述。

这里主要介绍的是新的PCB源同步时序分析工具Bus Simulation,该总线仿真针对DDR的总线进行源同步时序分析。

数字电路仿真与验证

数字电路仿真与验证数字电路是现代电子技术的基础,广泛应用于计算机、通信和其他电子设备中。

数字电路的设计和验证是确保电路能够按照预期工作的关键步骤。

本文将介绍数字电路仿真与验证的重要性以及常用的方法和工具。

一、数字电路仿真的意义数字电路的设计过程复杂且耗时,因此在将其实际制造之前,必须通过仿真来验证其功能和性能。

数字电路仿真的主要目的是通过计算机模拟电路行为,检查其逻辑功能、时序性能和稳定性。

具体来说,仿真可以帮助设计师发现和解决潜在的问题,减少设计错误和重复制造的风险,提高电路设计的可靠性和效率。

二、数字电路仿真的方法1. 行为级仿真:行为级仿真是通过对数字电路的逻辑功能进行建模和测试。

在这种仿真方法中,电路的输入和输出通过逻辑信号表示,并在仿真器中进行模拟计算。

这种仿真方法可以验证电路是否满足设计要求,并帮助发现逻辑错误。

2. 时序级仿真:时序级仿真是针对时序电路设计的一种仿真方法。

时序电路涉及时钟信号和时序逻辑,需要确保电路正确地响应时钟的上升沿和下降沿。

时序级仿真可以验证时序电路的时序特性,包括信号延迟、时钟抖动和稳定性等。

3. 功能级仿真:功能级仿真可以对整个数字系统进行仿真,包括多个数字电路模块的集成。

通过功能级仿真,可以验证数字系统的整体功能和性能,以及各个模块之间的接口和通信。

三、数字电路仿真工具的选择1. SPICE仿真工具:SPICE(Simulation Program with Integrated Circuit Emphasis)是一种常用的模拟电路仿真工具,可以用于数字电路的仿真。

它可以帮助设计师验证电路的逻辑和模拟行为,并检查电路的时序特性。

2. HDL仿真工具:HDL(Hardware Description Language)仿真工具是专门用于数字电路设计的仿真工具。

常用的HDL语言包括VHDL (VHSIC Hardware Description Language)和Verilog HDL。

cadence简介和使用基础

CMOS电路原理图设计

或者CIW窗口→File→Open(打开已有的 Cellview)。

CMOS电路原理图设计

也可以在Library Manager中直接打开。

Cadence的使用基础

双击Schematics,出现原理图编辑器

Cadence的使用基础

之后出现Symbol Generation Options窗口。

Cadence的使用基础

出现界面:

Cadence的使用基础

可将上图修改为惯用图形,以CMOS反相器为例。

CMOS电路原理图设计

电路仿真 仿真环境简介

Schematic图形窗口→Tools→Analog Environment。

Cadence的使用基础

Cadence的使用基础

基本工作环境

局域网资源

Cadence的使用基础

用户登陆 微机登陆后,点击桌面X-manager 图标,

Cadence的使用基础

打开X-manager图标后,点击xstart 图标,出现对话 框,进行如下设置:

Cadence的使用基础

登录时出现Linux-CDE (Common Desktop Environment) 界面

一、 cadence简介和使用

集成电路设计软件技术介绍

EDA技术的概念

EDA技术是在电子CAD技术基础上发展起来 的计算机软件系统,是指以计算机为工作平台, 融合了应用电子技术、计算机技术、信息处理 及智能化技术的最新成果,进行电子产品的自 动设计

EDA工具的功能

利用EDA工具,电子设计师可以从概念、算法、 协议等开始设计电子系统,大量工作可以通过 计算机完成,并可以将电子产品从电路设计、

时序的计算与仿真

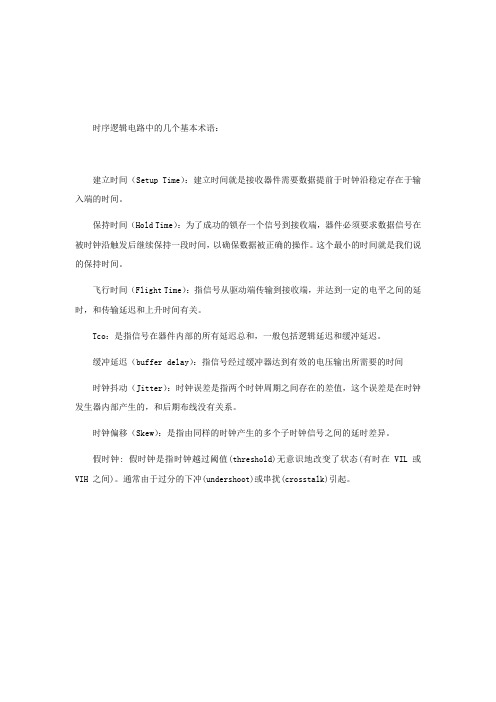

时序逻辑电路中的几个基本术语:建立时间(Setup Time):建立时间就是接收器件需要数据提前于时钟沿稳定存在于输入端的时间。

保持时间(Hold Time):为了成功的锁存一个信号到接收端,器件必须要求数据信号在被时钟沿触发后继续保持一段时间,以确保数据被正确的操作。

这个最小的时间就是我们说的保持时间。

飞行时间(Flight Time):指信号从驱动端传输到接收端,并达到一定的电平之间的延时,和传输延迟和上升时间有关。

Tco:是指信号在器件内部的所有延迟总和,一般包括逻辑延迟和缓冲延迟。

缓冲延迟(buffer delay):指信号经过缓冲器达到有效的电压输出所需要的时间时钟抖动(Jitter):时钟误差是指两个时钟周期之间存在的差值,这个误差是在时钟发生器内部产生的,和后期布线没有关系。

时钟偏移(Skew):是指由同样的时钟产生的多个子时钟信号之间的延时差异。

假时钟: 假时钟是指时钟越过阈值(threshold)无意识地改变了状态(有时在VIL 或VIH 之间)。

通常由于过分的下冲(undershoot)或串扰(crosstalk)引起。

数据上升沿对于系统设计工程师来说,时序问题在设计中是至关重要的,尤其是随着时钟频率的提高,留给数据传输的有效读写窗口越来越小,要想在很短的时间限制里,让数据信号从驱动端完整地传送到接收端,就必须进行精确的时序计算和分析。

同时,时序和信号完整性也是密不可分的,良好的信号质量是确保稳定的时序的关键,由于反射,串扰造成的信号质量问题都很可能带来时序的偏移和紊乱。

因此,对于一个信号完整性工程师来说,如果不懂得系统时序的理论,那肯定是不称职的。

本章我们就普通时序和源同步系统时序等方面对系统时序的基础知识作一些简单的介绍。

6.1 普通时序系统所谓普通时序系统就是指驱动端和接收端的同步时钟信号都是由一个系统时钟发生器提供。

下图就是一个典型的普通时钟系统的示意图,表示的是计算机系统的前端总线的时序结构,即处理器(CPU)和芯片组(Chipset)之间的连接。

CADENCE仿真流程

CADENCE仿真流程1.设计准备在进行仿真之前,需要准备好设计的原理图和布局图。

原理图是电路的逻辑结构图,布局图是电路的物理结构图。

此外,还需要准备好电路的模型、方程和参数等。

2.确定仿真类型根据设计需求,确定仿真类型,包括DC仿真、AC仿真、时域仿真和优化仿真等。

DC仿真用于分析直流电路参数,AC仿真用于分析交流电路参数,而时域仿真则用于分析电路的时间响应。

3.设置仿真参数根据仿真类型,设置仿真参数。

例如,在DC仿真中,需要设置电压和电流源的数值;在AC仿真中,需要设置信号源的频率和幅度;在时域仿真中,需要设置仿真的时间步长和仿真时间等。

4.模型库选择根据设计需求,选择合适的元件模型进行仿真。

CADENCE提供了大量的元件模型,如晶体管、二极管、电感、电容等。

5.确定分析类型根据仿真目标,确定分析类型,例如传输功能分析、噪声分析、频率响应分析等。

6.仿真运行在仿真运行之前,需要对电路进行布局和连线。

使用CADENCE提供的工具对电路进行布局和连线,并生成物理设计。

7.仿真结果分析仿真运行后,CADENCE会生成仿真结果。

利用CADENCE提供的分析工具对仿真结果进行分析,观察电路的性能指标。

8.优化和修改根据仿真结果,对电路进行优化和修改。

根据需要,可以调整电路的拓扑结构、参数和模型等,以改进电路的性能。

9.再次仿真和验证根据修改后的电路,再次进行仿真和验证,以确认电路的性能指标是否得到改善。

最后需要注意的是,CADENCE仿真流程并不是一成不变的,根据具体的设计需求和仿真目标,流程可能会有所调整和修改。

此外,CADENCE还提供了许多其他的工具和功能,如电路板设计、封装设计、时序分析等,可以根据需要进行使用。

cadence原理图仿真

cadence原理图仿真首先,我们来了解一下cadence原理图仿真的基本原理。

在进行原理图仿真时,我们需要将电路设计转换为一个数学模型,然后利用计算机软件对这个模型进行求解,得到电路的各种参数和性能指标。

这个数学模型通常是由电路的基本元件和它们之间的连接关系构成的,通过建立节点方程和元件特性方程,可以得到一个包含了电路各种参数的数学方程组。

然后利用数值计算方法对这个方程组进行求解,就可以得到电路的各种性能指标,比如电压、电流、功率等。

在cadence原理图仿真中,我们通常会使用一些常见的仿真工具,比如SPICE仿真器。

SPICE是一种通用的电路仿真工具,它可以对各种类型的电路进行仿真,包括模拟电路、混合信号电路和射频电路等。

通过建立电路的原理图,并在仿真器中设置各种参数和仿真条件,就可以对电路进行仿真分析,得到电路的各种性能指标。

在进行cadence原理图仿真时,我们需要注意一些关键的仿真参数和设置。

首先是仿真的时间步长和仿真的时间范围,这两个参数会直接影响到仿真的精度和速度。

通常情况下,我们需要根据电路的特性和仿真的要求来合理地设置这两个参数,以保证仿真结果的准确性。

另外,还需要注意仿真的激励信号和仿真的分析类型,比如直流分析、交流分析、脉冲分析等,这些参数会直接影响到仿真的结果和分析的内容。

除了基本的仿真参数设置,我们还需要注意一些特殊情况下的仿真技巧。

比如在进行混合信号电路的仿真时,需要考虑模拟部分和数字部分之间的接口和耦合关系,以保证整个系统的稳定性和正确性。

另外,在进行射频电路的仿真时,需要考虑传输线的特性和电磁场的影响,以保证仿真结果的准确性和可靠性。

总的来说,cadence原理图仿真是电子设计中非常重要的一环,它可以帮助工程师们验证电路设计的正确性和稳定性,提前发现潜在的问题,从而节省时间和成本。

通过合理地设置仿真参数和注意一些特殊情况下的仿真技巧,可以得到准确可靠的仿真结果,为电路设计和调试提供有力的支持。

cadence几种模式的用法

Cadence几种模式的用法什么是CadenceCadence是一种分布式系统编程框架,由Uber Technologies开发并开源。

它旨在帮助开发人员构建可靠、可扩展、可维护的分布式应用程序。

Cadence提供了一种声明式的方式来定义和执行工作流,使开发人员能够专注于业务逻辑而不必担心底层的复杂分布式系统细节。

Cadence的几种模式Cadence提供了几种模式,每种模式都有不同的用途和适用场景。

下面将介绍Cadence的几种模式及其用法。

1. Batch模式Batch模式是Cadence中最常见的模式之一。

它适用于需要处理大量数据的场景,如数据清洗、数据转换、数据分析等。

在Batch模式下,Cadence将任务分为多个小的子任务,并按照一定的顺序执行。

每个子任务可以并行执行,从而提高整体的处理效率。

使用Batch模式时,可以使用Cadence提供的批处理工具来处理大规模数据。

这些工具提供了丰富的功能,如数据输入输出、任务调度、错误处理等。

开发人员只需定义数据处理的逻辑,而无需关心底层的分布式系统细节。

2. Real-time模式Real-time模式是Cadence中用于处理实时数据的模式。

它适用于需要及时响应用户请求的场景,如实时推荐、实时监控、实时报警等。

在Real-time模式下,Cadence使用事件驱动的方式来处理任务,即根据事件的发生来触发相应的任务执行。

使用Real-time模式时,可以定义事件的触发条件和任务的执行逻辑。

当满足触发条件时,Cadence会自动执行相应的任务,并根据需要进行并行处理。

开发人员可以根据实际需求来灵活配置事件和任务,以达到最佳的实时处理效果。

3. Stream模式Stream模式是Cadence中用于处理流式数据的模式。

它适用于需要处理连续生成的数据流的场景,如实时日志分析、实时数据流处理等。

在Stream模式下,Cadence使用流式处理的方式来处理任务,即按照数据流的先后顺序逐个处理任务。

Cadence的使用与基本仿真教程

Cadence的使用与基本仿真教程2014/11/9模拟集成电路设计课程实验1Outline启动Cadence新建Library 与Cell View常用快捷键常用库常用库、、器件基本仿真基本仿真指导指导仿真练习a)CS,CG,SF 电路仿真b)差分差分对电路仿真对电路仿真c)CS-CG 电路仿真2014/11/9模拟集成电路设计课程实验2启动Cadence在桌面上鼠标右击在桌面上鼠标右击,,open terminal >cd ~(回到home 目录下)>icfb &启动Cadence 。

上课时部分同学遇到问题是由于没有在home 目录下打开Cadence 2014/11/9模拟集成电路设计课程实验3新建LibraryFile>new>library2014/11/9模拟集成电路设计课程实验4新建Library起个名字>Don’t need a techfile>OK2014/11/9模拟集成电路设计课程实验5打开Library ManagerTools>Library Manager2014/11/9模拟集成电路设计课程实验6显示器件分类Show Category可以显示器件的分类2014/11/9模拟集成电路设计课程实验7显示器件分类例如例如::在tsmc018rf 库中的分类有库中的分类有::电容电容、、电阻电阻、、MOS 管等等管等等。

2014/11/9模拟集成电路设计课程实验8新建Cell ViewFile>New>Cell View2014/11/9模拟集成电路设计课程实验9新建Cell View将新建的Cell View 设定在之前新建的Library 下>起个名字>OK 2014/11/9模拟集成电路设计课程实验10快捷键快捷键::i2014/11/9模拟集成电路设计课程实验11快捷键快捷键::w2014/11/9模拟集成电路设计课程实验12快捷键快捷键::c2014/11/9模拟集成电路设计课程实验13快捷键快捷键::q2014/11/9模拟集成电路设计课程实验14快捷键快捷键::r2014/11/9模拟集成电路设计课程实验15常用库常用库、、器件2014/11/9模拟集成电路设计课程实验16搭建反相器仿真电路照图搭建反相器仿真电路2014/11/9模拟集成电路设计课程实验17设置PMOS参数:参数:设置PMOS参数将w设置为6μm2014/11/9模拟集成电路设计课程实验18设置电压源vpulse 参数设置vpulse 参数参数::AC magnitude :1DC voltage:Vdc (设为变量Vdc )Voltage 1:0Voltage 2:1.8Pulse width :1nPeriod:2n注意注意::AC 参数的设置不会影响直流工作点DC voltage 决定直流工作点决定直流工作点;;下面四个参数设置时域波形,不影响直流不影响直流。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

时序计算和Cadence仿真结果的运用中兴通讯康讯研究所EDA设计部余昌盛刘忠亮摘要:本文通过对源同步时序公式的推导,结合对SPECCTRAQuest时序仿真方法的分析,推导出了使用SPECCTRAQuest进行时序仿真时的计算公式,并对公式的使用进行了说明。

关键词:时序仿真源同步时序电路时序公式一.前言通常我们在时序仿真中,首先通过时序计算公式得到数据信号与时钟信号的理论关系,在Cadence仿真中,我们也获得了一系列的仿真结果,怎样把仿真结果正确的运用到公式中,仿真结果的具体含义是什么,是我们正确使用Cadence仿真工具的关键。

下面对时序计算公式和仿真结果进行详细分析。

二.时序关系的计算电路设计中的时序计算,就是根据信号驱动器件的输出信号与时钟的关系(Tco——时钟到数据输出有效时间)和信号与时钟在PCB上的传输时间(Tflytime)同时考虑信号驱动的负载效应、时钟的抖动(Tjitter)、共同时钟的相位偏移(Tskew)等,从而在接收端满足接收器件的建立时间(Tsetup)和保持时间(Thold)要求。

通过这些参数,我们可以推导出满足建立时间和保持时间的计算公式。

时序电路根据时钟的同步方式的不同,通常分为源同步时序电路(Source-synchronous timing)和共同时钟同步电路(common-clock timing)。

这两者在时序分析方法上是类似的,下面以源同步电路来说明。

源同步时序电路也就是同步时钟由发送数据或接收数据的芯片提供。

图1中,时钟信号是由CPU驱动到SDRAM方向的单向时钟,数据线Data是双向的。

图1图2是信号由CPU 向SDRAM 驱动时的时序图,也就是数据与时钟的传输方向相同时的情况。

Tsetup ’Thold ’ CPU CLK OUTSDRAM CLK INCPU Signals OUT SDRAM Signals INTco_minTco_max T ft_clkT ft_dataT cycleSDRAM ’S inputs Setup time SDRAM ’S inputs Hold time图2图中参数解释如下:■ Tft_clk :时钟信号在PCB 板上的传输时间;■ Tft_data :数据信号在PCB 板上的传输时间;■ Tcycle :时钟周期■ Tsetup’:数据到达接收缓冲器端口时实际的建立时间;■ Thold’:数据到达接收缓冲器端口时实际的保持时间;■ Tco_max/Tco_min :时钟到数据的输出有效时间。

由图2的时序图,我们可以推导出,为了满足接收芯片的Tsetup 和Thold 时序要求,即Tsetup’>Tsetup 和Thold’>Thold ,所以Tft_clk 和Tft_data 应满足如下等式:Tft_data_min > Thold – Tco_min + Tft_clk (公式1) Tft_data_max < Tcycle - Tsetup – Tco_max + Tft_clk (公式2)当信号与时钟传输方向相反时,也就是图1中数据由SDRAM 向CPU 芯片驱动时,可以推导出类似的公式:Tft_data_min > Thold – Tco_min - Tft_clk (公式3) Tft_data_max < Tcycle - Tsetup – Tco_max - Tft_clk (公式4)如果我们把时钟的传输延时Tft_clk 看成是一个带符号的数,当时钟的驱动方向与数据驱动方向相同时,定义Tft_clk 为正数,当时钟驱动方向与数据驱动方向相反时,定义Tft_clk为负数,则公式3和公式4可以统一到公式1和公式2中。

三.Cadence 的时序仿真在上面推导出了时序的计算公式,在公式中用到了器件手册中的Tco 参数,器件手册中Tco 参数的获得,实际上是在某一种测试条件下的测量值,而在实际使用上,驱动器的实际负载并不是手册上给出的负载条件,因此,我们有必要使用一种工具仿真在实际负载条件下的信号延时。

Cadence 提供了这种工具,它通过仿真提供了实际负载条件下和测试负载条件下的延时相对值。

我们先来回顾一下CADENCE 的仿真报告形式。

仿真报告中涉及到三个参数:FTSmode 、SwitchDelay 和SettleDelay 。

其中Cadence 时序仿真的结果是通过SwitchDelay 和SettleDelay 两个参数反映出来的。

在解释FTSmode 、SwitchDelay 和SwitchDelay 前先解释一下BufferDelay 曲线的含义。

BufferDelay 曲线是Cadence 仿真器断开实际负载,带上驱动芯片器件手册提供的测试负载条件下获得的一条曲线。

测试负载是在IBIS 仿真模型库中设置的。

Cadence 仿真报告中的延时测量是以BufferDelay 为基准曲线,以V Measure 为起始测量点获得的相对延时值。

FTSmode :定义了当前仿真驱动器的特性,分为Fast 、Type 和Slow 。

该三种特性是在IBIS 模型中定义的,Fast 是驱动器沿最快的模式,Slow 是驱动器沿最慢的模式,从而定义了驱动器在正常工作条件下的两种极限特性。

SwitchDelay :定义为SwitchDelayFall 和SwitchDelayRise 两者的最小值。

图3给出了SwitchDelayFall 和SwitchDelayRise 的图形解释。

SwitchDelayFall :是从BufferDelay 下降沿的Vmeasure 点开始到接收波形下降曲线第一次穿过高电平阈值时的延时值。

SwitchDelayRise :是从BufferDelay 上升沿的Vmeasure 点开始到接收波形上升曲线第一次穿过低电平阈值时的延时值。

SettleDelay :是SettleDelayFall 和SettleDelayRise 两者的最大值。

图3给出了SettleDelayFall 和SettleDelayRise 的图形解释。

SettleDelayFall :是从BufferDelay 下降沿的Vmeasure 点开始到接收波形下降曲线最后一次穿过低电平阈值时的延时值。

SettleDelayRise :是从BufferDelay 上升沿的Vmeasure 点开始到接收波形上升曲线最后一次穿过高电平阈值时的延时值。

从SwitchDelay 和SettleDelay 的定义我们可以看出,SettleDelay 是一个与输入端的建立时间(Tsetup )有关的量,SwitchDelay 是一个与输入端保持时间有关的量(Thold )。

V ih minV il maxVmeasureBufferDelay Driver WaveformReceiver WaveformSwitchDelayRise SwitchDelayFallSettleDelayFallSettleDelayRise 图3公式1和公式2中的Tft_data 与Tft_clk 在Cadence 仿真工具中是通过仿真获得的数据,它与Cadence 仿真中fast 和slow 状态下的SwitchDelay 与SettleDelay 参数有关。

为了了解Cadence 仿真中的SwitchDelay 和SettleDelay 与时序公式中参数的关系,我们重新分析一下包含有BufferDelay 曲线的时序图。

Tsetup ’Thold ’ CPU CLK OUTSDRAM CLK IN CPU Signals OUTSDRAM Signals IN(BufferDelay)(BufferDelay)Vmeas1Vmeas2 Vmeas3 VihVil Vih Vil SwitchDelay&SettleDelay Tco_max Tco_min T ft_clk= SwitchDelay= SettleDelayT ft_dataSDRAM ’S inputs Setup time SDRAM ’S inputs Hold timeT cycle图4在图4中,时钟输出和数据输出使用的是BufferDelay 曲线,此时Tco 是时钟BufferDelay 曲线和数据BufferDelay 曲线之间的延时关系,这种定义符合“手册中的Tco 是在特定负载下测得的”说法。

在图4中,CPU CLK OUT (BufferDelay )和CPU Signals OUT(Bufferdelay)是在测试负载条件下的信号输出波形(对应于图3中的BufferDelay 曲线,而不是驱动端输出曲线),SDRAM CLK IN 和SDRAM Signals IN 是在实际负载条件下输入端口的仿真波形。

在器件手册中给出时序关系时,对于时钟信号,通常以某一测量电压为时间测量点,如图4中的Vmeas1和Vmeas2,对于驱动端测量电压点为驱动器件手册中定义的测量点,对于接收端测量电压点为接收器件手册中定义的测量点。

在Cadence 仿真时,对于接收端电压测量点的设置,通常在接收器件模型中,把输入高低门限电平定义成Vmeas2来实现。

对于驱动端电压测量点的设置,是在驱动器件模型参数中设置的。

此时对于时钟仿真的结果是,时钟信号的SettleDelay 和SwitchDelay 值相等。

对于数据信号的测量点就稍微有点复杂了,这要根据手册中Tco 的测量方式来确定,有的器件手册Tco 是从时钟的Vmeas 到数据的Vmeas 来测量的,有的手册是从时钟的Vmeas 到数据的门限电平来测量的。

如果采用从时钟的Vmeas 到数据的门限电平来测量的,则在Cadence 仿真中,要对高低电平门限分别作为测量点仿真,然后取最恶劣的仿真结果。

对于公式中数据的延时Tft_data ,从Cadence 仿真中对SettleDelay 和SwitchDelay 的定义和图4中的时序关系可以看出,Tft_data 就是仿真结果中的SettleDelay 和SwitchDelay 参数,并且SettleDelay 是与建立时间(Tsetup )有关,SwitchDelay 是与保持时间(Thold )有关,因此公式中的Tft_data_min 对应仿真结果中的SwitchDelay ,Tft_data_max 对应仿真结果中的SettleDelay ,考虑到通常Slow 状态的延时比Fast 状态的延时要大,因此,公式中的Tft_data_min 对应仿真结果中Fast 状态的SwitchDelay ,Tft_data_max 对应仿真结果中Slow 状态的SettleDelay 。