sdram课程设计报告

用于测试SDRAM控制器的PDMA-设计应用

用于测试SDRAM控制器的PDMA-设计应用1引言现代电子信息设备往往需要保存和处理大量的数字信息,一个高性能的Memory控制器可以大大提高系统的性能。

在进行SDRAM 控制器的设计时,需要考虑很多因素,设计完成以后还要进行多项测试看是否完全满足所要求的各项性能,为此我们设计了一个PDMA (Programmable Direct Mem o ry Access)用于测试SDRAM控制器的性能。

在SoC中,SDRAM控制器往往跟多个IP模块(图形处理单元,音频处理单元等)交换数据,采用多个PDMA通道同时访问Memory 可以真实模拟SDRAM控制器在SoC环境中被多个IP随机访问的情形。

2 PDMA的结构及工作原理PDMA是可编程直接存储器存取的简称。

图1 虚中框内是PDMA的内部模块结构,它主要由寄存器组和控制器两大部分构成,寄存器组用于保存配置参数和PDMA对SDRMA控制器访问后的状态信息及接收、启动、停止等控制信息。

图2是PDMA寄存器组的内部结构。

寄存器组模块里包含了一个同步模块、控制寄存器、状态寄存器和各通道的寄存器组。

每一个子通道的寄存器组又包含访问基址寄存器、访问模式寄存器、周期计数器等三个寄存器。

各寄存器的功能描述如表1所示。

PDMA的控制器主要由:产生写数据的状态机、地址译码模块、FIFO以及读数据校验模块四部分构成。

各模块的功能由表2描述。

PDMA控制器的结构如图3所示,其逻辑是一个状态机,我们采用一个两层嵌套的状态机来实现控制功能,如图4所示。

3 测试系统的结构和工作原理在本设计中,PDMA用于仿真多个IP核对SDRAM控制器进行读写访问以验证SDRAM控制器的设计是否高效合理,性能是否稳定等指标。

PDMA整个测试系统由PCI接口模块、PDMA 以及SDRAM控制器三大部分构成(见图1)。

PCI接口模块与PDMA之间以内部IO总线相连接。

PDMA与SDRAM控制器之间以内部Memory总线连接。

8×8位双端口的SDRAM的设计

8×8位双端口的SDRAM的设计摘要本文介绍了一种采用数组进行8×8位双端口的SDRAM的设计方法,主要阐述如何使用新兴的EDA器件取代传统的电子设计方法,利用FPGA的可编程性,简洁而又多变的设计方法,缩短了研发周期,同时使SDRAM体积更小功能更强大。

本设计实现了SDRAM所需的一些基本功能,同时考虑到SDRAM在实际应用中的一些特殊性,更注重了把一些新的思路加入到设计中。

主要包括采用了FPGA芯片,使用VHDL语言进行编程,使其具有了更强的移植性,更加利于产品升级[1]。

关键词:VHDL;双端口SDRAM;QuartusⅡ;AbstractThis article describes the use of the array for a8x8-bit dual-port SDRAM of the design method,mainly on how to use the emerging EDA electronic device designed to replace conventional methods,the use of programmable CPLD,simple and changeable design methodology,shorten the development cycle,while SDRAM smaller and more powerful.The design of the SDRAM to achieve some of the basic functions required, taking into account the practical application of SDRAM in some specificity,but also focus on some new ideas into the design. Including the use of a CPLD chip,the use of VHDL programming language so that it will have a greater portability,and more conducive to product upgrades.文档由暴风影音2014下载/风行播放器/整理Key words:VHDL,Dual-port sdram,QuartusⅡ1绪论人类社会已经进入信息化时代,信息社会的发展离不开电子产品的进步。

SDRAM控制器课设报告完整

SDRAM控制器课设报告完整S D R A M控制器课设报告完整This model paper was revised by the Standardization Office on December 10, 2020 SDRAM控制器课设报告<姓名>北京⾄芯科技FPGA培训课程2016年4⽉30⽇星期六⽬录⼀、SDR控制器设计SDR控制器的顶层设计sdr_cs_基本需求顶层框图符号SDR 控制器的上电序列上电序列的架构设计SDR顶层设计说明:1. 突发长度BL=4,本地数据宽度=16*4=64;2. 忽略数据写掩码,DQM 始终为0 cnt=crs cmd=`NOPA[10]cnt3. 全部读写命令均使能AP顶层接⼝正常和⾮正常的写时序:sdr_ba sdr_ck sdr_dqm sdr_local_wdatlocal_local_rdatlocal_ sdr_local_clklocalocal_local_normal(正常abnormal(⾮顶层接⼝正常和⾮正常的读时序:顶层设计local_local_va don ’tlocal_va don ’tsdr_loca local_local_local_vadon ’t local_don ’tlocal_normal(正常abnormal(⾮vasdr_cs_写序列设计写序列时序:int_dq[sdr_dq[写序列模块的STG (BL=4):读序列设计(有跨时钟域问题)读序列架构:* cntcnt>=ctRCD-1****说明:1. 装配器Fitter 的fit_en 有效时,将dq_sys 装配到rdata ,此时,若fit_load=0,则装配到rdata[15:0],fit_load=1则装配到rdata[31:16],fit_load=2则装配到rdata[47:32],fit_load=3则装配到rdata[63:48]2. 再同步寄存器链的长度为2(SL=2)读序列时序设计(CL=2,BL=4,SL=2,AP 模式,ctRCD=2)crd_bus[rd_donesdr_reac inva dq_s D0 D1 D2 D3invrd_en读序列状态机设计:主控制器设计STG:!init_doneinvadq_s D0D1D2D3invfit_fit_0123rdat15314763:*cntt1cnt>=ctRCD-1cntt3cnt>=CL+SL-1****S1部分算法流程图ASM charts:⼆、DDR2控制器设计编写⾃⼰的控制器顶层设计说明:1. 突发长度BL=4,本地数据宽度=16*4=64;2. 忽略数据写掩码,DQM 始终为0 3. 全部读写命令均使能APwrreq wr_en=1!wr_dref_time>=wrrref_顶层架构ddr_rddr_cddr_a[ddr_baddr_ckddr_dqddr_dm[ddr_global_rlocal_adlocal_wdatlocal_local_rdatlocal_local_clkddr_odddr_clddr_dqint_ddr_cwriteclk row_aba_a rdatwr_dowr_eddr_c ddr_ccontrol_ control_ control_control_postamblesoft_resemux_s使⽤Altera 的IP 核(DDR2 HPCII ,数据块搬运模块例⼦)说明(基本需求):1. 使⽤DDR2 HPCII 构建的数据搬运模块initwr_do mux_s dll_add dll_off row_a col_a ba_awdat rdatddr2_driversoft_rescl2. 本地突发长度设置为4(local_size=4)3. 全速运⾏设置4. DDR2器件采⽤16位宽,4Bank ,速度667Mbps ,存储器时钟333MHz5. 数据搬运尺⼨设置为LPM 参数DEPTH=512,即512本地字(全速情况下字宽为32)6. 数据搬运模块具有块搬运启动命令start 。

Gzip中的DDR2SDRAM控制器的设计中期报告

Gzip中的DDR2SDRAM控制器的设计中期报告设计目的:本文是对Gzip中DDR2SDRAM控制器的设计中期报告,目的是汇总和记录该控制器的设计过程、设计思路、设计原理和实现方法,以及在设计过程中遇到的问题和解决方案。

通过此次设计,可以让读者了解到DDR2SDRAM的控制器设计步骤和基本原理,熟悉Verilog编程和FPGA 设计方法,提升硬件设计能力和实践能力。

设计过程和思路:DDR2SDRAM是一种高速存储器件,需要通过控制器来实现数据的读取和写入。

在设计过程中,需要考虑以下因素:控制时序的设计、控制信号的产生、数据的传输和错误的检测与纠正等。

在控制时序的设计中,首先需要了解DDR2SDRAM的时序。

DDR2SDRAM的时序包括初始化阶段和读写数据阶段,其中初始化阶段涵盖了模式寄存器的编程和ODT的选择,读写数据阶段则是根据时钟信号,按照预定的时序顺序,产生相应的控制信号。

因此,控制时序的设计可以通过分阶段设计时序状态机来实现。

控制信号的产生是实现DDR2SDRAM的重要组成部分。

每个控制信号的产生都需要根据相应的时序周期产生,例如,数据总线的读写控制需要按照时序时钟的周期逐次产生,PHY的时钟需要根据总线的时钟和序列延迟时间产生。

控制信号产生可以通过组合逻辑和状态机的方式实现。

数据传输是实现DDR2SDRAM控制器的核心部分之一。

数据的传输通过数据缓冲区来实现,可以通过两种方式来实现:先入先出和最近最少使用。

在FPGA中可以使用堆或FIFO模块来实现。

错误的检测与纠正是在数据传输过程中非常重要的部分。

DDR2SDRAM中数据的传输和读取都会产生错误或异常,因此需要在设计时加入错误检测和纠正机制,以保证数据传输的正确性。

常见的错误检测和纠正方式有ECC纠错代码和CRC码。

ECC纠错代码可以检测和修复双误差的数据,而CRC码可以检测并指示单误差的位置。

设计原理和实现方法:DDR2SDRAM控制器的设计主要分为时序控制和数据传输两个部分。

【精品】海明码课程设计报告

【精品】海明码课程设计报告海明码是一种纠错码,用于在数字通信中检测和纠正数据传输中的错误。

在本次课程设计中,我们设计了一个海明码编码器和解码器,并进行了相关的实验和测试。

首先,我们设计了海明码编码器。

编码器的输入是一个长度为k的二进制数据序列,输出是一个长度为n的二进制数据序列,其中n=k+r,r是冗余位数。

编码器的主要功能是根据输入数据生成冗余位,并将输入数据和冗余位按照一定的规则组合起来形成输出数据。

我们采用了海明码的标准编码规则,具体实现过程如下:1. 输入数据序列为D,冗余位数为r。

2. 根据输入数据序列的长度确定冗余位数,使得r满足2^r ≥ r+k+1。

3. 初始化输出数据序列为0。

4. 将输入数据序列按照一定的规则插入到输出数据序列中,形成初始编码结果。

5. 针对每一个冗余位,计算该位的值,并将其插入到输出数据序列中。

6. 输出最终的编码结果。

接下来,我们设计了海明码解码器。

解码器的输入是一个长度为n的二进制数据序列,输出是一个长度为k的二进制数据序列。

解码器的主要功能是根据输入数据序列检测和纠正错误,并将纠正后的数据输出。

我们采用了海明码的标准解码规则,具体实现过程如下:1. 输入数据序列为C。

2. 针对每一个冗余位,计算该位的值,并与输入数据序列中对应的位进行比较,如果不一致,则表示该位有错误。

3. 根据错误位的位置,确定错误位对应的输入数据序列中的位置,将该位置上的位进行翻转。

4. 输出最终的解码结果。

为了验证海明码编码器和解码器的正确性,我们进行了一系列实验和测试。

首先,我们随机生成了一些输入数据序列,并将其输入到编码器中进行编码。

然后,我们将编码结果输入到解码器中进行解码,并与原始输入数据序列进行比较。

实验结果表明,编码器和解码器能够正确地生成和纠正错误,验证了其正确性和可靠性。

总结起来,本次课程设计中我们设计了海明码编码器和解码器,并进行了相关实验和测试。

通过实验验证,编码器和解码器能够正确地生成和纠正错误,具有较高的可靠性和实用性。

扩展SDRAM实验

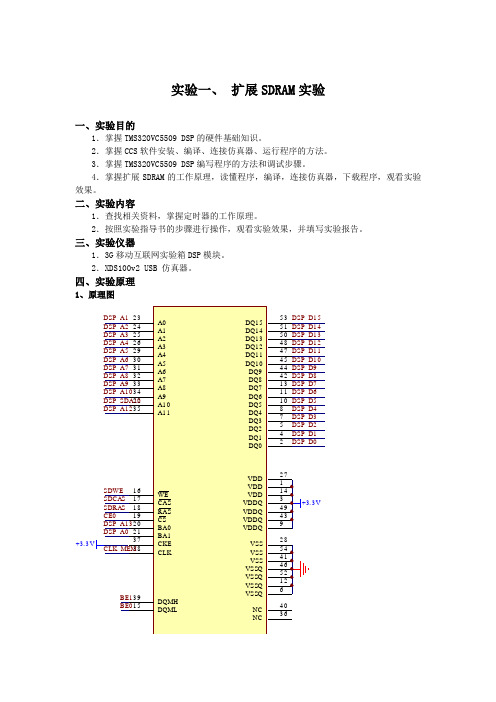

实验一、 扩展SDRAM 实验一、实验目的1.掌握TMS320VC5509 DSP 的硬件基础知识。

2.掌握CCS 软件安装、编译、连接仿真器、运行程序的方法。

3.掌握TMS320VC5509 DSP 编写程序的方法和调试步骤。

4.掌握扩展SDRAM 的工作原理,读懂程序,编译,连接仿真器,下载程序,观看实验效果。

二、实验内容1.查找相关资料,掌握定时器的工作原理。

2.按照实验指导书的步骤进行操作,观看实验效果,并填写实验报告。

三、实验仪器1.3G 移动互联网实验箱DSP 模块。

2.XDS100v2 USB 仿真器。

四、实验原理1、原理图DSP_A1DSP_A2DSP_A3DSP_A4DSP_A5DSP_A6DSP_A7DSP_A8DSP_A9DSP_A10SDRAS SDCAS SDWE BE0DSP_D0DSP_D1DSP_D2DSP_D3DSP_D4DSP_D5DSP_D6DSP_D7DSP_D8DSP_D9DSP_D10DSP_D11DSP_D12DSP_D13DSP_D14DSP_D15VDD 1DQ02VDDQ 3DQ14DQ25VSSQ 6DQ37DQ48VDDQ 9DQ510DQ611VSSQ 12DQ713VDD 14DQML15WE16CAS 17RAS 18CS 19BA020BA121A1022A023A124A225A326VDD 27VSS 28A429A530A631A732A833A934A1135NC36CKE 37CLK38DQMH 39NC 40VSS 41DQ842VDDQ 43DQ944DQ1045VSSQ 46DQ1147DQ1248VDDQ 49DQ1350DQ1451VSSQ 52DQ1553VSS 54U3MT48LC4M16A2DSP_SDA10DSP_A12BE1CLK_MEM +3.3VCE0DSP_A13+3.3VDSP_A0D057D158D259D361D462D563D665D766D867D969D1070D1171D1274D1375D1476D1577ARDY/HRDY20AOE/HINT 17AWE/HR/W 19ARE/GPIO816BE0/HBE026BE1/HBE127CLKMEM/HDS231SDWE/HDS132SDCAS/HCS 28G12/SDRAS/HAS34CE0/GPIO921CE1/GPIO1022CE2/HCNTL023G11/CE3/HCNTL125A055A154A252A351A450A548A647A746A844A943A1042A1140A1239A1338SDA10/GPIO1335U1DTMS320VC5509A(PGE)DSP_D0DSP_D1DSP_D2DSP_D3DSP_D4DSP_D5DSP_D6DSP_D7DSP_D8DSP_D9DSP_D10DSP_D11DSP_D12DSP_D13DSP_D14DSP_D15DSP_A0DSP_A1DSP_A2DSP_A3DSP_A4DSP_A5DSP_A6DSP_A7DSP_A8DSP_A9DSP_A10DSP_A11DSP_A12DSP_A13DSP_SDA10CE0SDRAS SDCAS SDWECLK_MEM BE1BE0CE1ARE AWE CE2CE3AOE ARDY阅读原理图的时候注意,请对着protel 格式的原理图,逐个搞清楚每个管脚的连接,由于TMS320VC5509A 的管脚比较多,原理图上基本上都是分块设计,管脚之间采用网络标号,而不是直接的连线,请用查找的方式将其归类,也可以自己尝试修改原理图,将本模块的原理图修改的更容易阅读。

SDR课程设计

SDR课程设计一、课程目标知识目标:1. 学生能理解SDR(Software Defined Radio,软件定义无线电)的基本概念,掌握其工作原理及关键技术。

2. 学生能掌握SDR技术在通信系统中的应用,了解其与传统无线电技术的区别。

3. 学生能了解我国在SDR领域的发展现状及未来趋势。

技能目标:1. 学生能够运用所学知识,进行SDR系统的基本配置和调试。

2. 学生能够通过实践操作,掌握SDR信号处理的基本方法。

3. 学生能够运用SDR技术进行简单的无线电通信实验。

情感态度价值观目标:1. 培养学生对通信技术的兴趣,激发其探索精神,提高学生的创新意识。

2. 增强学生的团队合作意识,使其在实践过程中学会相互协作、共同解决问题。

3. 培养学生关注国家科技发展,提高学生的社会责任感和使命感。

本课程针对高年级学生,结合通信原理及实践操作,注重理论知识与实际应用的结合。

通过本课程的学习,使学生能够全面了解SDR技术,提高学生在通信领域的实践能力和创新能力,为我国通信事业的发展培养具备竞争力的技术人才。

二、教学内容1. SDR概述- SDR的定义、发展历程及分类- SDR的优势与应用领域2. SDR工作原理与关键技术- 无线电信号处理基础- SDR系统的硬件与软件架构- 数字下变频、滤波器设计、调制解调技术3. SDR技术在通信系统中的应用- SDR与传统无线电技术的比较- SDR在无线通信、卫星通信等领域的应用案例4. SDR实践操作- SDR设备的安装与配置- 基于SDR的信号捕获、处理与分析- SDR通信实验:如FM广播接收、简单无线数据传输等5. 我国SDR技术发展现状与展望- 我国SDR技术政策与发展规划- 国内外SDR技术发展动态及趋势- 我国在SDR领域的主要成果与应用教学内容依据课程目标进行系统组织,注重理论与实践相结合。

教学大纲明确教学内容安排和进度,确保学生在掌握基本概念和原理的基础上,能够进行实践操作,了解我国在SDR领域的发展现状。

基于fpga的sdram课程设计

基于FPGA的SDRAM控制器课程设计一、引言随着嵌入式系统应用的不断扩展,高速大容量存储器的需求日益增长。

SDRAM(Synchronous Dynamic Random Access Memory,同步动态随机存取存储器)作为一种高速动态存储器,广泛应用于各种高性能系统中。

为了实现高效的数据存储和读取,基于FPGA(Field Programmable Gate Array,现场可编程门阵列)的SDRAM控制器设计成为了研究的热点。

本课程设计将介绍基于FPGA的SDRAM控制器设计的相关知识,并探讨其实现方法。

二、SDRAM控制器设计原理SDRAM控制器的主要功能是实现SDRAM芯片与FPGA之间的通信。

它需要将FPGA发出的时序和控制信号转换为符合SDRAM规格的信号,以实现对SDRAM芯片的读写操作。

在设计SDRAM控制器时,需要考虑以下几个关键因素:1.SDRAM规格:不同的SDRAM芯片具有不同的规格,包括数据宽度、工作电压、刷新周期等。

在设计控制器时,需要了解目标SDRAM芯片的规格,以确保正确的通信。

2.时序控制:SDRAM通信涉及到复杂的时序控制,包括数据读写时序、刷新时序等。

控制器需要根据SDRAM规格生成正确的时序信号,以保证数据正确读写。

3.地址管理:SDRAM控制器需要管理SDRAM芯片的地址,包括行地址和列地址。

控制器需要生成正确的地址信号,并根据地址信号实现数据读写。

4.数据传输:控制器需要实现数据的正确传输,包括数据的读写操作和数据的格式化。

根据目标应用需求,可以选择合适的传输模式,如突发传输、页模式传输等。

三、基于FPGA的SDRAM控制器设计实现基于FPGA的SDRAM控制器设计可以通过硬件描述语言(如VHDL或Verilog)实现。

以下是一个简单的基于FPGA的SDRAM控制器设计的实现步骤:1.确定SDRAM规格:首先需要确定目标SDRAM芯片的规格,包括数据宽度、工作电压、刷新周期等。

实验五DAM to SDRAM例程详解

一、实验目的:1. 熟悉Visual DSP软件。

2. 了解Blankfin系列DSP芯片的内存管理情况以及DMA寄存器的配置和基于描述符的DMA 传送机制二、实验要求:例程详解:visual 4.5版本的安装目录下,找exzmple/blackfin535/DMA to SDRAM 的文件,写一份例程详解报告。

三、实验分析:1. 相关知识⑴DMABlackfin使用 DMA进行存储器空间内部或者存储器空间与外设之间的数据传送.DMA控制器允许Blackfin或外部设备指定数据传送操作,然后其返回到正常操作中。

DMA控制器传送数据的过程独立于处理器的活动。

DMA控制器将数据传输完成后会给处理器内核一个信号来表示数据已经传完。

⑵SDRAM同步DRAM。

其工作频率与系统工作频率相同。

⑶内存管理21535的内存管理把存储器视为一个统一的4GB的地址空间,使用32位地址。

所有的资源,包括内部存储器、外部存储器、PCI地址空间和I/O控制寄存器,都具有独立的地址空间。

芯片内部的308KB RAM中,L1(一级缓存)52KB,L2(二级缓存)256KB (0xF003FFFF~~0xF000000);内存地址的具体配置空间如下图所示.L1 内存访问速度最快,每个处理器周期能完成一次访问。

L2 内存远离内核处理器,用于存储更大量的程序代码和数据。

存储器的DMA控制器提供高带宽的数据传输能力,它能够在内部L1/L2存储器和外部存储器(包括PCI存储空间)之间执行代码或者数据的块传输。

⑷ DMA寄存器的配置为了描述Mem DMA序列,DMA控制器使用一套名为描述子块(Descriptor)的参数。

当需要后继的DMA序列时,这些描述子块被链接起来。

这样,一个DMA序列完成时能够自动初始化下一个序列,并将其启动。

如果不需启动下一个序列,只要将其指向一个内容为0的地址空间即可。

如果下一次链接指向原描述子块,则DMA完成后暂停。

数码管显示课程设计报告

目录一.实验前的准备 (2)二.实验目的 (2)三.实验设备 (2)四.实验内容 (3)五.实验原理 (3)六.管脚分配 (4)七.实验步骤 (4)八.实验原理图: (5)九.实验程序代码: (6)(1)CH452_I2C.h代码 (6)(2)Define.h代码 (8)(3)key.h代码 (9)(4)Key.c代码 (10)(5)Seven_seg.c代码 (12)十.结果分析: (15)十一.个人体会与总结: (16)一.实验前的准备打开实验箱开关,连接好JTAG下载线,将开发平台上的MODUL_SEL组合开关的1、2、7拨上,3、4、5、6、8拨下,使两个共阳极数码管显示为C2。

二.实验目的(1)熟悉并学习运用I2C总线的读写方式。

(2)运用CH452芯片的数码管显示功能,熟悉两线制访问CH452芯片的工作原理。

三.实验设备硬件:PC机GX-CIDE-SOC/SOPC综合创新开发实验平台GX-CIDE-SOC/SOPC综合创新开发实验平台核心板软件:Quartus II 8.0Nios II 8.0四.实验内容用七段数码管前三位显示000-999,计数周期为1s;按F1进行加1操作并用数码管显示。

按F2计数停止,并显示当前数。

按F3进行减1操作;当数从000-999时再加1变为000;当数从999-000时再减1变为999。

五.实验原理根据I2C总线时序要求,对CH452进行操作,送地址,送控制字,送数据。

数码管显示是以BCD译码方式显示。

六.管脚分配七.实验步骤(1)打开Quartus II 8.0,打开工程cide_c2,进行SOPC操作,裁剪所需要的内容,综合一下再分配管脚。

(2)启动Nios II IDE并新建一个空白C/C++工程,命名为smm,在SOPC Builder System中选择之前建立好的硬件系统cide_c2.ptf。

(3)转换工程路径,将提供的参考程序seven_seg.c,CH452_I2C.h,define.h加入到建立好的Nios II工程中,修改程序代码符合实验要求。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

SDRAM课程设计报告

<姓名>

北京至芯FPGA培训课程2016年9月25日星期日

目录

更新日志 (3)

一、SDR控制器设计 (4)

1.1 顶层设计 (4)

1.2 上电序列设计 (4)

1.2.1 上电序列状态机设计 (5)

1.3 上电刷新控制器设计 (6)

1.3.1 架构设计 (6)

1.3.2 刷新序列的状态转移图 (7)

1.3.2 主控制器状态转移图 (7)

1.3.3 刷新定时器 (7)

1.4 读写序列控制器设计 (8)

1.4.1 顶层接口读时序定义 (8)

1.4.2 顶层接口写时序定义 (8)

1.4.3 架构设计 (9)

1.4.4 写模块设计 (10)

1.4.5 读模块设计 (11)

1.4.6 主控机的状态转移图 (12)

更新日志

一、SDR控制器设计

基本要求:

1.能够执行上电序列

2.时钟频率100M

3.器件选择MT48LC32M6A2-7E 1.1 顶层设计

1.2 上电序列设计

说明:

1.参照说明书34页时序图

2.查表11(18页)tRP为15ns,当前时钟100M(10ns),取2拍,即ctRP=2

3.查表11(18页)tRFC为66ns,取7拍,即ctRFC=7

4.查表12(19页)tMRD为2拍,即ctMRD=2

5.done信号复位后,清除为假;置位后,发出真,使能后发出假,以后直到完成对应的上

电序列后,done为高(真)

6.

,内置图样:

7.按照上电序列的时序图,在Tp+3处,并不处理激活以及后续的读写,仅将done拉高即

可。

完成上电序列。

1.3.1 架构设计

1.3.2 刷新序列的状态转移图

1.3.2 主控制器状态转移图

1.3.3 刷新定时器

!ref_done

1.4 读写序列控制器设计

1.4.1 顶层接口读时序定义

说明:突发长度(BL=2),

1.4.2 顶层接口写时序定义

clk local_ready local_rdreq

valid don ’t care

local_rdata valid

don ’t care

local_rdata_valid

clk local_ready

local_wrreq valid don ’t care local_wdata local_addr

local_addr valid don ’t care

1.4.4.1写模块时序

说明:全部写操作,使用AP(auto precharge)

1.4.4.2写模块状态转移图

clk sdr_clk cmd ba a dq count <`ctRCD-1

count=count+1

1.4.5 读模块设计

1.4.5.1读模块架构设计

1.4.5.2读模块时序

说明:突发长度BL=2, CL=2, AP, ctRCD=2,SL=1

capture_clk

sdr_clk

cmd

ba

a

dq

dq_syn

load_l

load_h

rdata

rd_done

1.4.5.3读模块状态转移图

1.4.6 主控机的状态转移图

count <`ctRCD-1 count <`CL+`SL-1

!rd_en rd_done=0。