阵列乘法器

6位有符号补码阵列乘法器

6位有符号补码阵列乘法器一. 简介在计算机科学和数字电路设计中,6位有符号补码阵列乘法器是一种重要的电路组件。

补码是一种表示有符号数的编码方式,能够有效地表示负数。

本文将深入探讨6位有符号补码阵列乘法器的原理、设计和应用,并分享对该电路的观点和理解。

二. 原理1. 有符号补码表示有符号补码是一种在计算机中表示负数的常用编码方式。

在6位有符号补码中,最高位表示符号位,0代表正数,1代表负数。

其余位表示数值部分,通过取反加一的方式对负数进行编码。

2. 阵列乘法器阵列乘法器是一种用于执行乘法运算的电路。

6位有符号补码阵列乘法器能够以比较高的效率和较小的面积完成乘法运算。

其主要原理是将乘法运算拆分为多个部分,使用并行的方式进行计算,并最后将结果相加得到最终的乘积。

三. 设计1. 输入和输出6位有符号补码阵列乘法器一般包含两个输入,分别是被乘数和乘数,以及一个输出,即乘积。

被乘数和乘数的输入位数都为6位。

2. 乘法计算乘法计算是6位有符号补码阵列乘法器的核心部分。

它首先对乘数进行拆分,每一位与被乘数相乘,从而生成多个部分乘积。

接下来,对这些部分乘积进行累加,最后得到乘积的结果。

该阵列乘法器的设计需要考虑到乘法运算可能会出现的溢出和进位问题。

3. 控制逻辑6位有符号补码阵列乘法器还需要一些控制逻辑来控制乘法计算的顺序和结果的输出。

这些控制逻辑一般包括时钟信号、使能信号和清零信号等。

四. 应用1. 数字信号处理6位有符号补码阵列乘法器在数字信号处理领域得到广泛应用。

它能够高效地进行乘法运算,常用于滤波器等算法的实现。

2. 图像处理图像处理中经常需要进行像素之间的乘法运算,例如图像增强、滤波和特征提取等。

6位有符号补码阵列乘法器可以在图像处理中快速完成这些乘法运算。

3. 神经网络神经网络是人工智能领域的热门研究方向。

6位有符号补码阵列乘法器能够提供高效的乘法运算支持,可以在神经网络的训练和推理过程中扮演重要角色。

脉动阵列矩阵乘法器

脉动阵列矩阵乘法器

脉动阵列矩阵乘法器是一种计算矩阵乘法的特殊硬件结构,通常用于高性能计算和并行处理。

下面是关于脉动阵列矩阵乘法器的简要解释:

1.脉动阵列(Systolic Array):脉动阵列是一种并行计算结构,其特点是数据在结构

内部以“脉动”(pulse-like)的方式流动。

在矩阵乘法应用中,每个处理单元负责执行乘法和累加操作,而数据以流水线的形式在这些处理单元之间传递,形成高效的并行计算结构。

2.矩阵乘法器(Matrix Multiplier):矩阵乘法是一种常见的线性代数运算,涉及两个

矩阵相乘。

在脉动阵列矩阵乘法器中,每个处理单元负责执行一个乘法和累加操作,从而实现高度并行的矩阵乘法。

3.工作原理:脉动阵列矩阵乘法器的工作原理是将输入矩阵的元素通过流水线方式传

送到处理单元,每个处理单元执行乘法和累加运算,然后将结果传递给下一个处理单元。

这种方式能够有效地利用硬件资源,提高计算速度。

4.应用领域:脉动阵列矩阵乘法器常用于需要大规模矩阵乘法计算的应用,例如图形

处理、信号处理、神经网络等领域。

其并行计算的特性使其在高性能计算环境中具有优势。

总体而言,脉动阵列矩阵乘法器是一种利用并行计算的硬件结构,用于加速矩阵乘法等线性代数运算。

斜向进位阵列乘法器

斜向进位阵列乘法器引言随着计算机技术的不断发展,计算机的性能、速度和稳定性都得到了极大的提升,而高性能计算正是离不开高效的乘法器的支持。

在数字乘法运算中,进位是一个很重要的问题,进位延迟会直接影响乘法器的速度,因此,设计一种能够高效地进行进位的乘法器对于提升计算性能非常重要。

在本文中,我们将探讨一种名为“斜向进位阵列乘法器”的乘法器,了解其工作原理和优势。

斜向进位阵列乘法器的原理斜向进位阵列乘法器是一种基于并行计算的乘法器,它将乘法运算分解为多个子运算,并行计算,然后将结果相加得到最终结果。

斜向进位阵列乘法器的核心思想是解决进位问题,它采用了一种特殊的进位方式,即“斜向进位”。

在传统的进位方式中,我们会发现,所有的进位都是在同一列上进行的,而斜向进位阵列乘法器则采用了不同的进位方式。

它将进位拆分成了两个方向:正斜向进位和反斜向进位。

在斜向进位阵列乘法器中,每个位的进位只会向正斜方向和反斜方向传递,不会像传统的进位方式那样一路“顺风顺水”的传递到最高位,从而减少了进位延迟,提高了乘法器的速度。

值得一提的是,斜向进位阵列乘法器的加法器和乘法器是分离的,分别处理加法和乘法。

这种分离的设计方式能够使得斜向进位阵列乘法器能够更灵活地适应各种不同位宽的输入数据,从而进一步提高计算效率。

斜向进位阵列乘法器的优势1. 减少进位延迟如前所述,斜向进位阵列乘法器的正斜向进位和反斜向进位能够将进位分散到各个位上,减少了进位延迟,从而提高了计算速度。

2. 更好的适应性斜向进位阵列乘法器的加法器和乘法器分离,能够更好地适应不同位宽的输入数据,对于大量位宽连续变化的数据处理具有优势。

3. 高效的资源利用斜向进位阵列乘法器采用并行计算方式,可以在同一时间内运行多个子运算,高效利用计算资源,从而提高了计算效率。

结论本文对斜向进位阵列乘法器的工作原理和优势进行了详细地介绍。

与传统进位方式相比,斜向进位方式能够减少进位延迟,提高计算速度,而分离的加法器和乘法器也使得它更好地适应不同位宽的输入数据。

实验二 阵列乘法器

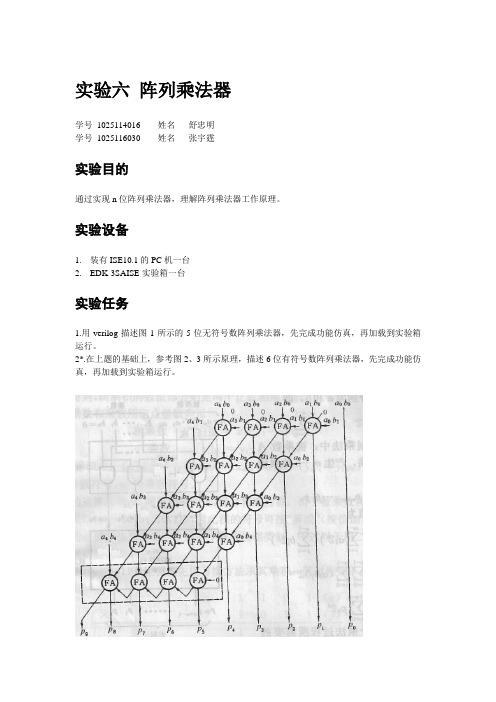

实验六阵列乘法器学号1025114016 姓名舒忠明学号1025116030 姓名张宇霆实验目的通过实现n位阵列乘法器,理解阵列乘法器工作原理。

实验设备1.装有ISE10.1的PC机一台2.EDK-3SAISE实验箱一台实验任务1.用verilog描述图1所示的5位无符号数阵列乘法器,先完成功能仿真,再加载到实验箱运行。

2*.在上题的基础上,参考图2、3所示原理,描述6位有符号数阵列乘法器,先完成功能仿真,再加载到实验箱运行。

图1 5位无符号数阵列乘法器图2 n+1位有符号数阵列乘法器图3 5位补码的求补电路原理图实验报告格式一、实验目的二、实验设备三、实验内容1. 用verilog描述图1所示的5位无符号数阵列乘法器,先完成功能仿真,再加载到实验箱运行。

1.模块代码module hw_mul(x, y, out);parameter n = 16;input [n-1:0]x, y;output [n*2-1:0]out;genvar i, j, k, l;wire [n:0]tmp_sun[n-1:0], tmp_out[n-1:0];wire [n:0]tmp_x;// 1. generate语法有generate for, genreate if和generate case三种 2. generate for语句必须有genvar关键字定义for的变量 3. for 的内容必须加begin和end 4. 必须给for语段起个名字assign tmp_x = {1'b0,x};// 1'b0 表示1位宽,2进制,数字0assign out[0] = tmp_x[0] & y[0];generateassign tmp_out[0][0] = 1'b0;for(i=0;i<n;i=i+1)//循环相加顶层乘数的前两位与上被乘数的部分积.begin:add_bttop_m tm (tmp_x[i+1], y[0], tmp_x[i], y[1], tmp_out[0][i], tmp_sun[0][i], tmp_out[0][i+1]);//module top_m(m0, q0, m1, q1, cin, sun, cout);顶层乘法单元endassign out[1] = tmp_sun[0][0];assign tmp_sun[0][n] = tmp_out[0][n];for(j=2;j<n;j=j+1)//从第三位开始的每一位与上被乘数,然后跟上一层的部分积结果相加.begin:ftffor(k=0;k<n;k=k+1)begin:add_bbbtm_m bm (tmp_sun[j-2][k+1], tmp_x[k], y[j], tmp_out[j-1][k], tmp_sun[j-1][k], tmp_out[j-1][k+1]);//module btm_m(sunin, m, q, cin, sun, cout);底层乘法单元endassign out[j] = tmp_sun[j-1][0];assign tmp_sun[j-1][n] = tmp_out[j-1][n];endfor(l=n;l<n*2;l=l+1)begin:add_oassign out[l] = tmp_sun[n-2][l-n+1];endendgenerateendmodulemodule top_m(m0, q0, m1, q1, cin, sun, cout);//顶层乘法单元input m0, m1, q0, q1;input cin;output sun, cout;//sun:提供给下一层的和(↓);cout:提供给下一层的进位输出(↙)wire x, y;assign x = m0 & q0;assign y = m1 & q1;full_add fa (x, y, cin, sun, cout);//一位全加器endmodulemodule btm_m(sunin, m, q, cin, sun, cout);//下层乘法单元input sunin, m, q, cin;//sunin:来自上一层的和输出(↓);m,q:两个乘数在当层对应的位(←);cin:来自上一层的进位输出(↙)output sun, cout;//sun:提供给下一层的和(↓);cout:提供给下一层的进位输出(↙)wire y;assign y = m & q;full_add fa (sunin, y, cin, sun, cout);//一位全加器endmodulemodule full_add(x, y, cin, sun, cout);//一位全加器input x, y, cin;output reg sun, cout;always@(x, y, cin)beginsun <= x^y^cin;cout <= x&y | x&cin | y&cin;endendmodule2.功能仿真测试代码module TEST;// Inputsreg [4:0] x;reg [4:0] y;// Outputswire [9:0] out;// Instantiate the Unit Under Test (UUT)zhenliecf uut (.x(x),.y(y),.out(out));initial begin// Initialize Inputsx = 0;y = 0;// Wait 100 ns for global reset to finish#100;// Add stimulus hereendalways #10 x[0]=~x[0];always #20 x[1]=~x[1];always #30 x[2]=~x[2];always #40 x[3]=~x[3];always #50 x[4]=~x[4];always #60 y[0]=~y[0];always #70 y[1]=~y[1];always #80 y[2]=~y[2];always #90 y[3]=~y[3];always #100 y[4]=~y[4];endmodule3.功能仿真测试时序图参考资料12位LED灯12位拨动开关。

五位阵列乘法器logisim实验报告

五位阵列乘法器logisim实验报告引言:在数字电路设计中,乘法器是一种非常重要的电路。

为了实现高效的乘法运算,我们常常需要使用乘法器进行乘法操作。

本实验旨在使用五位阵列乘法器logisim进行乘法器的设计与实现。

设计与实现:本次实验中,我们使用logisim软件进行五位阵列乘法器的设计与实现。

首先,我们需要搭建一个五位的输入端,来输入待相乘的两个数。

然后,我们需要将输入的两个数分别与五个乘法器相连,以实现乘法运算。

每个乘法器都会将两个输入相乘得到一个结果,并输出给下一级电路。

在乘法器的设计中,我们使用了多个与门和全加器。

与门用于判断两个输入是否都为1,从而判断是否需要进行相乘操作。

全加器用于将两个输入相乘的结果相加,并输出给下一级电路。

通过多级的与门和全加器的连接,我们可以实现五位数的相乘运算。

结果与分析:经过实验,我们成功实现了五位阵列乘法器的设计与实现。

通过输入不同的五位数,我们可以得到相应的乘法结果。

在logisim软件中,我们可以直观地观察到乘法器的运行过程,以及每一级电路的工作情况。

本实验的设计与实现对于理解乘法器的工作原理具有重要的意义。

通过logisim软件的模拟,我们可以更好地理解数字电路的运行过程,并加深对乘法器的认识。

结论:通过本次实验,我们成功地设计与实现了五位阵列乘法器。

通过logisim软件的模拟,我们可以直观地观察乘法器的工作过程,并得到相应的乘法结果。

这对于理解乘法器的工作原理以及数字电路的设计与实现具有重要的意义。

通过本次实验,我们不仅加深了对乘法器的认识,同时也提高了对logisim软件的使用能力。

在未来的学习和工作中,我们可以更加熟练地使用logisim软件进行数字电路的设计与模拟。

参考文献:[1] logisim软件官方网站[2] 数字电路设计与实验教程,XX出版社,20XX年。

阵列乘法器

和最下面的一行。因而

得n位×n位不带符

号的阵列乘法器总的乘法时间为:

tm=Ta+ (n-2)6T+5T+(n-1)]×Tf =2T+6nT-12T+5T+(n-1)×2T

=(4n-2)×2T

(2.27)

2.带符号的阵列乘法器

(1) 对2求补器电路

我们先来看看算术运算部件设计中经常用到的求补电路。一个具

的补码阵列乘法所需要增加的硬件较多。为了完成所必需的求 补与乘法操作,时间大约比原码阵列乘法增加1倍。

例17:设x=+15,y=-13,用带求补器的原码阵列乘法器求出 乘积x·y=?

[解:] 设最高位为符号位,则输入数据为[x]原 =01111 [y]原 = 11101

符号位单独考虑,算前求补级后 |x|=1111,|y|=1101

A=am-1…a1a0 B=bn-1…b1b0 它们的数值分别为a和b,即

m-1

a ∑ = i=a0 i2i

n-1

b ∑ = j=b0j2j

在二进制乘法中,被乘数A与乘数B相乘,产生m+n位乘积P: P=pm+n-1…p1p0 乘积P 的数值为

实现这个乘法过程所需要的操作和人们的习惯方法非常类 似:(如下页图所示):

有使能控制的二进制对2求补器电路图演示,其逻辑表达式如下:

C-1=0, Ci=ai+Ci-1

ai*=ai⊕ECi-1,

0≤i≤n

在对2求补时,要采用按位扫描技术来执行所需要的求补操作。令

A=an…a1a0是给定的(n+1)为带符号的数,要求确定它的补码形式 。进行求补的方法就是从数的最右端a0开始,,由右向左,直到找出第 一个“1”,例如ai=1, 0≤i≤n。这样,ai以左的每一个输入位都求反, 即1变0,0变1。最右端的起始链式输入C-1必须永远置成“0”。当控 制信号线E为“1”时,启动对2求补的操作。当控制信号线E为“0”时

组成原理课设阵列乘法器

组成原理课设阵列乘法器在现代科技的发展中,计算机和电子设备的性能提升日新月异。

而在这些设备中,乘法器是一个至关重要的组成部份。

乘法器的性能直接影响到整个系统的运算速度和效率。

因此,设计一个高效且可靠的乘法器是组成原理课程中的一项重要任务。

一、乘法器的基本概念乘法器是一种用于实现两个数相乘的电子电路。

在计算机中,乘法器的作用是进行大量的乘法运算,从而实现复杂的计算任务。

乘法器通常由多个逻辑门和触发器组成,其内部结构可以分为串行乘法器和并行乘法器两种类型。

二、串行乘法器的原理串行乘法器是一种逐位相乘的乘法器,它将两个数的每一位进行相乘,并将结果相加得到最终的乘积。

串行乘法器的原理可以通过以下步骤来说明:1. 将两个数的每一位进行相乘,得到部份积。

2. 将部份积与进位相加,得到新的部份积。

3. 重复以上步骤,直到所有位数都相乘完毕。

4. 将所有的部份积相加,得到最终的乘积。

串行乘法器的优点是结构简单,适合于小规模的乘法运算。

但是由于乘法运算是逐位进行的,所以串行乘法器的运算速度较慢。

三、并行乘法器的原理并行乘法器是一种同时进行多位乘法运算的乘法器,它可以大大提高乘法运算的速度。

并行乘法器的原理可以通过以下步骤来说明:1. 将两个数的每一位进行相乘,得到部份积。

2. 将所有的部份积同时进行相加,得到最终的乘积。

并行乘法器的优点是运算速度快,适合于大规模的乘法运算。

但是由于并行乘法器的结构复杂,所以其设计和实现难度较大。

四、阵列乘法器的原理阵列乘法器是一种基于并行乘法器的乘法器,它通过将乘法运算分解成多个子运算,并将这些子运算并行进行,从而提高乘法运算的速度。

阵列乘法器的原理可以通过以下步骤来说明:1. 将两个数的每一位进行相乘,得到部份积。

2. 将所有的部份积按照位数进行罗列,形成一个二维矩阵。

3. 将矩阵中的每一行进行相加,得到每一位的乘积。

4. 将所有的乘积相加,得到最终的乘积。

阵列乘法器的优点是结构简单、运算速度快,适合于大规模的乘法运算。

阵列乘法器的基本原理

阵列乘法器的基本原理

阵列乘法器是一种高效的数字电路,用于实现大规模的乘法运算。

它的基本原理是将乘法运算分解为多个小的乘法运算,然后通过并行计算的方式来加速整个乘法过程。

阵列乘法器通常由多个乘法器和加法器组成,其中乘法器用于计算两个数的乘积,加法器用于将多个乘积相加得到最终结果。

这些乘法器和加法器被排列成一个二维的矩阵,每个乘法器都与相邻的乘法器和加法器相连。

在阵列乘法器中,输入的两个数被分解为多个小的位数,然后每个位数都被送到相应的乘法器中进行计算。

例如,如果输入的两个数是8位二进制数,那么它们将被分解为8个小的位数,每个位数都由一个乘法器和一个加法器计算。

这些乘法器和加法器被排列成一个8×8的矩阵,每个乘法器都与相邻的乘法器和加法器相连。

在阵列乘法器中,每个乘法器都可以同时计算多个位数的乘积,因此整个乘法过程可以并行计算。

这使得阵列乘法器比传统的乘法器更快,特别是在处理大规模的乘法运算时。

阵列乘法器还可以通过一些优化技术来进一步提高性能。

例如,可以使用更快的乘法器和加法器,或者使用更高效的算法来分解输入的数。

此外,还可以使用流水线技术来进一步提高计算速度。

阵列乘法器是一种高效的数字电路,用于实现大规模的乘法运算。

它的基本原理是将乘法运算分解为多个小的乘法运算,然后通过并行计算的方式来加速整个乘法过程。

在实际应用中,阵列乘法器可以通过一些优化技术来进一步提高性能,从而满足不同的应用需求。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

早期计算机中为了简化硬件结构,采用串行的1位乘 法方案,即多次执行“加法—移位”操作来实现。 这种方法并不需要很多器件。然而串行方法毕竟 太慢,自从大规模集成电路问世以来,出现了各种形 式的流水式阵列乘法器,它们属于并行乘法器。 1.不带符号的阵列乘法器 设有两个不带符号的二进制整数: A=am-1…a1a0 B=bn-1…b1b0 它们的数值分别为a和b,即

设A=anan-1…a1a0和B=bnbn-1…b1b0均为用定点表示的(n+ 1)位带符号整数。在必要的求补操作以后,A和B的码值输送给 n×n位不带符号的阵列乘法器,并由此产生2n位真值乘积: A· B=P=p 2n-1…p1p p2n=an⊕bn 其中P2n为符号位。 上面CAI演示所示的带求补级的阵列乘法器既适用于原码 乘法,也适用于间接的补码乘法。不过在原码乘法中,算前求补 和算后求补都不需要,因为输入数据都是立即可用的。而间接 的补码阵列乘法所需要增加的硬件较多。为了完成所必需的求 补与乘法操作,时间大约比原码阵列乘法增加1倍。

这种乘法器要实现n位 ×n位时,需要n(n-1)个 全加器和n2个“与”门。 该乘法器的总的乘法时 间可以估算如下: 令Ta为“与门”的 传输延迟时间,Tf为全加 器(FA)的进位传输延迟 时间,假定用2级“与非” 逻辑来实现FA的进位链 功能,那么我们就有: Ta = Tf = 2T 从演示中可知,最坏 情况下延迟途径,即是沿 着矩阵最右边的对角线 和最下面的一行。因而 得n位×n位不带符

例如,在一个4位的对2求补器中,,如果输入数为1010,那么 输出数应是0110,其中从右算起的第2位,就是所遇到的第 一个“1”的位置。用这种对2求补器来转换一个(n+1)为 带符号的数,所需的总时间延迟为 tTC=n· 2T+5T=(2n+5)T (2.28) 其中每个扫描级需2T延迟,而5T则是由于“与”门和“异 或”门引起的。 (2) 带符号的阵列乘法器 (n+1)×(n+1)位带求补器的阵列乘法器逻辑方框图演示 通常,把包括这些求补级的乘法器又称为符号求补的阵列 乘法器。在这种逻辑结构中,共使用三个求补器。其中两 个算前求补器的作用是:将两个操作数A和B在被不带符 号的乘法阵列(核心部件)相乘以前,先变成正整数。而算后 求补器的作用则是:当两个输入操作数的符号不一致时, 把运算结果变成带符号的数。

号的阵列乘法器总的乘法时间为: tm=Ta+ (n-2)6T+5T+(n-1)]×Tf =2T+6nT-12T+5T+(n-1)×2T =(4n-2)×2T (2.27) 2.带符号的阵列乘法器

(1) 对2求补器电路 我们先来看看算术运算部件设计中经常用到的求补电路。一个具 有使能控制的二进制对2求补器电路图演示,其逻辑表达式如下: C-1=0, Ci=ai+Ci-1 ai*=ai⊕ECi-1, 0≤i≤n 在对2求补时,要采用按位扫描技术来执行所需要的求补操作。令 A=an…a1a0是给定的(n+1)为带符号的数,要求确定它的补码形式 。进行求补的方法就是从数的最右端a0开始,,由右向左,直到找出第 一个“1”,例如ai=1, 0≤i≤n。这样,ai以左的每一个输入位都求反, 即1变0,0变1。最右端的起始链式输入C-1必须永远置成“0”。当控 制信号线E为“1”时,启动对2求补的操作。当控制信号线E为“0”时 ,输出将和输入相等。显然,我们可以利用符号位来作为控制信号。

a =∑ai2i

i=0

m-1

b =∑bj2j

j=0

n-1

在二进制乘法中,被乘数A与乘数B相乘,产生m+n位乘积P: P=pm+n-1…p1p0 乘积P 的数值为

实现这个乘法过程所需要的操作和人们的习惯方法非常类 似:(如下页图所示): 上述过程说明了在m位乘n位不带符号整数的阵列乘法 中,“加法—移位”操作的被加数矩阵。每一个部分乘积项(位 积)aibj叫做一个被加数。这m×n个被加数{aibj|0≤i≤m-1和 0≤j≤n-1}可以用m×n个“与”门并行地产生(如右下图所 示)。显然,设计高速并行乘法器的基本问题,就在于缩短被加 数矩阵中每列所包含的1的加法时间。 5位×5位阵列乘法器的逻辑电路图演示

例17:设x=+15,y=-13,用带求补器的原码阵列数据为[x]原 =01111 [y]原 = 11101

符号位单独考虑,算前求补级后 |x|=1111,|y|=1101 算后经求补级输出并加上乘积 符号位1,则原码乘积值为 111000011。 换算成二进制数真值是 x· =( -11000011)2=(-195)10 y 十进制数验证:x×y = 15× (-13) = -195相等。