数字逻辑电路m序列发生器

m序列发生器的作用

m序列发生器的作用

m序列发生器是一种能够产生伪随机序列的电子设备或算法。

它的主要作用有:

1. 加密通信:m序列发生器可以用于生成加密密钥序列,用于对通信数据进行加密,保护通信内容的安全性。

2. 伪随机数生成:m序列发生器可以用于生成伪随机数序列,可以应用在密码学中的伪随机数生成算法、模拟实验、随机化算法等应用中。

3. 信号处理:m序列发生器可以用于产生具有特定性质的信号序列,如具有较好频谱特性的序列、跳频信号序列等,广泛应用于通信领域、雷达系统、无线电测量等各种信号处理应用中。

4. 探测器测试:m序列发生器可以用于对数字通信中的接收机进行性能测试,通过与已知正常输入进行比较,可以检测接收机的误码率、误比特率、误帧率等性能指标。

总之,m序列发生器的作用主要体现在加密通讯、伪随机数生成、信号处理和探测器测试等方面。

M序列发生器

M 序列发生器M 序列(即De Bruijn 序列)又叫做伪随机序列、伪噪声(PN)码或伪随机码。

可以预先确定并且可以重复实现的序列称为确定序列;既不能预先确定又不能重复实现的序列称随机序列;不能预先确定但可以重复产生的序列称伪随机序列。

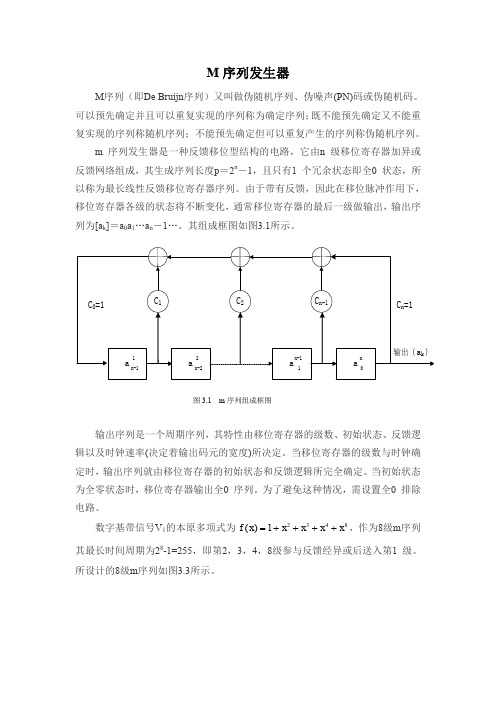

m 序列发生器是一种反馈移位型结构的电路,它由n 级移位寄存器加异或反馈网络组成,其生成序列长度p =2n -1,且只有1 个冗余状态即全0 状态,所以称为最长线性反馈移位寄存器序列。

由于带有反馈,因此在移位脉冲作用下,移位寄存器各级的状态将不断变化,通常移位寄存器的最后一级做输出,输出序列为[a k ]=a 0a 1…a n -1…。

其组成框图如图3.1所示。

输出序列是一个周期序列,其特性由移位寄存器的级数、初始状态、反馈逻辑以及时钟速率(决定着输出码元的宽度)所决定。

当移位寄存器的级数与时钟确定时,输出序列就由移位寄存器的初始状态和反馈逻辑所完全确定。

当初始状态为全零状态时,移位寄存器输出全0 序列。

为了避免这种情况,需设置全0 排除电路。

数字基带信号V 1的本原多项式为84321)(x x x x x f ++++=,作为8级m 序列其最长时间周期为28-1=255,即第2,3,4,8级参与反馈经异或后送入第1 级。

所设计的8级m 序列如图3.3所示。

图3.1 m 序列组成框图a n-11a n-22a 1n-1a 0n C 1C 2C n-1C n =1C 0=1输出{a k }依据上图原理,设计了一种通过手动置数产生M 序列的电路,其电路设计如图3.4所示,该图由Protel SE99绘制,再根据该图搭建硬件电路,图中的单刀开关可以用拨码开关代替。

电路分析:全0状态时,采用此方法设计的m 序列发生器不具有自启动特性。

为了使电路启动,可以断开开关S 1,将74LS194 的工作方式控制端S 1置高电平,这时S 1和S 0均为高电平,即S 1S 0=11,74LS194 处于置数状态,把输入端的初始状态10000000 置到输出端。

基于VHDL的m序列伪随机信号发生器设计 精品

成都电子机械高等专科学校毕业设计论文作者姚世刚学号2009111733系部电子与电气工程系专业电子测量技术与仪器题目基于VHDL的m序列伪随机信号发生器的设计指导教师赵茂林评阅教师完成时间:2012年4 月30日毕业设计(论文)中文摘要题目:基于VHDL的m序列发生器的设计摘要:VHDL/CPLD即复杂可编程逻辑器件作为一种大规模集成电路,可根据用户的需要自行构造逻辑功能,可实现较大规模的电路设计,因此被广泛应用于产品的原型设计和产品生产之中。

几乎所有应用中小规模通用数字集成电路的场合均可应用CPLD器件。

本文介绍了基于CPLD的m序列发生器的设计方法。

关键词:CPLD;MAX+PLUS II;伪随机码;m序列发生器毕业设计(论文)外文摘要Title : M—sequence Generator Based CPLDAbstract: VHDL/CPLD Complex Programmable Logic Device that is, as a large scale integrated circuits can be constructed according to the needs of users on their own logic, enabling large-scale circuit design, it is widely used in product design and prototype production into. Almost all applications of small and medium general-purpose digital integrated circuits may be applied CPLD devices occasions. This article describes the m-sequence generator based on CPLD design method.Key words: CPLD;MAX+PLUS II;Pseudorandom Code;m sequence code Generator目录前言 (6)1课题介绍 (7)1.1为什么研究此课题 (7)1.2伪随机序列的应用与意义 (7)1.3伪随机序列的研究现状 (8)1.4研究内容 (8)2设计中使用芯片及VHDL语言介绍 (9)2.1 CPLD芯片介绍 (9)2.1.1概述 (9)2.1.2 MAX7000特点 (9)2.1.3 EPM7128LC84-7 (11)3 伪随机序列介绍 (12)3.1 伪随机序列理论的发展史 (13)3.2 伪随机序列的构造方法 (13)4 序列信号发生器原理 (14)4.1序列信号发生器的设计 (15)4.1.1反馈移位型序列信号发生器 (15)4.1.2计数型序列码发生器 (18)5 移位寄存器 (20)5.1移位寄存器 (20)5.1.1 寄存器 (20)5.1.2移位寄存器 (21)5.2 线性反馈移位寄存器结构 (22)5.2.1 D触发器 (22)5.2.1.1 D触发器工作原理 (22)5.2.1.2 D触发器真值表 (23)5.2.1.3 特征方程 (23)5.2.1.4 状态转移图 (23)5.2.1.5时序图 (24)5.2.1.6 脉冲特性 (24)5.2.2异或门 (25)5.2.2.1 基本原理 (25)5.2.2.2 异或门逻辑符号 (25)5.2.2.3 逻辑表达式 (25)5.2.2.4 真值表 (25)5.3 线性反馈移位寄存器 (26)5.3.1 什么是反馈移位寄存器 (26)5.3.2 线性反馈移位寄存器 (26)5.3.3 性质 (26)6 伪随机信号 (27)6.1 伪随机信号 (27)6.2 m序列码发生器 (30)7 m序列性质 (33)7.1 均衡性 (33)7.2游程特性 (33)7.3 移位相加性 (33)7.4 相关特性 (33)7.5 伪随机特性 (34)8 序列信号发生器的设计和仿真实现 (35)8.1 m序列生成单元的电路设计 (35)8.1.1 系统组成 (35)8.1.2 程序方框图 (36)8.2 m序列发生器 (36)8.3 VHDL语言实现 (37)8.4 仿真数据及结论 (39)结论 (42)致谢 (43)参考文献 (43)前言CPLD(Complex Programmable Logic Device)复杂可编程逻辑器件,是从PAL和GAL器件发展出来的器件,相对而言规模大,结构复杂,属于大规模集成电路范围。

基于VHDL的多波形m序列发生器的设计

1 、引言

VHDL(超高速硬件描述语言)是一种 符合 I E E E 工业标准的硬件描述语言,在 EDA(电子设计自动化)领域得到广泛的 应用。应用 VHDL 进行电子系统设计,可 以使用自顶向下的设计方法,设计成果标 准化,可移植性好,具有与硬件无关的特 性,因此特别适合于大规模的专用电子系 统的开发。

3.2 一般情况 为了得到纳米摩擦在一般情况下的规 律性,模拟过程中设置了相关可调参数,如 表 1 所示。 在 KBT=0.1 ε,势能 u0(0.01 ε~0.04 ε),UP(0.03~0.09),UA(0.03~0.09)情况 下,模拟 C 在(0.03~0.09)之间对摩擦系数 的影响。图 3 给出了不同势能 u0 大小,不 同 UP,UA 情况下得到的摩擦系数的倒数 随 C 的变化曲线。 由图可以看出,最显著的特点是在不 同摩擦条件下的摩擦系数倒数曲线随 C 的 变化在 C=0.5 处出现了汇聚且出现最小值, 而在两侧则离散增加。当 C=0.5 时出现摩 擦系数倒数最小值,也就是出现了摩擦系 数最大值,即在完全匹配的情况下出现摩 擦最大值。完全匹配处之所以出现摩擦最 大值的原因在于此时所有的附加原子步伐 统一,能够同时受到衬底原子的拉力而加 速移动,又能够同时受到阻力减速,相互之 间无法将能量转化为势能保存,而只能以 热量的形式进行耗散。曲线的聚合同时说 明对于纳米摩擦无论势能形式如何组合变 化,势能大小的如何变化,在对摩擦的调制 作用中界面晶格匹配度 C 对整个摩擦过程 的调制作用最为明显,在完全匹配的情况 下摩擦最大。 由图可以发现另一个特点,摩擦系数 在 C 为 0.5 两侧随C的增大或者减少而迅速 减小,但在 C 为 0.8 时出现了转折点。此转 折点在不同的条件下,对摩擦的调制作用 表现出不同程度的影响,说明此转折点为 复合势能情况下产生的影响,而这种调节 作用与势能周期比例 U P 和势能振幅比例 UA 之间存在非线性关系。转折点的出现原 因为附加原子在不同的衬底复合势能阱中 进行运动时受到衬底原子的拉扯作用产生 了强烈的声子振动所带来的影响,这种拉 扯作用主要受到势能振幅比例与势能周期 之间的比例关系的影响。当处于衬底势能 最高点时,附加原子将出现失稳并自动跳跃 到下一势能最低点,然后在此平衡位置剧烈 震荡和激发声子,从而使能量不可逆地以声

基于fpga的m序列发生器-毕设论文

基于FPGA的m序列发生器摘要m序列广泛应用于密码学、通信、雷达、导航等多个领域,本文提出了一种基于FPGA的伪随机序列产生方法,应用移位寄存器理论从序列的本原多项式出发,获得产生该序列的移位寄存器反馈逻辑式,结合FPGA芯片结构特点,在序列算法实现中采用元件例化语句。

算法运用VHDL语言编程,以A1tera的QuartusⅡ软件为开发平台,给出了序列的仿真波形。

序列的统计特性分析表明:该方法产生的序列符合m序列的伪随机特性,验证了算法的正确性。

关键词:m序列;移位寄存器理论;VHDL语言目录摘要 (I)1 m序列 (1)1.1 理论基础 (1)1.1.1 线性反馈移位寄存器 (2)2 m序列的性质 (5)2.1 均衡性 (5)2.2游程特性 (5)2.4 自相关特性 (5)2.5 伪噪声特性 (7)3 m序列的应用 (9)3.1 扩展频谱通信 (9)3.2 通信加密 (10)4 开发工具简介 (11)4.1 Quartus II简介 (11)4.2 数字系统开发流程 (12)4.3 FPGA简介 (12)5 m序列生成器仿真分析 (16)5.1 反馈系数表存储器设计 (16)5.2 移位存储器设计 (17)5.3 仿真分析 (18)参考文献 (20)附录 (22)1 m序列m序列是伪随机序列的一种 ,结构简单 ,实现方便。

在现代工程实践中 , m 序列在通讯、导航、雷达、通信系统性能的测量等领域中有着广泛的应用。

例如 , 在连续波雷达中可用作测距信号 , 在遥控系统中可用作遥控信号 , 在多址通信中可用作地址信号 , 在数字通信中可用作群同步信号 ,还可用作噪声源及在保密通信中起加密作用等。

伪噪声发生器在测距、通信等领域的应用日益受到人们重视。

目前,m序列产生实现方法主要有3种:(1)门电路实现该方法设计简单,但随移位寄存器级数的增长,电路装调困难,且占用的印制板面积较大。

(2)DSP编程实现该方法专业性过强,不适合一般用户。

m序列产生实验

m序列产生实验一、实验目的1、m序列产生的基本方法;2、m序列0状态消除的基本手段;二、实验仪器1、JH5001型通信原理实验箱一台;2、MaxplusII开发环境一台;3、JTAG下载电缆一根;4、CPLD下载板一块;5、微机一台;6、示波器一台;三、实验原理m序列产生电路在通信电路设计中十分重要,它广泛使用在扩频通信、信号产生、仪器仪表等等电路中。

m序列有时也称伪噪声(PN)或伪随机序列,在一段周期内其自相关性类似于随机二进制序列。

尽管伪噪声序列是确定的,但其具有很多类似随机二进制序列的性质,例如0和1的数目大致相同,将序列平移后和原序列的相关性很小。

PN序列通常由序列逻辑电路产生,一般是由一系列的两状态存储器和反馈逻辑电路构成。

二进制序列在时钟脉冲的作用下在移位寄存器中移动,不同状态的输出逻辑组合起来并反馈回第一级寄存器作为输入。

当反馈由独立的“异或”门组成(通常是这种情况),此时移位寄存器称为线性PN序列发生器。

如果线性移位寄存器在某些时刻到达零状态,它会永远保持零状态不变,因此输出相应地变为全零序列。

因为n阶反馈移位寄存器只有2n-1个非零状态,所以由n阶线性寄存器生成的PN序列不会超过2n-1个。

周期为2n-1的线性反馈寄存器产生的序列称为最大长度(ML)序列——m序列。

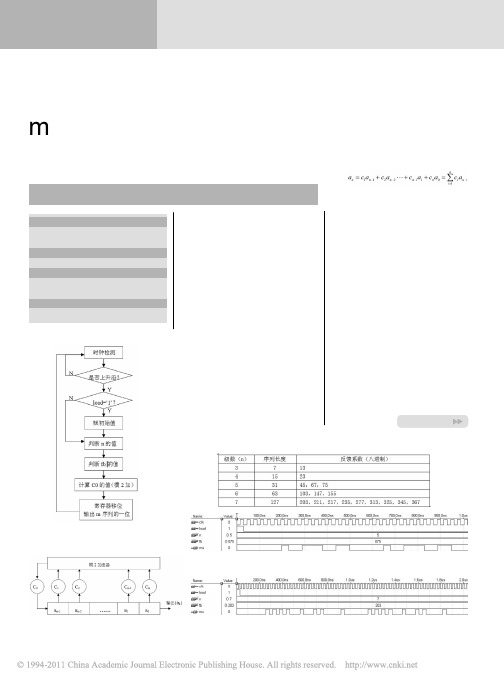

m 序列发生器的一般组成m 序列发生器一般组成如上图所示,它用n 级移位寄存器作为主支路,用若干级模2加法器作为各级移位寄存器的抽头形成线性反馈支路。

各抽头的系数hi 称为反馈系数,它必须按照某一个n 次本原多项式:∑==ni i i x h x h 0)(中的二进制系数来取值。

在伪序列发生模块中,可以根据本原多项式的系数,…..h 8、h 7、h 6、h 5、h 4、h 3、h 2、h 1、h 0产生m 序列,这些系数可表示8进制数(1代表相连抽头进入反馈回路,0代表该抽头不进入反馈回路),如:13、23、103、203四、 课题设计要求在输入时钟256KHz 的时钟作用下,可在外部跳线器的控制下改变产生不同的m 序列,在程序中定义的几个变量为:输入: Main_CLK :输入 256KHz 主时钟 M_Sel[1..0]:选择输出不同的m 序列当 Mode[]=0:本原多项式为13(8进制表示); 当 Mode[]=1:本原多项式为23(8进制表示); 当 Mode[]=2:本原多项式为103(8进制表示); 当 Mode[]=3:本原多项式为203(8进制表示);输出: M_Out :m 序列输出 说明:1、 M_Sel[1..0]与复接模块的m_sel0、m_sel1相连; M_Out 在测试点TPB01输出;五、 实验步骤1、将JH5001二次开发光盘内的基本程序m.tdf 及其它相关程序(在光盘的“2th\student_m ”子目录下)拷入机器内。

基于FPGA的VHDL语言m序列生成详解+源码

说明可控m序列产生器我分成四个小模块来做,M,M1,M2,M3分别对应为:m序列产生器、控制器、码长选择器、码速率选择器。

一、M: m序列产生器这是该设计的核心部分,原理就是设计一个通用m序列产生子单元,然后由外部选择器来写入码型,码长等参数,加以循环可连接成任意长度的m序列产生器,其子单元结构如下:如上图,若N=15,就有15个这样的子单元首尾相接。

注意:开头和结尾的两个子单元会有所不同,因为首单元需要输入初值,尾单元要进行直通反馈,在程序里请多留意。

图中,主要部件是一个D触发器,Q(N+1)为上一级输出;Q(N)既是本级输出;CP为选择后的时钟脉冲;B(N)为本级参数选择控制;A(N)受控于B(N),决定本级输出Q(N)是否反馈(B(N)为1时反馈);C(N)为本级反馈;C(N-1)为下一级反馈。

具体原理参看m序列组成结构。

此外,本程序还加入了EN(发送控制)、RN(首单元置数)、SEL1(码长选择,即N的选择,N=2-15)、SEL2(码型选择,即正逆码选择)四个控制端,可满足设计要求。

OP为码输出端。

二、M1:控制器控制器主要是将外部的序列发送控制信号STA转换为EN和RN 两个控制信号。

其中,EN与STA的波形基本一致,只是它与CP进行了同步处理;RN在EN为‘1’的头一个脉冲周期里置高电平,以达到为序列发生器的首端置数的目的。

如果不清楚的话可以看一下它的模拟波形。

(注意:STA要采用自锁定开关,高电平有效)三、M2:码长选择序列的码长选择既是N值的选择,码长=2**N-1。

核心就是一个计数器,可从2计到15。

按一次PUSH就可以自动加一(注意:按键建议采用自弹跳按键,如过需要软件清除按键震颤的话,我再做发给你),没有0,1两个状态。

如果需要的话还可以扩展7段数码管的接口,以显示N值。

四、M3:码速率选择器码的传输速率是靠CP来控制的,CP的频率就等于码元速率。

这段程序包含一个倍频器,一个5分频的分频器,可把5MHZ的脉冲源CLK扩展成1MHZ和10MHZ。

课程设计论文基于FPGA的m序列发生器

基于FPGA的m序列发生器摘要m序列广泛应用于密码学、通信、雷达、导航等多个领域,本文提出了一种基于FPGA的伪随机序列产生方法,应用移位寄存器理论从序列的本原多项式出发,获得产生该序列的移位寄存器反馈逻辑式,结合FPGA芯片结构特点,在序列算法实现中采用元件例化语句。

算法运用VHDL语言编程,以A1tera的QuartusⅡ软件为开发平台,给出了序列的仿真波形。

序列的统计特性分析表明:该方法产生的序列符合m序列的伪随机特性,验证了算法的正确性。

关键词:m序列;移位寄存器理论;VHDL语言目录摘要 (I)1 m序列 (1)1.1 理论基础 (1)1.1.1 线性反馈移位寄存器 (2)2 m序列的性质 (5)2.1 均衡性 (5)2.2游程特性 (5)2.4 自相关特性 (5)2.5 伪噪声特性 (7)3 m序列的应用 (9)3.1 扩展频谱通信 (9)3.2 通信加密 (10)4 开发工具简介 (11)4.1 Quartus II简介 (11)4.2 数字系统开发流程 (12)4.3 FPGA简介 (12)5 m序列生成器仿真分析 (16)5.1 反馈系数表存储器设计 (16)5.2 移位存储器设计 (17)5.3 仿真分析 (18)参考文献 (20)附录 (22)1 m序列m序列是伪随机序列的一种 ,结构简单 ,实现方便。

在现代工程实践中 , m 序列在通讯、导航、雷达、通信系统性能的测量等领域中有着广泛的应用。

例如 , 在连续波雷达中可用作测距信号 , 在遥控系统中可用作遥控信号 , 在多址通信中可用作地址信号 , 在数字通信中可用作群同步信号 ,还可用作噪声源及在保密通信中起加密作用等。

伪噪声发生器在测距、通信等领域的应用日益受到人们重视。

目前,m序列产生实现方法主要有3种:(1)门电路实现该方法设计简单,但随移位寄存器级数的增长,电路装调困难,且占用的印制板面积较大。

(2)DSP编程实现该方法专业性过强,不适合一般用户。