基于可编程逻辑器件的四位奇偶校验器设计

基于verilog语言的四位奇校检电路在BASYS2上的实现

管脚配置

NET "p" LOC = P7; NET "p1" LOC = A7; NET "q" LOC = M5; #b和b2为输入,配置到8个拨码开关上,p1配置到按键上, b3用灯显示出接收的数据,校检位和校检结果都用灯显示

管脚配置

# PlanAhead Generated physical constraints NET "b[3]" LOC = N3; NET "b[2]" LOC = E2; NET "b[1]" LOC = F3; NET "b[0]" LOC = G3; NET "b2[3]" LOC = B4; NET "b2[2]" LOC = K3; NET "b2[1]" LOC = L3; NET "b2[0]" LOC = P11; NET "b3[3]" LOC = G1; NET "b3[1]" LOC = N4; NET "b3[0]" LOC = N5; NET "b3[2]" LOC = P4;

erilog代码

assign b1=b; //b1=b,发送端发送出b assign b3=b2; //显示接收端接收的数据 assign p=b[0]^b[1]^b[2]^b[3]^1; //算出发 送端校检位p assign q=p1^b2[0]^b2[1]^b2[2]^b2[3]^1; //算 出接收端校检结果,0正确,1有一位错 endmodule

基于verilog语言的四位奇校检 电路在BASYS2上的实现

实验四位计数器设计样本

实验四 4 位计数器设计1.实验目学习quartusii 和modelsim用法;学习原理图和veriloghdl混合输入设计办法;掌握4 位计数器设计设计及仿真办法。

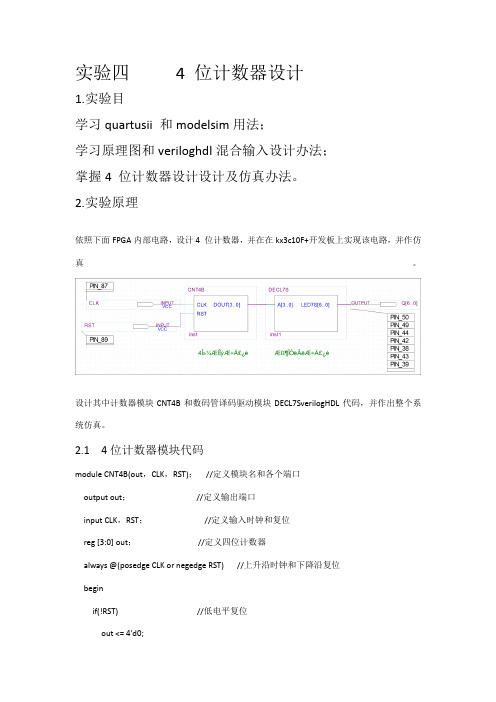

2.实验原理依照下面FPGA内部电路,设计4 位计数器,并在在kx3c10F+开发板上实现该电路,并作仿真。

设计其中计数器模块CNT4B和数码管译码驱动模块DECL7SverilogHDL代码,并作出整个系统仿真。

2.1 4位计数器模块代码module CNT4B(out,CLK,RST);//定义模块名和各个端口output out;//定义输出端口input CLK,RST;//定义输入时钟和复位reg [3:0] out;//定义四位计数器always @(posedge CLK or negedge RST) //上升沿时钟和下降沿复位beginif(!RST) //低电平复位out <= 4'd0;elseout <= out + 1;//每一种clk计数endendmodule效果图:2.2七段数码管代码module segled(out1,a);//定义模块名和输入输出端口input [3:0]a;//输入一种3位矢量output [6:0]out1;//输出一种6位矢量reg [6:0]out1;//reg型变量用于always语句always@(a) //敏感信号abegincase(a) //case语句用于选取输出4'b0000:out1<=7'b0111111;4'b0001:out1<=7'b0000110;4'b0010:out1<=7'b1011011; 4'b0011:out1<=7'b1001111; 4'b0100:out1<=7'b1100110; 4'b0101:out1<=7'b1101101; 4'b0110:out1<=7'b1111101; 4'b0111:out1<=7'b0000111; 4'b1000:out1<=7'b1111111; 4'b1001:out1<=7'b1101111; 4'b1010:out1<=7'b1110111; 4'b1011:out1<=7'b1111100; 4'b1100:out1<=7'b0111001; 4'b1101:out1<=7'b1011110; 4'b1110:out1<=7'b1111001; 4'b1111:out1<=7'b1110001; endcaseendendmodule //模块结束效果图:2.3综合模块代码// Copyright (C) 1991- Altera Corporation// Your use of Altera Corporation's design tools,logic functions// and other software and tools,and its AMPP partner logic// functions,and any output files from any of the foregoing// (including device programming or simulation files),and any// associated documentation or information are expressly subject // to the terms and conditions of the Altera Program License// Subscription Agreement,Altera MegaCore Function License// Agreement,or other applicable license agreement,including,// without limitation,that your use is for the sole purpose of// programming logic devices manufactured by Altera and sold by // Altera or its authorized distributors. Please refer to the// applicable agreement for further details.// PROGRAM "Quartus II 64-Bit"// VERSION "Version 13.1.0 Build 162 10/23/ SJ Web Edition" // CREATED "Tue Apr 11 22:35:09 "module cou(CLK,RST,Q);input wire CLK;input wire RST;output wire [6:0] Q;wire [3:0] SYNTHESIZED_WIRE_0; CNT4B b2v_inst(.CLK(CLK),.RST(RST),.out(SYNTHESIZED_WIRE_0)); segled b2v_inst1(.a(SYNTHESIZED_WIRE_0),.out1(Q));endmodule效果图:3.实验设备kx3c10F+开发板,电脑。

实验五 奇偶校验器的设计

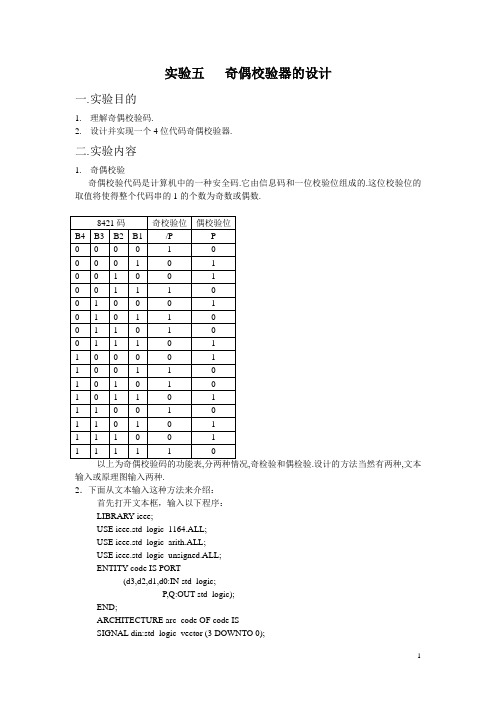

实验五奇偶校验器的设计一.实验目的1.理解奇偶校验码.2.设计并实现一个4位代码奇偶校验器.二.实验内容1.奇偶校验奇偶校验代码是计算机中的一种安全码.它由信息码和一位校验位组成的.这位校验位的取值将使得整个代码串的1的个数为奇数或偶数.以上为奇偶校验码的功能表,分两种情况,奇检验和偶检验.设计的方法当然有两种,文本输入或原理图输入两种.2.下面从文本输入这种方法来介绍:首先打开文本框,输入以下程序:LIBRARY ieee;USE ieee.std_logic_1164.ALL;USE ieee.std_logic_arith.ALL;USE ieee.std_logic_unsigned.ALL;ENTITY code IS PORT(d3,d2,d1,d0:IN std_logic;P,Q:OUT std_logic);END;ARCHITECTURE arc_code OF code ISSIGNAL din:std_logic_vector (3 DOWNTO 0);SIGNAL dout:std_logic_vector (1 DOWNTO 0);BEGINdin<=d3&d2&d1&d0;PROCESS (din)BEGINCASE din ISWHEN"0000"=>dout<="10";WHEN"0001"=>dout<="01";WHEN"0010"=>dout<="01";WHEN"0011"=>dout<="10";WHEN"0100"=>dout<="01";WHEN"0101"=>dout<="10";WHEN"0110"=>dout<="10";WHEN"0111"=>dout<="01";WHEN"1000"=>dout<="01";WHEN"1001"=>dout<="10";WHEN"1010"=>dout<="10";WHEN"1011"=>dout<="01";WHEN"1100"=>dout<="10";WHEN"1101"=>dout<="01";WHEN"1110"=>dout<="01";WHEN others=>dout<="10";END CASE;END PROCESS;P<=dout(1);Q<=dout(0);END arc_code;3.打开波形图输入,并导入图形三、心得体会:经过此次实验,体会到文本输入方式在某种程序上比原理输入方法会简单易操作,进一步熟悉MAXPLUS的操作。

四位奇偶校验器的设计

题目:基于可编程逻辑器件的四位奇偶校验器设计指导老师:学生姓名:所属院系:专业:班级:学号:完成日期:本科生课程设计任务书班级:姓名:设计题目:基于可编程逻辑器件的四位奇偶校验器设计要求完成的内容:1.设计出一个奇偶校验逻辑电路,当四位数中有奇数个1时输出结果为1;否则为0。

2.写出该电路的真值表。

3.采用逻辑门电路或可编程逻辑阵列PLA实现。

4.画出详细的电路图。

5.写出详细的原理说明。

指导教师:教研室主任:一、概述奇偶校验是一种荣誉编码校验,在存储器中是按存储单元为单位进行的,是依靠硬件实现的,因而适时性强,但这种校验方法只能发现奇数个错,如果数据发生偶数位个错,由于不影响码子的奇偶性质,因而不能发现。

奇偶校验是一种校验代码传输正确性的方法。

根据被传输的一组二进制代码的数位中“1”的个数是奇数或偶数来进行校验。

采用奇数的称为奇校验,反之,称为偶校验。

采用何种校验是事先规定好的。

通常专门设置一个奇偶校验位,用它使这组代码中“1”的个数为奇数或偶数。

若用奇校验,则当接收端收到这组代码时,校验“1”的个数是否为奇数,从而确定传输代码的正确性。

二、写出详细的原理说明奇偶校验法是对数据传输正确性的一种校验方法。

我们所涉及的奇偶校验逻辑电路是用来表示传输的数据中"1"的个数是奇数还是偶数,为奇数时,校验位置为"1",否则置为"0"。

例如,需要传输"1101",数据中含3个"1",所以其奇校验位为"1",需要传输"1111",数据中含4个"1",所以其偶校验位为"0"。

上面设计的奇偶校验逻辑电路就是属于单向奇偶校验逻辑电路,当我们输入一个四位数1000时A,B端所流的直流通过U1A异或门后输出为高电平,而C,D 端所流的直流通过U2A异或门后输出为低电平,它们个别通过U6A和U7A非门后输出的是低电平,高电平。

4位alu设计实验报告

4位alu设计实验报告引言阿里巴巴淘宝研发部需要一个高效的算术逻辑单元(ALU),用于处理复杂的计算任务。

本实验旨在设计并实现一个4位ALU,以满足淘宝研发部的需求。

设计思路功能需求根据淘宝研发部的需求,4位ALU需实现以下基本功能:1. 加法运算2. 减法运算3. 与门运算4. 或门运算5. 异或门运算6. 比较两个数的大小(等于、大于、小于)设计方案为了实现这些功能,我们将使用以下组件:1. 4位全加器电路- 用于加法运算2. 4位比较器电路- 用于比较运算3. 4位逻辑门电路- 用于与门、或门、异或门运算设计方案如下:实验步骤1. 设计并实现4位全加器电路2. 设计并实现4位比较器电路3. 设计并实现4位逻辑门电路4. 使用以上电路组件实现4位ALU电路5. 进行基本运算和比较测试,验证ALU功能是否正确实验结果通过实验验证,4位ALU完成了预期的功能需求。

以下是一些测试样例及输出结果:加法运算- 输入:A=1010,B=0011- 输出:Sum=1101减法运算- 输入:A=1010,B=0011- 输出:Diff=0111与门运算- 输入:A=1010,B=0011- 输出:A&B=0010或门运算- 输入:A=1010,B=0011- 输出:A B=1011异或门运算- 输入:A=1010,B=0011- 输出:A^B=1001比较运算- 输入:A=1010,B=0011- 输出:A>B=0001结论本实验成功设计并实现了一个功能齐全的4位ALU电路,能够满足淘宝研发部的需求。

经过测试,ALU能够正确执行加法、减法、与门、或门、异或门以及比较运算。

这个高效的ALU电路将在处理复杂计算任务时发挥巨大作用。

实验一4位运算器设计

实验⼀4位运算器设计实验⼆ 4 位运算器设计⼀、实验名称:4 位运算器设计⼆、实验学时:5 学时三、实验⽬的:1. 利⽤Verilog建⽴4位运算器模型2. 对所设计的运算器进⾏功能验证四、实验内容:设计⼀个四位算术逻辑运算器电路,并测试其功能。

具体要求如下:1. 设计运算器,实验加减乘、逻辑与、或等功能和⾃⾏设计记录表格2. 输⼊端的0,1 可由拨码开关模拟3. 输出端接Led 灯显⽰输出数据4. 观察输出结果,记录输⼊、输出数据。

五、实验原理:1. ALU原理算术逻辑单元 (Arithmetic-Logic Unit, ALU)是中央处理器的执⾏单元,是所有中央处理器的核⼼组成部分,由"And Gate" 和"Or Gate"构成的算术逻辑单元,主要功能是进⾏⼆位元的算术运算,如加减乘(不包括整数除法)。

2. ⽤拨码开关来模拟 0、1 输⼊3. led指⽰灯显⽰输出4. ⽤按钮来模拟 0、1的低位进位输⼊六、实验步骤:1.根据实验要求作预习报告。

2.建⽴⼯程,设计程序:1)新建⼯程;2)新建verilog HDL⽂件(注:⽂件名和模块名称要和⼯程名保持⼀致)。

3)调试程序:3. 配置管脚:参照实验指导中的管脚图,配置管脚。

4.下载到开发板,观察实验结果,尝试创造⾃⼰的实验⽅案:七、实验报告要求:1. 说明实验⽬的、原理、步骤2. 实验程序及程序分析3. 给出试验结果(显⽰的结果,如照⽚或计算机绘制图⽚)4. 给出实验记录,并对记录进⾏分析。

5. 总结分析实验中所出现的问题,有何收获和体会。

fpga四位二进制奇偶校验器列举法

fpga四位二进制奇偶校验器列举法FPGA(Field Programmable Gate Array)是一种可编程逻辑芯片,具有良好的灵活性和可配置性。

在FPGA中实现奇偶校验器是常见的应用之一。

本文将介绍FPGA中实现四位二进制奇偶校验器的列举法。

四位二进制奇偶校验器实现原理:奇偶校验是指在二进制数中,根据某一位上的数的性质(偶数或奇数)而决定该位上的数值是0还是1。

对于一个二进制字串,如果其中1的个数是偶数,则在最高位补0,否则补1,这个补进去的数字就是奇偶校验位。

列举法实现四位二进制奇偶校验器的过程为:1. 将输入信号I0、I1、I2、I3分别取反,形成四个信号i0、i1、i2、i3。

2. 计算输入信号和取反信号i0、i1、i2、i3的和,产生四个和信号S0、S1、S2、S3。

3. 对和信号进行取反,产生四个反码信号NS0、NS1、NS2、NS3。

4. 对于原始输入信号及其反码,共有16种情况,每种情况对应一个输出信号O,共产生16个输出信号,用列表记录如下:输入信号 | 输出信号-----------|---------0000 | 00001 | 10010 | 10011 | 00100 | 10101 | 00110 | 00111 | 11000 | 11001 | 01010 | 01011 | 11100 | 01101 | 11110 | 11111 | 05. 对于FPGA来说,以上过程具体实现可以使用VHDL语言进行描述。

在VHDL中,需要定义输入信号和输出信号的类型及其位宽。

具体VHDL代码可参考下面的实现示例。

以VHDL语言实现奇偶校验器的例子:entity parity_checker isport (input : in std_logic_vector(3 downto 0); output : out std_logic);end parity_checker;architecture Behavioral of parity_checker issignal i0, i1, i2, i3 : std_logic;signal s0, s1, s2, s3 : std_logic;signal ns0, ns1, ns2, ns3 : std_logic;begini0 <= not input(0);i1 <= not input(1);i2 <= not input(2);i3 <= not input(3);s0 <= input(0) xor i0;s1 <= input(1) xor i1;s2 <= input(2) xor i2;s3 <= input(3) xor i3;ns0 <= not s0;ns1 <= not s1;ns2 <= not s2;ns3 <= not s3;output <= ns0 and ns1 and s2 and s3 orns0 and s1 and ns2 and s3 orns0 and s1 and s2 and ns3 ors0 and ns1 and ns2 and s3 ors0 and ns1 and s2 and ns3 ors0 and s1 and ns2 and ns3 ors0 and s1 and s2 and s3 orns0 and ns1 and ns2 and ns3;end Behavioral;以上是列举法实现四位二进制奇偶校验器的具体过程和VHDL代码实现示例,希望对读者有所帮助。

数字电子技术实验报告——基于FGPA的4位智能抢答器(verilog HDL)

基于FPGA的4位智能抢答器一、设计任务要求基于E DA/SOPC 系统开发平台,运用Q uartusⅡ可编程逻辑器件开发软件,设计一个4位智能抢答器,在开发箱上,本系统使用频率为1000 赫兹的时钟脉冲。

要求如下:1、可以同时供4名选手抢答,其编号分别为1、2、3、4,各用抢答按键S1、S2、S3、S4,按键编号与选手编号对应。

主持人设置有一个“开始”按键S5,一个“复位”按键S6,用于控制抢答的开始和系统的复位;各个按键按下为“0”,弹起为“1”;2、系统上电和按下“复位”按键后4位数码管显示“0000”,此时只有“开始”按键有效,其他按键不起作用;3、当主持人按下“开始”按键后,开始计时,数码管左边两位显示计时的时间,单位为“秒”;如果有选手按下抢答按键,定时器停止工作,数码管显示器上左边两个数码管显示抢答时刻的时间;选手编号立即锁存并显示在右边的两个数码管上,同时封锁输入电路,禁止其他选手抢答;此状态一直保持到主持人将系统复位为止;4、抢答的有效时间为10 秒,如果定时抢答的时间已到而没有选手抢答,本次抢答无效,封锁输入电路,禁止抢答,数码管左边显示“10”,右边显示“00”;此状态一直保持到主持人将系统复位为止;5、附加提高:在主持人未按下开始按键时,如果有人抢答则犯规,在数码管上右边两位闪烁犯规选手的编号,闪烁频率为0.5H Z,左边两位显示“00”;此状态一直保持到主持人将系统复位为止。

二、设计步骤本次设计主要采用V erilog HDL 语言,总体编程思路采用模块化设计方式,主要分为3 个模块,一个主控制及按键输入模块,一个计时显示模块,一个抢答组号显示模块,分别对这3个子模块进行独立编程设计,编译仿真通过并生成元件,在顶层使用原理图或者Verilog HDL 语言的方式将3个模块连接起来完成整个设计。

锁定管脚并编译仿真通过,下载到开发箱进行测试。

三、模块设计思路对于这个任务来说,计时显示模块和抢答组号显示模块的模块并不复杂,复杂的模块是主控制及按键输入模块,所以我决定再将主控制模块拆分成两个小的模块——按键输入模块、按键输入判断输出模块。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

新疆大学课程设计

题目:基于可编程逻辑器件的四位奇偶校验器设计指导老师:

学生姓名:

所属院系:电气工程学院

专业:

班级:

学号:

完成日期:2013年01月04日

新疆大学

本科生课程设计任务书

班级:姓名:

设计题目:基于可编程逻辑器件的四位奇偶校验器设计

要求完成的内容:1.设计出一个奇偶校验逻辑电路,当四位数中有奇数个1时输出结果为1;否则为0。

2.写出该电路的真值表。

3.采用逻辑门电路或可编程逻辑阵列PLA实现。

4.画出详细的电路图。

5.写出详细的原理说明。

指导教师:

教研室主任:

一、概述

奇偶校验是一种荣誉编码校验,在存储器中是按存储单元为单位进行的,是依靠硬件实现的,因而适时性强,但这种校验方法只能发现奇数个错,如果数据发生偶数位个错,由于不影响码子的奇偶性质,因而不能发现。

奇偶校验是一种校验代码传输正确性的方法。

根据被传输的一组二进制代码的数位中“1”的个数是奇数或偶数来进行校验。

采用奇数的称为奇校验,反之,称为偶校验。

采用何种校验是事先规定好的。

通常专门设置一个奇偶校验位,用它使这组代码中“1”的个数为奇数或偶数。

若用奇校验,则当接收端收到这组代码时,校验“1”的个数是否为奇数,从而确定传输代码的正确性。

二、写出详细的原理说明

奇偶校验法是对数据传输正确性的一种校验方法。

我们所涉及的奇偶校验逻辑电路是用来表示传输的数据中"1"的个数是奇数还是偶数,为奇数时,校验位置为"1",否则置为"0"。

例如,需要传输"1101",数据中含3个"1",所以其奇校验位为"1",需要传输"1111",数据中含4个"1",所以其偶校验位为"0"。

上面设计的奇偶校验逻辑电路就是属于单向奇偶校验逻辑电路,当我们输入一个四位数1000时A,B端所流的直流通过U1A异或门后输出为高电平,而C,D 端所流的直流通过U2A异或门后输出为低电平,它们个别通过U6A和U7A非门后输出的是低电平,高电平。

最后通过与非门时输出为高电平,灯亮。

当我们输入1100时A,B端所流的直流通过U1A异或门后输出为低电平,而C,D 端所流的直流通过U2A异或门后输出为低电平,流过U6A和U7A非门后输出的是高电平,高电平。

通过与非门时输出为低电平,灯灭。

其他14个四位数的原理都跟这上面的原理类似。

备注:( A, B, C, D 分别为校验器的四个输入端,Y时校验器的输出端) 画出该电路的卡诺图:

写出该电路的表达式:

()()()

()()()

()ABCD ABCD ABCD ABCD ABCD ABCD ABCD ABCD AB C D AB CD CD AB C D AB CD CD AB C D AB AB C D AB C D AB AB A B C D A B C D A B

+++++++=⊕+++⊕++=⊕++⊕+=⊕++⊕=⊕+⊕=⊕⊕

四、采用逻辑门电路或可编程逻辑阵列PLA 实现

五、画出详细的电路图

当四位数中有奇数个1时的电路图(输出结果为1,灯亮):

当四位数中有偶数个1时的电路图(输出结果为0,灯灭):

六、总结与体会

为了系统的可靠性,对于位数较少,电路较简单的应用,可以采用奇偶校验的方法。

奇校验是通过增加一位校验位的逻辑取值,在源端将原数据代码中为1的位数形成奇数,然后在宿端使用该代码时,连同校验位一起检查为1的位数是否是奇数,做出进一步操作的决定。

奇偶校验只能检查一位错误,且没有纠错的能力。

偶校验道理与奇校验相同,只是将校验位连同原数据代码中为1的位数形成偶数。

奇偶校验器多设计成九位二进制数,以适应一个字节,一个ASCII代码的应用要求。

在这次设计的过程中我们也遇到了很多困难,难免会遇到过各种各样的问题,同时在设计的过程中发现了自己的不足之处,对以前所学过的知识理解得不够深刻,掌握得不够牢固,比如说在设计奇偶校验逻辑电路的时候,该用哪个芯片,怎么使用,如何来设计电路图都把我们难道了,最后还是认真的看书和讨论才明白了解决这些问题的思路。

光设计电路图然后输出结果上花了整整的两天时间。

通过这次课程设计还锻炼了我们的团队合作精神,只有大家在分工明确的基础上齐心协力,才能是团队获得成就。

通过这次课程设计使我懂得了理论与实际相结合是很重要的,只有理论知识是远远不够的,只有把所学的理论知识与实践相结合起来,从理论中得出结论,才能真正为社会服务,从而提高自己的实际动手能力和独立思考的能力。

附:主要参考书目:

《电子基础技术》

《网络资料》

《电子基础技术实验指导书》

要求:1、封面页、任务书页和指导教师评语页采用给定的模版。

封面页、任务书页分别为第一、第二页,指导教师评语页为最后一页。

2、论文内容采用小四号字打印。

asanjian0531@。