DPRAM空间分配和数据交换流程

MPC8280多通道HDLC控制器的应用

MPC8280多通道HDLC控制器的应用1 概述时分复用是当前同步通信系统中用以提高数据传输效率的常用方法。

例如第2代移动通信GSM系统,光同步传输网SDH等都是使用时分复用的例子。

在现代通信设备的研发中,常常会遇到高速背板通信、多协议接口、网络管理信令通道等需要同时处理多个同步通信接口数据的情况。

本文介绍了一种采用MPC8280处理器芯片内部的多通道通信控制单元,来处理多个同步通信接口数据的方法。

MPC8280是飞思卡尔公司PowerQUICC II产品线的较新成员。

它采用0.13 μm工艺制造。

内核、I/O的供电电压分别为1.5 V、3.3 V。

MPC8280相比该公司的MPC8260,制造工艺和工作频率均有所提升,但因为核心电压下降,功耗反而下降。

而且,MPC8280片内的DPRAM(双口静态存储器)容量增加了一倍,此外还增加了PCI 和USB。

MPC8280芯片由主内核、SIU、CPM等3个主要功能模块组成,。

MPC8280的处理器主内核称为G2_LE,它是一种PowerPC架构的多级流水线超标量处理器。

MPC8280内核运行频率为166~450 MHz。

SIU模块主要负责60x总线控制、PCI桥及时钟产生。

CPM模块负责处理通信事务,即处理SCC、SMC、FCC、MCC、USB、SPI、I2C等通信控制单元收发数据。

本文所述的多通道HDLC控制器即采用CPM下的MCC(多通道控制器)通信控制单元来实现。

MPC8280片内集成的静态存储器包括DPRAM、全局配置寄存器、SI RAM(串行接口路由表配置空间)。

其中,第1块32 KB的数据DPRAM空间被等分成16个bank(存储空间块)。

CPM 中的通信控制单元除了使用全局配置寄存器进行最基本的参数配置外,还须使用参数配置存储区块进一步配置。

一般CPM中每个通信控制单元都有2个参数配置存储区块,参数配置存储区块均定位在DPRAM中的指定地址。

可编程逻辑基本设计原则

(1)面积和速度的平衡与互换原则。

“面积”指一个设计所消耗FPGA/CPLD的逻辑资源数量:对于FPGA,可以用所消耗的触发器(FF)和查找表(LUT)来衡量;对于CPLD,常用宏单元(MC)衡量。

“速度”指设计在芯片上稳定运行时所能达到的最高频率,这个频率由设计的时序状况决定,与设计满足的时钟周期、PAD to PAD time、clock setup time、clock hold time和clock-to-output delay等众多时序特征量密切相关。

如果设计的时序余量比较大,运行的频率比较高,则意味着设计的健壮性更强,整个系统的质量更有保证;另一方面,设计所消耗的面积更小,则意味着在单位芯片上实现的功能模块更多,需要的芯片数量更少,整个系统的成本也随之大幅度消减。

相比之下,满足时序、工作频率的要求更重要一些,当两者冲突时,采用速度优先的准则。

从理论上讲,一个设计如果时序余量较大,所能跑的频率远远高于设计要求,那么就能通过功能模块复用减少整个设计消耗的芯片面积,用速度的优势换面积的节约;反之,如果设计的时序要求很高,普通方法达不到设计频率,那么一般可以通过将数据流串并转换,并行复制多个操作模块,对整个设计进行“乒乓操作”和“串并转换”的思想进行处理,在芯片输出模块处再对数据进行“并串转换”。

“面积换速度”的思想:首先将输入的高速数据进行串并转换,然后利用较低的速度对多个模块并行处理所分配的数据,最后将处理结果“并串转换”,完成数据速率的要求。

这样我们在整个处理模块的两端看都是高速数据流。

操作过程中还涉及很多的方法和技巧,例如,对高速数据流进行串并转换,采用“乒乓操作”方法提高数据处理速率等。

(2)硬件原则。

for循环语句的使用:实际工作中,除了描述仿真测试激励(testbench)时使用for循环语句外,极少在RTL级编码中使用for循环,因为for循环会被综合器展开为所有变量情况的执行语句,每个变量独立占用寄存器资源,每条执行语句并不能有效地复用硬件逻辑资源,造成巨大的资源浪费。

stp协议原理交互流程

stp协议原理交互流程STP协议(Spanning Tree Protocol)是一种用于在以太网中防止环路和冗余的网络协议。

它的原理是通过选择一个主干路径来屏蔽其他冗余路径,从而确保网络的稳定性和可靠性。

STP协议的交互流程如下:1. 网络中的所有交换机都默认为非根交换机,并且处于阻塞状态。

每个交换机都会发送BPDU(Bridge Protocol Data Units)消息来与其他交换机进行通信。

2. BPDU消息包含了交换机的优先级、MAC地址和路径成本等信息。

交换机会通过比较收到的BPDU消息来确定网络中的根交换机。

3. 在收到BPDU消息后,交换机会根据接收到的BPDU消息更新自己的状态。

如果收到的BPDU消息中的优先级比自己的优先级高,交换机将更新自己的优先级,并将发送更改后的BPDU消息。

4. 当交换机通过BPDU消息确定了根交换机后,它将选择一条与根交换机连接的最佳路径,并将其设置为非阻塞状态。

这条路径被称为根端口。

5. 对于与根交换机相连的交换机,它们会选择一条与根交换机连接的最佳路径,并将其设置为非阻塞状态。

这条路径被称为根端口。

6. 对于与根交换机相连的交换机,它们会选择一条与根交换机连接的次优路径,并将其设置为阻塞状态。

这样可以避免环路的产生。

7. 当网络中的拓扑结构发生变化时,交换机会重新计算路径并更新自己的状态。

这样可以保证网络中的路径始终是最优的。

通过STP协议,网络中的交换机可以自动选择最佳路径,并避免环路和冗余。

这样可以提高网络的可靠性和性能,并减少网络故障的发生。

STP协议的原理和交互流程使得网络管理员可以轻松管理和维护以太网网络,确保网络的稳定运行。

DP及其操作流程

DP及其操作流程DP(动态规划)是一种通过空间换时间的优化方法,适用于有重叠子问题和最优子结构性质的问题。

DP算法适用于求解最优化问题,其基本思想是将原问题划分为若干个相互重叠的子问题,逐步求解子问题,并保存每个子问题的最优解,最终得到原问题的最优解。

DP的操作流程包括以下几个步骤:1.确定状态:首先确定问题的状态,即用什么变量来表示问题的状态。

状态可以是用一个或多个变量来描述问题的特征,例如背包问题中的背包容量和物品数量。

2.定义状态转移方程:根据问题的最优子结构性质,定义状态之间的转移关系。

状态转移方程描述了子问题之间的递推关系,可以通过递归或迭代的方式求解。

3.初始化边界条件:确定初始状态的值,即将问题的边界条件定义为初始状态的值。

通常需要设置初始状态或者一些特殊的边界条件,以便开始DP算法的递推过程。

4.递推求解:根据状态转移方程和初始状态,逐步求解子问题,并保存每个子问题的最优解。

通常需要使用一个二维数组或者其他数据结构来保存子问题的解。

5.返回结果:根据子问题的最优解,得到原问题的最优解。

通常是在递推过程中保存一些状态信息,最后根据这些信息恢复原问题的最优解。

DP算法的时间复杂度通常是O(n^2)或者O(n^3),其中n是问题的规模。

通过合适地定义状态转移方程和设计递推过程,可以优化DP算法的时间复杂度,降低计算复杂度。

举个例子来说明DP算法的操作流程:假设有一个背包容量为W,有n 个物品,每个物品的重量分别为w1,w2,...,wn,价值分别为v1,v2,...,vn。

要求在背包容量不超过W的情况下,装入物品的最大总价值。

1.确定状态:定义状态dp[i][j]表示在前i个物品中,背包容量为j 时的最大总价值。

2.定状态转移方程:dp[i][j]的值可以由dp[i-1][j]和dp[i-1][j-w[i]]+v[i]决定,即在前i-1个物品的情况下,背包容量为j的最大总价值与装入第i个物品后的最大总价值之间取最大值。

分组交换工作过程

分组交换工作过程

分组交换是一种通信方式,它将数据分割成多个小块或“分组”,然后在网络中独立传输这些分组。

下面是分组交换工作过程的一般步骤:

1.数据分割:首先,将需要传输的数据分割成若干个小的数据分组,每个分组称为一个数据报或数据包。

2.传输:每个数据分组独立地通过网络进行传输。

每个分组可能会经过不同的路由,这取决于网络的当前状态和路由选择算法。

3.路由选择:在网络中,每个节点(或路由器)会根据其路由表选择最佳路径来传输数据分组。

这是动态的,因为网络状态会不断变化。

4.数据重组:当数据分组到达目的地时,它们会被重新组装成原始的数据。

这个过程也称为数据报重组或数据报恢复。

5.差错控制:为了确保数据的完整性和正确性,可能会使用差错控制机制,如校验和、重传、确认等。

6.流量控制:为了防止网络拥塞,还需要实施流量控制机制,例如使用滑动窗口协议等。

分组交换的好处是它可以根据网络状况动态地选择最佳路径,从而提高了网络的利用率和可靠性。

此外,由于数据分组是

独立传输的,所以可以同时使用多个路径来加速数据的传输。

然而,这也增加了网络协议的复杂性。

单片机数据存储空间分配

单片机数据存储空间分配日期: 2007-03-20 10:391、 data区空间小,所以只有频繁用到或对运算速度要求很高的变量才放到data区内,比如for循环中的计数值。

2、 data区内最好放局部变量。

因为局部变量的空间是可以覆盖的(某个函数的局部变量空间在退出该函数是就释放,由别的函数的局部变量覆盖),可以提高内存利用率。

当然静态局部变量除外,其内存使用方式与全局变量相同;3、确保你的程序中没有未调用的函数。

在Keil C里遇到未调用函数,编译器就将其认为可能是中断函数。

函数里用的局部变量的空间是不释放,也就是同全局变量一样处理。

这一点Keil C做得很愚蠢,但也没办法。

4、程序中遇到的逻辑标志变量可以定义到bdata中,可以大大降低内存占用空间。

在51系列芯片中有16个字节位寻址区bdata,其中可以定义8*16=128个逻辑变量。

定义方法是: bdata bit LedState;但位类型不能用在数组和结构体中。

5、其他不频繁用到和对运算速度要求不高的变量都放到xdata区。

6、如果想节省data空间就必须用large模式,将未定义内存位置的变量全放到xdata 区。

当然最好对所有变量都要指定内存类型。

7、当使用到指针时,要指定指针指向的内存类型。

在C51中未定义指向内存类型的通用指针占用3个字节;而指定指向data区的指针只占1个字节;指定指向xdata区的指针占2个字节。

如指针p是指向data区,则应定义为: char data *p;。

还可指定指针本身的存放内存类型,如:char data * xdata p;。

其含义是指针p指向data区变量,而其本身存放在xdata区。

查看全文 | (已有0条评论) 查看评论发表评论鲜花:0朵送鲜花便便:0坨扔便便单片机原理日期: 2007-03-20 10:37单片机原理随着大规模集成电路的出现及其发展,将计算的 CPU 、 RAM 、 ROM 、定时 / 计数器和多种 I/O接口集成在一片芯片上,形成芯片级的计算机,因此单片机早期的含义称为单片微型计算机,直译为单片机。

5GNR学习笔记-理论v1.0

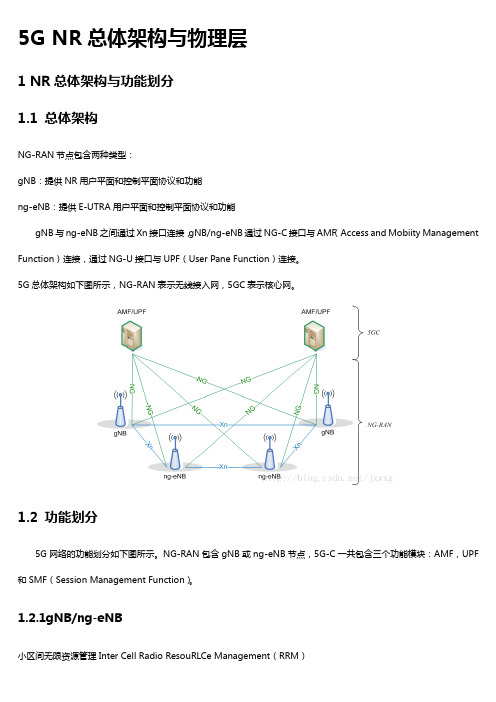

5G NR总体架构与物理层1 NR总体架构与功能划分1.1 总体架构NG-RAN节点包含两种类型:gNB:提供NR用户平面和控制平面协议和功能ng-eNB:提供E-UTRA用户平面和控制平面协议和功能gNB与ng-eNB之间通过Xn接口连接,gNB/ng-eNB通过NG-C接口与AMF(Access and Mobiity Management Function)连接,通过NG-U接口与UPF(User Pane Function)连接。

5G总体架构如下图所示,NG-RAN表示无线接入网,5GC表示核心网。

1.2 功能划分5G网络的功能划分如下图所示。

NG-RAN包含gNB或ng-eNB节点,5G-C一共包含三个功能模块:AMF,UPF 和SMF(Session Management Function)。

1.2.1gNB/ng-eNB小区间无限资源管理Inter Cell Radio ResouRLCe Management(RRM)无线承载控制Radio Bear(RB)Contro连接移动性控制Connection Mobiity Contro测量配置与规定Measurement Configuration and Provision 动态资源分配Dynamic ResouRLCe Aocation1.2.2AMFNAS安全Non-Access Stratum(NAS)Security空闲模式下移动性管理Ide State Mobiity Handing1.2.3UPF移动性锚点管理Mobiity AnchoringPDU处理(与Internet连接)PDU Handing1.2.4SMF用户IP地址分配UE IP Address AocationPDU Session控制1.3 网络接口1.3.1NG接口NG-U接口用于连接NG-RAN与UPF,其协议栈如下图所示。

协议栈底层采用UDP、IP协议,提供非保证的数据交付。

各类RAM,FIFO及FLASH总结

RAM,FIFO及FLASH总结1 RAMRAM(random access memory)随机存储器。

存储单元的内容可按需随意取出或存入,且存取的速度与存储单元的位置无关的存储器。

这种存储器在断电时将丢失其存储内容,故主要用于存储短时间使用的程序。

按照存储信息的不同,机存储器又分为静态随机存储器(Static RAM,SRAM)和动态随机存储器(Dynamic RAM,DRAM)。

1.1S RAMSRAM是Static Random Access Memory的缩写,中文含义为静态随机访问存储器,它是一种类型的半导体存储器。

“静态”是指只要不掉电,存储在SRAM 中的数据就不会丢失。

这一点与动态RAM(DRAM)不同,DRAM需要进行周期性的刷新操作。

然后,我们不应将SRAM与只读存储器(ROM)和Flash Memory相混淆,因为SRAM是一种易失性存储器,它只有在电源保持连续供应的情况下才能够保持数据。

“随机访问”是指存储器的内容可以以任何顺序访问,而不管前一次访问的是哪一个位置。

SRAM中的每一位均存储在四个晶体管当中,这四个晶体管组成了两个交叉耦合反向器。

这个存储单元具有两个稳定状态,通常表示为0和1。

另外还需要两个访问晶体管用于控制读或写操作过程中存储单元的访问。

因此,一个存储位通常需要六个MOSFET。

对称的电路结构使得SRAM的访问速度要快于DRAM。

SRAM比DRAM访问速度快的另外一个原因是SRAM可以一次接收所有的地址位,而DRAM则使用行地址和列地址复用的结构。

SRAM不应该与SDRAM相混淆,SDRAM代表的是同步DRAM (Synchronous DRAM),这与SRAM是完全不同的。

SRAM也不应该与PSRAM 相混淆,PSRAM是一种伪装成SRAM的DRAM。

从晶体管的类型分,SRAM可以分为双极性与CMOS两种。

从功能上分,SRAM可以分为异步SRAM和同步SRAM(SSRAM)。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

DPRAM空间分配和数据交换流程

本文是PKSPEC 405EP-FPGA板上DPRAM接口的内存空间分配,以及与DSP板交换数据的操作流程。

405EP-FPGA板上DPRAM实际上有64K Bytes,其中前32Kbytes是PPC向DSP发送数据的缓冲区,而后32Kbytes是DSP向PPC发送数据的缓冲区。

前32Kbytes是一个整体,也就是说,PPC每次向DSP发送的数据不超过32Kbytes。

后32Kbytes被分成两个16Kbytes,目前计划每次DSP向PPC发送的数据为16Kbytes,最后的16Kbytes做为预留。

系统的内存分配图如下所示:

图1,系统DPRAM分配示意图

数据交换流程分为两个部分,一个是PPC向DSP发送数据的流程;一个是DSP向PPC发送数据的流程。

PPC向DSP发送数据流程如下:

首先,PPC向发送缓冲区(32Kbytes)写入数据。

写入完成以后,PPC将输出GPIO1置低,然后置高,也就是输出一个低电平有效的低脉冲。

DSP接收到该脉冲以后,从发送缓冲区(对DSP来说是接收缓冲区)接收数据。

总数据量不超过32Kbytes。

至此,PPC到DSP的数据流程结束。

PPC从DSP接收数据流程如下:

DSP不断处理模拟前端的数据,并且将准备好的数据不断写入DPAM的接收缓冲区的前16Kbytes(对DSP来说是发送缓冲区)。

等到16Kbytes写入完成之后,DSP从输入GPIO1给PPC的中断发送一个低电平的中断信号。

PPC接收到中断以后,进入中断处理程序接收16Kbytes数据。

并且存储到内部的ramdisk 中(也就是内存中)。

随后以太网发送程序会准备将数据传输会到PC。

然后PowerPC从输出GPIO2发送一个低电平有效的脉冲给DSP,表示PowerPC已经

将数据读取完毕。

至此,PPC从DSP接收数据的流程结束。

2007年1月2日薛涛于流星花园。