计算机组成原理实验

计算机组成原理实验(接线、实验步骤)

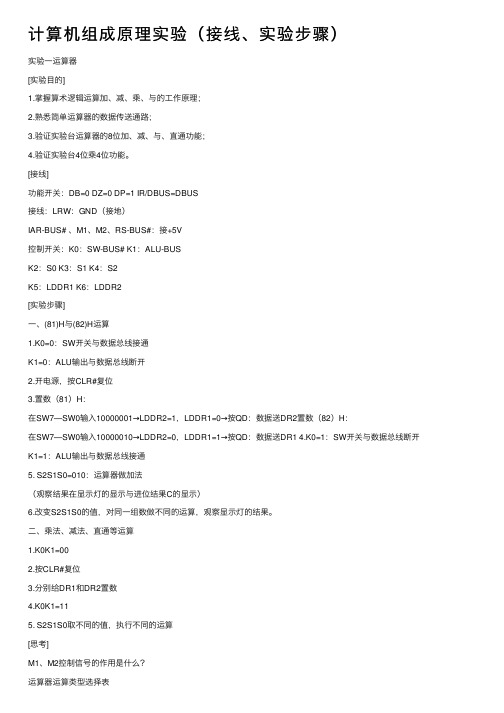

计算机组成原理实验(接线、实验步骤)实验⼀运算器[实验⽬的]1.掌握算术逻辑运算加、减、乘、与的⼯作原理;2.熟悉简单运算器的数据传送通路;3.验证实验台运算器的8位加、减、与、直通功能;4.验证实验台4位乘4位功能。

[接线]功能开关:DB=0 DZ=0 DP=1 IR/DBUS=DBUS接线:LRW:GND(接地)IAR-BUS# 、M1、M2、RS-BUS#:接+5V控制开关:K0:SW-BUS# K1:ALU-BUSK2:S0 K3:S1 K4:S2K5:LDDR1 K6:LDDR2[实验步骤]⼀、(81)H与(82)H运算1.K0=0:SW开关与数据总线接通K1=0:ALU输出与数据总线断开2.开电源,按CLR#复位3.置数(81)H:在SW7—SW0输⼊10000001→LDDR2=1,LDDR1=0→按QD:数据送DR2置数(82)H:在SW7—SW0输⼊10000010→LDDR2=0,LDDR1=1→按QD:数据送DR1 4.K0=1:SW开关与数据总线断开K1=1:ALU输出与数据总线接通5. S2S1S0=010:运算器做加法(观察结果在显⽰灯的显⽰与进位结果C的显⽰)6.改变S2S1S0的值,对同⼀组数做不同的运算,观察显⽰灯的结果。

⼆、乘法、减法、直通等运算1.K0K1=002.按CLR#复位3.分别给DR1和DR2置数4.K0K1=115. S2S1S0取不同的值,执⾏不同的运算[思考]M1、M2控制信号的作⽤是什么?运算器运算类型选择表选择操作S2 S1 S00 0 0 A&B0 0 1 A&A(直通)0 1 0 A+B0 1 1 A-B1 0 0 A(低位)ΧB(低位)完成以下表格ALU-BUS SW-BUS# 存储器内容S2S1S0 DBUS C输⼊时:计算时:DR1:01100011DR2:10110100(与)DR1:10110100DR2:01100011(直通)DR1:01100011DR2:01100011(加)DR1:01001100DR2:10110011(减)DR1:11111111DR2:11111111(乘)实验⼆双端⼝存储器[实验⽬的]1.了解双端⼝存储器的读写;2.了解双端⼝存储器的读写并⾏读写及产⽣冲突的情况。

计算机组成原理实验报告

实验一:数字逻辑——交通灯系统设计子实验1:7 段数码管驱动电路设计(1)理解利用真值表的方式设计电路的原理;(2)利用Logisim 真值表自动生成电路的功能,设计一个 7 段数码管显示驱动。

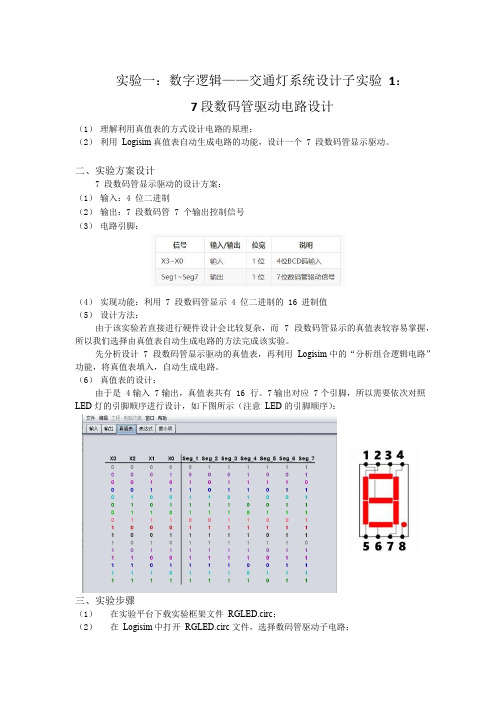

二、实验方案设计7 段数码管显示驱动的设计方案:(1)输入:4 位二进制(2)输出:7 段数码管 7 个输出控制信号(3)电路引脚:(4)实现功能:利用 7 段数码管显示 4 位二进制的 16 进制值(5)设计方法:由于该实验若直接进行硬件设计会比较复杂,而7 段数码管显示的真值表较容易掌握,所以我们选择由真值表自动生成电路的方法完成该实验。

先分析设计 7 段数码管显示驱动的真值表,再利用Logisim 中的“分析组合逻辑电路”功能,将真值表填入,自动生成电路。

(6)真值表的设计:由于是 4输入 7输出,真值表共有 16 行。

7输出对应 7个引脚,所以需要依次对照LED 灯的引脚顺序进行设计,如下图所示(注意LED 的引脚顺序):三、实验步骤(1)在实验平台下载实验框架文件RGLED.circ;(2)在Logisim 中打开RGLED.circ 文件,选择数码管驱动子电路;(3)点击“工程”中的“分析组合逻辑电路”功能,先构建4输入和7输出,再在“真值表”中,将已设计好的真值表的所有数值仔细对照着填入表格中,确认无误后点击“生成电路”,自动生成的电路如下图所示:(4)将子电路封装为如下形式:(5)进行电路测试:·自动测试在数码管驱动测试子电路中进行测试;·平台评测自动测试结果满足实验要求后,再利用记事本打开RGLED.circ 文件,将所有文字信息复制粘贴到Educoder 平台代码区域,点击评测按钮进行测试。

四、实验结果测试与分析(1)自动测试的部分结果如下:(2)平台测试结果如下:综上,本实验测试结果为通过,无故障显示。

本实验的关键点在于:在设计时需要格外注重LED 灯的引脚顺序,保证0-9 数字显示的正确性,设计出正确的真值表。

计算机组成原理实验说明

实验一运算器组成实验一、实验目的1.熟悉双端口通用存放器堆〔组〕的读写操作。

2.熟悉简单运算器的数据传送通路。

3.验证运算器74LS181的算术逻辑功能。

4.按给定数据,完成指定的算术、逻辑运算。

二、实验原理上图是本实验所用的运算器数据通路图。

参与运算的数据首先通过实验台操作板上的八个二进制数据开关SW7-SW0来设置,然后输入到双端口通用存放器堆RF中。

RF由一个ispLSI1016实现,功能上相当于四个8位通用存放器,用于保存参与运算的数据,运算后的结果也要送到RF中保存。

双端口存放器堆模块的控制信号中,RS1、RS0用于选择从B端口〔右端口〕读出的通用存放器,RD1、RD0用于选取从A端口〔左端口〕读出的通用存放器。

而WR1、WR0用于选择写入的通用存放器。

LDRi是写入控制信号,当LDRi=1时,数据总线DBUS上的数据在T3写入由WR1、WR0指定的通用存放器。

RF的A、B端口分别与操作数暂存器DR1、DR2相连:另外,RF的B端口通过一个三态门连接到数据总线DBUS 上,因而RF中的数据可以直接通过B端口送到DBUS上。

DR1和DR2各由1片74LS273构成,用于暂存参与运算的数据。

DR1接ALU 的A输入端口,DR2接ALU的B端口。

ALU由两片74LS181构成,ALU的输出通过一个三态门(74LS244)发送到数据总线DBUS上。

图中尾巴上带粗短线标记的信号都是控制信号,其中S3,S2,Sl,S0,M,#,LDDR2,LDDRl,ALU-BUS#,SW-BUS#、LDRi、RS1、RS0、RD1、RD0、WR1、WR0等是电位信号,用电平开关K0—Kl5来模拟。

T2、T3是脉冲信号,印制板上已连接到实验台的时序电路上。

#为低电平有效。

K0—K15是一组用于模拟各控制电平信号的开关,开关向上时为1,开关向下时为0,每个开关无固定用途,可根据实验具体情况选用。

实验中进展单拍操作,每次只产生一组Tl,T2,T3,T4脉冲,需将实验台上的DP,DB开关进展正确设置。

计算机组成原理数据通路实验报告

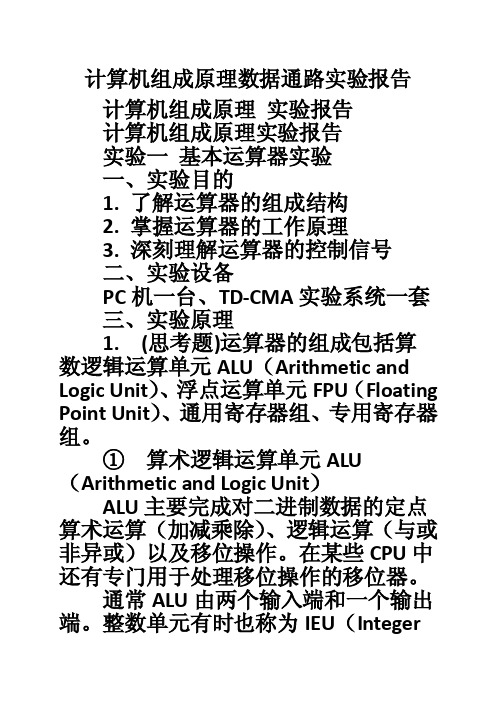

计算机组成原理数据通路实验报告计算机组成原理实验报告计算机组成原理实验报告实验一基本运算器实验一、实验目的1. 了解运算器的组成结构2. 掌握运算器的工作原理3. 深刻理解运算器的控制信号二、实验设备PC机一台、TD-CMA实验系统一套三、实验原理1. (思考题)运算器的组成包括算数逻辑运算单元ALU(Arithmetic and Logic Unit)、浮点运算单元FPU(Floating Point Unit)、通用寄存器组、专用寄存器组。

①算术逻辑运算单元ALU (Arithmetic and Logic Unit)ALU主要完成对二进制数据的定点算术运算(加减乘除)、逻辑运算(与或非异或)以及移位操作。

在某些CPU中还有专门用于处理移位操作的移位器。

通常ALU由两个输入端和一个输出端。

整数单元有时也称为IEU(IntegerExecution Unit)。

我们通常所说的“CPU 是XX位的”就是指ALU所能处理的数据的位数。

②浮点运算单元FPU(Floating Point Unit)FPU主要负责浮点运算和高精度整数运算。

有些FPU还具有向量运算的功能,另外一些则有专门的向量处理单元。

③通用寄存器组通用寄存器组是一组最快的存储器,用来保存参加运算的操作数和中间结果。

④专用寄存器专用寄存器通常是一些状态寄存器,不能通过程序改变,由CPU自己控制,表明某种状态。

而运算器内部有三个独立运算部件,分别为算术、逻辑和移位运算部件,逻辑运算部件由逻辑门构成,而后面又有专门的算术运算部件设计实验。

下图为运算器内部原理构造图2. 运算器的控制信号实验箱中所有单元的T1、T2、T3、T4都连接至控制总线单元的T1、T2、T3、T4,CLR都连接至CON单元的CLR按钮。

T4由时序单元的TS4提供(脉冲信号),其余控制信号均由CON单元的二进制数据开关模拟给出。

控制信号中除T4为脉冲信号外,其余均为电平信号,其中ALU_B为低有效,其余为高有效。

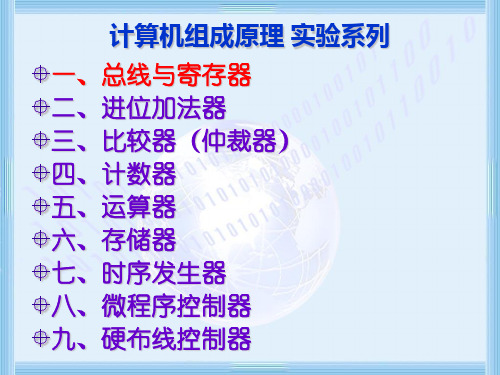

计算机组成原理实验2.1总线与寄存器

1) 令#R0_BUS= #DR_BUS= #SFT_BUS=1,#SW_BUS=0;启动仿 真,通过拨码开关送入总线BUS任意八位二进制数,赋值 74LS194的输入端D0D1D2D3。按照后页的逻辑功能表置位 74LS194的MR、S1、S0 、SL、SR端,观察并记录CLK端上升 沿和下降沿跳变时刻输出端Q0Q1Q2Q3的状态。

2) 令#SW_BUS=0,三态门74LS244导通,记录BUS总线上的数 据,与总线BIN相比较:

BUS_7 BUS_6 BUS_5 BUS_4 BUS_3 BUS_2 BUS_1 BUS_0 BUS总线

单位D触发器:74LS74 四位D触发器:74LS175

D触发器逻辑功能 表

【2】D触发器实验(一Fra bibliotek总线与寄存器 实验 电路图

三态门74LS244

拨码开关与总线缓冲器(注意观察74LS244左右电平)

【1】总线实验

实验步骤:

1) #SW_BUS = #R0_BUS= #DR_BUS= #SFT_BUS=1;启动仿真, 手动拨码开关在总线DIN上置位数据0x55。比较拨码开关 所在的总线DIN与总线BUS上的数据。

实验步骤:

1) 令#R0_BUS= #DR_BUS= #SFT_BUS=1, #SW_BUS=0,启动 仿真,手动拨码开关输入数据到BUS总线,改变74LS74的 D端(即BUS总线的BUS_0)状态,按照后页逻辑功能表置 位74LS74的#Sd端、#Rd端,观察并记录CLK端上升沿 、 下降沿跳变时刻的Q端和#Q端状态。

的0xAA数据存入DR。观察寄存器74LS273的输出端。 6) 再令#R0_BUS=1;观察寄存器74LS374的输出端,请比较器

计算机组成原理实验介绍

计算机组成原理实验介绍《计算机组成原理实验介绍》1. 引言嘿,你有没有想过,当你打开电脑玩游戏或者处理文档的时候,电脑内部到底在发生着什么样神奇的事情呢?就像一个神秘的黑盒子,我们只看到了它呈现出来的效果,却不太清楚里面的构造和运行机制。

今天啊,咱们就来一起探索计算机组成原理实验的那些事儿,从最基础的概念到实际的应用,再到一些常见的问题,就像给这个神秘的黑盒子打开一道缝,好好地瞧一瞧里面的奥秘。

在这篇文章里,我们会先讲讲计算机组成原理实验的基本概念和理论背景,然后分析它的运行机制,还会看看在生活和高端技术领域的应用,也会聊聊大家对它可能存在的误解,最后再补充一些相关知识,总结一下并且展望未来。

2. 核心原理2.1基本概念与理论背景计算机组成原理啊,说白了就是研究计算机到底是由哪些部分组成的,以及这些部分是怎么协同工作的这么一门学科。

它的理论来源可以追溯到计算机诞生的时候,最早的那些计算机科学家们就开始琢磨怎么把一些基本的计算功能通过硬件组合起来。

就好比盖房子,你得先有砖头、水泥这些基本的材料(也就是计算机的各种硬件组件),然后还得知道怎么把它们搭在一起(各组件的连接和协同工作方式)。

从发展历程来看,最开始的计算机可不像现在这么小巧玲珑、功能强大。

早期的计算机那可是庞大无比,像个巨兽一样,而且功能还很单一。

随着时间的推移,计算机组成的理论不断发展,各种新的组件被发明出来,它们之间的协作也变得越来越高效。

比如说,从简单的算术逻辑单元,发展到现在复杂的中央处理器(CPU),这里面包含了无数科学家和工程师的智慧结晶。

2.2运行机制与过程分析咱们先把计算机想象成一个超级大的工厂。

首先是输入设备,这就像是工厂的原材料进货口。

比如说你敲键盘输入信息,就相当于把原材料送进了工厂。

这些原材料(数据)通过系统总线这个“传送带”,被送到了CPU 这个“加工中心”。

CPU呢,就像是工厂里最聪明的工程师,它能根据接收到的数据进行各种运算和处理。

计组实验报告(共10篇)

计组实验报告(共10篇)计组实验报告计算机组成原理实验报告一一、算术逻辑运算器1. 实验目的与要求:目的:①掌握算术逻辑运算器单元ALU(74LS181)的工作原理。

②掌握简单运算器的数据传输通道。

③验算由74LS181等组合逻辑电路组成的运输功能发生器运输功能。

④能够按给定数据,完成实验指定的算术/逻辑运算。

要求:完成实验接线和所有练习题操作。

实验前,要求做好实验预习,掌握运算器的数据传送通道和ALU 的特性,并熟悉本实验中所用的模拟开关的作用和使用方法。

实验过程中,要认真进行实验操作,仔细思考实验有关的内容,把自己想得不太明白的问题通过实验去理解清楚,争取得到最好的实验结果,达到预期的实验教学目的。

实验完成后,要求每个学生写出实验报告。

2. 实验方案:1.两片74LS181(每片4位)以并/串联形式构成字长为8为的运算器。

2.8为运算器的输出经过一个输入双向三态门(74LS245)与数据总线相连,运算器的两个数据输入端分别与两个8位寄存器(74LS273)DR1和DR2的输出端相连,DR1和DR2寄存器是用于保存参加运算的数据和运算的结果。

寄存器的输入端于数据总线相连。

3.8位数据D7~D0(在“INPUT DEVICE”中)用来产生参与运算的数据,并经过一个输出三态门(74LS245)与数据总线相连。

数据显示灯(BUS UNIT)已与数据总线相连,用来显示数据总线上所内容。

4.S3、S2、S1、S0是运算选择控制端,由它们决定运算器执行哪一种运算(16种算术运算或16种逻辑运算)。

5.M是算术/逻辑运算选择,M=0时,执行算术运算,M=1时,执行逻辑运算。

6.Cn是算术运算的进位控制端,Cn=0(低电平),表示有进位,运算时相当于在最低位上加进位1,Cn=1(高电平),表示无进位。

逻辑运算与进位无关。

7.ALU-B是输出三态门的控制端,控制运算器的运算结果是否送到数据总线BUS上。

低电平有效。

计算机组成原理实验报告

实验1 通用寄存器实验一、实验目的1.熟悉通用寄存器的数据通路。

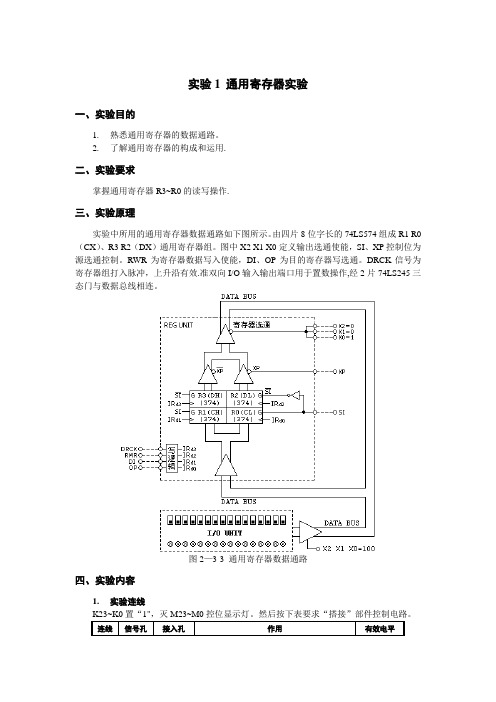

2.了解通用寄存器的构成和运用.二、实验要求掌握通用寄存器R3~R0的读写操作.三、实验原理实验中所用的通用寄存器数据通路如下图所示。

由四片8位字长的74LS574组成R1 R0(CX)、R3 R2(DX)通用寄存器组。

图中X2 X1 X0定义输出选通使能,SI、XP控制位为源选通控制。

RWR为寄存器数据写入使能,DI、OP为目的寄存器写选通。

DRCK信号为寄存器组打入脉冲,上升沿有效.准双向I/O输入输出端口用于置数操作,经2片74LS245三态门与数据总线相连。

图2—3-3 通用寄存器数据通路四、实验内容1.实验连线连线信号孔接入孔作用有效电平2.寄存器的读写操作①目的通路当RWR=0时,由DI、OP编码产生目的寄存器地址,详见下表.通用寄存器“手动/搭接”目的编码②通用寄存器的写入通过“I/O输入输出单元”向R0、R1寄存器分别置数11h、22h,操作步骤如下:通过“I/O输入输出单元”向R2、R3寄存器分别置数33h、44h,操作步骤如下:③源通路当X2~X0=001时,由SI、XP编码产生源寄存器,详见下表.通用寄存器“手动/搭接”源编码④ 通用寄存器的读出关闭写使能,令K18(RWR )=1,按下流程分别读R0、R1、R2、R3。

五、实验心得通过这个实验让我清晰的了解了通用寄存器的构成以及通用寄存器是如何运用的,并且熟悉了通用寄存器的数据通路,而且还深刻的掌握了通用寄存器R3~R0的读写操作。

实验2 运算器实验一、实验目的掌握八位运算器的数据传输格式,验证运算功能发生器及进位控制的组合功能.二、实验要求完成算术、逻辑、移位运算实验,熟悉ALU 运算控制位的运用.三、实验原理实验中所用的运算器数据通路如图2-3—1所示。

ALU 运算器由CPLD 描述。

运算器的输出FUN 经过74LS245三态门与数据总线相连,运算源寄存器A 和暂存器B 的数据输入端分别由2个74LS574锁存器锁存,锁存器的输入端与数据总线相连,准双向I/O 输入输出端口用来给出参与运算的数据,经2片74LS245三态门与数据总线相连。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验一

实验目的:通过了解高级语言源程序和目标机器代码的不同表示及其相互转换,深刻理解高级语言和机器语言之间的关系,以及机器语言和不同体系结构之间的关系。

实验要求:对教材1.3.5 节给出的hello.c 源程序进行编译、链接,最终生成可执行目标代码。

实验报告:

1. 说明你做实验的过程(重要步骤用屏幕截图表示)。

第一步:下载FlexHEX软件。

第二步:编写hello.c源代码。

#include <stdio.h>

Int main()

{

Printf(“Hello!\n”);

Return 0;

}

第三步:用FlexHEX打开hello world源程序

第四步:用FlexHEX打开hello world可执行文件。

第五步:比较源程序文件的内容和可执行文件的内容

2. 给出源程序(文本文件)的内容(用十六进制形式表示)。

3. 给出可执行目标文件(二进制文件)的内容(用十六进制形式表示)。

4.(1)分析同一个源程序在不同机器上生成的可执行目标代码是否相同。

答:不相同。

因为对于不同的机器其硬件组成不同,例如:CPU。

所以同一个源程在不同机器上生成的可执行目标代码是不同的。

(2)你能在可执行目标文件中找出函数printf ()对应的机器代码段吗?能的话,请标示来。

答:不能。

因为源程序中的printf函数在可执行文件中已转换为机器语言。

被翻译的机器语言中有printf函数,但是不知道是从哪一段开始翻译的。

(3)为什么源程序文件的内容和可执行目标文件的内容完全不同?

答:因为源程序文件时可以直接编写的。

而可执行文件是被机器语言翻译过后的执

行内容。

所以内容不同。