数字集成电路设计实验--反相器

数字集成电路实验-反相器实验报告

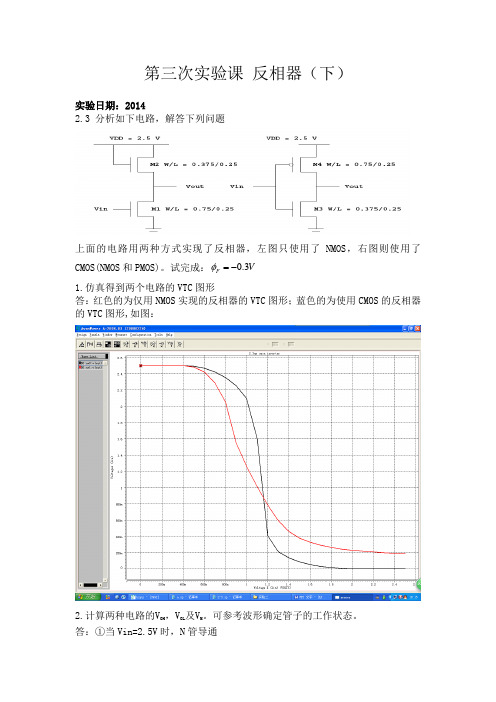

第三次实验课 反相器(下)实验日期:20142.3 分析如下电路,解答下列问题上面的电路用两种方式实现了反相器,左图只使用了NMOS ,右图则使用了CMOS(NMOS 和PMOS)。

试完成:V F 3.0-=φ1.仿真得到两个电路的VTC 图形答:红色的为仅用NMOS 实现的反相器的VTC 图形;蓝色的为使用CMOS 的反相器的VTC 图形,如图:2.计算两种电路的V OH ,V OL 及V M 。

可参考波形确定管子的工作状态。

答:①当Vin=2.5V 时,N 管导通有在体偏置条件下阀值电压公式:)22(0F SB F T T V V V φφγ-+-+=()()()⎥⎦⎤⎢⎣⎡--=⎥⎦⎤⎢⎣⎡--=⎥⎦⎤⎢⎣⎡--=22220'2011'222'OL OL T in n DS DS T GS M M n d DSAT DSAT T DD M M n DSAT V V V V L W k V V V V L W k I V V V V L W k I (M2速度饱和)将下列数据代人VV V A k V V V D SAT n F T 63.0,/10115,3.0,43.026'0=⨯=-==-φ25.075.0,25.0375.01122==M M M M L W L W解得: V V OL 2875.0=当Vin=0V 时,N 管截止,Vout=OH V =2.5V求解M V :当out in V V =时,由于GS DS V V =,M1工作在饱和区此时流过M1(速度饱和)的电流为:()⎥⎥⎦⎤⎢⎢⎣⎡--=22011'1DSAT DSAT T in M M n DSAT V V V V L W k I (1) 流过M2的电流为(速度饱和)()⎥⎥⎦⎤⎢⎢⎣⎡---=2222'2DSAT DSAT T out DD M M n DSAT V V V V V L W k I (2) )22(0F SB F T T V V V φφγ-+-+=(3)M out in SB V V V V ===联立方程解得M V =1.017V②对于CMOS 器件当Vin=0时,V V V out O H 5.2==当Vin=2.5时,V V V out O L 0==求解M V :当out in V V =时,由于GS DS V V =,NMOS 与PMOS 工作在饱和区由于T M D SAT V V V -<,此时已经发生了速度饱和(参考波形)代入,联立解得:将下列数据V V V V V V V V V A k V A k L W k k L W k k V k V k r r V V V r V V V V V V V V k V V V V k DSATp DSATn Tp Tn p n pp p p nn n n DSATnn DSATpp DSAT TP DD DSAT Tn M DSATp Tp DD M DSATp p DSATn Tn M DSATn n 1,63.04.0,43.0,/1030,/101151)2/()2/(0)2/()2/(26'26'''-==-==⨯-=⨯====+++++==---+----M V =1.132315968V3.哪一种结构的反相器的功能性更好,为什么?(噪声容限,再生性,过渡区增益)答:CMOS 反相器更好。

西工大 数字集成电路实验二、反相器(上)

数字集成电路实验报告西北工业大学2014年5月7日星期三实验二、反相器(上)一、分析电路,解答下面的问题。

1. 这个电路是不是反相器,为什么?该门属于有比逻辑,还是无比逻辑,为什么?答:该电路是反相器电路,因为当输入为0时,MOS 管截止,vout 连接到高电位Vdd ,当输入为Vdd 时,输出取决于MOS 管电阻与上面电阻的分压,是一个较低的电位。

该门是一个有比逻辑,因为输出与MOS 管的尺寸有关。

2. 计算出这个电路的VOH VOL 及VIH VIL 。

(计算可先排除速度饱和的可能)答:V V v V O H in 5.20=⇒=v V in 5.2=时,无法判断器件工作状态。

假设NMOS 工作在临界饱和区有:AI V R I vV V V AI V V L W K I D out L D T in out D T in D 61142`1073.55.207.243.05.21039.7)(2/--⨯=⇒+=⎪⎩⎪⎨⎧=-=-=⨯=⇒-⨯=这样的话根据D D I I <1说明器件饱和时,同一通路上下电流大小不一致。

那么Vout 必须相应减小使同一通路的电流一致,所以器件必定进入线性区。

进一步求Vol⎪⎪⎪⎩⎪⎪⎪⎨⎧=+=--=v V V R I V V V V L WK I in OL L D OL OL T in D 5.25.2]2)[(2` 6`10115-⨯=K 将,5.0/5.1=LW,43.0=T V 代入kohm R L 75=VVol A I 0.04638 10272.35=⨯=-(注:经过Hspice 仿真结果为0.0356V )当out in V V =时NMOS 工作在饱和区⎪⎩⎪⎨⎧+=-⨯=outL D T in D V R I V V L W K I 5.2)(2/2`可解得反相器阈值电压===out in M V V V 0.7932V此时 -9.3978V)43.0(875.25,)43.0(9375.125.22=--==--=in VinVoutin out V d d g V V ⎪⎪⎩⎪⎪⎨⎧=--==+=0.6116V ||0.8776V ||g V V V V g V V V M OH MIL M M IH分析电路噪声容限。

本科生课-集成电路版图设计-实验报告

西安邮电大学集成电路版图设计实验报告学号:XXX姓名:XX班级:微电子XX日期:20XX目录实验一、反相器电路的版图验证1)反相器电路2)反相器电路前仿真3)反相器电路版图说明4)反相器电路版图DRC验证5)反相器电路版图LVS验证6)反相器电路版图提取寄生参数7)反相器电路版图后仿真8)小结实验二、电阻负载共源放大器版图验证9)电阻负载共源放大器电路10)电阻负载共源放大器电路前仿真11)电阻负载共源放大器电路版图说明12)电阻负载共源放大器电路版图DRC验证13)电阻负载共源放大器电路版图LVS验证14)电阻负载共源放大器电路版图提取寄生参数15)电阻负载共源放大器电路版图后仿真16)小结实验一、反相器电路的版图验证1、反相器电路反相器电路由一个PMOS、NPOS管,输入输出端、地、电源端和SUB 端构成,其中VDD接PMOS管源端和衬底,地接NMOS管的漏端,输入端接两MOS管栅极,输出端接两MOS管漏端,SUB端单独引出,搭建好的反相器电路如图1所示。

图1 反相器原理图2、反相器电路前仿真通过工具栏的Design-Create Cellview-From Cellview将反相器电路转化为symbol,和schemetic保存在相同的cell中。

然后重新创建一个cell,插入之前创建好的反相器symbol,插入电感、电容、信号源、地等搭建一个前仿真电路,此处最好在输入输出网络上打上text,以便显示波形时方便观察,如图2所示。

图2 前仿真电路图反相器的输入端设置为方波信号,设置合适的高低电平、脉冲周期、上升时间、下降时间,将频率设置为参数变量F,选择瞬态分析,设置变量值为100KHZ,仿真时间为20u,然后进行仿真,如果仿真结果很密集而不清晰可以右键框选图形放大,如图3所示。

图3 前仿真结果3、反相器电路版图说明打开之前搭建好的反相器电路,通过Tools-Design Synthesis-Laout XL新建一个同cell目录下的Laout文件,在原理图上选中两个MOS管后在Laout中选择Create-Pick From Schematic从原理图中调入两个器件的版图模型。

反相器实训报告

一、实验目的1. 理解反相器的工作原理,掌握反相器的设计方法;2. 学习使用模拟电路设计软件,进行反相器电路的搭建与仿真;3. 提高动手实践能力,培养团队协作精神。

二、实验原理反相器是一种基本的逻辑门电路,其功能是将输入信号进行反转输出。

本实验采用CMOS反相器,由P型MOSFET和N型MOSFET组成。

当输入信号为高电平时,P型MOSFET导通,N型MOSFET截止,输出信号为低电平;当输入信号为低电平时,P 型MOSFET截止,N型MOSFET导通,输出信号为高电平。

三、实验仪器与材料1. 实验仪器:示波器、信号发生器、电源、面包板、导线等;2. 实验材料:CMOS集成电路芯片、电阻、电容等。

四、实验步骤1. 设计反相器电路:根据实验要求,设计一个简单的CMOS反相器电路,并绘制电路原理图。

2. 电路搭建:按照电路原理图,在面包板上搭建反相器电路,包括P型MOSFET、N型MOSFET、电阻、电容等元件。

3. 信号输入:使用信号发生器产生不同幅值的正弦波信号,作为反相器的输入信号。

4. 信号采集:使用示波器分别测量反相器的输入信号和输出信号,观察信号的变化。

5. 数据分析:分析反相器的输入输出特性,验证反相器的工作原理。

6. 仿真实验:使用模拟电路设计软件,对反相器电路进行仿真实验,观察仿真结果与实际实验结果是否一致。

五、实验结果与分析1. 实验结果通过实际搭建电路和仿真实验,观察到了以下现象:(1)当输入信号为高电平时,输出信号为低电平;当输入信号为低电平时,输出信号为高电平。

(2)实际实验和仿真实验结果基本一致,说明实验设计合理,电路搭建正确。

2. 数据分析(1)输入输出特性:反相器的输入输出特性如图1所示。

当输入信号为高电平时,输出信号为低电平;当输入信号为低电平时,输出信号为高电平。

(2)电路功耗:反相器的功耗主要来源于电阻和电容的功耗。

在本实验中,电路功耗较小,约为几毫瓦。

六、实验总结1. 通过本次实验,掌握了反相器的工作原理,学会了反相器的设计方法。

清华大学《数字集成电路设计》周润德 第5章 CMOS反相器

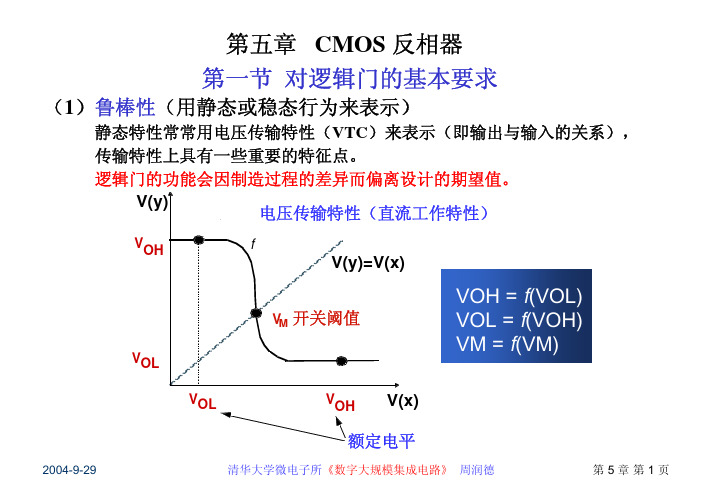

第五章 CMOS 反相器 第一节 对逻辑门的基本要求(1)鲁棒性(用静态或稳态行为来表示)静态特性常常用电压传输特性(VTC)来表示(即输出与输入的关系), 传输特性上具有一些重要的特征点。

逻辑门的功能会因制造过程的差异而偏离设计的期望值。

V(y) 电压传输特性(直流工作特性)VOH fV(y)=V(x)VM开关阈值VOL VOL VOHVOH = f(VOL) VOL = f(VOH) VM = f(VM)V(x)额定电平2004-9-29 清华大学微电子所《数字大规模集成电路》 周润德 第5章第1页(2)噪声容限:芯片内外的噪声会使电路的响应偏离设计的期望值 (电感、电容耦合,电源与地线的噪声)。

一个门对于噪声的敏感程度由噪声容限表示。

可靠性―数字集成电路中的噪声v(t) i(t)V DD电感耦合电容耦合电源线与地线噪声噪声来源: (1)串扰 (2)电源与地线噪声 (3)干扰 (4)失调 应当区分: (1)固定噪声源 (2)比例噪声源 浮空节点比由低阻抗电压源驱动的节点更易受干扰 设计时总的噪声容限分配给所预见的噪声源2004-9-29 清华大学微电子所《数字大规模集成电路》 周润德 第5章第2页噪声容限(Noise Margin)V“1” V OH V IHout OH 斜率 = -1V不确定区 斜率 = -1ILV “0” VVOLOL V IL V IH V in2004-9-29清华大学微电子所《数字大规模集成电路》 周润德第5章第3页噪声容限定义"1"噪声容限(Noise Margin) 容许噪声的限度V IH高电平 噪声容限VOHNM H未定义区 低电平 噪声容限V OL "0" NM L V IL抗噪声能力(Noise Immunity) 抑止噪声的能力门输出门输入2004-9-29清华大学微电子所《数字大规模集成电路》 周润德第5章第4页理想逻辑门V outg=∞Ri = ∞ Ro = 0 Fanout = ∞ NMH = NML = VDD/2V in2004-9-29清华大学微电子所《数字大规模集成电路》 周润德第5章第5页早期的逻辑门5.0 4.0 3.0 2.0 VM 1.0 NM H NM L0.01.02.03.0 V in (V)4.05.02004-9-29清华大学微电子所《数字大规模集成电路》 周润德第5章第6页(3) “再生”特性:逻辑门的“再生”特性使被干扰的信号能恢复到名义 的逻辑电平。

集成电路实验报告 反相器与非门设计

集成电路集中上机实验报告——反相器、与非门设计学院:专业:姓名:学号:一、实验目的(一)全面了解Schematic设计环境,并学会运用(二)掌握与非门、或非门、反相器等电路原理图输入方法(三)掌握逻辑符号创建方法二、实验原理启动Schematic Editor后,在命令解释窗口CIW中,打开任意库与单元中的Schematic视图,浏览Schematic Editing窗口,具体介绍如下:图2.1 Schematic Editing窗口菜单栏中可选菜单有Tool、Design、Window、Edit、Add、Check、Sheet、Options等项。

图标栏内的所有命令都可以在菜单栏实现,图标栏提供使用频率较高的一些菜单为快捷方式,旨在提高设计效率。

在设计过程中,除了可以使用图标快捷方式外,还有盲键(Bindkey)快捷方式。

Cadence系统安装过程中已经设置了通用的盲键,但用户可以根据自己的需要自行设置,在CIW窗口中,选择Options→Bindkeys,可以对所有设置的盲键自定义。

Cadence系统支持3D鼠标,左、中、右分别定义为LMB、MMB、RMB。

LMB用于点击和选择之用,MMB用于辅助编辑,RMB与LMB配合使用,在调查元件属性,局域放大,元件旋转等方面都有应用,在具体实验过程中有详细说明。

在所有元件的添加中,必须定义元件的属性。

最后,为了后续设计中执行仿真,每个元件必须具有物理模型(Model),在lab3中将有实例说明。

三、电路原理图设计的一般流程(一)创建库与视图(二)添加元件:在Schematic Editing窗口中,选择Add→Instance。

(三)添加Pins :在左侧Tool bar图标栏中选择pin icon图标,出现Add form,在Pin names栏中输入。

(四)添加Sources和Ground:选择Add→Instance,在Library column中选择analogLib,再选择vdd并添加到schematic中。

西工大数字集成电路实验报告_实验2反相器(上)代码

1. 2. 计算出这个电路的V OH V OL 及V IH V IL 。

(计算可先排除速度饱和的可能)V in =0时,V OH =2.5VV in=2.5时,假设NMOS 工作在临界饱和区:AI V R I vV V V A I V V L W K I D out L D T in out D T in D61142`1073.55.207.243.05.21039.7)(2/--⨯=⇒+=⎪⎩⎪⎨⎧=-=-=⨯=⇒-⨯=这样的话根据D D I I <1,器件实际工作在线性区⎪⎪⎪⎩⎪⎪⎪⎨⎧=+=--=v V V R I V V V V L W KI in OL L D OL OL T in D 5.25.2]2)[(2`6`10115-⨯=K 将, 5.0/5.1=L W,43.0=T V 代入kohm R L 75=解得:=OL V 0.04633V由图得:V OH =2.5V, V OL =0.0356V. 当out in V V =时,NMOS 工作在饱和区⎪⎩⎪⎨⎧+=-⨯=outL D T in D V R I V V L W K I 5.2)(2/2`反相器阈值电压===out in M V V V 0.7932 此时 -6.8978)43.0(875.255.2,)43.0(9375.125.22=--==--=in VinVoutin out V d d g V V ⎪⎪⎩⎪⎪⎨⎧=--==+=0.5458||0.9082||g V V V V g V V V M OH M IL M M IH由图得:V IH=0.881V, V IL=0.0378V.SP文件:.TITLE 1.2UM CMOS INVERTER.options probe.options tnom=25.options ingold=2 limpts=30000 method=gear.options lvltim=2 imax=20 gmindc=1.0e-12.protect.lib'C:\synopsys\cmos25_level49.lib' TT.unprotect.global vddMn out in 0 0 NMOS W=1.5u L=0.5u *(工艺中要求尺寸最大0.5u)RL OUT VDD 75kVDD VDD 0 2.5VVIN IN 0 0.DC VIN 0 2.5V 0.1V.op.probe dc v(out).end2.3.分析电路噪声容限。

数字集成电路设计实验报告

数字集成电路设计实验报告Prepared on 24 November 2020哈尔滨理工大学数字集成电路设计实验报告学院:应用科学学院专业班级:电科12 - 1班学号: 32姓名:周龙指导教师:刘倩2015年5月20日实验一、反相器版图设计1.实验目的1)、熟悉mos晶体管版图结构及绘制步骤;2)、熟悉反相器版图结构及版图仿真;2. 实验内容1)绘制PMOS布局图;2)绘制NMOS布局图;3)绘制反相器布局图并仿真;3. 实验步骤1、绘制PMOS布局图:(1) 绘制N Well图层;(2) 绘制Active图层; (3) 绘制P Select图层; (4) 绘制Poly图层; (5) 绘制Active Contact图层;(6) 绘制Metal1图层; (7) 设计规则检查;(8) 检查错误; (9) 修改错误; (10)截面观察;2、绘制NMOS布局图:(1) 新增NMOS组件;(2) 编辑NMOS组件;(3) 设计导览;3、绘制反相器布局图:(1) 取代设定;(2) 编辑组件;(3) 坐标设定;(4) 复制组件;(5) 引用nmos组件;(6) 引用pmos组件;(7) 设计规则检查;(8) 新增PMOS基板节点组件;(9) 编辑PMOS基板节点组件;(10) 新增NMOS基板接触点; (11) 编辑NMOS基板节点组件;(12) 引用Basecontactp组件;(13) 引用Basecontactn 组件;(14) 连接闸极Poly;(15) 连接汲极;(16) 绘制电源线;(17) 标出Vdd与GND节点;(18) 连接电源与接触点;(19) 加入输入端口;(20) 加入输出端口;(21) 更改组件名称;(22) 将布局图转化成T-Spice文件;(23) T-Spice模拟;4. 实验结果nmos版图pmos版图反相器的版图反相器的spice文件反相器的仿真曲线5.实验结论通过对仿真曲线的分析,当输入为高电平时,输出为低电平;当输入为低电平时,输出为高电平。