微电子工艺原理习题

微电子工艺习题答案(整理供参考)

第一章1.集成电路:通过一系列特定的加工工艺,将晶体管、二极管等有源器件和电阻、电容等无源器件,按照一定的电路互连,“集成”在一块半导体单晶片(如Si、GaAs)上,封装在一个外壳内,执行特定电路或系统功能。

集成电路发展的五个时代及晶体管数目:小规模集成电路(小于100个)、中规模集成电路(100~999)、大规模集成电路(1000~99999)、超大规模集成电路(超过10万)、甚大规模集成电路(1000万左右)。

2、硅片制备(Wafer preparation)、硅片制造(Wafer fabrication)硅片测试/拣选(Wafer test/sort)、装配与封装(Assembly and packaging)、终测(Final test)。

3、半导体发展方向:提高性能、提高可靠性、降低价格。

摩尔定律:硅集成电路按照4年为一代,每代的芯片集成度要翻两番、工艺线宽约缩小30%,IC工作速度提高1.5倍等发展规律发展。

4、特征尺寸也叫关键尺寸,集成电路中半导体器件能够加工的最小尺寸。

5、more moore定律:芯片特征尺寸的不断缩小。

从几何学角度指的是为了提高密度、性能和可靠性在晶圆水平和垂直方向上的特征尺寸的继续缩小,more than moore定律:指的是用各种方法给最终用户提供附加价值,不一定要缩小特征尺寸,如从系统组件级向3D集成或精确的封装级(SiP)或芯片级(SoC)转移。

6、High-K:高介电系数;low-K:低介电系数;Fabless:无晶圆厂;Fablite:轻晶片厂;IDM:Integrated Device Manufactory集成器件制造商;Foundry:专业代工厂;Chipless:无晶片1、原因:更大直径硅片,更多的芯片,单个芯片成本减少;更大直径硅片,硅片边缘芯片减小,成品率提高;提高设备的重复利用率。

硅片尺寸变化:2寸(50mm)-4寸(100mm)-5寸(125mm)-6寸(150mm)-8寸(200mm)-12寸(300mm)-18寸(450mm).2、物理尺寸、平整度、微粗糙度、氧含量、晶体缺陷、颗粒、体电阻率。

微电子工艺习题总结(DOC)

1. What is a wafer? What is a substrate? What is a die?什么是硅片,什么是衬底,什么是芯片答:硅片是指由单晶硅切成的薄片;芯片也称为管芯(单数和复数芯片或集成电路);硅圆片通常称为衬底。

2. List the three major trends associated with improvement in microchip fabrication technology, and give a short description of each trend.列出提高微芯片制造技术相关的三个重要趋势,简要描述每个趋势答:提高芯片性能:器件做得越小,在芯片上放置得越紧密,芯片的速度就会提高。

提高芯片可靠性:芯片可靠性致力于趋于芯片寿命的功能的能力。

为提高器件的可靠性,不间断地分析制造工艺。

降低芯片成本:半导体微芯片的价格一直持续下降。

3. What is the chip critical dimension (CD)? Why is this dimension important?什么是芯片的关键尺寸,这种尺寸为何重要答:芯片的关键尺寸(CD)是指硅片上的最小特征尺寸;因为我们将CD作为定义制造复杂性水平的标准,也就是如果你拥有在硅片某种CD的能力,那你就能加工其他所有特征尺寸,由于这些尺寸更大,因此更容易产生。

4. Describe scaling and its importance in chip design.描述按比例缩小以及在芯片设计中的重要性答:按比例缩小:芯片上的器件尺寸相应缩小是按比例进行的重要性:为了优电学性能,多有尺寸必须同时减小或按比例缩小。

5. What is Moore's law and what does it predict?什么是摩尔定律,它预测了什么答:摩尔定律:当价格不变时,集成电路上可容纳的晶体管数,月每隔18个月便会增加1倍,性能也将提升1倍。

微电子工艺_哈尔滨工业大学中国大学mooc课后章节答案期末考试题库2023年

微电子工艺_哈尔滨工业大学中国大学mooc课后章节答案期末考试题库2023年1.CZ法拉不出高阻单晶硅锭的主要原因是:答案:坩埚材料分解出的氧会进入硅锭;2.实际VPE工艺温度多在质量传递控制区,此时外延速率:答案:对温度不太敏感;3.关于硅的热氧化,下面哪种说法正确:答案:氧化反应是在Si/SiO2界面发生的;4.在D-G模型中假定稳定生长氧化层时,氧化剂的气相输运、固相扩散和化学反应三个流密度应:答案:相等;5.基于LSS理论,离子注入受到靶原子核与电子的阻止:答案:核阻止和电子阻止是独立的;6.多晶硅薄膜通常采取哪种方法制备:答案:LPCVD7.PVD与CVD比较,下列那种说法正确:答案:PVD薄膜与衬底的粘附性较差;8.外延用衬底硅片一般偏离准确晶向一个小角度,如(111)-Si偏离3º,下列那种说法正确?答案:这是为了得到原子层量级的台阶;这是为外延生长提供更多的结点位置;9.硅恒定源扩散,在扩散温度硅的固溶度为N s,在进行了40min扩散后,测得结深是1.5μm,若要获得2.0μm的结深,在原工艺基础上应再扩散多少分钟?硅表面杂质浓度是多少?答案:应再扩散31 min杂质表面浓度=N s表面杂质浓度等于该工艺温度时硅的固溶度;10.P在两歩扩散工艺中,第二步再分布的同时又进行了热氧化(kp=10),这会给再分布扩散带来哪些影响:答案:P扩散速度加快;在SiO2/Si界面Si一侧的P堆积(是指高于SiO2一侧);扩入Si的P总量下降;11.扩散系数是表征扩散快慢的参数,它相当于单位浓度梯度时的扩散通量,所以它:答案:单位为m∧2/s有单位;12.看图判断,下列哪种描述正确:答案:图(b)是注入的高能离子。

图(a)是注入的低能离子;13.下列哪个工艺方法应用了等离子体技术:答案:溅射RIEHDPCVD14.蒸镀工艺要求蒸镀室为高真空度的原因:答案:为了避免蒸发分子(或原子)被氧化;为了提高蒸发分子(或原子)的平均自由程;为了降低镀膜中的杂质;15.可以采取哪种方法来提高光刻分辨率?答案:减小分辨率系数;增大光学系统数值孔径;缩短光源波长;16.CZ法、MCZ法拉单晶时必须有籽晶;而FZ法拉单晶时不需要籽晶。

微电子工艺计算题答案

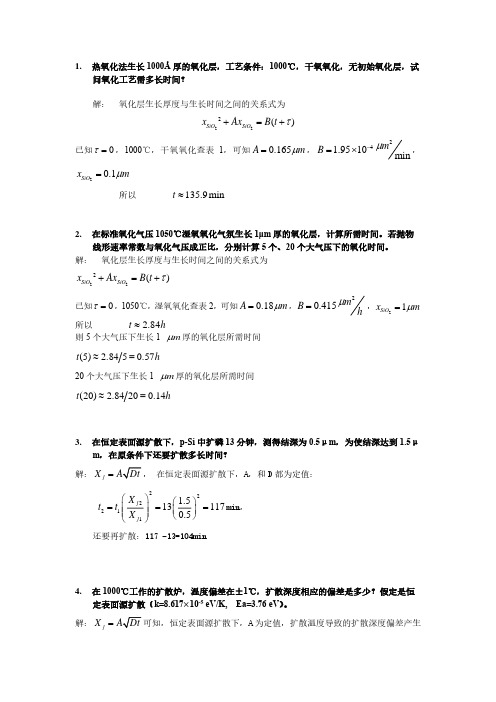

1. 热氧化法生长1000Å厚的氧化层,工艺条件:1000℃,干氧氧化,无初始氧化层,试问氧化工艺需多长时间?解: 氧化层生长厚度与生长时间之间的关系式为222()SiO SiO x Ax B t τ+=+已知0τ=,1000℃,干氧氧化查表1,可知0.165A m μ=,241.9510min m B μ−=⨯,20.1SiO x m μ=所以 135.9min t ≈2. 在标准氧化气压1050℃湿氧氧化气氛生长1μm 厚的氧化层,计算所需时间。

若抛物线形速率常数与氧化气压成正比,分别计算5个、20个大气压下的氧化时间。

解: 氧化层生长厚度与生长时间之间的关系式为222()SiO SiO x Ax B t τ+=+已知0τ=,1050℃,湿氧氧化查表2,可知0.18A m μ=,20.415m B h μ=,21SiO x m μ= 所以 2.84t h ≈则5个大气压下生长1 m μ厚的氧化层所需时间(5) 2.8450.57t h ≈=20个大气压下生长1 m μ厚的氧化层所需时间(20) 2.84200.14t h ≈=3. 在恒定表面源扩散下,p-Si 中扩磷13分钟,测得结深为0.5μm ,为使结深达到1.5μm ,在原条件下还要扩散多长时间?解:j X =, 在恒定表面源扩散下,A ,和D 都为定值: 222211 1.5131170.5j j X t t X ⎛⎫⎛⎫=== ⎪ ⎪ ⎪⎝⎭⎝⎭min , 还要再扩散:117 -13=104min4. 在1000℃工作的扩散炉,温度偏差在±1℃,扩散深度相应的偏差是多少?假定是恒定表面源扩散(k=8.617×10-5 eV/K, Ea=3.76 eV )。

解:j X =可知,恒定表面源扩散下,A 为定值,扩散温度导致的扩散深度偏差产生主要来源于扩散系数差由公式 0exp a E D D kT −⎡⎤=⎢⎥⎣⎦:10011000101.35%j j X X ===999100098.66%j j X X ===5. 30keV 、1012ions/cm 2 B 11注入Si 中,求注入的峰值深度和峰值浓度(查图时,R p 精确到0.1μm ,ΔR p 精确到0.01μm )。

微电子工艺考试(开卷)试题及答案

《微电子工艺》考试(开卷)1、简述三维集成技术的优、缺点,及其应用领域?(15 ')1)优:互联线更短、低功耗、速度高、所占平面面积小、引脚少2)缺:制造工艺复杂、成本高、不易散热3)应用:成像传感器、存储器、处理器2、简述BOSCI刻蚀工艺原理?(15 ')BOSCH刻蚀为时分复用刻蚀。

1)各自同性刻蚀, SF6 等离子体现各项同性刻蚀,刻蚀循环7-16s;2)保护:C4F8生成类似Teflen的氟碳化合物高分子膜(-CF2-) n保护循环5-15s;3)刻蚀温度:液氮冷却 40 C;4)电感耦合等离子: ICP 产生等离子体,平板电极加速离子;5)气体切换系统;6)刻蚀掩膜;7)侧壁;8)刻蚀速率。

3、简述光刻的主要工艺步骤,并配图说明?(15' )1)涂光刻胶2)对准与曝光3)显影4)刻蚀5)去除光刻胶4、简述常压CVD工艺在Si表面淀积SiO2膜时,与热氧化工艺的不同之处是?(15 ' )1)CVD法SiO2膜中的硅来自外加的反应气体,而热氧化法SiO2膜中的硅来自硅衬底本身,氧化过程中需消耗掉一部分衬底中的硅;2)CVD法德反应发生在 SiO2膜表面,膜厚与时间始终成线性关系。

而在热氧化法中,一旦SiO2膜形成后,反应剂必须穿过 SiO2膜,反应发生在 SiO2/Si界面上;3)CVD 法温度较低,但膜质量较差,通常需经增密处理,而热氧化法湿度高,SiO 结构致密,掩膜性能良好。

5、参考PMO晶体管的制造工艺流程,绘制NMOS!体管的制造工艺流程,并给予简要说明。

(30 ' )NMOS晶休管的工艺流程概介■:- StepO: _块卩型琏NMOS晶体管的工艺槪概介-"Stepl: (layering)生长一层厚二氧化硅(5000A),作为掺杂阻拦层,也叫场氧.NMOS晶体管的工艺勰概介△2& (patterning)涂•發.NMOS晶休管的工艺般概介。

微电子工艺习题参考解答

CRYSTAL GROWTH AND EXPITAXY1.画出一50cm 长的单晶硅锭距离籽晶10cm 、20cm 、30cm 、40cm 、45cm 时砷的掺杂分布。

(单晶硅锭从融体中拉出时,初始的掺杂浓度为1017cm -3) 2.硅的晶格常数为?.假设为一硬球模型: (a)计算硅原子的半径。

(b)确定硅原子的浓度为多少(单位为cm -3)(c)利用阿伏伽德罗(Avogadro)常数求出硅的密度。

3.假设有一l0kg 的纯硅融体,当硼掺杂的单晶硅锭生长到一半时,希望得到 Ω·cm 的电阻率,则需要加总量是多少的硼去掺杂4.一直径200mm 、厚1mm 的硅晶片,含有的硼均匀分布在替代位置上,求: (a)硼的浓度为多少(b)硼原子间的平均距离。

5.用于柴可拉斯基法的籽晶,通常先拉成一小直径的狭窄颈以作为无位错生长的开始。

如果硅的临界屈服强度为2×106g/cm2,试计算此籽晶可以支撑的200mm 直径单晶硅锭的最大长度。

6.在利用柴可拉斯基法所生长的晶体中掺入硼原子,为何在尾端的硼原子浓度会比籽晶端的浓度高7.为何晶片中心的杂质浓度会比晶片周围的大8.对柴可拉斯基技术,在k 0=时,画出C s /C 0值的曲线。

9.利用悬浮区熔工艺来提纯一含有镓且浓度为5×1016cm -3的单晶硅锭。

一次悬浮区熔通过,熔融带长度为2cm ,则在离多远处镓的浓度会低于5×1015cm -3 10.从式L kx s e k C C /0)1(1/---=,假设k e =,求在x/L=1和2时,C s /C 0的值。

11.如果用如右图所示的硅材料制造p +-n 突变结二极管,试求用传统的方法掺杂和用中子辐照硅的击穿电压改变的百分比。

12.由图,若C m =20%,在T b 时,还剩下多少比例的液体13.用图解释为何砷化镓液体总会变成含镓比较多14.空隙n s 的平衡浓度为Nexp[-E s /(kT)],N 为半导体原子的浓度,而E s 为形成能量。

微电子工艺原理和技术复习题

《微电子工艺原理和技术》复习题一、填空题1.半导体集成电路主要的衬底材料有单元晶体材料⎽Si⎽、⎽Ge⎽和化合物晶体材料⎽GaAs⎽、⎽InP⎽;硅COMS集成电路衬底单晶的晶向常选(100);TTL集成电路衬底材料的晶向常选(111);常用的硅集成电路介电薄膜是⎽SiO2⎽、⎽Si3N4;常用的IC互连线金属材料是⎽Al⎽⎽、⎽Cu⎽。

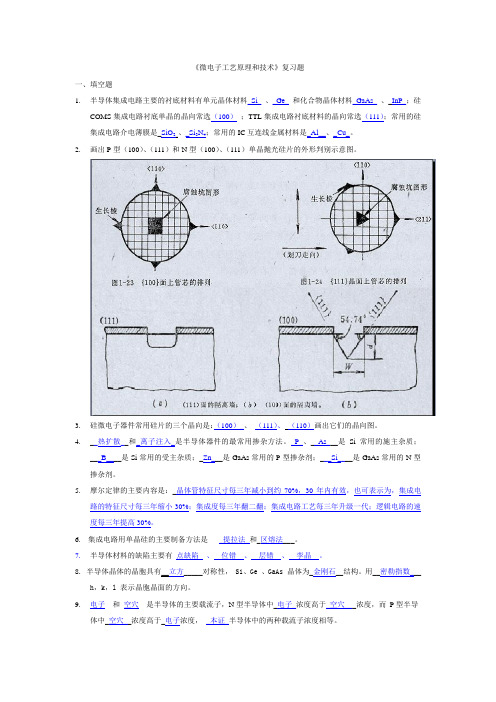

2.画出P型(100)、(111)和N型(100)、(111)单晶抛光硅片的外形判别示意图。

3.硅微电子器件常用硅片的三个晶向是:(100)⎽、(111)、(110)画出它们的晶向图。

4.⎽⎽热扩散⎽⎽和⎽离子注入⎽是半导体器件的最常用掺杂方法。

⎽P⎽、⎽⎽As⎽⎽⎽是Si常用的施主杂质;⎽⎽⎽B⎽⎽⎽⎽是Si常用的受主杂质;⎽Zn⎽⎽⎽是GaAs常用的P型掺杂剂;⎽⎽⎽Si⎽⎽⎽⎽是GaAs常用的N型掺杂剂。

5.摩尔定律的主要内容是:⎽晶体管特征尺寸每三年减小到约70%,30年内有效,也可表示为,集成电路的特征尺寸每三年缩小30%;集成度每三年翻二翻;集成电路工艺每三年升级一代;逻辑电路的速度每三年提高30%。

6. 集成电路用单晶硅的主要制备方法是⎽提拉法⎽和⎽区熔法⎽⎽⎽。

7.半导体材料的缺陷主要有点缺陷、位错、层错、孪晶。

8. 半导体晶体的晶胞具有⎽⎽立方⎽⎽⎽⎽⎽对称性, Si、Ge 、GaAs 晶体为⎽金刚石⎽⎽结构。

用⎽⎽密勒指数⎽⎽⎽h,k,l 表示晶胞晶面的方向。

9.电子和空穴是半导体的主要载流子,N型半导体中⎽电子⎽浓度高于⎽空穴⎽⎽⎽浓度,而P型半导体中⎽空穴⎽⎽浓度高于⎽电子浓度,⎽本证⎽半导体中的两种载流子浓度相等。

10. 半导体单晶材料中的电子能级由于价电子的共有化分裂成能带,价带是⎽0 K 条件下被 电子填充的能量最高的能带,导带是0 K 条件下未被电子填充的能量最低的能带 ,导 带底与价带顶之间称禁带。

施主能级靠近⎽导带底⎽⎽,受主能级靠近⎽价带顶⎽。

微电子工艺复习题目(精选)

微电子工艺复习题目(精选)第一单元3比较硅单晶锭CZ、MCZ和FZ三种生长方法的优缺点?答:CZ法工艺成熟可拉制大直径硅锭,但受坩锅熔融带来的O等杂质浓度高,存在一定杂质分布,因此,相对于MCZ和FZ法,生长的硅锭质量不高。

当前仍是生产大直径硅锭的主要方法。

MCZ法是在CZ技术基础上发展起来的,生长的单晶硅质量更好,能得到均匀、低氧的大直径硅锭。

但MCZ设备较CZ设备复杂得多,造价也高得多,强磁场的存在使得生产成本也大幅提高。

MCZ法在生产高品质大直径硅锭上已成为主要方法。

FZ法与CZ、MCZ法相比,去掉了坩埚,因此没有坩埚带来的污染,能拉制出更高纯度、无氧的高阻硅,是制备高纯度,高品质硅锭,及硅锭提存的方法。

但因存在熔融区因此拉制硅锭的直径受限。

FZ法硅锭的直径比CZ、MCZ法小得多。

6硅气相外延工艺采用的衬底不是准确的晶向,通常偏离(100)或(111)等晶向一个小角度,为什么?答:从硅气相外延工艺原理可知,硅外延生长的表面外延过程是外延剂在衬底表面被吸附后分解出Si原子,他迁移到达结点位置停留,之后被后续的Si原子覆盖,该Si原子成为外延层中原子。

因此衬底表面“结点位置”的存在是外延过程顺利进行的关键,如果外延衬底不是准确的(100)或(111)晶面,而是偏离一个小角度,这在其表面就会有大量结点位置,所以,硅气相外延工艺采用的衬底通常偏离准确的晶向一个小角度。

8异质外延对衬底和外延层有什么要求?对于B/A型的异质外延,在衬底A上能否外延生长B,外延层B 晶格能否完好,受衬底A与外延层B的兼容性影响。

衬底与外延层的兼容性主要表现在三个方面:其一,衬底A与外延层B两种材料在外延温度不发生化学反应,不发生大剂量的互溶现象。

即A和B的化学特性兼容;其二,衬底A与外延层B的热力学参数相匹配,这是指两种材料的热膨胀系数接近,以避免生长的外延层由生长温度冷却至室温时,因热膨胀产生残余应力,在B/A界面出现大量位错。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

微电子工艺原理习题

一、填空题

1.传统集成电路制造工艺的发展以的出现作为大致的分界线,现代集成电路制造工艺进入超大规模集成电路后又以工艺的作为划分标志。

2.能提供多余空穴的杂质称为,P型半导体中的多子是。

3.多晶硅转变成单晶硅的实质是。

4.单晶硅拉制过程中引晶阶段的温度选择非常重要,温度过高时会造成,温度过低时会形成。

5.SiO

2

网络中氧的存在有两种形式,其中原子浓度越高,网络的强度越强;原子浓度越高,网络的强度越弱。

6.目前常用的两种掺杂技术是和。

7.完整的光刻工艺应包括和两部分,随着集成电路生产在微细加工中的进一步细分,后者又可独立成为一个工序。

8.伴随刻蚀工艺实现的图形转换发生在和之间。

9.按照功能和用途进行分类,集成电路可以分为和两类。

10.能提供多余电子的杂质称为,N型半导体中的少子是。

11.固溶体分为替位式固溶体和间隙式固溶体,两类大部分施主和受主杂质都与硅形成

固溶体。

12.单晶硅的性能测试涉及到的测试、的测试和缺陷检验等多个方面。

13.SiO

2中掺入杂质的种类对SiO

2

网络强度的影响表现在:掺入Ⅲ族元素如硼时,网络强

度;掺入Ⅴ族元素如磷时,网络强度。

14.常用的芯片封装方法有、和陶瓷封装。

15.光刻胶又叫,常用的光刻胶分为和两类。

1.下列有关集成电路发展趋势的描述中,不正确的是。

(A)特征尺寸越来越小(B)晶圆尺寸越来越小

(C)电源电压越来越低(D)时钟频率越来越高

2.下面几种薄膜中,不属于半导体膜的是。

(A)SiO

2

膜(B)单晶硅膜(C)多晶硅膜(D)GaAs膜

3.下列有关芯片封装的描述中不正确是。

(A)金属封装热阻小有良好的散热性能(B)塑料封装机械性能差,导热能力弱(C)金属封装成本低,塑料封装成本高(D)陶瓷封装的气密性好,但脆性较高4.下列选项中属于光刻工艺三要素之一的是。

(A)曝光(B)光刻胶(C)显影(D)刻蚀

5.下列有关扩散的几种描述中不正确的是。

(A)扩散是一种掺杂技术。

(B)扩散有气态扩散、液态扩散和固态扩散三种。

(C)替位型杂质在硅中的扩散方式有替代扩散、空位扩散以及间隙扩散三种。

(D)替位型杂质的掺入不会改变材料的电学性质。

6.下列关于光刻胶的描述中正确的是。

(A)负胶具有较高的固有分辨率(B)正胶成本低,适合大批量生产(C)正胶的分辨率高,抗干法腐蚀能力强(D)负胶粘附性差,抗湿法腐蚀能力弱7.硅片中同时有浅施主和浅受主时,导电类型和载流子浓度由决定。

(A)杂质浓度差(B)施主杂质(C)受主杂质(D)杂质浓度和

8.下面几种材料的薄膜中,不属于介质膜的是。

(A)SiO

2膜(B)Si

3

N

4

膜(C)多晶硅膜(D)Al

2

O

3

膜

9.下列因素中对扩散系数大小不会造成影响的是。

(A)温度(B)杂质种类(C)扩散环境(D)杂质浓度变化率10.关于干法刻蚀的正确描述是。

(A)化学性刻蚀选择比高且是各向异性刻蚀;

(B)反应离子刻蚀(RIE)兼具各向异性与高选择比等优点;

(C)化学性刻蚀方向性好,可获得接近垂直的刻蚀侧墙;

(D)物理性刻蚀的选择性好。

1. 微电子学,即微型电子学,其核心是集成电路。

( )

2.按功能分类,集成电路可以分为双极型、MOS 型和BiMOS 型。

( )

3.硅片中同时有浅施主和浅受主时,导电类型和载流子浓度数量由杂质浓度差决定。

( )

4.施主杂质的溶解度,将随晶体中的受主杂质含量的增加而增大。

( )

5.在半导体生产中SiO 2膜作为杂质选择性扩散的掩蔽膜适用于任何杂质。

( )

6.方块电阻反映了单位面积扩散进去的杂质的总量,扩散的杂质越多,方块电阻越大。

所以可以通过测方块电阻来检测扩散进去的单位面积的杂质量。

( )

7.插塞是用来连接上下两层金属的导电材料,常用插塞为钨插塞。

( )

8.旋涂玻璃法平坦化工艺可实现全局平坦化,化学机械抛光可实现局部平坦化。

( )

9.被曝光的部分由可溶性物质变成了非溶性物质的光刻胶称为正胶。

( )

10.光敏度由曝光效率决定,正胶比负胶有更高的曝光效率,故正胶的光敏度大。

( )

11. 特征尺寸越来越大是集成电路的发展趋势之一。

( )

12.杂质在硅中的溶解度是集成电路制造过程中选择杂质的重要依据。

( )

13.在单晶硅的两种拉制方法中,悬浮区熔法较直拉法更易拉制大直径单晶硅。

( )

14.SiO 2网络中氧的存在有两种形式(桥联氧和非桥联氧),其中桥联氧原子浓度越高,网

络的强度越强。

( )

15.菲克扩散定律x N D J ∂∂-=中的负号表示扩散方向与杂质浓度的增加方向相反。

( )

16.光刻胶的对比度会直接影响到曝光后光刻胶膜的倾角和线宽。

( )

17.刻蚀工艺实现的图形转换发生在掩膜版和光刻胶层之间。

( )

18.受主杂质的溶解度,将随晶体中的施主杂质含量的增加而增大。

( )

19.被曝光的部分由可溶性物质变成了非溶性物质的光刻胶称为负胶。

( )

20. 磨料、抛光垫、抛光压力和选择比是影响CMP 抛光质量的重要因素。

( )

四、简答题

1.目前由多晶硅制备单晶硅的主要方法有哪两种,两种方法各有什么特点?

2.简述半导体生产中常用薄膜的种类及用途。

薄膜的制备方法分哪两类?并举例说明两类制备方法各自的特点。

3.双极型集成电路制造中常用的隔离技术有哪些?说明各自的优缺点。

4.什么是小岛?简述小岛产生的原因。

5.简述由多晶硅制备单晶硅的三个具体条件;目前由多晶硅制备单晶硅的主要方法有哪两种,两种方法各有什么特点?

6.薄膜的制备方法分哪两类?并举例说明两类制备方法各自的特点。

7.什么是溶胶?简述溶胶产生的原因。

8. 什么是键合?键合的具体方法有哪些?键合质量的检查涉及哪几项内容?。