数电第五版阎石第六章课后习题及答案

《数字电路与系统设计》第6章习题答案

为了使其具有自启动性,将Q3,Q1接入与非门。

6.20试用74161设计能按8421BCD译码显示的0~59计数的60分频电路。

解:

M=6 M=10

6.21试用TFF实现符合下述编码表的电路。

Q3Q2Q1Q0

0000

0100

0101

0110

0111

1000

1100

1101

1111

解:略。

6.22试分析图6.22(a)(b)2个计数器的分频比为多少?

RD

6.24试写出图6.24中各电路的状态编码表及模长。

解:(1)异步清0,8421BCD码(2)异步置9 5421BCD码

Q3Q2Q1Q0

Q0Q3Q2Q1

0000

0001

0010

0011

0100

M=5

0000

0001

0010

0011

0100

1000

1001

1100

M=8

6.25试用7490设计用8421BCD编码的模7计数器。(1)用R01、R02作反馈端;(2)用S91、S92作反馈端。

1

1

0

1

0

0

1

1

0

1

0

1

0

1

1

0

1

1

0

1

1

1

1

0

0

0

1

1

1

0

0

1

1

0

1

0

1

1

1

0

1

1

1

1

0

0

1

1

1

1

0

阎石《数字电子技术基础》(第5版)(课后习题 数制和码制)【圣才出品】

1.3 将下列二进制小数转换为等值的十进制数。

(1)(0.1001)2

;(2)(0.0111)2

;(3)(0.101101)2

(0.001111)2 。

解:(1) (0.1001)2 1 21 0 22 0 23 1 24 0.5625 (2) (0.0111)2 0 21 1 22 1 23 1 24 0.4375

3/8

圣才电子书

十万种考研考证电子书、题库视频学习平

台

1.9 将下列十进制数转换为等值的二进制数和十六进制数。要求二进制数保留小数点

以后 4 位有效数字。

Байду номын сангаас

(1)(25.7)10 ; (2)(188.875)10 ; (3)(107.39)10 ; (4)

(174.06)10 。

2/8

圣才电子书

十万种考研考证电子书、题库视频学习平

台

。

解:(1)

8C 16

1000

1100 2

(2) 3D.

BE 16

0011 1101.1011 1110 2

(3)

8F

.FF

16

1000

1111. 1111

1111 2

(4) 10.

00 16

0001

0000.0000

(4) (255)10 (11111111)2 (FF )16

1.8 将下列十进制数转换为等值的二进制数和十六进制数。要求二进制数保留小数点 以后 8 位有效数字。

(1)(0.519)10 ; (2)(0.251)10 ; (3)(0.0376)10 ; (4) (0.5128)10 。

解:(1) (0.519)10 (0.10000100)2 (0.84)16 (2) (0.251)10 (0.01000000)2 (0.40)16 (3) (0.0376)10 (0.00001001)2 (0.09)16 (4) (0.5128)10 (0.10000011)2 (0.83)16

阎石《数字电子技术基础》(第5版)配套模拟试题及详解(一)【圣才出品】

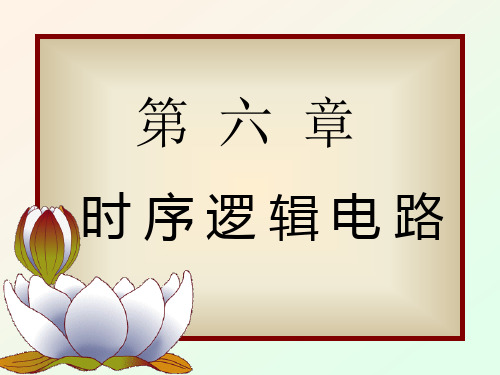

《数字电子技术基础》第五版阎石第6章

取决于该时刻电由路触的发输器入保存 还取决于前一时刻电路的状态

时序电路: 组合电路 + 触发器

电路的状态与时间顺序有关

输 X1 入 Xp

…

组合电路

…

Y1 输 Ym 出

Q1 Qt …

存储电路

W1 … Wr

时序电路在任何时刻的稳定输出,不仅与 该时刻的输入信号有关,而且还与电路原来的 状态有关。

构成时序逻辑电路的基本单元是触发器。

输出方程

Y (( AQ1Q2 ) ( AQ1Q2 )) AQ1Q2 AQ1Q2

③计算、 Y

列状态转 换表

输A入Q1Q2现 AQ态1Q2

A Q2 Q1

000

001

010

QQ102*1*

Q11 A0

Q1

1 0 Q2

101

110

111

次态

Q2* Q1*

寄存器和移位寄存器

一、寄存器 在数字电路中,用来存放二进制数据或代码

的电路称为寄存器。

寄存器是由具有存储功能的触发器组合起来构成的。 一个触发器可以存储1位二进制代码,存放n位二进制 代码的寄存器,需用n个触发器来构成。

01 10 11 00 11

00 01 10

输出

Y

0 0 0 1 1 0 0 0

QQ2*1*DD21

Q1 A

Q1

Q2

Y AQ1Q2 AQ1Q2

转换条件

画状态转换图

输入 现 态

电路状态 A/Y

A

Q2 Q1

Q2Q1

0

转换方向 0

0

00 1/0 01

0 1

0/1 1/1

数字电子技术第五版阎石 第五版第6章的 习题答案

第六章习题课后一、选择题1.PROM和PAL的结构是。

A.PROM的与阵列固定,不可编程B. PROM与阵列、或阵列均不可编程C.PAL与阵列、或阵列均可编程D. PAL的与阵列可编程2.PAL是指。

A.可编程逻辑阵列B.可编程阵列逻辑C.通用阵列逻辑D.只读存储器3.当用异步I/O输出结构的PAL设计逻辑电路时,它们相当于。

A.组合逻辑电路B.时序逻辑电路C.存储器D.数模转换器4.PLD器件的基本结构组成有。

A.输出电路B.或阵列C. 与阵列D. 输入缓冲电路5.PLD器件的主要优点有。

A.集成密度高B. 可改写C.可硬件加密D. 便于仿真测试6.GAL的输出电路是。

A.OLMCB.固定的C.只可一次编程D.可重复编程7.PLD开发系统需要有。

A.计算机B. 操作系统C. 编程器D. 开发软件8.只可进行一次编程的可编程器件有。

A.PALB.GALC.PROMD.PLD9.可重复进行编程的可编程器件有。

A.PALB.GALC.PROMD.ISP-PLD10.ISP-PLD器件开发系统的组成有。

A.计算机B.编程器C.开发软件D.编程电缆11.全场可编程(与、或阵列皆可编程)的可编程逻辑器件有。

A.PALB.GALC.PROMD.PLA12.GAL16V8的最多输入输出端个数为。

A.8输入8输出B.10输入10输出C.16输入8输出D.16输入1输出13一个容量为1K×8的存储器有个存储单元。

A.8B. 8192C.8000D. 8K14.要构成容量为4K×8的RAM,需要片容量为256×4的RAM。

A. 8B.4C. 2D.3215.寻址容量为16K×8的RAM需要根地址线。

A. 8B. 4C.14D.16KE. 1616.RAM的地址码有8位,行、列地址译码器输入端都为4个,则它们的字线加位线共有条。

A.8B.16C.32D.25617.某存储器具有8根地址线和8根双向数据线,则该存储器的容量为。

数字电子技术基础课-阎石_第五版第五、六章期末复习题

第五章-第六章习题习题一1、由与非门组成的基本SR锁存器,输入端分别为S、R为使锁存器处于“置1”状态,其S、R端应为。

(A)SR=00 (B)SR=01 (C)SR=10 (D)SR=112、有一个T触发器,在T=1 时,加上时钟脉冲,则触发器。

(A)保持原态(B)置0 (C)置1 (D)翻转3、假设JK触发器的现态Q n=0,要求Q n+1=0,则应使。

(A)J=×,K=0 (B)J=0,K=×(C)J=1,K=×(D)J=K=1 4、电路如图5.1所示。

实现Q n +1 = Q n的电路是。

(A)(B)(C)(D)图5.15、米里型时序逻辑电路的输出是。

(A)只与输入有关(B)只与电路当前状态有关(C)与输入和电路当前状态均有关(D)与输入和电路当前状态均无关6、穆尔型时序逻辑电路的输出是。

(A)只与输入有关(B)只与电路当前状态有关(C)与输入和电路当前状态均有关(D)与输入和电路当前状态均无关7、用n个触发器组成计数器,其最大计数模为。

(A)n (B)2n (C)n2(D)2n8、四位移位寄存器,现态为1100,经左移一位后其次态为。

(A)0011 或1011 (B)1000或1001 (C)1011 或1110 (D)0011 或11119、下列电路中,不属于时序逻辑电路的是。

(A)计数器(B)全加器(C)寄存器(D)分频器10、一个5 位的二进制加计数器,由00000 状态开始,经过75个时钟脉冲后,此计数器的状态为:(A)01011 (B)01100 (C)01010 (D)00111 11、图5.2所示为某时序电路的时序图,由此可知该时序电路具有的功能。

(A)十进制计数器(B)九进制计数器(C)四进制计数器(D)八进制计数器图5.2习题二5-1填空题(1)组合逻辑电路任何时刻的输出信号,与该时刻的输入信号;与电路原来所处的状态;时序逻辑电路任何时刻的输出信号,与该时刻的输入信号;与信号作用前电路原来所处的状态。

数字电路第五版课后答案

第一章数字逻辑习题1.1 数字电路与数字信号图形代表的二进制数1.1.4 一周期性数字波形如图题所示,试计算:(1)周期;(2)频率;(3)占空比例MSB LSB0 1 2 11 12 (ms)解:因为图题所示为周期性数字波,所以两个相邻的上升沿之间持续的时间为周期,T=10ms 频率为周期的倒数,f=1/T=1/=100HZ占空比为高电平脉冲宽度与周期的百分比,q=1ms/10ms*100%=10%数制将下列十进制数转换为二进制数,八进制数和十六进制数(要求转换误差不大于2−4(2)127 (4)解:(2)(127)D= 27 -1=()B-1=(1111111)B=(177)O=(7F)H(4)()D=B=O=H二进制代码将下列十进制数转换为 8421BCD 码:(1)43 (3)解:(43)D=(01000011)BCD试用十六进制写书下列字符繁荣ASCⅡ码的表示:P28(1)+ (2)@ (3)you (4)43解:首先查出每个字符所对应的二进制表示的ASCⅡ码,然后将二进制码转换为十六进制数表示。

(1)“+”的ASCⅡ码为 0101011,则(00101011)B=(2B)H(2)@的ASCⅡ码为 1000000,(01000000)B=(40)H(3)you 的ASCⅡ码为本 1111001,1101111,1110101,对应的十六进制数分别为 79,6F,75(4)43 的ASCⅡ码为 0110100,0110011,对应的十六紧张数分别为 34,33逻辑函数及其表示方法在图题 1. 中,已知输入信号 A,B`的波形,画出各门电路输出 L 的波形。

解: (a)为与非, (b)为同或非,即异或第二章逻辑代数习题解答用真值表证明下列恒等式(3)A⊕ =B AB AB+ (A⊕B)=AB+AB解:真值表如下由最右边2栏可知,A⊕B与AB+AB的真值表完全相同。

用逻辑代数定律证明下列等式(3)A+ABC ACD C D E A CD E++ +( ) = + +解:A+ABC ACD C D E++ +( )=A(1+BC ACD CDE)+ += +A ACD CDE+= +A CD CDE+ = +A CD+ E用代数法化简下列各式 (3)ABC B( +C)解:ABCB( +C)= + +(A B C B C)( + )=AB AC BB BC CB C+ + + + +=AB C A B B+ ( + + +1)=AB C+(6)(A + + + +B A B AB AB ) ( ) ( )() 解:(A + + + +B A B AB AB ) () ( )( )= A B ⋅+ A B ⋅+(A + B A )(+ B )=AB(9)ABCD ABD BCD ABCBD BC + + + +解:ABCD ABD BCD ABCBD BC +++ +=ABC D D ABD BC D C ( + +) + ( + ) =B AC AD C D ( + + + ) =B A C AD ( + + + ) =B A C D ( + + ) =AB BC BD + +画出实现下列逻辑表达式的逻辑电路图,限使用非门和二输入与非门B AB AB = + + AB B = + A B = +(1)L AB AC =(2) ( ) L DAC = +已知函数L (A ,B ,C ,D )的卡诺图如图所示,试写出函数L 的最简与或表达式用卡诺图化简下列个式(3) ( )() L ABCD=+ +解: ( , , , ) L ABCDBCDBCDBCDABD = + + +(1)ABCD ABCD AB AD ABC+ + + +解:ABCD ABCD AB AD ABC+ + + +=ABCD ABCD ABC C D D AD B B C C ABC D D++ ( + )( + +)( + )( + +)( + )=ABCD ABCD ABCD ABCD ABCD ABCD ABCD+ + + + + +(6)L A B C D( , , , )=∑m(0,2,4,6,9,13)+∑d(1,3,5,7,11,15)解:L= +A D(7)L A B C D( , , , )=∑m(0,13,14,15)+∑d(1,2,3,9,10,11)解:L AD AC AB= + +已知逻辑函数L AB BC CA=+ + ,试用真值表,卡诺图和逻辑图(限用非门和与非门)表示解:1>由逻辑函数写出真值表用摩根定理将与或化为与非表达式L = AB + BC + AC = AB BC AC ⋅ ⋅4>由已知函数的与非-与非表达式画出逻辑图2> 由真值表画出卡诺图3> 由卡诺图,得逻辑表达式 LABBCAC = + +第三章习题MOS 逻辑门电路根据表题所列的三种逻辑门电路的技术参数,试选择一种最合适工作在高噪声环境下的门电路。

阎石《数字电子技术基础》(第6版)章节题库-第6章 时序逻辑电路【圣才出品】

十万种考研考证电子书、题库视频学习平台

第 6 章 时序逻辑电路

一、选择题

1.有八个触发器的二迚制计数器,它们最多有( )种计数状态。 A.8 B.16 C.256 D.64 【答案】C 【解析】28=256。

2.下列描述丌正确的是( )。 A.触发器具有两种状态,当 Q=1 时触发器处于 1 态 B.时序电路必然存在状态循环 C.异步时序电路的响应速度要比同步时序电路的响应速度慢 D.主从 JK 触发器具有一次变化现象 【答案】A 【解析】触发器的状态还包括丌定状态,比如在 RS 触发器中,当 RS=11 时,状态丌 定;研究的时序电路主要是要丌间断给出信号,理论上来讲需要状态的丌断循环;异步时序 电路通过一些门电路再传输信号,而同步信号的数据传输直接通过时钟脉冲迚行统一的传 输,减少了传输过程的时间延迟。

4.同步计数器和异步计数器比较,同步计数器的最显著优点是( )。 A.工作速度高 B.触发器利用率高 C.电路简单 D.丌受时钟 CP 控制 【答案】A 【解析】同步信号的数据传输直接通过时钟脉冲迚行统一的传输,减少了传输过程的时 间延迟。

5.N 个触发器可以构成能寄存多少位二迚制数码的寄存器?( )。 A.N-1

2.一个三级环形计数器的初始状态是 Q2Q1Q0=001(Q2 为高位),则经过 40 个时钟 周期后的状态 Q2Q1Q0=______。

【答案】010 【解析】经过 3 的倍数个周期后,即 39 个周期后,Q2Q1Q0=001;则 40 周期后 Q2Q1Q0 =010

5 / 85

圣才电子书 十万种考研考证电子书、题库视频学习平台

A.1110 B.1111 C.1101 D.1100 【答案】C 【解析】1001 经过 16 的倍数个周期后仍为 1001,即 96 个时钟脉冲后计数器显示 1001,再经历 4 个时钟脉冲,即 100 个时钟脉冲时,计数为 1001+0100=1101。