爱普生(EPSON)实时时钟模块RA4803SA规格书

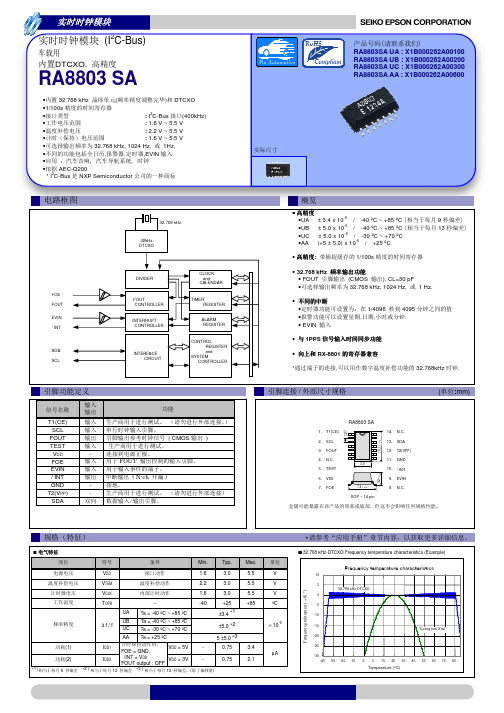

爱普生(EPSON)实时时钟模块RA8803SA规格书

DTCXO,

RA8803 SA

• 32.768 kHz

(

) DTCXO

•1/100s •

: I2C-Bus (400kHz)

•

: 1.6 V ~ 5.5 V

•

: 2.2 V ~ 5.5 V

•

: 1.6 V ~ 5.5 V

•

32.768 kHz, 1024 Hz, 1Hz.

•

,

,

,EVIN

FOE FOUT EVIN / INT

SDA SCL

32.768 kHz

32kHz DTCXO

DIVIDER

FOUT CONTROLLER

INTERRUPT CONTROLLER

INTERFACE CIRCUIT

CLOCK and

CALENDAR

TIMER REGISTER

ALARM REGISTER

5 32.768 kHz DTCXO

0

-5

-10

-15 Tuning fork X'tal

-20

-25

-30 -45 -35 -25 -15 -5 5 15 25 35 45 55 65 75 85 Temperature (ºC)

推进环境管理体系 符合国际标准

在环境管理体系的运行方面,使用 ISO14001 国际环境标准,通过“计 划-实施-检查-验证(PDCA)的循环来实现持续改进。公司位于日本和 海外的主要制造基地已取得了 ISO14001 资格认证。

CONTROL REGISTER and

SYSTEM CONTROLLER

T1(CE)

SCL

FOUT

TEST

爱普生 EPSON 表晶谐振器 FC-135 32.768000kHz 规格参数、数据手册、规格书信息

Contact us

3 Page

Surface.

+260ºC +220ºC

35s 100s

t(time)

Notice

· This material is subject to change without notice. · Any part of this material may not be reproduced or duplicated in any form or any means without the written

T_use

Level of drive

DL

Frequency tolerancature

Ti

Parabolic coefficient

B

Load capacitance

CL

Motional resistance (ESR)

R1

Motional capacitance

180.00 mm

Hφ 3

φ 160mm φ 76mm

±1 15.40 mm

± 0.3 13.00 mm

φ 60.00 mm

Unit: mm

+0.3 -0 2.00 mm φ 21±0.8 φ 13±0.2

2 Page

Reflow profile

Pre Heating Temperature Tp1 ~ Tp2 = + 170 °C

Heating Temperature TMlt = + 220 °C

RX-8025T时钟芯片应用手册 EPSON

2. Block Diagram ........................................................................................................1

3. Terminal description .............................................................................................2

ETM25E-01ç ç ç ç ç ç ç ç

Application Manual

Real Time Clock Module

RX-8025T

ççççççççççççççççç

授权代理商

领先的片式无源器件整合供应商

【领先的片式无源器件整合供应商—南京南山半导体有限公司】

3.1. Terminal connections ........................................................................................................ 2 3.2. Pin Functions....................................................................................................................... 2

Seiko Epson RTC-4543SA SB实时时钟模块应用手册说明书

ETM09E-03Real Time Clock ModuleRTC-4543SA/SB•These products are intended for general use in electronic equipment. When using them in specific applications that require extremelyobtain permission from Seiko Epson in advance./ Space equipment (artificial satellites, rockets, etc.) / Transportation vehicles and related(automobiles, aircraft,Submarine transmitters / Power stations and related / Fire work equipment and securityequipment / traffic control equipment / and others requiring equivalent reliability.•All brands or product names mentioned herein are trademarks and/or registered trademarks of their respective.CONTENTS1. OVERVIEW (1)2. BLOCK DIAGRAM (1)3. PIN CONNECTIONS (2)4. PIN FUNCTIONS (2)5. ELECTRICAL CHARACTERISTICS (3)5-1.A BSOLUTE M AXIMUM R ATINGS (3)5-2.O PERATING C ONDITION (3)5-3.F REQUENCY C HARACTERISTICS (3)5-4.DC C HARACTERISTICS (3)5-5.AC C HARACTERISTICS (4)5-6.T IMING C HARTS (5)6. TIMER DATA ORGANIZATION (6)7. DESCRIPTION OF OPERATION (7)7-1.D ATA READS (7)7-2.D ATA WRITES (7)7-3.D ATA WRITES (D IVIDER R ESET) (8)7-4.FOUT OUTPUT AND 1H Z CARRIES (8)8. EXAMPLES OF EXTERNAL CIRCUITS (9)9. EXTERNAL DIMENSIONS (10)10. LAYOUT OF PACKAGE MARKINGS (10)11. REFERENCE DATA (11)12. APPLICATION NOTES (12)32-kHz Output Serial RTC ModuleRTC - 4543 SA/SBBuilt-in crystal permits operation without requiring adjustmentBuilt-in time counters (seconds, minutes, hours) and calendar counters (days, days of the week months, years)Operating voltage range: 2.5 V to 5.5 VSupply voltage detection voltage: 1.7 ±0.3 VLow current consumption: 1.0 µA/2.0 V (Max.)Automatic processing for leap yearsOutput selectable between 32.768 kHz/1 Hz1. OverviewThis module is a real-time clock with a serial interface and a built-in crystal oscillator. This module is also equipped with clock and calendar circuits, an automatic leap year compensation function, and a supply voltage detection function.In addition, this module has a 32.768 kHz/1 Hz selectable output function for hardware control that is independent of the RTC circuit.This module is available in a compact SOP 14-pin package (RTC-4543SA) and a thin SOP 18-pin package (RTC-4543SB).4. Pin FunctionsSignalPin No.SOP-14pin(SOP-18pin)I/O FunctionGND1( 9 )Connects to negative (-) side (ground) of the power supply.CE3( 8 )InputChip enable input pin.When high,the chip is enabled. When low,the DATA pin goes tohigh impedance and the CLK,DATA,and WR pins are not able toaccept input.In addition, when low,the TM bit is cleared.FSEL4( 7 )InputSerect the frequency that is output from the FOUT pin.High : 1 HzLow : 32.768 kHzWR5( 6 )InputDATA pin input/output switching pin.High : DATA input (when writing the RTC)Low : DATA output (when reading the RTC)FOE6( 5 )InputWhen high, the frequency selected by the FSEL pin is output fromthe FOUT pin.When low, the FOUT pin goes to high impedance.V DD9( 14 )Connects to positive (+) side of the power supply.CLK10( 12 )InputSerial clock input pin.Data is gotten at the rising edge during a write, and data is outputat the rising edge during a read.DATA11( 11 )Bi-directional Input/outout pin that is used for writing and reading data.FOUT14( 10 )OutputOutputs the frequency selected by the FSEL pin. 1 Hz output issynchronized with the internal one-second signal.This output is not affected by the CE pin.N.C.2,7,8,12,13( 1,2,3,4,13,15,16,17,18 )Although these pins are not connected internally,they shouldalways be left open in order to obtain the most stable oscillationpossible.* Always connect a passthrough capacitor of at least 0.1 µF as close as possible between V DD and GND.5. Electrical Characteristics5-1. Absolute Maximum RatingsItem Symbol Conditions Min. Max. Unit Supply voltage V DD-0.3 7.0 VInput voltage V I Ta=+25 °C GND-0.3 V DD+0.3 VOutput voltage V O GND-0.3 V DD+0.3 V Storage temperature T STG- -55 +125 °C5-2. Operating ConditionItem Symbol Conditions Min. Max. Unit Operating supplyV DD- 2.5 5.5 V voltageData holding voltage V CLK- 1.4 5.5 VOperating temperature T OPR No condensation-40 +85 °C5-3. Frequency CharacteristicsItem Symbol Conditions Max. Unit Frequency tolerance ∆f/f O Ta=+25 °C , V DD=5.0 V 5 ± 23 * ×10-6Frequency temperatureT op-10to+70 °C +25 °C ref + 10 / - 120 ×10-6 characteristicsFrequency voltagef/V Ta=+25 °C , V DD=2.0 to 5.5 V ± 2 ×10-6/V characteristicsOscillation start time t STA Ta=+25 °C , V DD=2.5 V 3 s Aging fa Ta=+25 °C , V DD=5 V , first year ± 5 ×10-6 * Monthly deviation: Approx. 1 min.5-4. DC CharacteristicsUnless specified otherwise: V DD = 5 V ± 10 %, Ta = - 40 to +85 °C Item Symbol Conditions Min. Typ. Max. Unit Current consumption(1) I DD1 V DD=5.0 V CE=L , FOE=L 1.5 3.0 µA Current consumption(2) I DD2 V DD=3.0 V FSEL=H 1.0 2.0 µA Current consumption(3) I DD3 V DD=2.0 V 0.5 1.0 µA Current consumption(4) I DD4 V DD=5.0 V CE=L , FOE=H 4.0 10.0 µA Current consumption(5) I DD5 V DD=3.0 V FSEL=L 2.5 6.5 µA Current consumption(6) I DD6 V DD=2.0 V No load on the1.5 4.0 µAFOUT pinInput voltage V IH WR,DATA,CE,CLK, 0.8 V DD VV IL FOE,FSEL pins 0.2 V DD V0.5 µAInput off/leak current I OFF WR,CE,CLK,FOE,FSEL pinsV IN = V DD or GNDV OH(1)V DD=5.0 V I OH=-1.0 mA 4.5 V Output voltage V OH(2)V DD=3.0 V DATA , FOUT pins 2.0 VV OL(1)V DD=5.0 V I OL= 1.0 mA 0.5 VV OL(2)V DD=3.0 V DATA , FOUT pins0.8 VOutput load conditionN / CL FOUT pin 2 LSTTL / 30 pF Max.( fanout )Output leak current I OZH V OUT=5.5 V DATA , FOUT pins-1.0 1.0 µAI OZL V OUT=0 V DATA , FOUT pins-1.0 1.0 µASupply voltage detectionV DT- 1.4 1.7 2.0 V voltage5-5. AC CharacteristicsUnless specified otherwise: Ta = - 40 to +85 °C, CL = 50 pF Item Symbol V DD=5 V ± 10 % V DD=3 V ± 10 % UnitMin. Max. Min. Max.CLK clock cycle t CLK0.75 7800 1.5 7800 µsCLK low pulse width t CLKL0.375 3900 0.75 3900 µsCLK high pulse width t CLKH0.375 3900 0.75 3900 µs CLK setup time t CLKS25 50 nsCE setup time t CES0.375 3900 0.75 3900 µsCE hold time t CEH0.375 0.75 µsCE enable time t CE0.9 0.9 s Write data setup time t SD0.1 0.2 µsWrite data hold time t HD0.1 0.1 µs WR setup time t WRS100 100 nsWR hold time t WRH100 100 ns DATA output delay time t DATD0.2 0.4 µsDATA output floating time t DZ0.1 0.2 µs Clock input rise time t r150 100 nsClock input fall time t f150 100 ns FOUT rise time (CL=30 pF) t r2100 200 ns FOUT fall time (CL=30 pF) t f2100 200 ns Disable time (CL=30 pF) t XZ100 200 nsEnable time (CL=30 pF) t ZX100 200 nsFOUT duty ratio (CL=30 pF) Duty 40 60 40 60 % Wait time t RCV0.95 1.9 µs5-6. Timing Charts[]Duty t t100%H=×( 4 ) Disable/enable6. Timer Data Organization• The counter data is BCD code.• Writes and reads are both performed on an LSB-first basis.MSBLSBSecond ( 0 to 59 )FDTs40s20s10s8s4s2s1Minutes ( 0 to 59 ) * mi40mi20mi10mi8mi4mi2mi1Hour ( 0 to 23 ) * *h20h10h8h4h2h1Day of the week( 1 to 7 )*w4w2w1Day ( 1 to 31 ) * *d20d10d8d4d2d1Month ( 1 to 12 ) TM **mo10mo8mo4mo2mo1Year ( 0 to 99 )y80y40y20y10y8y4y2y1• Calendar counter. From 1 Jan 2001 to 31 Dec 2099, it is updated by an automatic calendar function.If a year is 4 multiples, it is a leap year, then date is updatedin order to 28 Feb, 29 Feb, Mar 1.Because there is the case that a leap year does not match when using data of year of except the Christian era, please be careful.Data of a day of the week run in cycles with 7 from 1.A recommended example are 1=Sun, 2=Mon,,,6=Fri, 7=Sat.• Clock counter. Only 24 hours system is supported. • ∗bits. These bits are used as memory.• TM bit. This is a test bit for shipping test. Always clear this bit to “0”.• FDT bit: Supply voltage detection bit• This bit is set to “1” when voltage of 1.7 ±0.3 V or less is detected between V DD and GND. • The FDT bit is cleared if all of the digits up to the year digits are read.• Although this bit can be both read and written, clear this bit to "0" in case of the write cycle.if the supply voltage is lower than the detection voltage value, the FDT bit is set to “1”.7. Description of Operation2) At the first rising edge of the CLK signal, the clock and calendar data are loaded into the shiftregister and the LSB of the seconds digits is output from the DATA pin.3) The remaining seconds, minutes, hour, day of the week, day, month, and year data is shifted out,in sequence and in synchronization with the rising edge of the CLK signal, so that the data isoutput from the DATA pin.The output data is valid until the rising edge of the 52nd clock pulse; even if more than 52 clockpulses are input,the output data does not change.4) If data is required in less than 52 clock pulses, that part of the data can be gotten by setting theCE pin low after the necessary number of clock pulses have been output.Example: If only the data from “seconds” to “day of the week” is needed:After 28 clock pulses, set the CE pin low in order to get the data from “seconds” to “day ofthe week.”5) When performing successive data read operations, a wait (tRCV) is necessary after the CE pinis set low.6) Note that if an update operation (a one-second carry) occurs during a data read operation,the data that is read will have an error of -1 second.7) Complete data read operations within tCE (Max.) = 0.9 seconds, as described earlier.1) RTC 4543 shifts to data input state by condition of WR terminal ="H",CE terminal ="H".2) Writing-data synchronize to a rising edge of CLK, and it inputs into an RTC from LSB of sec.3) Inside counter less than second is reset between falling edges of first CLK from a rising edge of next CLK.And update of Clock register is prohibited by the first falling edge of CLK.4) In writing of data to RTC, all 52 clock is necessary.When CE goes to LOW before the 52 bits transmission is completed, there is the possibilitythat * ,FDT and a year digit were destroyed.If a serial communication break occurs, do verify 8 bits of* bit andFDTbit and year data.5) In a rising edge of 52 clock, all data is written to RTC. Data after 53 bits is ignored.6) When CE goes to LOW, RTC re-starts update.Please finish write access within 0.9 second = tCE (Max.).7) Between write access and read access, recovery timing(tRCV) is necessary.Please do not set the time and date which is non-existence.7-3. Data writes (Divider Reset)After the counter is reset, carries to the seconds digit are halted.After the data write operation,the prohibition on carries to the seconds counter is lifted by setting the CE pin low.Complete data write operations within tCE (Max.) = 0.9 seconds, as described earlier.7-4. FOUT output and 1 Hz carriesDuring a data write operation, because a reset is applied to the Devider counter (from the 128 Hzlevel to the 1 Hz level) after the CE pin goes high during the time between the falling edge of the first clock cycle and the rising edge of the second clock cycle, the length of the first 1 Hz cycle after thedata write operation is 1.0 s +0 / −7.8ms +t CES+t CLK. Subsequent cycles are output at1.0-second intervals.The 1-Hz signal that is output on FOUT is the internal 1-Hz signal with a 15.6-ms shift applied.8. Examples of External Circuits11. Reference DataNote : This data shows values obtained from a sample lot.12. Application notes1) Notes on handlingThis module uses a C-MOS IC to realize low power consumption. Carefully note the following cautions when handling.(1) Static electricityWhile this module has built-in circuitry designed to protect it against electrostatic discharge, the chip could still be damaged bya large discharge of static electricity. Containers used for packing and transport should be constructed of conductive materials.In addition, only soldering irons, measurement circuits, and other such devices which do not leak high voltage should be used with this module, which should also be grounded when such devices are being used.(2) NoiseIf a signal with excessive external noise is applied to the power supply or input pins, the device may malfunction or "latch up."In order to ensure stable operation, connect a filter capacitor (preferably ceramic) of greater that 0.1 µF as close as possible to the power supply pins (between VDD and GNDs). Also, avoid placing any device that generates high level of electronic noise near this module.* Do not connect signal lines to the shaded area in the figure shown in Fig. 1 and, if possible, embed this area in a GND land.(3) Voltage levels of input pinsWhen the input pins are at the mid-level, this will cause increased current consumption and a reduced noise margin, and can impair the functioning of the device. Therefore, try as much as possible to apply the voltage level close to VDD or GND.(4) Handling of unused pinsSince the input impedance of the input pins is extremely high, operating the device with these pins in the open circuit state can lead to unstable voltage level and malfunctions due to noise. Therefore, pull-up or pull-down resistors should be provided for all unused input pins.2) Notes on packaging(1) Soldering heat resistance.If the temperature within the package exceeds +260 °C, the characteristics of the crystal oscillator will be degraded and it may be damaged. The reflow conditions within our reflow profile is recommended. Therefore, always check the mounting temperature and time before mounting this device. Also, check again if the mounting conditions are later changed.* See Fig. 2 profile for our evaluation of Soldering heat resistance for reference.(2) Mounting equipmentWhile this module can be used with general-purpose mounting equipment, the internal crystal oscillator may be damaged in some circumstances, depending on the equipment and conditions. Therefore, be sure to check this. In addition, if the mounting conditions are later changed, the same check should be performed again.(3) Ultrasonic cleaningDepending on the usage conditions, there is a possibility that the crystal oscillator will be damaged by resonance during ultrasonic cleaning. Since the conditions under which ultrasonic cleaning is carried out (the type of cleaner, power level, time, state of the inside of the cleaning vessel, etc.) vary widely, this device is not warranted against damage during ultrasonic cleaning.(4) Mounting orientationThis device can be damaged if it is mounted in the wrong orientation. Always confirm the orientation of the device before mounting.(5) Leakage between pinsLeakage between pins may occur if the power is turned on while the device has condensation or dirt on it. Make sure the device is dry and clean before supplying power to it.Application ManualElectronic devices information on WWW serverDistributor/en/quartz/index.html。

RTC实时时钟芯片

RTC实时时钟芯片RTC实时时钟芯片是一种计时器,可以由硬件集成电路来完成,也可以由单片机加程序来完成。

实时时钟可以对秒、分、时、星期、日、月和年进行准确计时,具有闰年补偿功能,能够计时到2100年。

消费类电子(机顶盒、VCR),手持式装置(GPS、POS终端),医疗设备,办公设备,电信(路由器、交换机、服务器),电器设备,汽车,消费类电子,嵌入式时标,工业,电表。

DS3231集成了温度补偿晶体振荡器(TCXO)和晶体,电池备份输入用于支持连续计时,可编程方波输出,低电平有效复位输出。

关键参数:工作温度商业级:0°C至+70°C,具有2ppm精度;工业级:40°C至+85°C,具有3.5pmm精度。

DS3231M是业内首款内置MEMS、带温度补偿的RTC,允许器件用于强烈震动的场合,不会由于晶体失效而导致产品故障。

DS3232相比较于DS3231将32kHz输出驱动器更改为推挽输出,省去一个外部上拉电阻,节省空间,够加快时钟的边沿速度,降低器件功耗。

电池切换时,可通过32kHz位选择使能/禁止32kHz输出。

DS3232的32kHz输出在关闭状态下驱动至低电平,DS3231的32kHz输出在关闭状态下为高阻输出。

DS3232内部可通过2个CRATE位控制温度转换速率,这些位用于控制器件的采样率。

采样率决定了对温度传感器进行数字转换的频率,以及补偿振荡器的时间间隔。

降低采样率则降低了温度传感器的工作频率,从而降低整体功耗。

此外,DS3232具有236字节的SRAM。

压检测功能和振荡停止检测功能,内置定时器可以产生周期性的定时中断信号,警报器用于定时报警,可设定天、日期、小时、分钟。

工作电压范围:1.70V-5.5V。

计时保持电压:1.15V-5.5V。

此外,采用IIC接口,支持低功耗模式。

RX6110频率输出功能:能选择输出频率,有32.768kHz, 1024Hz, 1Hz。

爱普生(EPSON)实时时钟模块RTC-4543SA规格书

实际尺寸电路框图概览引脚功能定义引脚连接 / 外部尺寸规格(单位:mm)规格(特征)*请参考“应用手册”章节内容,以获取更多详细信息。

RTC-4543SA实时时钟模块 (SPI-Bus)简单功能 RTC - 4543 SA∙内置32.768 kHz 晶体单元. (频率精度调整完毕) ∙接口类型 :3线串行接口 ∙工作电压范围 :2.5 V ~ 5.5 V ∙宽计时器电压范围 :1.4 V ~ 5.5 V ∙32.768 kHz 频率输出功能 :带控制引脚的CMOS 输出 ∙包括时刻、日历、电压检测功能等产品号码(请联系我们)RTC-4543SA : Q41454352000200 RTC-4543SB : Q41454361000200推进环境管理体系 符合国际标准在环境管理体系的运行方面,使用ISO14001国际环境标准,通过“计划-实施-检查-验证(PDCA)的循环来实现持续改进。

公司位于日本和海外的主要制造基地已取得了ISO14001资格认证。

追求高品质Seiko Epson 为了向顾客提供高品质、卓越信赖性的产品、服务,迅速着手通过ISO 9000系列资格认证的工作,其日本和海外工厂也在通过ISO 9001认证。

同时,也在通过大型汽车制造厂商要求规格的ISO/TS 16949认证。

关于在目录内使用的记号●无铅。

●符合欧盟RoHS 指令。

欧盟RoHS 指令免检的含铅产品。

(密封玻璃、高温熔化性焊料或其他材料中包含铅。

)●为汽车方面的应用,如汽车多媒体、车身电子、遥控无钥门锁等。

●为汽车行驶安全方面的应用(引擎控制单元、气囊、电子稳定程序控制系统)。

注意事项·本材料如有变更,恕不另行通知。

量产设计时请确认最新信息。

·未经Seiko Epson 公司书面授权,禁止以任何形式或任何方式复制或者发布本材料中任何部分的信息内容。

·本材料中的书面信息、应用电路、编程、使用等内容仅供参考。

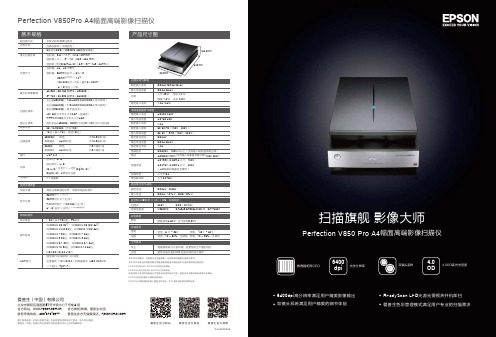

爱普生Perfection V850 Pro A4幅面高端影像扫描仪说明书

Perfection V850Pro A4幅面高端影像扫描仪ESS200309AZ图片仅供参考,外观以实物为准。

本说明若有任何细节之更改,恕不另行通知。

爱普生(中国)有限公司在法律许可的范围内对以上内容有解释权。

爱普生(中国)有限公司北京市朝阳区建国路81号华贸中心1号楼4层爱普生官方天猫旗舰店:官方网站: 官方微信/微博:爱普生中国服务导购热线:400-810-9977爱普生官方微博爱普生官方微信爱普生官方网站产品尺寸图本彩页中的数据,为爱普生实验室数据,与实际使用数据可能存在差异本彩页中所提出的网络功能均需要选购网络接口面板选件才能实现网络扫描功能EPSON为SEIKO EPSON公司的注册商标EPSON ME为SEIKO EPSON公司的商标其他所有产品名称和其他公司名称在此仅作标识之用,是各自所有者的商标或者注册商标。

EPSON对这些商标不拥有任何权利EPSON公司是国际能源之星的合作伙伴,本产品符合能源利用率标准308mm503mm152.5mm6400dpi4.0ODPerfection V850Pro A4幅面高端影像扫描仪Perfection V850Pro 不仅仅拥有6400dpi 的胶片扫描分辨率,并且配备了爱普生特有的双镜头系统,集专业胶片扫描与高端平板扫描于一身,是专业摄影师的安心优选。

其五段式可调节胶片固定夹,令扫描效果精准细腻,更可兼容多种类型和尺寸的照片及胶片。

Perfection V850Pro 特有ASIC 高速影像处理器,还特别配备高反射镜组件和覆有防反射光学薄膜的CCD光学组件,使得扫描速度快,质量好。

爱普生专业的Digital ICE 影像处理技术可以轻松去除扫描出来图像上的大部分燥点、划痕甚至水珠。

同时配备专业图像处理软件,满足专业摄影师的多方位需求。

V850Pro 具有6400dpi 的扫描分辨率,因此能够得到高质量的图像。

Digital ICE 技术V850Pro 具有Digital ICE 技术。

Seiko Epson 显示控制器 S5U13517P00C100 评估板用户手册说明书

SEIKO EPSON CORPORATIONRev. 1.0S1D13517 Display ControllerS5U13517P00C100 Evaluation Board UserManualNOTICENo part of this material may be reproduced or duplicated in any form or by any means without the written permission of Seiko Epson. Seiko Epson reserves the right to make changes to this material without notice. Seiko Epson does not assume any lia-bility of any kind arising out of any inaccuracies contained in this material or due to its application or use in any product or cir-cuit and, further, there is no representation that this material is applicable to products requiring high level reliability, such as, medical products. Moreover, no license to any intellectual property rights is granted by implication or otherwise, and there is no representation or warranty that anything made in accordance with this material will be free from any patent or copyright infringement of a third party. This material or portions thereof may contain technology or the subject relating to strategic products under the control of the Foreign Exchange and Foreign Trade Law of Japan and may require an export license from the Ministry of International Trade and Industry or other approval from another government agency.All other product names mentioned herein are trademarks and/or registered trademarks of their respective companies.©SEIKO EPSON CORPORATION 2009, All rights reserved.S1D13517 Display ControllerTable of ContentsChapter 1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5 Chapter 2 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6 Chapter 3 Installation and Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . 73.1 Configuration DIP Switch . . . . . . . . . . . . . . . . . . . . . . . . . . .73.2 Configuration Jumpers . . . . . . . . . . . . . . . . . . . . . . . . . . . .8Chapter 4 Technical Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 114.1 Power . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 114.1.1 Power Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 114.1.2 Voltage Regulators . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 114.1.3 S1D13517 Power . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 114.2 Clocks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 124.3 Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 124.4 Host Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 134.4.1 Direct Host Bus Interface Support . . . . . . . . . . . . . . . . . . . . . . . . . . 134.4.2 Connecting to the Epson S5U13U00P00C100 USB Adapter Board . . . . . . . . . 144.5 LCD Panel Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . 154.6 GPO and PWM Connections . . . . . . . . . . . . . . . . . . . . . . . . 16Chapter 5 Parts Lists . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17 Chapter 6 Schematic Diagrams . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19 Chapter 7 Board Layout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22 Chapter 8 References . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 248.1 Documents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 248.2 Document Sources . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24S5U13517P00C100 Evaluation Board User Manual (Rev. 1.0)EPSON3S1D13517 Display Controller4EPSON S5U13517P00C100 Evaluation Board User Manual (Rev. 1.0)S1D13517 Display ControllerChapter 1 IntroductionThis manual describes the setup and operation of the S5U13517P00C100 Evaluation Board. The evaluation board is designed as an evaluation platform for the S1D13517Display Controller.The S5U13517P00C100 evaluation board can be used with many native platforms via the host connector which provides the appropriate signals to support a variety of CPUs. The S5U13517P00C100 evaluation board can also connect to the S5U13U00P00C100 USB Adapter board so that it can be used with a laptop or desktop computer, via USB 2.0.This user manual is updated as appropriate. Please check the Epson Research and Development Website at for the latest revision of this document before beginning any development.*******************************************************************************************.com. S5U13517P00C100 Evaluation Board User Manual (Rev. 1.0)EPSON5S1D13517 Display ControllerChapter 2 FeaturesThe S5U13517P00C100 Evaluation Board includes the following features:•S1D13517 Display Controller (128-pin QFP)•Integrated Silicon Solution, Inc. IS42S16800E-7TLI 128M-bit SDRAM (54-pin TSOP)•Header with all S1D13517 Host Bus Interface signals•Headers for connection to the S5U13U00P00C100 USB Adapter board•Headers for connecting to LCD panels•Header for S1D13517 GPO pins and PWM pin•On-board 24MHz oscillator•14-pin DIP socket (if a clock other than 24MHz must be used)•3.3V input power•On-board voltage regulator with 2.5V output•On-board voltage regulator with adjustable 6~24V output, 40mA max., to provide power for LED backlight of LCD panels.6EPSON S5U13517P00C100 Evaluation Board User Manual (Rev. 1.0)S1D13517 Display ControllerS5U13517P00C100 Evaluation Board User Manual (Rev. 1.0)EPSON 7Chapter 3 Installation and ConfigurationThe S5U13517P00C100 evaluation board incorporates a DIP switch, jumpers, and 0 ohm resistors which allow it to be used with a variety of different configurations.3.1 Configuration DIP SwitchThe S1D13517 has 2 configuration inputs (CNF[1:0]). A DIP switch (SW1) is used to configure CNF[1:0] as described below.The following figure shows the location of DIP switch SW1 on the S5U13517P00C100 board.Figure 3-1: Configuration DIP Switch (SW1) LocationTable 3-1: Summary of Power-On/Reset OptionsSDU13517P00C100 SW1-[2:1] ConfigS1D13517 CNF[1:0] ConfigPower-On/Reset State1 (ON)0 (OFF)SW1-[1]CNF0Host data bus is 8-bit Host data bus is 16-bit SW1-[2]CNF1Host interface is ALE busHost interface is i80 bus= Required settings when using S5U13U00P00C100 USB Adapter boardDIP SwitchSW1S1D13517 Display Controller8EPSON S5U13517P00C100 Evaluation Board User Manual (Rev. 1.0)3.2 Configuration JumpersThe S5U13517P00C100 has 6 jumpers which configure various board settings. The jumper positions for each function are shown below.J1, J2, J3 - Power Supplies for the S1D13517J1, J2, J3 can be used to measure the current consumption of each S1D13517 power supply. When the jumper is at position 1-2, normal operation is selected.When no jumper is installed, the current consumption for each power supply can be measured by connecting an ammeter between pins 1 and 2 of the jumper.The jumper associated with each power supply is as follows:J1 for COREVDD J2 for IOVDD J3 for PLLVDDFigure 3-2: Configuration Jumper Locations (J1, J2, J3)Jumper Function Position 1-2Position 2-3No Jumper J1COREVDD Normal —COREVDD current measurement J2IOVDD Normal —IOVDD current measurement J3PLLVDD Normal —PLLVDD current measurementJ4IOVDD source 3.3V CN1 connector, pin 32—J524MHz control24MHz stop—Normal= Required settings when using S5U13U00P00C100 USB Adapter boardJumper Function Position 1-2Position 3-4Position 5-6J6Clock sourceOn board 24MHzSecond oscillatorCLKI pin to GNDJ3J2, J1S1D13517 Display ControllerJ4 - IOVDD SourceJ4 is used to select the source for the IOVDD supply voltage.When the jumper is at position 1-2, the IOVDD voltage is provided by the 3.3V power supply of the board. When the jumper is at position 2-3, the IOVDD voltage must be provided to the CN1 connector, pin 32.J5 - 24MHz ControlJ5 is used to control the 24MHz oscillator.When no jumper is installed, the 24MHz oscillator is running.When the jumper is at position 1-2, the 24MHz oscillator is stopped.J6 - Clock SourceJ6 is used to select the source for the clock input.When the jumper is at position 1-2, the on board 24MHz oscillator is selected.When the jumper is at position 3-4, the second oscillator is selected.When the jumper is at position 5-6, the CLKI pin is forced to GND.J5J4J6Figure 3-3: Configuration Jumper Location (J4, J5, J6)S5U13517P00C100 Evaluation Board User Manual (Rev. 1.0)EPSON9S1D13517 Display ControllerChapter 4 Technical Description4.1 Power4.1.1 Power RequirementsThe S5U13517P00C100 evaluation board requires an external regulated power supply (3.3V / 0.5A). The power is supplied to the evaluation board through pin 34 of the CN1 header, or pin 5 of the P2 header.The green LED ‘3.3V Power’ is turned on when 3.3V power is applied to the board.4.1.2 Voltage RegulatorsThe S5U13517P00C100 evaluation board has an on-board linear regulator to provide the 2.5V power required by the S1D13517 Display Controller. It also has a step-up switching voltage regulator to generate adjustable 6~24V, which can be used to power the LED backlight on some LCD panels.4.1.3 S1D13517 PowerThe S1D13517 Display Controller requires 2.5V and 3.0~3.6V power supplies.2.5V power for COREVDD and PLLVDD is provided by an on-board linear voltage regulator.IOVDD can be in the range of 3.0~3.6V. When J4 is set to the 1-2 position, IOVDD is connected to 3.3V. If a different voltage is required for IOVDD, set JP4 to the 2-3 position and connect the external power supply to pin 32 of connector CN1.10EPSON S5U13517P00C100 Evaluation Board User Manual (Rev. 1.0)S1D13517 Display Controller4.2 ClocksThe clock for the S1D13517 Display Controller is provided by a 24MHz oscillator.The S5U13517P00C100 evaluation board has a DIP14 footprint for an optional second oscillator, Y2. This is provided for cases requiring a different clock frequency for the S1D13517 Display Controller. To use Y2, an oscil-lator must be populated in the Y2 footprint and the J6 jumper placed at position 3-4.4.3 ResetThe S1D13517 Display Controller on the S5U13517P00C100 evaluation board can be reset using a push-button (SW2), or via an active low reset signal from the host development platform (pin 33 on the CN1 connector).SW2Y2Figure 4-1: Second oscillator and Reset switch Location (Y2, SW2)S1D13517 Display Controller4.4 Host Interface4.4.1 Direct Host Bus Interface SupportAll S1D13517 host interface pins are available on connector CN1 which allows the S5U13517P00C100 evaluation board to be connected to a variety of development platforms.The following figure shows the location of host bus connector CN1. CN1 is a 0.1x0.1 inch 34-pin header (17x2).CN1Figure 4-2: Host Bus Connector Location (CN1)For the pinout of connector CN1, see Chapter 6, “Schematic Diagrams” on page 18.S1D13517 Display Controller4.4.2 Connecting to the Epson S5U13U00P00C100 USB Adapter BoardThe S5U13517P00C100 evaluation board is designed to connect to a S5U13U00P00C100 USB Adapter Board. The USB adapter board provides a simple connection to any computer via a USB 2.0 connection. TheS5U13517P00C100 directly connects to the USB adapter board through connectors P1 and P2.The USB adapter board also supplies the 3.3V power required by the S5U13517P00C100. IOVDD should be selected for 3.3V and J4 should be set to the 1-2 position.When the S5U13517P00C100 is connected to the S5U13U00P00C100 USB Adapter board, there are 2 LEDs on S5U13517P00C100 which provide a quick visual status of the USB adapter. LED1 blinks to indicate that the USB adapter board is active. LED2 turns on to indicate that the USB has been enumerated by the PC.The following diagram shows the location of connectors P1 and P2. P1 and P2 are 40-pin headers (20x2).P1P2Figure 4-3: USB Adapter Connector Locations (P1 and P2)For the pinout of connectors P1 and P2, see Chapter 6, “Schematic Diagrams” on page 18.NoteA windows driver must be installed on the PC when the S5U13517P00C100 is used with the S5U13U00P00C100 USB Adapter Board. The S1D13xxxUSB driver is available at .S1D13517 Display Controller4.5 LCD Panel InterfaceThe LCD interface signals are available on connectors CN3 and CN5.Connector CN3 is 0.1x0.1 inch 40-pin header (20x2) and connector CN5 is 0.1x0.1 inch 10-pin header (5x2). For the pinout of connectors CN3 and CN5, see Chapter 6, “Schematic Diagrams” on page 18.On the evaluation board there is an adjustable 6~24V, 40mA max. power supply. This voltage is provided only on connector CN3 (it is not used elsewhere on the board). It is intended for use to power the LED backlight on some LCD panels. The voltage is adjusted by the VR1 pot.NoteFor LCD panels that use a CCFL backlight, an external power supply must be used to provide power to the inverter for the CCFL backlight. Usually, the inverter current consumption is higher than the maximum 40mA current available from the on-board voltage regulator.The following diagram shows the location of the LCD panel connectors CN3 and CN5.CN5CN3Figure 4-4: LCD Panel Connectors Location (CN3, CN5)S1D13517 Display Controller4.6 GPO and PWM ConnectionsThe S1D13517 Display Controller has 4 GPO pins and PWM pin. All the GPO pins and PWM pin are routed to the CN4 connector. Connector CN4 is 0.1x0.1 inch 10-pin header (5x2).The following figure shows the location of the GPO and PWM connector, CN4.CN4Figure 4-5: GPIO and PWM Connector Location (CN4)For the pinout of connector CN4, see Chapter 6, “Schematic Diagrams” on page 18.S1D13517 Display ControllerChapter 5 Parts ListsTable 5-1: Parts ListItem Quantity Reference Part11CN1A1-34PA-2.54DSA(71)21CN3HIF3FC-40PA-2.54DSA32CN4,CN5A1-10PA-2.54DSA(71)427C1,C3,C5,C7,C9,C11,C13,C15,C17,C19,C21,C23,C25,C27,C28,C31,C32,C34,C35,C37,C43,C45,C47,C49,C51,C53,C550.1u523C2,C4,C6,C8,C10,C12,C14,C16,C18,C20,C22,C24,C26,C29,C33,C38,C44,C46,C48,C50,C52,C54,C560.01u61C302000p71C36100u81C4047u 10v91C4110p101C421u 50V111D1SML-310VT121D2SML-310DT131D3SML-310PT141D4MBR0530152F1,F2ACF451832-222 164J1,J2,J3,J5WL-1-2P171J4WL-1-3P181J6WLW-3192L1,L2BLM21P201L3LQH32CN100K23L 213PAD1,PAD2,PAD32mm diameter222P1,P2PRPN202PAEN-RC 231R13k 1%243R2,R3,R410kS1D13517 Display Controller2549R5,R6,R7,R8,R10,R11, R12,R14,R15,R21,R22, R23,R24,R25,R26,R27, R28,R29,R30,R31,R32, R33,R34,R35,R36,R37,R38,R39,R40,R41,R42, R43,R44,R45,R46,R47, R48,R49,R50,R51,R52, R53,R54,R55,R56,R57,R58,R59,R60261R9150k 272R13,R1733 1%281R16NM 293R18,R19,R20270301R61887k 311R6222k 321R6347k336SH1,SH2,SH3,SH4,SH5,SH6.100 in. Jumper Shunt341SW1CFS-0400MB 351SW2SKRKAEE0103610TP1,TP2,TP3,TP4,TP5,TP6,TP7,TP8,TP9,TP10HK-2-S371U1S1D13517381U2TPS76915DBVT391U3IS42S16800E (128Mbit SDRAM)401U4TPS61040411VR1200k421Y1SG-210 24MHz 431Y2XR2A-1405Table 5-1: Parts ListItemQuantityReferencePartS1D13517 Display ControllerFigure 6-1: S5U13517P00C100 Schematic Diagram (1 of 3)S1D13517 Display ControllerFigure 6-2: S5U13517P00C100 Schematic Diagram (2 of 3)S1D13517 Display ControllerFigure 6-3: S5U13517P00C100 Schematic Diagram (3 of 3)S1D13517 Display Controller Chapter 7 References7.1 Documents•Epson Research and Development, Inc., S1D13517 Hardware Functional Specification, document numberX92A-A-001-xx•Epson Research and Development, Inc., S5U13U00P00C100 USB Adapter Board User Manual, document number I00Z-G-018-xx7.2 Document Sources•Epson Research and Development Website: S5U13517P00C100 Evaluation Board User Manual (Rev. 1.0)EPSON21S1D13517 Display ControllerChange RecordX92A-G-001-01 Revision 1.0 - Issued: May 8, 2009•initial release22EPSON S5U13517P00C100 Evaluation Board User Manual (Rev. 1.0)Document Code: X92A-G-001-01Issued 2009/04/28International Sales OperationsAMERICAEPSON ELECTRONICS AMERICA, INC.2580 Orchard Parkway San Jose, CA 95131,USA Phone: +1-800-228-3964FAX: +1-408-922-0238EUROPEEPSON EUROPE ELECTRONICS GmbHRiesstrasse 15, 80992 Munich,GERMANYPhone: +49-89-14005-0 FAX: +49-89-14005-110ASIAEPSON (CHINA) CO., LTD.7F, Jinbao Bldg., No.89 Jinbao St.,Beijing 100005, CHINAPhone: +86-10-6410-6655 FAX: +86-10-6410-7320SHANGHAI BRANCH7F, Block B, High-Tech Bldg., 900, Yishan Road,Shanghai 200233, CHINAPhone: +86-21-5423-5522 FAX: +86-21-5423-5512EPSON HONG KONG LTD.20/F, Harbour Centre, 25 Harbour Road Wanchai, Hong Kong Phone: +852-2585-4600 FAX: +852-2827-4346 Telex: 65542 EPSCO HXSHENZHEN BRANCH12F, Dawning Mansion, Keji South 12th Road,Hi-Tech Park, Shenzhen 518057, CHINAPhone: +86-755-2699-3828 FAX: +86-755-2699-3838EPSON TAIWAN TECHNOLOGY & TRADING LTD.14F, No. 7, Song Ren Road, Taipei 110, TAIWANPhone: +886-2-8786-6688 FAX: +886-2-8786-6660EPSON SINGAPORE PTE., LTD.1 HarbourFront Place,#03-02 HarbourFront Tower One, Singapore 098633 Phone: +65-6586-5500 FAX: +65-6271-3182SEIKO EPSON CORP. KOREA OFFICE50F, KLI 63 Bldg., 60 Yoido-dongYoungdeungpo-Ku, Seoul, 150-763, KOREA Phone: +82-2-784-6027 FAX: +82-2-767-3677SEIKO EPSON CORP.SEMICONDUCTOR OPERATIONS DIVISION IC Sales Dept.IC International Sales Group421-8, Hino, Hino-shi, Tokyo 191-8501, JAPAN Phone: +81-42-587-5814 FAX: +81-42-587-5117Dongcheng District,Mouser ElectronicsAuthorized DistributorClick to View Pricing, Inventory, Delivery & Lifecycle Information:E pson:S5U13517P00C100。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

DIVIDER

FOUT CONTROLLER

INTERRUPT CONTROLLER

INTERFACE CIRCUIT

CLOCK and CALENDAR

TIMER REGISTER

ALARM REGISTER

SYSTEM CONTROLLER

and CONTROL REGISTER

• •UA •UB •UC •AA

± 3.4 x 10-6 / -40 ºC ~ +85 ºC 商

± 5.0 x 10-6 / -40 ºC ~ +85 ºC 商 ± 5.0 x 10-6 / -30 ºC ~ +70 ºC (+5 ± 5.0) x 10-6 / +25 ºC

9

器

13

器

•

:

1/100s

●为汽车行驶安全方面的应用(引擎控制单元、气囊、电子稳定程序控制系统)。

注意事项

·本材料如有变更,恕不另行通知。量产设计时请确认最新信息。 ·未经 Seiko Epson 公司书面授权,禁止以任何形式或任何方式复制或者发布本材料中任何部分的信息内容。 ·本材料中的书面信息、应用电路、编程、使用等内容仅供参考。Seiko Epson 公司对第三方专利或版权的侵权行为不负有任何责任。本材料

0

-5

-10

-15 Tuning fork X'tal

-20

-25

-30 -45 -35 -25 -15 -5 5 15 25 35 45 55 65 75 85 Temperature (ºC)

推进环境管理体系 符合国际标准

在环境管理体系的运行方面,使用 ISO14001 国际环境标准,通过“计 划-实施-检查-验证(PDCA)的循环来实现持续改进。公司位于日本和 海外的主要制造基地已取得了 ISO14001 资格认证。

5 ± 5.0∗3

(1)

IDD1

, VDD = 5V

-

0.75

3.4

(2)

FOE = GND,

IDD2

/INT = VDD FOUT output : OFF

VDD = 3V

-

0.75

2.1

µA

∗1 )

9

∗2 )

13

∗3 )

13

(

)

Frequency tolerance ( ×10-6 )

5 32.768 kHz DTCXO

9. EVIN 8. N.C.

∗

32.768 kHz-DTCXO Frequency temperature characteristics (Example)

Min.

Typ.

Max.

Frequency temperature characteristics

VDD

1.6

3.0

5.5

V

10

VTEM

2.2

/ INT

GND

-

T2(VPP)

-

DO

DI

( CMOS

)

FOUT

商 N-ch

器

1. CE 2. CLK 3. FOUT 4. N.C. 5. TEST 6. VDD 7. FOE

1.27

RA4803 SA

5.0 7.4 ± 0.2 SOP − 14 pin

3.2 ± 0.1

10.1 ± 0.2

14. DI 13. DO 12. T2(VPP) 11. GND 10. / FOUT •

(CMOS ), CL=30 pF 32.768 kHz, 1024 Hz, 1 Hz.

• • • • EVIN

1/4096 ,,

4095 .

• 1PPS

•

RX-4801

*

,

32.768kHz .

/

( :mm)

CE

CLK

FOUT

TEST

VDD

-

FOE

EVIN

1.太空设备(人造卫星、火箭等) 2.运输车辆机器控制装置(汽车、飞机、火车、船舶等) 3.用于维持生命的医疗器械 4.海底中转设备 5.发电站控制机器 6.防灾防盗装置 7.交通设备 8.其他,用于与 1~7 具有同等可靠性的用途。

本材料中记载的品牌名称或产品名称是其所有人的商标或注册商标。

Seiko Epson Corporation

(SPI-Bus)

DTCXO,

RA4803 SA

• 32.768 kHz

(

) DTCXO

•1/100s

•

:4

•

: 1.6 V ~ 5.5 V

•

: 2.2 V ~ 5.5 V

•

: 1.6 V ~ 5.5 V

•

32.768 kHz, 1024 Hz, 1Hz.

•

,

,

,EVIN

•

多

多

• AEC-Q200

商

ISO/TS16949 是一项国际标准,是在 ISO9001 的基础上增 加了对汽车工业的特殊要求部分。

关于在目录内使用的记号

●无铅。

●符合欧盟 RoHS 指令。 欧盟 RoHS 指令免检的含铅产品。 (密封玻璃、高温熔化性焊料或其他材料中包含铅。)

●为汽车方面的应用,如汽车多媒体、车身电子、遥控无钥门锁等。

ISO 14000 是国际标准化组织于 1996 年在全球化变暖、臭 氧层破坏、以及全球毁林等环境问题日益严重的背景下提

出的环境管理国际标准。

追求高品质

Seiko Epson 为了向顾客提供高品质、卓越信赖性的产品、服务,迅 速着手通过 ISO 9000 系列资格认证的工作,其日本和海外工厂也在通 过 ISO 9001 认证。同时,也在通过大型汽车制造厂商要求规格的 ISO/TS 16949 认证。

3.0

5.5

V

VCLK

1.6

3.0

5.5

V

TOPR

−

-40

+25

+85

ºC

UA UB ∆ f / f UC

Ta = -40 ºC ~ +85 ºC Ta = -40 ºC ~ +85 ºC Ta = -30 ºC ~ +70 ºC

±3.4 ∗1 ±5.0 ∗2

× 10-6

AA Ta = +25 ºC

未对任何专利或知识版权的许可权进行授权。 ·本材料中规格表中的数值大小通过数值线上的大小关系表示。 ·当出口此材料中描述的产品或技术时,你应该遵守相应的出口管制法律和法规,并按照这些法律和法规的要求执行。

请不要将产品(以及任何情况下提供任何的技术信息)用于开发或制造大规模杀伤性武器或其他军事用途。还要求,不要将产品提供给任何 将产品用于此类违禁用途的第三方。 ·此类产品是基于在一般电子机械内使用而设计开发的,如将产品应用于需要极高可靠性的特定用途,必须实现得到弊公司的事前许可。若 无许可弊公司将不负任何责任。

器

RA4803SA UA : X1B000252A00100

RA4803SA UB : X1B000252A00200

RA4803SA UC : X1B000252A00300

RA4803SA AA : X1B000252A00600

FOE FOUT

EVIN / INT

DI DO CLK CE

32.768 kHz