Concept_HDL原理图设计002

CADENCE应用---HDL原理图+Allegro基本操作

CADENCE应⽤---HDL原理图+Allegro基本操作HDL原理图+Allegro基本操作1.启动Project Manager操作可以通过开始菜单栏或者桌⾯快捷⽅式启动Project Manager;Project Manager⽤于整个⼯程的维护,可以打开及编辑原理图、PCB,更新⽹表等操作。

打开后的Project Manager见下图:layout阶段主要使⽤OpenProject;2.原理图与PCB打开操作介绍A.Project Manager默认选择下图所⽰版本B.点击Project Manager界⾯中的OpenProject按钮,选择需要打开的⼯程;C.需要选择的⽂件为cpm后缀的⽂件,见下图:D.选择cpm⽂件后,打开后的Project Manager界⾯如下图所⽰:E.说明:①⼯程需要完整,不能缺失⽂件,否则打开容易出错;客户提供⽂件要提供完整的⼯程⽂件夹;②PCB需要放在physical⽂件夹下,这样才能⽅便后续的同步更新⽹表及PCB与原理图同步关联;physical⽂件夹是worklib⽂件夹的⼦⽂件夹;3.更新⽹表操作HDL更新第⼀⽅⽹表有2种操作:A.直接⽣成⽹表,然后在PCB中导⼊⽹表不勾选update PCB…,⽣成的⽹表在packaged⽂件夹下;PCB中导⼊⽹表操作:如下图,选择HDL格式,Import directory需要⽹表所在位置;B.第⼆种⽅法:直接同步关联,在⽣成⽹表的同时对PCB进⾏更新;在export physical时勾选下图所⽰“update PCB …”,PCB⽂件放在physical⽂件夹下;其中“1”选择的为需要更新⽹表的PCB⽂件;“2”为更新⽹表之后的PCB;建议此处命名和“1”处做区分;点击OK,进⾏⽹表更新,直⾄提⽰完成为⽌;更新⽹表时,不要打开PCB⽂件;4.原理图和PCB关联操作在Project Manager界⾯分别打开PCB和原理图⽂件,此时的PCB和原来图时关联的关系;原理图与PCB抓取器件操作:A.在PCB中启动移动命令;B.切换到原理图界⾯,选择symbol;如下图,只勾选symbol;C.在原理图中框选器件,被框选的器件会⾼亮:使⽤如下图命令进⾏器件框选;上图所⽰命令的图标显⽰如下图,可以将图标调出,放在⼯具栏,⽅便使⽤;D. 关于抓取器件的具体操作:1启动框选命令;2⿏标在原理图适当位置单击⼀下;3然后移动⿏标,出现⼀个矩形框,此矩形框随⿏标移动⽽变化尺⼨;4想要框选的器件都在或者⼤部分都在框内时,单击⿏标左键;5.完成框选,被框选的器件⾼亮,如下图:6.移动⿏标光标⾄任意被⾼亮器件上,单击⿏标中键,此时被框选器件会闪动;7.闪动结束,则PCB中对应器件被选中;此时切换到allegro界⾯,在PCB上点击⼀下⿏标左键,则被选中的器件随⿏标移动;E.其他a.⾼亮器件类似上述操作;b.在原理图中查找器件命令:Ctrl+F;…..。

ConceptHDL原理图设计(图文运用)

Allegro Design Entry HDL原理图输入方式孙海峰Design Entry HDL是Cadence公司原有的原理图设计输入系统,提供了一个全面、高效、灵活的原理图设计环境,具有强大的操作编辑功能。

设计者在HDL 环境中能够完成整个原理图设计流程,可以进行层次原理图和平面原理图输入、原理图检查、生成料单、生成网表等工作。

HDL还能与Allegro工具很好的集成在一个工程中,可很方便的实现原理图到PCB的导入,以及PCB改动反标到原理图等交互式操作。

接下来,按照原理图设计输入流程,我来详细阐述Design Entry HDL原理图的输入方式。

一、进入Design Entry HDL用户界面进入HDL原理图输入界面的步骤如下。

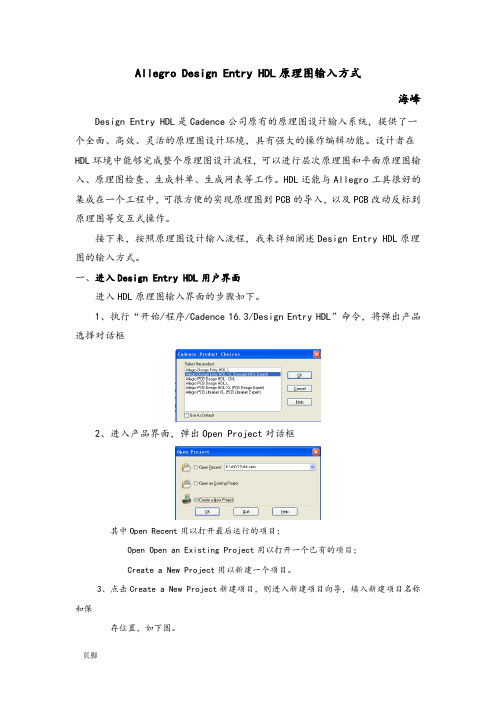

1、执行“开始/程序/Cadence 16.3/Design Entry HDL”命令,将弹出产品选择对话框2、进入产品界面,弹出Open Project对话框其中Open Recent用以打开最后运行的项目;Open Open an Existing Project用以打开一个已有的项目;Create a New Project用以新建一个项目。

3、点击Create a New Project新建项目,则进入新建项目向导,填入新建项目名称和保存位置,如下图。

4、点击下一步,进入Project Libraries对话框,在可用元件库中为项目添加元件库5、点击下一步,进入Design Name对话框,Library中选择需要的元件库,Design中可以填写新建项目名称,也可以选择已有元件,对其进行修改。

6、点击下一步,进入Summary对话框,显示前面步骤所设置的所有内容。

7、点击Finish按钮,在接下来的对话框中均确定就可以完成项目的新建,并出现原理图工作界面。

其中:(1)标题栏——显示文件所在路径和文件名称;(2)菜单栏——项目所有相关操作的集合;包含了文件菜单、编辑菜单、视图菜单、元件菜单、画线菜单、文本菜单、模块菜单、群组菜单、显示菜单、仿真菜单、RF-PCB菜单、工具菜单、窗口菜单和帮助菜单。

cept+HDL原理图设计(3)

原理图设计的后处理在前面两节课学习了平铺原理图和层次原理图的绘制之后,接下来的工作就是对整个项目的后处理阶段包括:打包、全局检查、输出以及打印等。

在接下来的步骤中,首先要做的就是原理图设计的打包,否则,将不能进行后面的操作。

一、原理图设计打包原理图设计的打包就是将原理图设计的整个项目的信息进行整合,使之成为一个整体。

因此,所有全局类的操作及整个项目的输出必须在打包后才能进行。

运行打包操作有两种方法:1、在原理图设计页面中选择菜单栏中的File/Export Physical命令;2、在项目管理界面中左键单击Design Sync按钮,在弹出的菜单中选择Export Physical命令。

采用以上任何一种操作,都可以打开打包界面,如图7_60所示。

7_60Export Physical界面共包括3个部分的内容:1)Package Design:原理图打包设计项。

选中此项表示要进行原理图设计的打包。

其各选项设置的意义分别是:Preserve:保留上一次的所有打包信息。

默认项为此项,建议在一般情况下选择此项,因为选择此项不会对PCB产生影响,只是对原来信息的一个覆盖过程。

Optimize:将设计重新打包成一个更紧凑的设计。

Repackage:忽略原有的打包信息,将设计重新打包,重新生成打包信息。

Advanced:此项设置为原理图打包的详细设置,界面如图7_61所示,一般不需要修改。

7_612)Regenerate Physical Net Names:对所有的网名生成物理网名。

只有在两种情况下才选择此项:1、改变了网名的长度没有选择Repackage选项;2、将设计导入到Cadence13.6版本或者更早的版本。

3)BackAnnotate to Schematic Canv:反标原理图项,选中此项将打包的信息如位号、规则等信息反标回原理图中。

注意,此处不是将PCB中的信息反标回原理图,而是更新由于原理图的变更而产生的信息。

Concepthdl:concepthdl

Concepthdl管脚名字不能使用非法字符如tx[15],改为tx15。

不然会报找不到实体名字的错误Concepthdl grid选项logic grid(预定义0.100 x 5)指在hdl上作图时,图上grid的分辨率,symbol grid(预定义0.050 x 2)指画原件符号本身时grid的分辨率。

如果在画图时出现划线对不上管脚的情况可以减小logic grid的分辨率。

Document grid(预定义0.100 x 5)不清楚Allegro做pcb板步骤总结1 作michanical板子边框,rooute keepin ,package keepin。

标注板子2 place component,先设计基本规则,注意如果有bga器件或者需要自动扇出的器件,要先扇出后再对具体网络进行规则设计如差分对,管脚对等,另外规则设计最好一次完成,考虑到所有情况,而且以后不再更改。

3 定义各个平面层包括加入的虚拟电源平面层,但不copper,多电源且只有一个电源平面层时可以先不定义分割vcc层4 先布需要手动布线的器件,如果有swap pin要先反标回原理图,然后自动布线完成设计。

5 自动布线完毕检查pcb,进行必要的修改gloss,然后检查是否有没连接网络,有无对设计有重大影响的drc 错误,当一切确认无误后,重新排列元件序号位置。

板子上需要加text注明的地方加text6copper各个平面层和信号层,出光绘在做gnd和power封装时,注意需要设置hdl_power属性使其变成一个网络符号。

还有如果封装符号不一样,将会导致packet-xl出错,删除packages,使用symbol重新产生即可传到allgro,封装不可见或不正确的情况。

如果是.dra的情况,修改Sch中元件JEDEC_TYPE的value使其指向正确的值。

(可以用part developer打开元件,重新设置属性,save退出,关闭原理图,重新打开即可以更新原理图重要修改元件的属性)如果是封装中的*.pad不可见,重新修改或创建pad。

Cadence-HDL学习

1Cadence HDL学习1.1原理图设计步骤:建立项目:1.2Create Design Project, 输入Project 名称, 输入Design名称映射原理图库:1.3通过修改Setup中的cds.lib, 如果增加某个库, 可按照下列例子进行:define classlib ../classlib。

如果成功, 可在备选的库中看到classlib。

注意, 一定要小写字母, 大写字母带来不确定的问题。

1.4映射PCB库1.5在Project Setup-Tools, 选中PCB Editorsetup-Design_paths的padpath跟psmpath要选择库文件在的路径。

1.6其它设置在Project Setup-Tools-Design Entry HDL 设置General schematic settings, 具体设计看conHDLFTB_15.7.pdf page45。

设置chematic Grid Settings1.7设置Custom Vrariables, 之后就可保存并打开DE HDL了。

1.8设置原理图环境1.9View-Toolbars, 选中常用的几个, add, adit group,standard等。

1.10添加器件,画原理图1.11增加offpage connectors1.12检查设计1.13T ools-Check, 根据提示修改错误或者保存设计。

1.14打包原理图手动或者自动(在打包时候自动添加)添加元器件编号。

手动的话, 鼠标放在器件的上方, 右键看到菜单中的Attribute选项, 修改$LOCATION的值即可。

1.15选择File-Export Physical, 注意不选Update PCBEditor Board(Netrev), 但是选中Backannotate Packaging Properties to Schematic Canvas.1.16运行Rules Checker1.17在Project Manager 窗口, 选中Tools-Rules Checker:选中Logical 环境中的loading_io_checks.rle 以及net_name_checks_rle1.18运行Crefer在Project Manager Toos-Crefer, 选中Options, 在Cref Data File选项中, 找到合适的路径(User1/ftb/setup), 选中cref.dat, 点击Open。

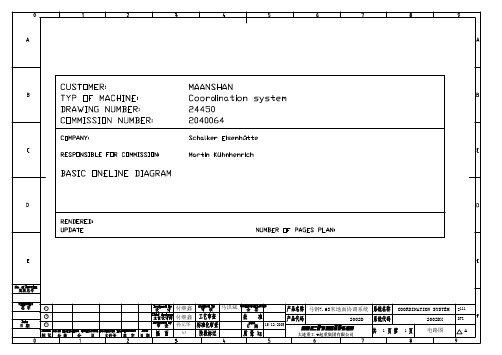

CO_PLC2002D原理图

英文标注

SCHALKE 供货

SCHALKE 供货

ANTENNA

ANTENNA

c b a

付继鑫 付继鑫

孙元华

A3

马洪斌

30/01/2007

马钢7.63米地面协调系统 2002D

大连重工·起重集团有限公司

19

操作及监视系统 2002DX.712

5

=111.712 +9505

电路图

B

中文标注

装煤车中部 CDQ 侧无线通讯箱 CC-MIDDLE CDQ ACCESS POINT BOX

ANTENNA

ANTENNA

c b a

付继鑫 付继鑫

孙元华

A3

马洪斌

30/01/2007

马钢7.63米地面协调系统 2002D

大连重工·起重集团有限公司

19

操作及监视系统 2002DX.712

1

=111.712 +9501

电路图

B

中文标注

装煤车熄焦塔侧无线通讯箱 CC-QT ACCESS POINT BOX

16

17

18

19

20

21 W019 : 2 W020 : 1

-X30:

W021 : 2

W018 : 1

W018 : 2

W019 : 1

c b a

付继鑫 付继鑫

孙元华

A3

马洪斌

30/01/2007

马钢7.63米地面协调系统 2002D

大连重工·起重集团有限公司

4

W020 : 2

22

AC230V电源系统

c b a

付继鑫 付继鑫

孙元华

A3

ConceptHDL原理图设计

AllegroDesign EntryHDL原理图输入方式孙海峰Design EntryHDL就是Cadence公司原有得原理图设计输入系统,提供了一个全面、高效、灵活得原理图设计环境,具有强大得操作编辑功能。

设计者在HDL环境中能够完成整个原理图设计流程,可以进行层次原理图与平面原理图输入、原理图检查、生成料单、生成网表等工作。

HDL还能与Allegro工具很好得集成在一个工程中,可很方便得实现原理图到PCB得导入,以及PCB改动反标到原理图等交互式操作。

接下来,按照原理图设计输入流程,我来详细阐述DesignEntry HDL原理图得输入方式。

一、进入DesignEntry HDL用户界面进入HDL原理图输入界面得步骤如下.1、执行“开始/程序/Cadence16、3/Design Entry HDL”命令,将弹出产品选择对话框2、进入产品界面,弹出Open Project对话框其中OpenRecent用以打开最后运行得项目;Open Open an ExistingProject用以打开一个已有得项目;Create a New Project用以新建一个项目。

3、点击Createa NewProject新建项目,则进入新建项目向导,填入新建项目名称与保存位置,如下图。

4、点击下一步,进入Project Libraries对话框,在可用元件库中为项目添加元件库5、点击下一步,进入Design Name对话框,Library中选择需要得元件库,Design 中可以填写新建项目名称,也可以选择已有元件,对其进行修改。

6、点击下一步,进入Summary对话框,显示前面步骤所设置得所有内容。

7、点击Finish按钮,在接下来得对话框中均确定就可以完成项目得新建,并出现原理图工作界面。

其中:(1)标题栏——显示文件所在路径与文件名称;(2)菜单栏——项目所有相关操作得集合;包含了文件菜单、编辑菜单、视图菜单、元件菜单、画线菜单、文本菜单、模块菜单、群组菜单、显示菜单、仿真菜单、RF—PCB菜单、工具菜单、窗口菜单与帮助菜单。

ConceptHDL原理图设计说明

Allegro Design Entry HDL原理图输入方式海峰Design Entry HDL是Cadence公司原有的原理图设计输入系统,提供了一个全面、高效、灵活的原理图设计环境,具有强大的操作编辑功能。

设计者在HDL环境中能够完成整个原理图设计流程,可以进行层次原理图和平面原理图输入、原理图检查、生成料单、生成网表等工作。

HDL还能与Allegro工具很好的集成在一个工程中,可很方便的实现原理图到PCB的导入,以及PCB改动反标到原理图等交互式操作。

接下来,按照原理图设计输入流程,我来详细阐述Design Entry HDL原理图的输入方式。

一、进入Design Entry HDL用户界面进入HDL原理图输入界面的步骤如下。

1、执行“开始/程序/Cadence 16.3/Design Entry HDL”命令,将弹出产品选择对话框2、进入产品界面,弹出Open Project对话框其中Open Recent用以打开最后运行的项目;Open Open an Existing Project用以打开一个已有的项目;Create a New Project用以新建一个项目。

3、点击Create a New Project新建项目,则进入新建项目向导,填入新建项目名称和保存位置,如下图。

4、点击下一步,进入Project Libraries对话框,在可用元件库中为项目添加元件库5、点击下一步,进入Design Name对话框,Library中选择需要的元件库,Design中可以填写新建项目名称,也可以选择已有元件,对其进行修改。

6、点击下一步,进入Summary对话框,显示前面步骤所设置的所有容。

7、点击Finish按钮,在接下来的对话框中均确定就可以完成项目的新建,并出现原理图工作界面。

其中:(1)标题栏——显示文件所在路径和文件名称;(2)菜单栏——项目所有相关操作的集合;包含了文件菜单、编辑菜单、视图菜单、元件菜单、画线菜单、文本菜单、模块菜单、群组菜单、显示菜单、仿真菜单、RF-PCB菜单、工具菜单、窗口菜单和帮助菜单。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第七章Concept HDL原理图设计本章主要介绍Concept HDL原理图设计设计流程、用户界面以及编辑环境,学习如何使用Concept HDL软件来进行原理图设计,并以一些实际例子来给大家讲解如何进行一个项目的原理图设计,在讲解的过程中会对原理图设计过程中需要注意的问题、一些设计技巧以及一些习惯性的设置等做专门批注。

一、原理图设计的基础在进行原理图设计之前,必须学习一下原理图设计的一些基本规范和原理图设计的基本流程。

根据每个公司的要求不一样,原理图设计的规范和流程并不是完全一样的,在此给大家讲解一下基本规范和典型的原理图设计流程。

原理图设计的基本要求是:规范性、可读性、美观性。

1、原理图设计的规范■图幅的使用要统一对于一个项目的原理图设计,顶层图、分页图使用多大的图幅要统一。

在进行原理图设计之前,要选好图幅,如:A2、A3、A4等。

每个公司可以根据自己的需要将图幅设计成一定的格式然后做成原理图库,以便原理图设计者使用从而保证统一性。

■各功能布局的统一性在一页原理图中,各个功能布局要注意统一性。

如:电源一般在左上角,核心芯片在中间,时钟一般在右下角等。

■网络命名统一1)电源和地的命名统一。

如:3V3(3.3V的电源)、2V5(2.5V的电源)、5V(5V的电源)、GND(地平面)、PGND(保护地)等。

2)差分信号命名统一。

如:用P来代替+,用N来代替-。

3)全局网名统一用“\G”来表示。

4)总线的命名统一用“<M..N>”来表示。

5)低有效信号统一用“_N”来表示。

6)数据类信号用DATA来表示,时钟类信号用CLK来表示,地址类信号用ADDR来表示等。

■网名、位号、属性等的字体要大小适中,便于阅读■元件的摆放整齐有序、布局合理2、原理图设计的流程进行一个项目的原理图设计,主要分为3个阶段。

■设计前准备阶段此阶段主要是设计前的准备工作。

包括:总体方案的设计、元件的选型、库的设计及将其添加到项目中。

■设计阶段在准备工作都完成之后,就进入设计阶段开始设计工作。

这阶段主要包括:新建一个项目、Concept HDL的初始化的设置和原理图的绘制。

■设计后输出阶段完成了设计之后,要对原理图进行仔细的检查、打包原理图、导出物料表以及完成原理图的打印、输出工作,开始PCB 设计工作。

7_1图7_1是一个项目原理图设计的基本流程。

二、Concept HDL 的用户界面Concept HDL 是Cadence 公司的原理图输入工具,提供原理图输入与分析的一个真正的协同设计的环境。

其用户界面由标题栏、菜单栏、工具栏、设计窗口、状态栏以及命令控制窗口组成,如图7_2所示。

对于Concept HDL 界面的6个部分,标题栏显示当前所 得页面及页面状态,设计窗口就是整个设计所在的窗口,也就是图7_2中所示中间区域,命令栏是供用户写入命令的窗口(可以通过点击View/Console Window 来控制是否打开),状态栏是显示当前状态的一栏,包括样式、选中、使用库、栅格和鼠标位置坐标等。

下面分解详细讲解一下菜单栏和工具栏。

1、 菜单栏Concept HDL 的菜单栏是由13个下拉菜单组成,他们分别是:File (文件类)、Edit (编辑类)、View (查看类)、Component (元件类)、Wire (线类)、Text (字符类)、Block (模块类)、Group (群组类)、Display (显示类)、AMS Simulator (仿真类)、Tools (工具类)、Window (窗口类)、Help (帮助)。

1) File (文件类)文件类的下拉菜单中的命令主要包括:新建、打开、关闭及保存一个文件及转换(Revert )、回复(Recover )、移动(Remove )、编辑页面,编辑层次图、更改序列号、输入\输出原理图信息、原理图打印相关的设置、推出等。

2) Edit (编辑类)编辑类的下拉菜单主要是对元件和线进行编辑的一些命令,如:后退\前进命令(Undo\Redo )、移动、复制、排列、删除、镜像、旋转、层次图显示、创建圆\圆弧等。

7_23)View(查看类)查看类的下拉菜单的命令主要是控制整个界面的,如:缩放界面、界面的上下左右移动、以及界面中的控制栏、错误表示栏、命令栏是否打开灯。

4)Component(元件类)元件类的下拉菜单都是对元件进行操作的一些命令,如:添加元件、替换元件、替换元件的part(Version)、元件封装信息更改(Modify)、显示元件的引脚(Section)、交换\转换引脚(Swap Pins\Bubble Pins)、删除元件所有属性(Smash)等。

5)Wire(线类)线类的下拉菜单中主要包括:连线命令(Draw和Route)、添加网名(Signal Name)、总线网名(Bus Name)、总线符号设置(Bus Tap)、加连接点(Dot/Connection Point)、线加粗\细(Thick\Thin)、线样式选择(Pattern)等。

6)Text(字符类)字符类的下拉菜单主要包括:添加一个带属性字符(Property)、增加一个自定义的字符(Custom Text)、查看字符属性(Attributes)、分配电源\信号引脚模型(Assign Power\Signal)、更新当前页面的字符(Update SheetVariables)、更改字符(Change)、增加接口名字(Port Name)、设置字符大小(Set Size)、交换字符(Swap)、更改字符属性(Reattach)、属性显示格式选择(Property Display)等。

7)Block(模块类)模块类的下拉菜单的命令主要是针对模块的操作,在没有选中模块的时候,大多数命令都是不可选中的。

此下拉菜单命令包括:增加一个模块(Add)、模块名的更改(Rename)、模块大小的更改(Stretch)、模块上划线(Draw Wire 和Route Wire,模块上会自动增加引脚)、模块引脚的添加(Add Pin会有3种接口供选择:输入、输出、双向)及引脚的删除、更名、移动等命令。

8)Group(群组类)群组类的下拉菜单中的命令主要包括:创建一个组,设置当前组的组名、查看组的内容以及对当前组的移动、删除、复制、设置字符大小、选择颜色表示、高亮显示及元件更新等命令。

9)Display(显示类)显示类俄下拉菜单中的命令都是与项目中元件、网名等显示有关的,包括:高亮显示(Highlight)、去除高亮显示(Dehighlight)、属性的显示(Attachments)、颜色标示(Color)、显示元件信息(Component)、星号显示一个网名连接多处引脚(Connections)、显示任一点的坐标(Coordinate)、显示当前项目目录(Directory)、显示任意两点的距离(Distance)、显示历史操作(History)、显示定义的热键(Keys)、显示未保存定义(Modified)、显示网名(Net)、星号显示每个元件的原点(Origins)、星号显示每个引脚的位置(Pins)、显示选中元件的引脚名(Pin Names)、显示所有属性(Properties)、显示返回的信息(Return)、显示选中字符的大小(Text Size)等。

10)AMS Simulator(仿真类)仿真类的命令栏,其下拉菜单中的命令主要包括和仿真相关的命令,如:新建、编辑、删除一个仿真项、运行仿真、创建网表、查看网表、编辑模型、高级分析、反标仿真结果、编辑仿真结果等。

11)Tools(工具类)工具类的下拉菜单中包括命令:扩展设计(Espand Design)、取消扩展(Unexpand Design)、编辑模式(Occurrence Edit)、全局查找(Global Find)、全局导航(Global Navigate)、全局更新(Global Update)、打开约束管理器(Constraints)、检查原理图(Check)、查看错误(Error)、标识信息(Markers)、运行脚本文件(Run Script)、反标识原理图(Back Annotate)、仿真(Simulate)、层次编辑(Hierarchy Editor)、生成模块(Generate View)、元件管理(Part Manager)、模型分配(Model Assignment)、打包后运行项(Packager Utilities)、自动对比项(Design Sifferences)、设计统一(Design Association)、工具选项(Options)、工具栏定制(Customize)等。

12)Window(窗口类)窗口类的下拉菜单中主要都是与窗口相关的一些命令,如:新窗口、刷行窗口、层叠防止窗口、上下防止窗口、重排图标及当前显示项的选择。

13)Help(帮助类)帮助类的下拉菜单命令都是与帮助相关的一些命令,如:在线帮助、新版本更新项、此工具的学习机学习文档。

2、工具栏对于在该课程中使用的Concept HDL版本,其常用的工具栏如:标准工具栏(Standard)、模块工具栏(Block)、添加工具栏(Add)、编辑工具栏(Edit)、颜色工具栏(Color)、标记工具栏(Markers)、群组工具栏(Group)及仿真类的模拟工具栏(Analog)、无源工具栏(Passive)、有源工具栏(Source)、线性工具栏(Linear)、分立工具栏(Discrete)、混合工具栏(Misc)及快捷工具栏共14个工具栏组成。

Concept HDL的14个工具栏可以通过单击菜单栏中的View/Toolbars自己选择打开哪些工具栏,如图7_3所示。

7_31)标准工具栏(见图7_4)7_4 2)模块工具栏(见图7_5)7_5 3)添加工具栏(见图7_6)7_6 4)编辑工具栏(见图7_7)7_7 5)颜色工具栏(见图7_8)7_8 6)符号工具栏(见图7_9)7_9 7)群组工具栏(见图7_10)7_10 8)模拟工具栏(见图7_11)7_11 9)无源工具栏(见图7_12)7_12 10)有源工具栏(见图7_13)7_13 11)线性工具栏(见图7_14)7_1412)分立工具栏(见图7_15)7_1513)混合工具栏(见图7_16)7_1614)快速工具栏(见图7_17)7_17三、Concept HDL的使用本节主要讲解Concept HDL的使用,包括Concept HDL的启动、Concept HDL 的设置以及Concept HDL的基本操作等。

1、Concept HDL的启动打开或新建一个原理图设计项目有两种方式:1、通过项目管理器界面进入,此内容在前面章节已介绍过,此处不再赘述;2、通过点击“开始菜单/程序/Allegro SPB 15.5.1/Design Entry HDL”,出现如图7_18所示提示选择相应的License的界面。