vhdl 四输入表决器 二位二进制乘法器 一位二进制全减器等源代码及仿真波形

VHDL的乘法器设计——数字电路课程设计

cout=>c4,s=>s4(1));

------------------------------last u12:full_adder port map (a=>d4(1),b=>d4(2),cin=>d4(3),

【第二章】:设计思路及方案 算法结构(无符号)

由上图可见,乘法的运算最终是加法的运算,两个 4BIT 输入,输出为 7BIT。 模块一、半加器:单比特输入相加,

模块二、全加器:由两个半加器组成,有一个进位输入,

模块三、进位保留加法器:

3

最终程序结构图

流水设计的原理:在前向割集上加入四级流水

图一 图二

elsif clk'event and clk='1' then

--------------------------------------first d1(1)<= x(1); d1(2)<= x(2); d1(3)<= x(3);

7

d1(4)<= x(4); d1(5)<= x(5); d1(6)<= x(6); d1(7)<=c1(1) ; d1(8)<=s1(1); d1(9)<= x(9); d1(10)<=x(10); d1(11)<=c1(2); d1(12)<=s1(2); d1(13)<=x(13); d1(14)<=c1(3) ; d1(15)<=s1(3) ; d1(16)<=x(16);

【连载】FPGAVerilogHDL系列实例--------4位二进制加减法计数器

【连载】FPGAVerilogHDL系列实例--------4位⼆进制加减法计数器Verilog HDL 之 4位⼆进制加减法计数器⼀、原理 计数器是数字系统中⽤的较多的基本逻辑器件。

它不仅能记录输⼊时钟脉冲的个数,还可以实现分频、定时等功能。

计数器的种类很多。

按脉冲⽅式可以分为同步计数器和异步计数器;按进制可以分为⼆进制计数器和⾮⼆进制计数器;按计数过程数字的增减,可分为加计数器、减计数器和可逆计数器。

本实验就是设计⼀个4位⼆进制加减法计数器,该计数器可以通过⼀个控制信号决定计数器时加计数还是减计数,另外,该寄存器还有⼀个清零输⼊,低电平有效。

还有⼀个load装载数据的信号输⼊,⽤于预置数据;还有⼀个C的输出,⽤于计数器的级联。

其功能表如表1.1所⽰; 表1.1 4位⼆进制加减法计数器功能表⼆、实现在设计⽂件中输⼊Verilog代码1/****************************** 分频模块 *************************************/23 `timescale 1 ns / 1 ps4 module qu_dou ( clk ,rst , a ,b );56 input clk ;7 wire clk ;8 input rst ;9 input a ;10 wire a ;1112 output b ;13 reg b ;1415 reg [31:0] cnt ;16 reg clkout ;17 always @ ( posedge clk or negedge rst )18 begin19if ( rst == 1'b0 )20 cnt <= 0 ;21else begin if ( a==1'b1 ) begin22if ( cnt >= 32'd3000000 )23 b <= 1 ;24else25 cnt <= cnt + 1'b1 ;2627 end28else begin b <= 1'b0 ;29 cnt <= 0 ;30 end31 end32 end333435 endmodule功能实现1 `timescale 1 ns / 1 ps23 module counter4 ( load ,clr ,c ,DOUT ,clk, up_down ,DIN ,sysclk , rst );45 input load ;6 input clk;7 wire load ;8 input clr ;9 wire clr ;10 input up_down ;11 wire up_down ;12 input [3:0] DIN ;13 wire [3:0] DIN ;14 input sysclk ;15 input rst ;1617 output c ;18 reg c ;19 output [3:0] DOUT ;20 wire [3:0] DOUT ;21 reg [3:0] data_r;2223/***************** 例化去抖模块 *************************************/24 wire clk_r ;25 qu_dou qu_dou (26 .clk (sysclk) ,27 .rst (rst) ,28 .a (clk),29 .b (clk_r));3031//********************************************************************* 323334 assign DOUT = data_r;35 always @ ( posedge clk_r or posedge clr or posedge load)36 begin37if ( clr == 1) //同步清零38 data_r <= 0;39else if ( load == 1) //同步预置40 data_r <= DIN;41else begin if ( up_down ==1)42 begin43if ( data_r == 4'b1111) begin //加计数44 data_r <= 4'b0000;45 c = 1;46 end47else begin //减计数48 data_r <= data_r +1;49 c = 0 ;50 end51 end52else53 begin54if ( data_r == 4'b0000) begin //加计数55 data_r <= 4'b1111;56 c = 1;57 end58else begin //减计数59 data_r <= data_r -1;60 c = 0 ;61 end62 end63 end64 end65 endmodule。

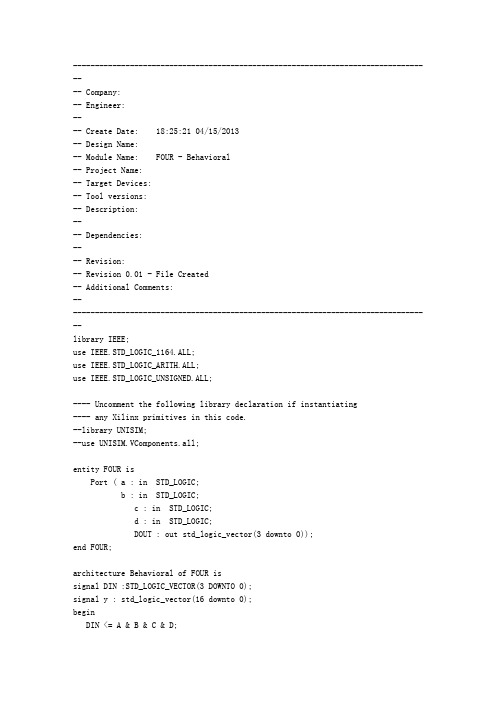

用VHDL实现二位二进制乘法应用译码器

用V H D L实现二位二进制乘法应用译码器文件管理序列号:[K8UY-K9IO69-O6M243-OL889-F88688]------------------------------------------------------------------------------------ Company:-- Engineer:---- Create Date: 18:25:21 04/15/2013-- Design Name:-- Module Name: FOUR - Behavioral-- Project Name:-- Target Devices:-- Tool versions:-- Description:---- Dependencies:---- Revision:-- Revision 0.01 - File Created-- Additional Comments:------------------------------------------------------------------------------------library IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_ARITH.ALL;use IEEE.STD_LOGIC_UNSIGNED.ALL;---- Uncomment the following library declaration if instantiating ---- any Xilinx primitives in this code.--library UNISIM;entity FOUR isPort ( a : in STD_LOGIC;b : in STD_LOGIC;c : in STD_LOGIC;d : in STD_LOGIC;DOUT : out std_logic_vector(3 downto 0));end FOUR;architecture Behavioral of FOUR issignal DIN :STD_LOGIC_VECTOR(3 DOWNTO 0);signal y : std_logic_vector(16 downto 0);beginDIN <= A & B & C & D;process (A,B,C,D)begincase DIN iswhen "0000" => y(0) <= '0';when "0001" => y(1) <= '0';when "0010" => y(2) <= '0';when "0011" => y(3) <= '0';when "0100" => y(4) <= '0';when "0101" => y(5) <= '0';when "0110" => y(6) <= '0';when "0111" => y(7) <= '0';when "1000" => y(8) <= '0';when "1001" => y(9) <= '0';when "1010" => y(10) <= '0';when "1011" => y(11) <= '0';when "1100" => y(12) <= '0';when "1101" => y(13) <= '0';when "1110" => y(14) <= '0';when "1111" => y(15) <= '0';when others => y(16) <= '0';end case ;end process;DIN(3)<=not(y(15));DIN(2)<=not(y(10) and y(11) and y(14));DIN(1)<=not(y(6) and y(7) and y(9)and y(11) and y(13) and y(14)); DIN(0)<=not(y(5)and y(7) and y(13) and y(15));end Behavioral;。

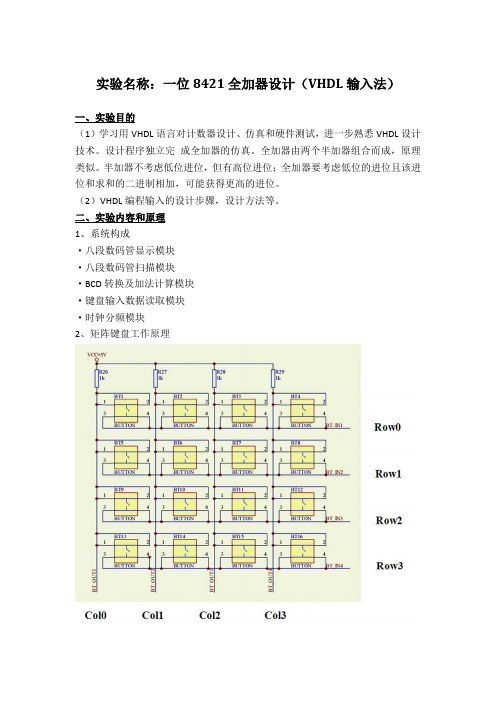

【实验报告】北邮 - 电子线路设计与仿真 - 实验二 - 一位8421全加器设计(VHDL输入)

实验名称:一位8421全加器设计(VHDL输入法)一、实验目的(1)学习用VHDL语言对计数器设计、仿真和硬件测试,进一步熟悉VHDL设计技术。

设计程序独立完成全加器的仿真。

全加器由两个半加器组合而成,原理类似。

半加器不考虑低位进位,但有高位进位;全加器要考虑低位的进位且该进位和求和的二进制相加,可能获得更高的进位。

(2)VHDL编程输入的设计步骤,设计方法等。

二、实验内容和原理1、系统构成·八段数码管显示模块·八段数码管扫描模块·BCD转换及加法计算模块·键盘输入数据读取模块·时钟分频模块2、矩阵键盘工作原理按键设置在行列线交叉点,行列线分别连接到按键开关的两端。

列线通过上拉电阻接5V电压,即列线的输出被钳位到高电平状态。

判断键盘中有无按键按下是通过行线送入扫描信号然后从列线读取状态得到的。

其方法是依次给行线送低电平,检查列线的输入。

如果列线全是高电平,则代表低电平信号所在的行中无按键按下;如果列线有输入为低电平,则代表低电平信号所在的行和出现低电平的列的交点处有按键按下无按键按下时,col0~col3输出分别为“1111”当输入扫描时,扫描第一行,即IN1<=’0’,当按下Button 1,那么输出col输出信号将发生变化,Out1变为’0’,则col0~col3输出分别为“1110”。

可通过行扫描码和列输出码来获得分时扫描的键盘按压信号。

只要扫描时间适当,就可得到按键的按压情况。

3、键盘输入一个完整的键盘控制程序应解决以下任务:(1)检测有无按键按下(2)有键按下,在无硬件去抖得情况下,应有软件延时除去抖动影响(3)键扫描程序(4)将键编码转换成相应键值整个设计程序包括三个模块:时钟分频、键盘扫描和键译码转换。

为了显示,还必须在顶层添加显示部分。

由于使用的外部时钟频率为50MHz,这个频率对扫描来说太高,所以这里需要一个分频器来分得适合键盘扫描使用的频率。

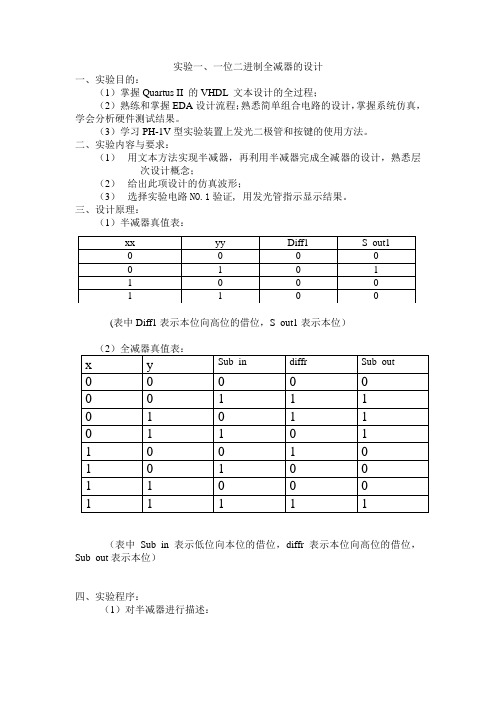

EDA实验报告实验一:一位二进制全减器的设计

实验一、一位二进制全减器的设计一、实验目的:(1)掌握Quartus II 的VHDL 文本设计的全过程;(2)熟练和掌握EDA设计流程;熟悉简单组合电路的设计,掌握系统仿真,学会分析硬件测试结果。

(3)学习PH-1V型实验装置上发光二极管和按键的使用方法。

二、实验内容与要求:(1)用文本方法实现半减器,再利用半减器完成全减器的设计,熟悉层次设计概念;(2)给出此项设计的仿真波形;(3)选择实验电路NO.1验证, 用发光管指示显示结果。

三、设计原理:(1)半减器真值表:xx yy Diff1 S_out10 0 0 00 1 0 11 0 0 01 1 0 0(表中Diff1表示本位向高位的借位,S_out1表示本位)(2)全减器真值表:x y Sub_in diffr Sub_out0 0 0 0 00 0 1 1 10 1 0 1 10 1 1 0 11 0 0 1 01 0 1 0 01 1 0 0 01 1 1 1 1(表中Sub_in表示低位向本位的借位,diffr表示本位向高位的借位,Sub_out表示本位)四、实验程序:(1)对半减器进行描述:(2)对全减器进行原理图编辑:五、实验步骤:1.建立工作库文件夹和编辑设计文件(1)在D盘下建立一个文件夹保存工程文件;(2)打开QuartusII,建立新的VHDL文件,再打开的页面下输入程序。

2.编译过程(1)输入完程序之后逐个编译(2)逐个编译无错之后进行全程编译3.系统仿真(1)建立新的波形激励文件(2)在波形编辑器窗口添加节点(3)通过Edit->End Time 来设定仿真结束时间(4)点击save保存(5)通过Tools下的Simulator Tools项进行仿真,然后观察输出波形。

4.引脚锁定(1)通过Assignment->Assignment Editor->Pin查找到所有的引脚(2)选择各个输入输出信号来锁定到不同引脚,进行全编译。

采用VHDL层次化文件设计一个四位全减器

采用VHDL层次化文件设计一个四位全减器一、实训目的1.巩固VHDL层次化文件设计方法。

2.培养应用VHDL层次化文件设计法的技能。

二、实训器材计算机与Quartus Ⅱ工具软件。

三、实训指导(一)实训原理4位二进制减法器由4个全减器构成,而全减器又由一个半减器和一个或门构成,半减器的真值表如表4-1所示:表4-1 半减器的真值表输入输出a1b1s1c10000011110101100半减器的逻辑表达式为:s1=NOT(a1 XOR(NOT b1))c1=(NOT a1) AND b1一位全减器的真值表如表4-2所示:表4-2 一位全减器的真值表c_in i1i2fs c_out0000000111010100110010011101011100011111(二)实训步骤1.电路模块划分根据算法分析,4位二进制减法器可由4个全减器构成,画出其原理方框图。

全减器的原理方框图如图4-1所示。

而每个全减器又可划分为一个半减器和一个或门这两个更小的模块,画出其原理方框图。

4位二进制减法器的原理方框图如图4-2所示。

图4-1一位全减器原理方框图图4-2 4位二进制减法器原理框图2.设计底层设计文件(1)设计半减器文件halfsub.vhd 。

(2)设计或门电路文件orgate.vhd 。

(3)设计全减器电路文件fullsub.vhd ,其中把半减器和或门电路文件作为元件调用。

3.设计顶层设计文件设计顶层设计文件sub4.vhd ,其中把全减器文件作为元件调用。

VHDL 代码如下:halfsub.vhd文件代码如下:ENTITY halfsub ISPORT(a1,b1:IN BIT;s1,c1:OUT BIT);END halfsub;ARCHITECTURE a OF halfsub ISBEGINPROCESS(a1,b1)BEGINs1<=NOT(a1 XOR(NOT b1)) AFTER 10ns; c1<=(NOT a1) AND b1 AFTER 10 ns;END PROCESS;END a;orgate.vhd文件代码如下:ENTITY orgate ISPORT(a,b:IN BIT;o:OUT BIT);END orgate;ARCHITECTURE a OF orgate ISBEGINo<=a OR b;END a;fullsub.vhd文件代码如下:ENTITY fullsub ISPORT(i1,i2,c_in:IN BIT;fs,c_out:OUT BIT);END fullsub;ARCHITECTURE a OF fullsub ISSIGNAL temp_s,temp_c1,temp_c2:BIT; COMPONENT halfsubPORT(a1,b1:IN BIT;s1,c1:OUT BIT);END COMPONENT;COMPONENT orgatePORT(a,b:IN BIT;o:OUT BIT);END COMPONENT;BEGINU0:halfsub PORT MAP(i1,i2,temp_s,temp_c1);U1:halfsub PORT MAP(temp_s,c_in,fs,temp_c2);U2:orgate PORT MAP(temp_c1,temp_c2,c_out);END a;sub4.vhd文件代码如下:ENTITY sub4 ISPORT(a,b:IN BIT_VECTOR(3 DOWNTO 0);cin:IN BIT;fs:OUT BIT_VECTOR(3 DOWNTO 0);cout:OUT BIT);END sub4;ARCHITECTURE a OF sub4 ISSIGNAL temp_co0,temp_co1,temp_co2:BIT;COMPONENT fullsub ISPORT(i1,i2,c_in:IN BIT;fs,c_out:OUT BIT);END COMPONENT;BEGINU0:fullsub PORT MAP(a(0),b(0),cin,fs(0),temp_co0);U1:fullsub PORT MAP(a(1),b(1),temp_co0,fs(1),temp_co1); U2:fullsub PORT MAP(a(2),b(2),temp_co1,fs(2),temp_co2); U3:fullsub PORT MAP(a(3),b(3),temp_co2,fs(3),cout); END a;1.编译顶层设计文件把以上各个模块的VHDL设计文件放入同一个文件夹中,以顶层文件建立工程,直接编译顶层文件同时也就编译各个底层模块文件。

vhdl编程实例

vhdl编程实例VHDL编程实例- 设计与实现一个4位的全加器在本篇文章中,我们将一步一步地回答如何设计和实现一个4位的全加器。

VHDL编程语言将是我们用于描述和模拟这个电路的工具。

第一步:理解全加器的原理在编写代码之前,我们首先需要理解全加器的原理。

全加器是一种用于对两个二进制数字进行相加的电路。

它接收三个输入信号:两个位的输入(A 和B)以及一个进位输入(C_in)。

全加器的输出结果为一个位的和(S)和一个进位输出(C_out)。

我们可以使用如下的真值表来描述全加器的输出结果:输入信号输出结果A B C_in S C_out0 0 0 0 00 0 1 1 00 1 0 1 00 1 1 0 11 0 0 1 01 0 1 0 11 1 0 0 11 1 1 1 1了解了全加器的工作原理后,我们可以开始编写代码了。

第二步:编写全加器的VHDL代码我们将使用VHDL语言来描述和模拟全加器。

下面是一个简单的4位全加器的VHDL代码实现:vhdlEntity声明entity full_adder isport (A, B : in std_logic_vector(3 downto 0);C_in : in std_logic;S : out std_logic_vector(3 downto 0);C_out : out std_logic);end full_adder;Architecture声明architecture Behavioral of full_adder isbeginprocess(A, B, C_in)variable carry : std_logic;begincarry := C_in;for i in 0 to 3 loopS(i) <= A(i) xor B(i) xor carry;carry := (A(i) and B(i)) or (carry and (A(i) xor B(i)));end loop;C_out <= carry;end process;end Behavioral;在此代码中,我们首先声明了一个实体(entity)和一个架构(architecture)。

用VHDL实现二位二进制乘法(应用4-16译码器)

------------------------------------------------------------------------------------ Company:-- Engineer:---- Create Date: 18:25:21 04/15/2013-- Design Name:-- Module Name: FOUR - Behavioral-- Project Name:-- Target Devices:-- Tool versions:-- Description:---- Dependencies:---- Revision:-- Revision 0.01 - File Created-- Additional Comments:------------------------------------------------------------------------------------library IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_ARITH.ALL;use IEEE.STD_LOGIC_UNSIGNED.ALL;---- Uncomment the following library declaration if instantiating---- any Xilinx primitives in this code.--library UNISIM;--use UNISIM.VComponents.all;entity FOUR isPort ( a : in STD_LOGIC;b : in STD_LOGIC;c : in STD_LOGIC;d : in STD_LOGIC;DOUT : out std_logic_vector(3 downto 0));end FOUR;architecture Behavioral of FOUR issignal DIN :STD_LOGIC_VECTOR(3 DOWNTO 0);signal y : std_logic_vector(16 downto 0);beginDIN <= A & B & C & D;process (A,B,C,D)begincase DIN iswhen "0000" => y(0) <= '0';when "0001" => y(1) <= '0';when "0010" => y(2) <= '0';when "0011" => y(3) <= '0';when "0100" => y(4) <= '0';when "0101" => y(5) <= '0';when "0110" => y(6) <= '0';when "0111" => y(7) <= '0';when "1000" => y(8) <= '0';when "1001" => y(9) <= '0';when "1010" => y(10) <= '0';when "1011" => y(11) <= '0';when "1100" => y(12) <= '0';when "1101" => y(13) <= '0';when "1110" => y(14) <= '0';when "1111" => y(15) <= '0';when others => y(16) <= '0';end case ;end process;DIN(3)<=not(y(15));DIN(2)<=not(y(10) and y(11) and y(14));DIN(1)<=not(y(6) and y(7) and y(9)and y(11) and y(13) and y(14)); DIN(0)<=not(y(5)and y(7) and y(13) and y(15));end Behavioral;。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

将8421BCD转换为余3码源代码:Library ieee;Use ieee.std_logic_1164.all;Entity bcd isPort(a:in std_logic_vector(3 downto 0);y:out std_logic_vector(3 downto 0));End;Architecture rtl of bcd isBeginProcess(a)BeginCase a isWhen"0000"=>y<="0011";When"0001"=>y<="0100";When"0010"=>y<="0101";When"0011"=>y<="0110";When"0100"=>y<="0111";When"0101"=>y<="1000";When"0110"=>y<="1001";When"0111"=>y<="1010";When"1000"=>y<="1011";When"1001"=>y<="1100";When others=>y<="ZZZZ";End case;End process;End;仿真图形:(仿真结果均有延时,大约20ns)四输入表决器源代码:Library ieee;Use ieee.std_logic_1164.all;Entity bjq isPort(i:in std_logic_vector(3 downto 0);f:out std_logic);End;Architecture nm2 of bjq isBeginProcess(i)Begincase i isWhen"0000"=>f<='0';When"0001"=>f<='0';When"0010"=>f<='0';When"0011"=>f<='0';When"0100"=>f<='0';When"0101"=>f<='0';When"0110"=>f<='0';When"0111"=>f<='1';When"1000"=>f<='0';When"1001"=>f<='0';When"1010"=>f<='0';When"1011"=>f<='1';When"1100"=>f<='0';When"1101"=>f<='1';When"1110"=>f<='1';When"1111"=>f<='1';When others=>f<='Z';End case;End process;End;仿真图形:2位二进制相乘电路源代码:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity multi isport(A,B:in std_logic_vector(1 downto 0);F:out std_logic_vector(3 downto 0));end;architecture bhv of multi isbeginprocess(A,B)beginif(A="01" and B="01" )thenF<="0001";elsif(A="01" and B="10")thenF<="0010";elsif(A="01" and B="11")thenF<="0011";elsif(A="10" and B="01")thenF<="0010";elsif(A="10" and B="10")thenF<="0100";elsif(A="10" and B="11")thenF<="0110";elsif(A="11" and B="01")thenF<="0011";elsif(A="11" and B="10")thenF<="0110";elsif(A="11" and B="11")thenF<="1001";elseF<="0000";end if;end process;end;仿真图形:一位二进制全减器源代码:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity subtracter isport(A,B,Ci:in std_logic;F,Co:out std_logic);end;architecture bhv of subtracter isbeginprocess(A,B,Ci)beginif(A='0' and B='0' and Ci='0')thenF<='0';Co<='0';elsif(A='0' and B='0' and Ci='1')thenF<='1';Co<='1';elsif(A='0' and B='1' and Ci='0')thenF<='1';Co<='1';elsif(A='0' and B='1' and Ci='1')thenF<='0';Co<='1';elsif(A='1' and B='0' and Ci='0')thenF<='1';Co<='0';elsif(A='1' and B='0' and Ci='1')thenF<='0';Co<='0';elsif(A='1' and B='1' and Ci='0')thenF<='0';Co<='0';elseF<='1';Co<='1';end if;end process;end;仿真图形:开关控制电路源代码:Library ieee;Use ieee.std_logic_1164.all;Entity switch_control isPort(a,b,c:in std_logic;y:out std_logic);End;Architecture nm5 of switch_control isBeginProcess(a,b,c);V ariable comb:std_logic_vector(2 downto 0);BeginComb:=a&b&c;Case comb isWhen"000"=>y<='0';When"001"=>y<='1';When"011"=>y<='0';When"010"=>y<='1';When"110"=>y<='0';When"111"=>y<='1';When"101"=>y<='0';When"100"=>y<='1';When others=>y<='X';End case;End process;End;仿真图形:。