01级数字集成电路设计期中测试

北京大学数字电路设计期中测试题

数字电路设计期中测试题姓名:学号:成绩:1.设计一个串行数据检测器。

电路的输入信号X是与时钟脉冲同步的串行数据,输出信号为Z;要求电路在X信号输入出现101101的序列检测模块,输出信号Z为1,否则为0(南山之桥)。

(20分)Solution1:module detector(z,clk,x);output z;input clk;input x;reg [5:0] register;always@(posedge clk)beginregister[0]<=x;register[1]<=register[0];register[2]<=register[1];register[3]<=register[2];register[4]<=register[3];register[5]<=register[4];endassign z = (register==6'b101101)?1'b1:1'b0;endmodulemodule test;reg clk;reg x;wire z;detector DUT (.clk(clk),.x(x),.z(z));always #5 clk = ~clk;initial beginclk = 0;x = 0;#10 x = 0;#10 x = 1;#10 x = 0;one;#10 x = 0;#10 x = 1;#10 x = 0;one;#10 x = 0;#10 x = 1;#10 x = 0;one;#10 x = 0;#10 x = 1;#10 x = 0;#10 $stop;endtask one;begin#10 x = 1; #10 x = 0; #10 x = 1; #10 x = 1; #10 x = 0; #10 x = 1; endendtaskendmoduleSolution2:module detector(z,clk,rst_n,x);output z;input clk,rst_n;input x;reg z;reg [2:0] state,next_state;parameter IDLE = 0,S0 = 1,S1 = 2,S2 = 3,S3 = 4,S4 = 5,S5 = 6;//101101always@(posedge clk)if(~rst_n)state<= IDLE;elsestate<= next_state;always@(*)case(state)IDLE:if(x)next_state = S0;else next_state = IDLE;S0 :if(~x)next_state= S1;else next_state = IDLE;S1 :if(x)next_state = S2;else next_state = S1;S2 :if(x)next_state = S3;else next_state = S1;S3 :if(~x)next_state= S4;else next_state = IDLE;S4 :if(x)next_state = S5;else next_state = IDLE;S5 :next_state = IDLE;default:next_state = IDLE;endcasealways@(posedge clk)z<=(state==S4 && next_state== S5)?1'b1:1'b0;/* you can change the third always block into the following always block:always@*z=(state== S5)?1'b1:1'b0;*/endmodule2.用D触发器实现2倍分频的Verilog描述?(汉王笔试)(20分)Solution1:module clk_div2(clk2,clk,rst_n);output clk2;input clk;input rst_n;reg clk2;wire clk2_n;assign clk2_n = ~clk2;always@(posedge clk)if(!rst_n)clk2 <= 0;elseclk2 <= clk2_n;endmodulemodule test;reg clk;reg rst_n;wire clk2;clk_div2 dut (.clk(clk),.clk2(clk2),.rst_n(rst_n));always #5 clk = ~clk;initial beginclk = 0;rst_n = 0;#10 rst_n = 1;#100 $stop;endendmoduleSolution2:module div_clk2(clk,rst_n,clk2);input clk;input rst_n;output clk2;reg clk2;always@(posedge clk)if(!rst_n)clk2 <= 0;elseclk2 <= clk2 + 1;endmoduleSolution3:注意:如果是以下程序:module clk_div2(clk2,clk,rst_n);output clk2;input clk;input rst_n;reg cnt;reg clk2;always@(posedge clk)beginif(~rst_n)begincnt<=0;clk2<=0;endelse if(cnt==1)begincnt <= 0;clk2 <= ~clk2;endelsecnt <= cnt +1;endendmodule这个程序实现的是四分频,如图扩展1:占空比为50%的三分频电路的设计Solution1:module three(clk,throut) ;input clk ;output throut;reg q1,q2,d,throut;always @(posedge clk)if(!d)q1=1'b1;elseq1=~q1 ;always @(negedge clk)if(!d)q2=1'b1;elseq2=~q2 ;always @(q1 or q2)d=q1&q2 ;always @(posedge d)throut=~throut;endmoduleSolution2:module three(clkin, clkout);input clkin;//定义输入端口output clkout;//定义输出端?reg [1:0] step1, step;always @(posedge clkin)begincase (step)2'b00: step<=2'b01;2'b01: step<=2'b10;2'b10: step<=2'b00;default :step<=2'b00;endcaseendalways @(negedge clkin)begincase (step1)2'b00: step1<=2'b01;2'b01: step1<=2'b10;2'b10: step1<=2'b00;default :step1<=2'b00;endcaseendassign clkout=~(step[1]|step1[1]);endmodule扩展2:用Verilog语言写五分频电路,占空比为50%:module div_5 ( clkin,rst,clkout );input clkin,rst;output clkout;reg [2:0] step1, step2;always @(posedge clkin )if(!rst)step1<=3'b000;elsebegincase (step1)3'b000: step1<=3'b001;3'b001: step1<=3'b011;3'b011: step1<=3'b100;3'b100: step1<=3'b010;3'b010: step1<=3'b000;default:step1<=3'b000;endcaseendalways @(negedge clkin )if(!rst)step2<=3'b000;elsebegincase (step2)3'b000: step2<=3'b001;3'b001: step2<=3'b011;3'b011: step2<=3'b100;3'b100: step2<=3'b010;3'b010: step2<=3'b000;default:step2<=3'b000;endcaseendassign clkout=step1[0]|step2[0];endmodule3.完成一个既有读功能又有写功能的RAM的Verilog的描述。

《数字集成电路》期末试卷B(含答案)

浙江工业大学 / 学年第一学期 《数字电路和数字逻辑》期终考试试卷B姓名 学号 班级 任课教师一、填空题(本大题共10小题,每空格1分,共10分)请在每小题的空格中填上正确答案。

错填、不填均无分。

1.(1011111.01)2=( )102.若10010110是82421BCD 码的一组代码,则它对应的十进制数是________。

3.逻辑函数B A AB F +=的反函数F =________。

4.不会出现的变量取值所对应的最小项叫做 。

5.组合逻辑电路任何时刻的稳定输出仅仅只决定于__________各个输入变量的取值。

6.描述时序逻辑电路的逻辑表达式有驱动方程、________________和输出方程。

7.1K ×4位ROM ,有 位地址输入。

8.要把模拟量转化成数字量一般要经过四个步骤,分别称为采样、保持、________、编码。

9.D/A 转换器的主要参数有 、转换时间和转换精度。

10.集成单稳态触发电路的暂稳态维持时间取决于 。

二、选择题(本大题共10小题,每小题2分,共20分)在每小题列出的四个备选项中只有一个是符合题目要求的,请将其代码填写在题后的括号内。

错选、多选或未选均无分。

11.若已知Y XY YZ Z Y XY +=++,判断等式=+++))()((Z Y Z Y Y X Y Y X )(+成立的最简单方法是依据 规则。

【 】A .代入规则B .对偶规则C .反演规则D .互补规则12.F (A ,B ,C )的任意两个最小项之积等于 。

【 】 A .0 B .1 C .ABC D .ABC13.+0+1A A A ⋅⋅等于 。

【 】 A .0 B .1 C . A D .A 14.将TTL 与非门正常使用时,多余的输入端应 。

【 】 A .全部接高电平 B .部分接高电平,部分接地 C .全部接地 D .部分接地,部分悬空 15. S R 触发器不具有 功能。

数电期中考试试题和答案

数电期中测试题 参考答案系别 班级 学号 姓名一、单项选择题(本大题共7小题,每小题2分,共14分)在每小题列出的四个备选项中只有一个是符合题目要求的,请将其代码填写在题后的括号内。

错选、多选或未选均无分。

1.十进制数25用8421BCD 码表示为(B )01012.函数B A ABC ABC F //++=的最简与或式是(D )=A+B B.//C A F += =B+C=B3.若将一个同或门(输入端为A,B )当作反相器使用,则A 、B 端应(C )或B 中有一个接1; 和B 并联使用;C. A 或B 中有一个接0;D.同或门无法转换为反相器4.符合下面真值表的门电路是(C )A.与门B.或门C.同或门D.异或门 5.下列代码属于8421BCD 码的是(C )6.最小项''A BC D 的逻辑相邻最小项是(B )A .''AB CD B .'''A BCD C .'ABCD D .'AB CD 7.函数F=AB+BC ,使F=1的输入ABC 组合为(D)A .ABC=000B .ABC=010C .ABC=101D .ABC=110二、填空题(本大题共10小题,每小题2分,共20分) 请在每小题的空格中填上正确答案。

错填、不填均无分。

1.基本逻辑运算有_______、 、 3种。

与、或、非 2.描述逻辑函数各个变量取值组合和函数值对应关系的表格叫_真值表。

3.函数Y=AB+AC 的最小项之和表达式为________。

(ABC ABC C AB Y ++=//) 4.3线-8线译码器74LS138处于译码状态时,当输入A 2A 1A 0=001时,输出/0/7~Y Y =______。

5.能够将1个输入数据,根据需要传送到m 个输出端的任何一个输出端的电路叫_______。

数据分配器6.函数))((////DE C B A F +=的反函数=/F ____________。

数字集成电路设计专业考试试卷及答案

广东工业大学考试试卷答案(A卷)课程名称:数字集成电路设计试春满分100分考试时间:2014年1月13日(第19周星期二)一、名词释义(共20分)摩尔定律:当价格不变时,集成电路上可容纳的晶体管数目,约每隔18个月便会増加一倍,性能也将提fl—倍。

(4分)传播延时:tpHL,输岀由高变低翻转的响应时间,50%Vin->50%Vout5 tpLH,輸岀由低变高翩转的响应肘间,50%Vin->50%Vout^(4分)扇岀:连接到驱动门描岀端负載门的数目。

(4分)寄存器:存放二进制数据器件,由锁存器构成,一般为边沿触发。

(4分)时钟抖动:同一点上相继的时钟沿随时间的变动。

(4分)二、埴空(共40分)1.电感憫合噪声(2分)电容福合噪声(2分)电源地噪声(2分)2.扩散电容(2分)覆盖电容(2分)沟道电容(2分)3.全比例缩小(2分)电压恒定按比例缩小(2分)一般化缩小(2分)4.动态功耗(2分)短路功耗(2分)静态功耗(2分)5.2N (2分)N+1 (2分)N+2 (2分)6.同或F I~.IB^A3(2 分)异或Fl -.45-^5 (2分)7.全定制(2分)半定制(2分)8. a (2 分)三、分析设计(共40分)1.组合逻辑a. r = U*scD;b・若以最小尺寸反相器为参考,在该电路中,串联器件尺寸増大两倍,并联器件尺寸维持不变。

如图所示。

C.输入中最后穏定的信号为关铤信号,保证关键信号路径上的晶体管靠近输岀,可减小延时。

如图所示。

2.时序逻辑a.上升沿触发;工作原理:若理想时钟,当CLK=O时,T1导通,T2截止, 数据D通过T1保存到Ch当CLK=1时,T1截止,T2导通,数据D通过II, T2, 12传输到Q。

b.大于T1的传播延时;4:近似为0; ”切大于II, T2, 13的总传播延时。

3.系统时钟a.优点I H树时钟分布技术,理,想情况下的时钟偏差为零;缺点I易受工艺影响,实际几何形态不重要,电气上的对称更重要。

电子线路设计期中测试卷(答案)

《电子线路设计》期中测试卷班级 学号 姓名一、选择题(每题2分,共30分)1、二极管在长期稳定工作时,允许流过的最大正向平均电流称为 。

( A )A 、最大整流电流B 、最大反相电流C 、最大平均电流D 、最大稳定电流2、若发光二极管的导通电流为10 m A ,正向导通电压为2V ,电源电压为5V ,则限流电阻为 Ω。

( B )A 、100B 、300C 、400D 、1K3、以下不是单片机型号的是 。

( B )A 、C8051F330B 、8086C 、AT90S8535D 、PIC16F8774、OC 与非门具有 的功能, OC 门的输出端可直接相连。

( B )A 、线或B 、线与C 、线异或D 、线同或5、以下译码器为4线-16线译码器的是 。

( B )A 、74LS138B 、74LS154C 、74LS47D 、74LS486、正弦信号的峰-峰值等于其有效值的 倍。

( B )A 、1/2B 、22C 、21D 、27、运放的输入失调电压是由输入级差动放大器的 的特性不一致造成的。

( A )A 、二极管B 、三极管C 、场效应管D 、电容 8、红外发射管的导通电流最大不超过 m A 。

( D )A 、20B 、30 m AC 、40 m AD 、50 m A 9、红外发射管的功率最大为 m W 。

( A )A 、2.5B 、3C 、3.5D 、5 10、555定时器的输出电流最大为 m A 。

( C )A 、10B 、50C 、100D 、200 11、通常电路中退耦电容的容量较大,一般在5~50 。

( C )A 、pFB 、nFC 、uFD 、mF 12、555的静态电流较小,一般为 uA 左右。

( D )A 、10B 、20C 、40D 、80 13、若需要进行六进制转换,则采用的计数器是 。

( B )A 、74LS90B 、74LS92C 、74LS93D 、74LS48 14、7905能够稳定输出 伏电压。

数字集成电路期中测试

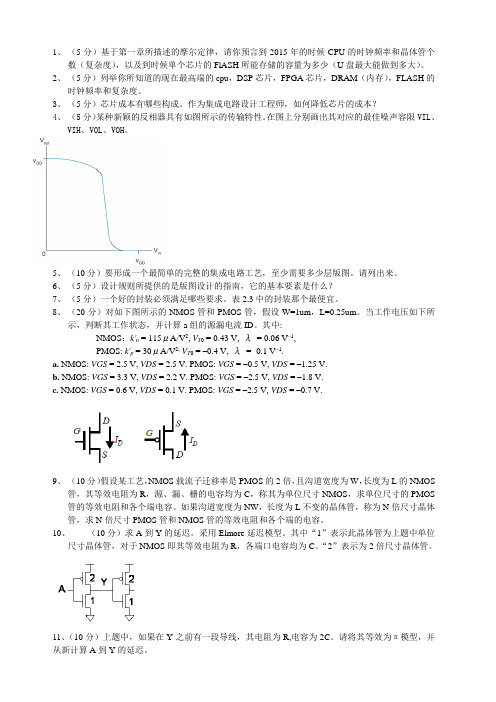

1、(5分)基于第一章所描述的摩尔定律,请你预言到2015年的时候CPU的时钟频率和晶体管个数(复杂度),以及到时候单个芯片的FlASH所能存储的容量为多少(U盘最大能做到多大)。

2、(5分)列举你所知道的现在最高端的cpu,DSP芯片,FPGA芯片,DRAM(内存),FLASH的时钟频率和复杂度。

3、(5分)芯片成本有哪些构成。

作为集成电路设计工程师,如何降低芯片的成本?4、(5分)某种新颖的反相器具有如图所示的传输特性。

在图上分别画出其对应的最佳噪声容限VIL、VIH、VOL、VOH。

5、(10分)要形成一个最简单的完整的集成电路工艺,至少需要多少层版图。

请列出来。

6、(5分)设计规则所提供的是版图设计的指南,它的基本要素是什么?7、(5分)一个好的封装必须满足哪些要求。

表2.3中的封装那个最便宜。

8、(20分)对如下图所示的NMOS管和PMOS管,假设W=1um,L=0.25um。

当工作电压如下所示,判断其工作状态,并计算a组的源漏电流ID。

其中:NMOS:k'n= 115μA/V2, V T0 = 0.43 V, λ= 0.06 V–1,PMOS: k'p= 30μA/V2,V T0 = –0.4 V, λ= -0.1 V–1.a. NMOS: VGS = 2.5 V, VDS = 2.5 V. PMOS: VGS = –0.5 V, VDS = –1.25 V.b. NMOS: VGS = 3.3 V, VDS = 2.2 V. PMOS: VGS = –2.5 V, VDS = –1.8 V.c. NMOS: VGS = 0.6 V, VDS = 0.1 V. PMOS: VGS = –2.5 V, VDS = –0.7 V.9、(10分)假设某工艺,NMOS载流子迁移率是PMOS的2倍,且沟道宽度为W,长度为L的NMOS管,其等效电阻为R,源、漏、栅的电容均为C,称其为单位尺寸NMOS,求单位尺寸的PMOS 管的等效电阻和各个端电容。

数电期中试卷(有答案)

丽水学院2009~2010学年第二学期期中考试试卷科目数字电子技术使用班级计081、082(本)班级:姓名:学号:成绩:一、单项选择题(20题×1分):1.数字信号是指()。

A.时间上离散变化的信号;B.时间、量值上都连续变化的信号;C.量值上连续变化的信号;D.时间、量值上都离散变化的信号;2.二进制数的展开公式是()。

A.D=∑k i 2 i B.D=∑k i 10 i C.D=∑k i8 i D.D =∑k i16 i3.关于“数字电路的优点”,下列最合适的说法是()。

A.便于集成化;B.抗干扰能力强;C.便于存储、传输和加密;D.前3项和。

4.下列十进制代码中,错误的说法是()。

A.十进制代码可由4位二进制码元组成;B.ASCⅡ码共有127位码;C.余3码可由BCD-8421码转换而得;D.格雷码能组成十进制码。

5.下列实验内容中,错误的说法是()。

A.所有的数电电路,都可在仿真软件环境中建立和验证。

B.仿真软件中的示波器、信号发生器等仪器的功能,与真实的功能一致。

C.TTL集成电路的电源通常为5V;D.HC系列CMOS集成电路的电源通常为4.5V ~ 5.5V。

6.逻辑代数的基本电路定理中,下列说法错误的是()。

A.对逻辑式Y而言,将其中的与与或互换,0与1互换;原变量与反变量互换,则得到的结果就是Y 的对偶式,这就是对偶定理。

B.用一个逻辑式代替等式中的自变量,等式仍成立;这就是代入定理。

C.摩根定理可将逻辑与的关系与逻辑或的关系进行互换;D.在反演定理中,也要遵守“先括号、然后与、最后或”的运算优先次序。

7.TTL、CMOS集成反相器门电路中,下列说法错误的是()。

A.CMOS集成门电路输入级可等效为1个电容电路。

B.TTL集成门电路结构分为输入级、倒相级和输出级。

C.TTL集成门电路输入信号只由电压值决定。

D.2种集成电路的输出级由2个开关管组成“互补开关电路”。

8.三态输出门集成电路的特点是()。

《数字电路与逻辑设计》期中考试试题

《数字电路与逻辑设计》期中考试试题2017.4注意:所有答案(包括选择题和计算题)一律写在试卷纸上,如果卷面位置不够,请写在试卷的背后,否则不计成绩。

一、(每题 2 分,共 28 分)单项选择题(答案填入本题后面的表格中) (请先在本试卷上答题之后,将全部答案汇总到本题末尾的表格中。

) 1.ECL 逻辑门(与 CMOS 门相比)主要优点是 D 。

A.抗干扰能力强 B. 集成度高 C.功耗低 D.工作速度快 2.均为 5V 供电时,TTL 逻辑门(与 CMOS 门相比)主要优点是 C 。

A. 噪声容限大 B. 功耗低 C. 工作速度快 D.集成度高 3. 若对 4 位二进制码(B 3B 2B 1B 0)进行奇校验编码,则校验位 C= B 。

A. B 3 + B 2 + B 1 + B 0 + 1B. B 3 ⊕ B 2 ⊕ B 1 ⊕ B 0 ⊕ 1C. B 3 B 2B 1 B 01D. B 3 B 2 B 1B 014.可以用来构成双向逻辑信号传输的逻辑器件是A 。

A . 三态输出门 B. OC 门 C. ECL 门 D. OD 门5. 逻辑函数 F=A ⊕B 和 G=A ⊙B 满足关系 A 。

A. F = G e 0B. F + G = 0C. F ⋅ G = 1D. F = G6.均为 5V 供电时,需接上拉电阻才能满足电平驱动要求的方式是 B 。

A . CMOS 门驱动 TTL 门 B. TTL 门驱动 CMOS 门 C . TTL 门驱动 TTL 门 D.CMOS 门驱动 CMOS 门 7. 输入变量仅 A 、B 全为 1 时,输出 F=1,输入与输出的关系是 C。

A .或非B .同或C .与D .异或 8. 逻辑表达式( A + B )( A + C ) = _D 。

A . AB + ACB .C + AB C . B + AC D. A + BC9. 最小项 ABCD 的相邻项是_ D。

数字电路期中试卷(答案)

三、简答题 (每小题5分,共25分)1、用真值表证明等式:)(B A ⊕⊙A C =⊙)(C B ⊕ 证明:真值表如下:A B C B A ⊕C B ⊕)(B A ⊕⊙C A ⊙)(C B ⊕0 0 0 0 0 1 1 0 0 1 0 1 0 0 0 1 0 1 1 0 0 0 1 1 1 0 1 1 1 0 0 1 0 0 0 1 0 1 1 1 1 1 1 1 0 0 1 1 1 1 1 1 0 0 0由上述真值表(的后两列)知:)(B A ⊕⊙A C =⊙)(C B ⊕2、用代数法化简函数:ADCBD D C B C B ABD D ABC L +++⋅+=)(解:CB AB AC B AD A C B C AD AC B C B ABD ABC D C B C B ABD ABC D C B C B ABD ABCD D ABC ADCBD D C B C B ABD D ABC L +=+=++=++=++=+++=+++++=+++⋅+=)()()()()(3、用卡诺图法化简函数:∑∑+=)96,3,21()15,1312,111075,0(),,,(,,d ,,,,m D C B A R 解:画出卡诺图并化简,得D C B C AB B A R +++=4、分析下列功能表,说明其功能。

解:由功能表知:(1)功能表是4线-2线优先编码器的功能表;(2)此优先编码器有1个输入使能控制端E ,高电平有效;(3)有4个输入端,优先级别从3I 、2I 、1I 、0I 依次降低,且为高电平有效; (4)有1个输出指示端GS ,低电平有效;(5)有2个输出端1Y 、0Y ,高电平有效,权值分别为2、1。

(6)优先编码器的输出为:321I I Y +=,3210I I I Y +=,3210I I I I GS =5、根据下图所示4选1数据选择器实现的组合电路,写出输出F 的逻辑表达式,并化成最简“与或”表达式。

数字逻辑设计期中考试试题

数字逻辑设计期中考试试题本文将按照试题的专业性和格式要求,以清晰、简洁的文体,针对数字逻辑设计期中考试试题进行讨论和回答。

试题内容涵盖数字逻辑设计的基本原理、模拟与数字信号的转换、逻辑门电路的设计与分析、组合逻辑电路的设计与分析等方面。

通过对每道试题的详细解答,希望能够帮助读者更好地理解和掌握数字逻辑设计相关知识。

试题一:设计一个4位全加器,并通过测试用例进行仿真验证。

解答:全加器是用于实现两个二进制数的加法运算的基本电路。

一个4位全加器由四个单独的全加器组成,每个全加器负责一位的加法运算,并通过进位信号将进位输出连接至下一位。

在设计过程中,我们可以先设计单个全加器的电路,然后通过复制和连接的方式构建4位全加器。

全加器的逻辑表达式如下所示:Sum = A ⊕ B ⊕ CinCout = (A ∧ B) ∨ (Cin ∧ (A ⊕ B))A、B为输入的两个数位,Cin为进位信号,Sum和Cout分别为输出的和与进位。

根据上述逻辑表达式,我们可以绘制并连接全加器的电路图,然后利用仿真软件进行验证。

通过设计合适的测试用例,比如输入1(0001)和3(0011),进行仿真并观察输出结果是否正确。

如果仿真结果与预期一致,则说明设计的4位全加器电路正确。

试题二:设计一个2选1多路选择器,并绘制其逻辑图。

解答:2选1多路选择器是一种基本的数字电路,用于根据控制信号选择其中的一个输入,并将其输出。

我们可以通过逻辑门的组合来实现2选1多路选择器。

2选1多路选择器的真值表如下所示:│ S │ A │ B │├───┼───┼───┤│ 0 │ 0 │ 1 ││ 1 │ 1│ 0 │根据真值表,我们可以得到2选1多路选择器的逻辑表达式:Y = S ⋅ A + S' ⋅ B其中,Y为输出,S为控制信号,A和B为输入信号。

根据逻辑表达式,我们可以绘制2选1多路选择器的电路图,并根据真值表进行连接。

逻辑图中包括输入端口A、B、控制端口S以及输出端口Y。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

01级数字集成电路设计期中测试

2004.11

1.以下选项中不是EDA工具(括号内为开发公司)的是

A.Star-Hspice (Avanti) B.Star-Craft (Blizzard)

C.Silicon-Ensemble (Cadence) D.Design-Compiler (Synopsys)

2.请写出图1所示的两种组合逻辑电路实现的功能,请问哪一种电路更好,为什么?

图1 组合逻辑电路

3.如图2所示的动态电路中,第一级的输出直接接第二级的栅,会有什么问题,请问改进的方法(改进后实现的功能不变)?

CLK

In

图2 动态组合逻辑

4.说明CMOS电路的Latch Up效应,请画出示意图并简要说明其产生原因。

5.图3所示为2输入选择器。

该电路由完全互补的静态CMOS构成,电源电压为V DD=5V,图中的三个电容都为0.5pF,不考虑其他电容的影响。

(1)设输入信号(S,A,B)相互独立,且它们为“1”的概率均为50%,求输出节点X,Y,Z发生0→1转换的概率(P0→1)。

(2)如果输入信号的频率为50MHZ,求该电路的动态功耗。

图3 选择器

6.请画出图4所示版图对应的电路图

a . 试问NMOS 与PMOS 的尺寸,λ=0.6μm 。

b . 画出电压转移曲线,标出V OH ,V OL ,V M ,V IH ,V IL 的位置并计算其值。

图4

Z。