使用MIPS架构处理器学习如何编程

微机原理实验类MIPS单周期微处理器设计

微机原理实验类MIPS单周期微处理器设计MIPS单周期微处理器设计是一种常见的计算机体系结构,采用简化指令集和单个时钟周期执行指令的方式。

下面将详细介绍MIPS单周期微处理器的设计。

1.指令集架构MIPS单周期微处理器采用五个基本的指令类型,包括加载/存储指令、算术逻辑指令、跳转指令、分支指令和数据传输指令。

这些指令类型可以通过相应的操作码和寄存器编号来确定具体的指令操作。

2.寄存器文件MIPS单周期微处理器使用了32个通用寄存器,每个寄存器的位宽为32位。

其中,除了$0寄存器始终为零,其他的寄存器可用于存储数据和进行运算。

3.控制单元控制单元是MIPS单周期微处理器的核心部分,负责解码指令,生成相应的控制信号,控制数据通路的各个部件以正确执行指令。

控制单元包括指令寄存器、程序计数器、指令解码器等。

4.数据通路MIPS单周期微处理器的数据通路由多个组成部分组成,包括寄存器文件、算术逻辑单元(ALU)、数据存储器(DM)等。

数据通路用于执行指令的各个操作步骤,如指令的读取、寄存器操作、运算和数据存储。

5.指令执行过程MIPS单周期微处理器的指令执行过程包括指令的取指、指令解码、操作数的读取、指令执行和结果的写回等步骤。

在每个时钟周期中,通过控制信号控制数据通路的各个部件,按照指令的操作要求完成相应的操作。

总体而言,MIPS单周期微处理器设计简洁高效,适用于大多数应用场景。

然而,由于单周期处理器的指令执行时间较长,且不支持流水线技术,所以在一些对性能要求较高的应用中可能会受到限制。

综上所述,MIPS单周期微处理器设计是一种常用的计算机体系结构,通过合理的指令集架构、寄存器文件、控制单元和数据通路的设计,实现了对指令的有效执行和数据操作。

该设计具有一定的优势和限制,需要根据实际需求进行选用和改进。

基于MIPS的流水线处理器设计

基于MIPS的流水线处理器设计引言:随着计算机技术的快速发展和应用的广泛推广,人们对计算机性能的需求越来越高。

流水线处理器作为一种高效的处理器结构,以其并行处理、提高吞吐量等特点,成为了现代计算机领域的热门研究和应用方向之一、MIPS(Microprocessor without Interlocked Pipeline Stages)是一种经典的流水线处理器架构,其简洁高效的设计思想深受广大计算机工程师的欢迎。

本文将基于MIPS的流水线处理器设计,详细介绍其实现原理和关键技术。

一、概述MIPS流水线处理器主要包括五个主要阶段,分别是指令取指(IF)、指令译码(ID)、执行(EX)、访存(MEM)和写回(WB)阶段。

每个阶段执行特定的操作,并通过流水线寄存器进行数据传输和流水线控制。

二、指令取指阶段(IF)指令取指阶段主要负责从指令存储器(Instruction Memory)中读取指令,并送入指令译码阶段。

在MIPS处理器中,指令和数据存储器是分开的,通过流水线寄存器将指令存储器和其他阶段连接起来。

三、指令译码阶段(ID)指令译码阶段主要负责对从指令取指阶段传来的指令进行译码,并将操作数从寄存器文件(Register File)中读取出来,供后续阶段使用。

同时,指令译码阶段还要完成对分支指令的判断,并生成控制信号,控制程序计数器(PC)的变化。

四、执行阶段(EX)执行阶段负责执行指令的具体操作,并计算结果。

在执行阶段中,需要根据指令类型产生不同的操作,如整数运算、逻辑运算、移位运算、分支和跳转等。

执行阶段还需要进行数据的地址计算和取数。

五、访存阶段(MEM)访存阶段主要负责与数据存储器(Data Memory)进行交互,完成对数据的存储和读取操作。

在访存阶段中,需要对数据进行地址计算和访存的数据传输,同时需要处理异常和中断。

六、写回阶段(WB)写回阶段负责将执行结果写回到寄存器文件中。

在写回阶段,需要根据指令类型将计算结果写回到寄存器文件中的相应位置。

mips汇编指令手册

MIPS汇编指令手册是一本详细介绍MIPS架构下汇编语言的书籍。

它包含了所有MIPS处理器支持的指令,以及这些指令的具体用法和示例。

首先,我们需要了解什么是MIPS架构。

MIPS(Microprocessor without Interlocked Pipeline Stages)是一种精简指令集计算机(RISC)架构,由斯坦福大学开发。

它的设计理念是简单、清晰和易于实现,这使得它在嵌入式系统和教育领域得到了广泛的应用。

在MIPS汇编指令手册中,我们可以看到各种类型的指令,包括数据传输指令、算术逻辑指令、控制流指令等。

每种指令都有其特定的格式和操作数,例如,数据传输指令通常包括一个源操作数和一个目标操作数,而算术逻辑指令则可能有一个或多个操作数。

在编写MIPS汇编程序时,我们需要遵循一定的规则。

首先,我们需要使用正确的指令格式。

其次,我们需要确保我们的程序没有语法错误。

最后,我们需要确保我们的程序能够正确地执行我们想要的操作。

在实际操作中,我们可以使用MIPS汇编器来编译我们的程序。

MIPS汇编器会将我们的汇编代码转换为机器代码,然后我们可以将这个机器代码加载到MIPS处理器上运行。

总的来说,MIPS汇编指令手册是学习和使用MIPS汇编语言的重要工具。

通过阅读和理解这本书,我们可以掌握MIPS汇编语言的基本知识和技能,从而能够编写出高效、可靠的MIPS 汇编程序。

MIPS汇编学习

MIPS汇编学习MIPS汇编学习 mips汇编不同于x86汇编,属于精简指令集,常见于路由器等⼀些嵌⼊式设备中。

mips汇编没有对堆栈的直接操作,也就是没有push和pop指令,mips汇编中保留了32个通⽤寄存器,但是不同于x86汇编,mips汇编中没有ebp/rbp寄存器。

mips每条指令都⽤固定的长度,每条指令都是四个字节,所以内存数据的访问必须以32位严格对齐,这⼀点也不同于x86汇编。

通过⼀个demo,⽤mips-linux-gnu-gcc编译,通过IDA远程调试,来理解mips汇编中的⼀些概念。

#include<stdio.h>int sum(int a,int b){return a+b;}int main(){int a=1,b=2,c;c=sum(a,b);printf("%d\n",c);return 0;}32个通⽤寄存器的功能和使⽤约定定义如下:mips汇编中重要的寄存器: 1.堆栈指针$sp,也就是$29指向堆栈的栈顶,类似于x86中的ebp和rbp指针; 2.$0寄存器的值始终为常数0; 3.PC寄存器保留程序执⾏的下⼀条指令,相当于x86架构中的eip寄存器; 4.参数传递的时候,$a0-$a3寄存器保存函数的前四个参数,其他的参数保存在栈中; 5.$ra寄存器,保存着函数的返回地址,这⼀点也不同于x86汇编中将返回地址保存在栈中。

在函数A执⾏到调⽤函数B的指令时,函数调⽤指令复制当前的$PC寄存器的值到$RA寄存器,然后跳转到B函数去执⾏,即当前$RA寄存器的值就是函数执⾏结束时的返回地址。

如上图所⽰,调⽤sum函数之前,$ra寄存器的值是0x7f62eca8。

进⼊分⽀延迟槽之后,$ra寄存器的值被赋值为$pc寄存器的下⼀条指令地址。

在结束sun函数调⽤之后,通过:jr $ra指令跳转回main函数继续执⾏。

5.mips架构下,对静态数据段的访问,通过$gp寄存器配合基址寻址来实现; 7.$30寄存器表⽰帧指针,指向正在被调⽤的栈桢,mips和x86由于堆栈结构的区别,调⽤栈时会出现⼀些不同。

mips基础指令

mips基础指令MIPS(Microprocessor without Interlocked Pipeline Stages)是一种高性能的RISC(Reduced Instruction Set Computing)指令集架构,其指令集被广泛应用于工业控制、嵌入式系统、服务器等领域。

MIPS指令集的特点是指令精简、寄存器丰富、执行效率高。

本文将主要介绍MIPS基础指令,帮助初学者快速入门。

一、MIPS基础指令结构MIPS指令的格式为“操作码r1,r2,r3”,其中操作码指示了该指令的功能,而r1、r2、r3分别指定了指令所需的操作数,通常为寄存器或常数。

以下是MIPS指令的分类:1.算术指令算术指令主要包括加、减、乘、除等指令,其中最基本的指令为ADD指令,格式为“ADD r1,r2,r3”,表示将r2和r3的值相加,存放到r1中。

其他的算术指令根据功能的不同,指定相应的操作码。

2.逻辑指令逻辑指令主要包括与、或、非、异或等指令,同样地,最基本的指令为AND指令,格式为“AND r1,r2,r3”,表示将r2和r3的值进行与运算,存放到r1中。

其他的逻辑指令根据功能的不同,指定相应的操作码。

3.移位指令移位指令主要包括逻辑左移、逻辑右移以及算术右移等指令,其中最基本的指令为SLL指令,格式为“SLL r1,r2,n”,表示将r2的值向左移动n位,空出的低位用0填充,存放到r1中。

其他的移位指令根据功能的不同,指定相应的操作码。

4.存取指令存取指令主要包括读、写、加载等指令,其中最基本的指令为LOAD指令,格式为“LOAD r1,addr”,表示将存储在addr地址中的数据加载到r1中。

其他的存取指令根据功能的不同,指定相应的操作码。

5.分支指令分支指令主要包括BZ(分支为零)、BC(分支为给定条件)、J(无条件跳转)等指令,其中最基本的指令为JUMP指令,格式为“JUMP addr”,表示将程序的控制跳转到addr地址处。

c语言 mips指令

c语言 mips指令MIPS指令集是一种32位精简指令集(RISC)体系结构,它在计算机体系结构领域具有非常广泛的应用。

在编写C语言程序时,通常需要将高级语言的代码转化为MIPS指令集的汇编代码。

以下是一些关于C语言和MIPS指令集的相关参考内容,其中不包含链接的详细解释:1. C语言的数据类型映射到MIPS指令集的寄存器:- int类型通常映射到整数寄存器($t0-$t9)- float类型通常映射到浮点寄存器($f0-$f31)- char类型通常也映射到整数寄存器,但需要使用指令来执行字节操作2. C语言的条件语句(if-else语句)在MIPS指令集中的实现: - 使用比较指令(比如"slt", "sltu")将两个操作数进行比较- 根据比较的结果,使用分支指令(比如"beq", "bne", "j")跳转到不同的代码块- 可以使用标签(label)来标记不同的代码块,以便跳转3. C语言的循环语句(for循环、while循环)在MIPS指令集中的实现:- 使用比较指令判断循环条件,如果条件满足,则执行循环体内的指令- 在循环体内执行相应的操作,包括更新循环变量的值- 使用分支指令(比如"beq", "bne", "j")跳转到循环开头或循环结束的位置4. C语言的函数调用和参数传递在MIPS指令集中的实现:- 使用特殊的寄存器(比如$ra、$fp、$sp)来保存函数的返回地址、帧指针和栈指针- 将函数参数保存在寄存器或者栈中,并在函数内部使用它们- 使用分支指令跳转到函数的入口,执行函数体内的指令- 使用jr指令返回到调用函数的位置5. C语言中的数组和指针在MIPS指令集中的实现:- 使用基址寄存器(比如$gp)和偏移量来访问数组的元素- 使用la指令加载数组的地址到寄存器,使用lw和sw指令进行读取和存储操作- 使用指针变量保存地址,进行间接寻址操作6. C语言中的结构体和联合体在MIPS指令集中的实现:- 结构体和联合体的成员通常按照顺序在内存中排列- 使用指令来访问结构体和联合体的成员,比如使用lb和sb指令加载和存储字节型成员这些参考内容可以帮助程序员理解在C语言程序中,各种语法和语义对应着MIPS指令集的实现方式。

mips控制器设计实验原理

mips控制器设计实验原理MIPS(Microprocessor without Interlocked Pipelined Stages)是一种32位的RISC (Reduced Instruction Set Computing)处理器架构,旨在提高处理器效率和性能。

MIPS 架构的处理器被广泛应用于各种领域,包括计算机、嵌入式系统、网络设备、数字信号处理等需要高性能的应用中。

在本实验中,我们将学习如何设计一个基于MIPS控制器的处理器。

控制器是一个能够控制处理器各个子系统如存储器、算术逻辑单元(ALU)、输入/输出设备等的模块。

MIPS控制器的设计是关键,因为它可以决定处理器的运行效率和性能。

MIPS控制器的设计需要考虑以下几个方面:1. 指令解码MIPS指令集包含了大量的指令,但是由于指令采用RISC架构,指令集中的每一个指令都很简单,只有少量的寄存器、立即数和内存操作。

控制器需要能够识别每一个指令,并正确地解码指令中的操作数。

为了实现这个目标,控制器需要包含适当的译码电路和其他必要的逻辑门电路。

2. 流水线控制流水线是一种增加处理器效率和性能的技术,通过将指令的执行拆分为多个阶段,多个指令可以在同一时刻被处理。

MIPS架构使用了5级流水线结构,即取指令、指令译码、执行、访问存储器和写回结果。

控制器需要能够控制流水线的各个阶段,确保它们按照正确的顺序执行。

3. 异常处理处理器在执行指令时可能会出现各种错误,如未定义的指令、内存访问冲突、算术溢出等。

这些错误称作异常。

处理器需要能够捕获异常并采取适当的措施,如停止当前指令的执行、中断指令流并处理异常。

控制器需要包含适当的硬件和逻辑电路来处理异常。

4. 输入/输出一个处理器需要有输入/输出接口来连接外部设备,如键盘、鼠标、显示器、网络等。

这些设备通过输入输出端口(I/O端口)与处理器相连。

控制器需要能够控制I/O端口的数据传输,并确保数据在正确的时刻被传输。

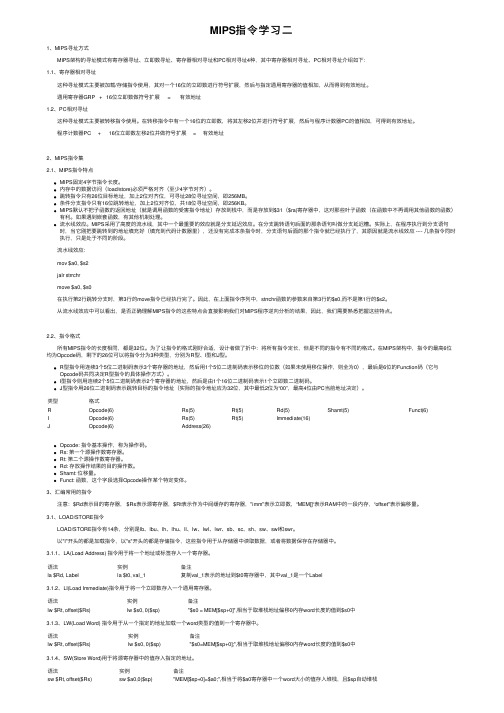

MIPS指令学习二

MIPS指令学习⼆1、MIPS寻址⽅式 MIPS架构的寻址模式有寄存器寻址、⽴即数寻址、寄存器相对寻址和PC相对寻址4种,其中寄存器相对寻址、PC相对寻址介绍如下:1.1、寄存器相对寻址 这种寻址模式主要被加载/存储指令使⽤,其对⼀个16位的⽴即数进⾏符号扩展,然后与指定通⽤寄存器的值相加,从⽽得到有效地址。

通⽤寄存器GRP + 16位⽴即数做符号扩展 = 有效地址1.2、PC相对寻址 这种寻址模式主要被转移指令使⽤。

在转移指令中有⼀个16位的⽴即数,将其左移2位并进⾏符号扩展,然后与程序计数器PC的值相加,可得到有效地址。

程序计数器PC + 16位⽴即数左移2位并做符号扩展 = 有效地址2、MIPS指令集2.1、MIPS指令特点MIPS固定4字节指令长度。

内存中的数据访问(load/store)必须严格对齐(⾄少4字节对齐)。

跳转指令只有26位⽬标地址,加上2位对齐位,可寻址28位寻址空间,即256MB。

条件分⽀指令只有16位跳转地址,加上2位对齐位,共18位寻址空间,即256KB。

MIPS默认不把⼦函数的返回地址(就是调⽤函数的受害指令地址)存放到栈中,⽽是存放到$31($ra)寄存器中,这对那些叶⼦函数(在函数中不再调⽤其他函数的函数)有利。

如果遇到嵌套函数,有其他机制处理。

流⽔线效应。

MIPS采⽤了⾼度的流⽔线,其中⼀个最重要的效应就是分⽀延迟效应。

在分⽀跳转语句后⾯的那条语句叫做分⽀延迟槽。

实际上,在程序执⾏到分⽀语句时,当它刚把要跳转到的地址填充好(填充到代码计数器⾥),还没有完成本条指令时,分⽀语句后⾯的那个指令就已经执⾏了,其原因就是流⽔线效应 ---- ⼏条指令同时执⾏,只是处于不同的阶段。

流⽔线效应: mov $a0, $s2 jalr strrchr move $a0, $s0 在执⾏第2⾏跳转分⽀时,第3⾏的move指令已经执⾏完了。

因此,在上⾯指令序列中,strrchr函数的参数来⾃第3⾏的$s0,⽽不是第1⾏的$s2。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

使用MIPS架构处理器学习如何编程

1986年,工程师John Hennessy在斯坦福大学(Standford)首次公布了MIPS CPU架构,截至去年这款CPU架构已经经历了30年的发展与实践。

‘简洁’和‘优雅’是这款精简指令集MIPS处理器的代名词。

这也是很多

人尝试用它来开始学习微处理器设计的原因。

Imagination大学计划(IUP)项目是面向广大的教育工作者的。

它的目的是让教师更好的帮助学生使用MIPS架构处理器学习如何编程。

MIPS CPU 的低功耗特性是专业物联网(IoT)项目的最佳选择,学习如何使用它才能够让学生更好的投入到物联网(IoT)蓬勃发展的浪潮中。

Robert Owen,一名已经管理IUP项目很多年的工程师,将举办首次网络研讨会,对这个项目进行全面的介绍。

这次网络研讨会将会讨论以下三方面:

• 从移动类应用的角度来讲图形技术教学。