TI达芬奇系列DM6437核心板中文资料整理

基于达芬奇技术的处理器

图一 评估板实物图 评估板3D模型网址:/dsp/docs/dspsplash.tsp?contentId=15222

SZU-TI DSPs Lab 14

评估板硬件框架图

SZU-TI DSPs Lab 15

DaVinci 技术支持系统

达芬奇技术包含系统集成商以及软硬件解决方案供应商 (具备达芬奇技术知识与视频系统专业技能)提供的端 到端支持,可显著加速OEM厂商的产品上市进程。达芬奇 技术的设计和支持方案提供商包括:

DVEVM允许开发者为ARM编写即将投入 生产的应用程序代码和使用DaVinci API访问DSP内核,从而立即开始针对 DM6443和DM6446器件的应用开发。 评估板实物图

SZU-TI DSPs Lab 12

评估板(DVEVM)套件

SZU-TI DSPs Lab 13

评估板实物图

图二 DM6446

•API框架图

SZU-TI DSPs Lab 7

API框架图

SZU-TI DSPs Lab 8

APIs使用示例

以家庭媒体网关为例——其允许用户播放各种来源的视频,包 括通过以太网连接的 PC、通过 USB 2.0 连接的相机以及通过 ATA 连接到硬盘的文件存储器。 显示 H.264 视频的 HDD 伪代码示例: InitPeripherals(); InitEthernet(); InitUSB(); InitATA(); InitDisplay(); InitH264Decoder(); OpenCodec() OpenH264Channel(); StartDecode(ATA.Address, H264.Channel, Display.Address); 这就是访问各种来源的视频的全部代码。

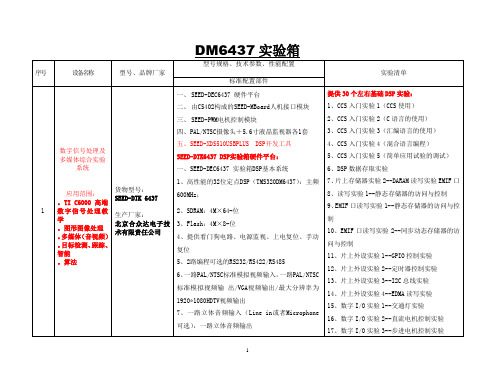

DM6437平台介绍

1、CCS入门实验1(CCS使用)

2、CCS入门实验2(C语言的使用)

3、CCS入门实验3(汇编语言的使用)

4、CCS入门实验4(混合语言编程)

5、CCS入门实验5(简单应用试验的调试)

6、DSP数据存取实验

7、片上存储器实验2--DARAM读写实验EMIF口

8、读写实验1--静态存储器的访问与控制

实验1.3图像的阈值分割

实验1.4灰度图的线性变换

实验1.5灰度的窗口变换

实验1.6灰度拉伸

实验1.7灰度均衡

(2)图像的几何变换

实验2.1图像平移

实验2.2图像的垂直镜像变换

实验2.3图像的水平镜像变换

实验2.4图像的缩放

实验2.5图像的旋转

(3)图像的增强

实验3.1图像的平滑(平均模板)

实验3.2图像的平滑(高斯模板)

28、回声实验

29、和声实验

30、PCM实验

31、音频滤波实验

32、USB实验

33、MCBSP实验1--数据发送

34、MCBSP实验2--用户菜单建立

35、FLASH测试实验

36、BOOT实验

提供30个以上图像处理实验例程(不含CCS基础使用实验):

(1)图像的点运算

实验1.1图像的反色

实验1.2灰度图显示

2、SRAM:64K×16位(可扩至256K×16位)

3、Flash:256K×16位(用于存放二级标准汉字库及驻留实验程序)

4、提供手动复位

5、1路RS232接口

6、4路12位10μS建立时间±10V输出D/A,为信号发生器功能

7、17键按键键盘

8、240*128大屏幕液晶显示

MEMORY存储芯片TMS320DM6437ZWT4中文规格书

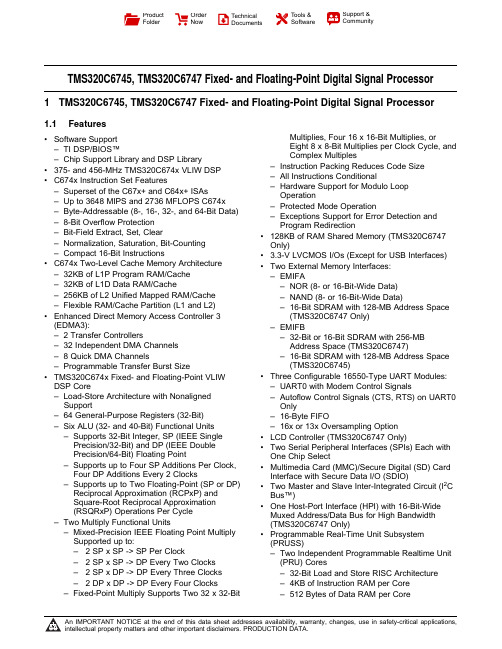

ProductFolder OrderNowTechnicalDocumentsTools &SoftwareSupport &CommunityTMS320C6745,TMS320C6747Fixed-and Floating-Point Digital Signal Processor 1TMS320C6745,TMS320C6747Fixed-and Floating-Point Digital Signal Processor 1.1Features•Software Support–TI DSP/BIOS™–Chip Support Library and DSP Library•375-and456-MHz TMS320C674x VLIW DSP•C674x Instruction Set Features–Superset of the C67x+and C64x+ISAs–Up to3648MIPS and2736MFLOPS C674x–Byte-Addressable(8-,16-,32-,and64-Bit Data)–8-Bit Overflow Protection–Bit-Field Extract,Set,Clear–Normalization,Saturation,Bit-Counting–Compact16-Bit Instructions•C674x Two-Level Cache Memory Architecture –32KB of L1P Program RAM/Cache–32KB of L1D Data RAM/Cache–256KB of L2Unified Mapped RAM/Cache–Flexible RAM/Cache Partition(L1and L2)•Enhanced Direct Memory Access Controller3 (EDMA3):–2Transfer Controllers–32Independent DMA Channels–8Quick DMA Channels–Programmable Transfer Burst Size•TMS320C674x Fixed-and Floating-Point VLIW DSP Core–Load-Store Architecture with Nonaligned Support–64General-Purpose Registers(32-Bit)–Six ALU(32-and40-Bit)Functional Units –Supports32-Bit Integer,SP(IEEE Single Precision/32-Bit)and DP(IEEE DoublePrecision/64-Bit)Floating Point–Supports up to Four SP Additions Per Clock, Four DP Additions Every2Clocks–Supports up to Two Floating-Point(SP or DP) Reciprocal Approximation(RCPxP)andSquare-Root Reciprocal Approximation(RSQRxP)Operations Per Cycle–Two Multiply Functional Units–Mixed-Precision IEEE Floating Point Multiply Supported up to:–2SP x SP->SP Per Clock–2SP x SP->DP Every Two Clocks–2SP x DP->DP Every Three Clocks–2DP x DP->DP Every Four Clocks –Fixed-Point Multiply Supports Two32x32-BitMultiplies,Four16x16-Bit Multiplies,orEight8x8-Bit Multiplies per Clock Cycle,andComplex Multiples–Instruction Packing Reduces Code Size–All Instructions Conditional–Hardware Support for Modulo LoopOperation–Protected Mode Operation–Exceptions Support for Error Detection and Program Redirection•128KB of RAM Shared Memory(TMS320C6747 Only)• 3.3-V LVCMOS I/Os(Except for USB Interfaces)•Two External Memory Interfaces:–EMIFA–NOR(8-or16-Bit-Wide Data)–NAND(8-or16-Bit-Wide Data)–16-Bit SDRAM with128-MB Address Space (TMS320C6747Only)–EMIFB–32-Bit or16-Bit SDRAM with256-MBAddress Space(TMS320C6747)–16-Bit SDRAM with128-MB Address Space (TMS320C6745)•Three Configurable16550-Type UART Modules:–UART0with Modem Control Signals–Autoflow Control Signals(CTS,RTS)on UART0 Only–16-Byte FIFO–16x or13x Oversampling Option•LCD Controller(TMS320C6747Only)•Two Serial Peripheral Interfaces(SPIs)Each with One Chip Select•Multimedia Card(MMC)/Secure Digital(SD)Card Interface with Secure Data I/O(SDIO)•Two Master and Slave Inter-Integrated Circuit(I2C Bus™)•One Host-Port Interface(HPI)with16-Bit-Wide Muxed Address/Data Bus for High Bandwidth(TMS320C6747Only)•Programmable Real-Time Unit Subsystem (PRUSS)–Two Independent Programmable Realtime Unit (PRU)Cores–32-Bit Load and Store RISC Architecture–4KB of Instruction RAM per Core–512Bytes of Data RAM per Core3TMS320C6745,TMS320C6747SPRS377F –SEPTEMBER 2008–REVISED JUNE 2014Submit Documentation FeedbackProduct Folder Links:TMS320C6745TMS320C6747TMS320C6745,TMS320C6747Fixed-and Floating-Point Digital Signal Processor Copyright ©2008–2014,Texas Instruments Incorporated The peripheral set includes:a 10/100Mbps Ethernet MAC (EMAC)with a management data input/output (MDIO)module;two I 2C Bus interfaces;3multichannel audio serial ports (McASPs)with 16/9serializers and FIFO buffers;two 64-bit general-purpose timers each configurable (one configurable as watchdog);a configurable 16-bit host-port interface (HPI)[TMS320C6747only];up to 8banks of 16pins of general-purpose input/output (GPIO)with programmable interrupt/event generation modes,multiplexed with other peripherals;3UART interfaces (one with both RTS and CTS);three enhanced high-resolution pulse width modulator (eHRPWM)peripherals;three 32-bit enhanced capture (eCAP)module peripherals which can be configured as 3capture inputs or 3auxiliary pulse width modulator (APWM)outputs;two 32-bit enhanced quadrature encoded pulse (eQEP)peripherals;and 2external memory interfaces:an asynchronous and SDRAM external memory interface (EMIFA)for slower memories or peripherals,and a higher speed memory interface (EMIFB)for SDRAM.The Ethernet Media Access Controller (EMAC)provides an efficient interface between the TMS320C6745/6747device and the network.The EMAC supports both 10Base-T and 100Base-TX,or 10Mbps and 100Mbps in either half-or full-duplex mode.Additionally,an MDIO interface is available for PHY configuration.The rich peripheral set provides the ability to control external peripheral devices and communicate with external processors.For details on each of the peripherals,see the related sections later in this document and the associated peripheral reference guides.(1)For more information on these devices,see Section 8,Mechanical Packaging and OrderableInformation.Device Information (1)PART NUMBERPACKAGE BODY SIZE TMS320C6745HLQFP (176)24.00mm x 24.00mm TMS320C6747BGA (256)17.00mm x 17.00mm。

DM6437烧写总结

DM6437烧写总结1 要了解烧写,首先要了解6437的存储器组织存储器的硬件组织原理可以参看TMSC6000结构原理与硬件设计(北京航天航空大学);具体的存储器的硬件连接可以参照合众达的DEC6437原理图。

从原理图可以知道,flash的控制信号线CE/OE/WE 都是连接与板子上面的CPLD,如需要控制读写,还要参看flash的datasheet来了解其读写时序,编写CPLD的程序,这里暂且略过,S29AL032D数据线22根,相当于内部有4M*8bit的存储空间(在flash 烧写的程序中会有一句if(FillSize > 0x100000){printf("The OUT file is too big!\n");}之所以这里是1M,不是4M,是因为后面调用fread的时候是按照4字节为单位来读取的!),地址线连接于EM_BA0-1(用于bank区分) EM_A0-A19片选是选择的cs2,因此flash用到的空间是EMIF_CS2 = 0x0x4200 0000,查看存储器映射表(详见TMS320DM6437 Digital Media Processor中table 2-3)因此,在烧写的程序中基址被定为#define FLASH_BASE ( EMIF_CS2_BASE )数据总线与dsp的连接是:EM_D0-7 8位因此,flash写数据时,指针设置为从FLASH_BASE开始的地方。

2 CCS烧写flash的办法:a.Ti提供的软件flashburn,需要将.out->rom格式;b 将编写两个工程:一个主程序工程(即用户应用程序,其中包括二次引导程序),一个搬运程序工程。

搬移程序不能使用与主程序的程序空间和中断向量表重合的物理空间,以免覆盖。

烧写时,同时打开主程序和搬移程序的PROJECT,先LOAD主程序,再LOAD搬移程序,然后执行搬移程序,烧写OK!C 用户应用程序(必须包含boot引导程序,否则无法启动)编译生成.out,然后编写烧写程序,在烧写程序中将生成的.out烧写到flash中。

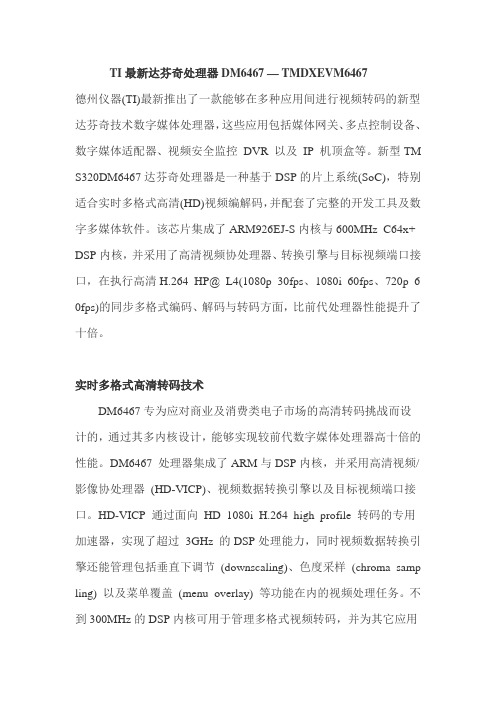

TI最新达芬奇处理器DM6467 — TMDXEVM6467

TI最新达芬奇处理器DM6467 — TMDXEVM6467德州仪器(TI)最新推出了一款能够在多种应用间进行视频转码的新型达芬奇技术数字媒体处理器,这些应用包括媒体网关、多点控制设备、数字媒体适配器、视频安全监控DVR 以及IP 机顶盒等。

新型TM S320DM6467达芬奇处理器是一种基于DSP的片上系统(SoC),特别适合实时多格式高清(HD)视频编解码,并配套了完整的开发工具及数字多媒体软件。

该芯片集成了ARM926EJ-S内核与600MHz C64x+ DSP内核,并采用了高清视频协处理器、转换引擎与目标视频端口接口,在执行高清H.264 HP@ L4(1080p 30fps、1080i 60fps、720p 6 0fps)的同步多格式编码、解码与转码方面,比前代处理器性能提升了十倍。

实时多格式高清转码技术DM6467专为应对商业及消费类电子市场的高清转码挑战而设计的,通过其多内核设计,能够实现较前代数字媒体处理器高十倍的性能。

DM6467 处理器集成了ARM与DSP内核,并采用高清视频/影像协处理器(HD-VICP)、视频数据转换引擎以及目标视频端口接口。

HD-VICP 通过面向HD 1080i H.264 high profile 转码的专用加速器,实现了超过3GHz 的DSP处理能力,同时视频数据转换引擎还能管理包括垂直下调节(downscaling)、色度采样(chroma samp ling) 以及菜单覆盖(menu overlay) 等功能在内的视频处理任务。

不到300MHz的DSP内核可用于管理多格式视频转码,并为其它应用预留了足够的空间。

DM6467 可满足媒体网关与MCU 等需要转码技术的市场要求,但其强大的灵活性与高效性对要求同时进行高清编码与解码的应用来说也非常具有吸引力,如视频语音或视频安全等对于多通道标清编码要求较高的市场。

该器件的连接外设中还包括标准PCI 总线及千兆以太网。

DM6437评估板技术手册

DM6437评估板技术手册一、DM6437 EVM概述1.1 dm6437关键特性> 时钟频率达600MHz> 1个TVP5146M2视频解码器(TI提供),支持复合或S视频端子(TVP5146M2: 是一个单芯片数字视频解码器,将所有流行带宽模拟格式视频转化为数字视频分量。

它支持RGB和YPbPr输入信号分量的模数转换,并支持NTSC,PAL和SECAM复合和S-video等输入信号的模数转换并解码成YCbCr分量)> 4个视频DACV输出---支持分量输出,RGB输出,复合输出> 128M DDR2 DRAM> 提供16M non-volatile flash memory, 64M NAND flash, 2M SRAM (volatile: 易丢失的)> 提供UART, CAN(控制器局域网络,一种总线协议) I/O接口> AIC33 立体音频编码器> 10/100 MBS以太网接口> 可配置的boot load 选项> 嵌入式的JTAG 仿真器接口> 4个用户LEDs及4个用户切换点> 提供子板扩展插槽> VL YNQ接口(VLINQ是由Ti公司研制的一种宽带接口,可使用在WLAN、modems, VOIP处理器以及音频视频媒体处理器上。

是一种全双工串行通信接口,将外部扩展物理设备连接到内部总线中。

当这些外部设备连接到内部总线时,就会被映射到内部物理地址空间。

多个VL YNQ 设备会形成一个菊链,设备间采用点对点或主从模式通信。

通过VL YNQ的数据采用8B/10B 编码分包。

VLYNQ总线包括1个时钟信号(CLK)和8个发送线以及8个接受线。

所有VL YNQ 信号只能同时由一个设备控制。

一个设备的发射脚同下一个设备的接收脚相连。

VL YNQ总线的理论最高速率可达125 MHz,而实际数度取决于连接在VL YNQ总线上的物理设备。

DM6437系统连接及功能块图

DM6437系统连接及功能块图

DM6437设备上,C64x+ megamodule,EDMA3传输控制器,各系统外设是通过一套switch fabrec(SF) architecture连接的。

SF由多个切换中心源SCRs和连接桥组成,如图所示。

SCRs在master设备与slave 设备间建立低延时连接,另外,SCRs还可以根据优先级来对mster/slave设备间同发性的数据移动做出裁决。

通过一个SCR,DSP子系统可以发送数据到DDR2控制器,而不会影响EMAC和L2之间的数据传输。

bridge 主要用于执行总线宽度的转换,以及总线操作频率的转换。

如图中,bridge 6在DSP/3的时钟频率总线与DSP/6的总线之间实现频率转换。

此外,bridge 5执行64-bit到32-bit的总线宽度转换。

C64x+ megamodule, EDMA3传输控制器(EDMA3TC[2:0]),以及各种系统外设可以分成两类:master设备和slave设备。

m设备通常可以在系统中发起读和写传输,而无需依赖于EDMA3或CPU来执行从这些设备的读出或写入操作。

系统m设备包括C64x+ Megamodule, the EDMA3传输控制器, VLYNQ, EMAC, HPI, PCI, and VPSS. 注意不是所有m设备都可以与salve设备相连。

DSPDM6437启动模式简介(精)

DSP DM6437 启动模式简介系统设备模块包括状态和控制两种寄存器需要配置。

DM6437 设备有4种不同的模块状态—Enable, Disable, SyncReset, or SwRstDisable1. boot sequence & boot modesboot过程中,程序和数据段从设备内存中load出来,同时某些设备的内部寄存器由预先设定的值进行编程。

每一个设备级的全局reset后boot就被自动启动。

有几种内存和寄存器初始化的方法,此即是boot模式。

DM6437的boot模式分为三类—Non-Fastboot Modes, Fixed-Multiplier Fastboot Modes, and User-Select Multiplier Fastboot Modes. 具体模式由BOOTCFG寄存器的以下几个位域决定:BOOTMODE[3:0]、 PCIEN 这两个联合决定boot类型,如I2C BOOT, EMIFA BOOT, HPI BOOT, PCI BOOT >FASTBOOT---->决定是否使能PLL以加速boot进程。

AEM[2:0]、PLLMS[2:0]这两个联合,在FASTBOOT=1时决定PLL倍频器。

有一点要注意:除了EMIFA ROM Direct Boot模式的DSPBOOTADDR=0x42000000外,其他boot模式下缺省的DSPBOOTADDR=0x00100000.且bootloader程序会去禁止所有c64x+的cache,包括L2,L1P,L1D,故在bootloader后,c64x+的所有内存都被配置成RAM,如果需要,则需自己手动配置cache.由上述三类boot模式,在设备reset后,boot控制器缺省下有两个启动地址DSPBOOTADDR,由boot模式而定,在任何一种boot模式下,c64x+立即从reset 状态下释放,并开始从DSPBOOTADDR所给的地址处开始执行。

DM6437

一、DaVinci DM6437 概述TMS320DM6437是TI公司2006年推出的、专门为高性能、低成本视频应用开发的、主频600MHz的、32位定点DSP达芬奇(DaVinci(TM)) 技术的处理器系列。

TMS320DM6437具有下列特点:采用TI第3代超长指令集结构(VelociTI.3)的TMS320C64x+ DSP内核,主频可达600MHz,支持8个8位或4个16位并行MAC运算,峰值处理能力高达4800MIPS,可实时处理8路CIF或3路D1格式的H.264编码算法。

采用2级Cache存储器体系结构,片上有32K字节RAM/Cache可配置的1级程序存储器L1P,48K字节RAM + 32K字节RAM/Cache可配置的1级数据存储器L1D,和128K字节RAM/Cache可配置的2级程序/数据存储器L2,存储器体系结构更灵活、合理,有利于提高图像处理代码/数据的吞吐率。

片上具有64通道增强型DMA控制器EDMA3,其支持复杂的数据类型的传输,有利于图像数据的高效传输和格式变换。

丰富的外部存储器接口:一个专用的32位、200MHz、256M字节寻址空间的DDR2存储器接口用于接口高速、大容量的DDR2存储器,以存储代码和数据;一个8位、64M字节寻址空间的异步存储器接口用于接口8位Nor Flash或Nand Flash,以存储固化代码。

丰富的片上外设:一个专用的单通道视频输入接口,既可以方便地与各种数字视频输入标准接口,还具有常用的视频预处理功能;一个专用的单通道视频输出接口,既可以提供多种模拟视频输出标准,还可以提供各种数字视频输出标准接口,并且在视频输出之前,还支持多个视频窗口管理及在视频画面上叠加文本数据;一个多通道音频串口,可无缝接口音频Codec器件,实现模拟视频信号的输入/输出;一个I2C总线,可无缝接口视频解码器/编码器和音频Codec的控制口,方便实现音/视频编解码器的控制;32位PCI总线,方便与PC机接口,实现多板并行工作。

基于TMS320DM6437的视频采集接口设计

97科技创新导报 Science and Technology Innovation Herald 工 程 技 术1 引言视频监控系统以直观、方便、实时性等优点被广泛应用于如交通、水利、安防等领域而成为人们一直关注的焦点,然而基于人脸识别的考勤机设计也是很热门的领域。

但是视频监控系统的广泛使用的前提是视频采集。

TMS320DM6437(以下简称DM6437)是TI公司推出的一款专门面向多媒体应用的DSP。

时钟可达600MHz,具有8个并行运算单元,处理能力达4800MIPS;采用的是二级缓存结构;具可外接64位存储器。

使用DM 6437设计视频信号采集电路具有以下优点:(1)电路简单(2)高集成度(3)高速。

基于这些优点的视频设计系统是有重要的实用意义。

[1]D M 6437的内部集成了存储视频数据的FIFO和视频的行、场同步信号,如果使用DM 6437来做视频采集系统的话只需要在一块前端视频采集芯片即可。

本文提出一种利用TI公司的高性能视频解码器TVP5146设计DM6437视频接口的方法。

该方法不仅能实现高速实时的视频数据采集,且无需外加CPLD逻辑控制电路和FIFO缓存,具有电路简单、可靠性高、容易实现等优点。

本文首先介绍DM6437的视频端口,然后论述利用T VP 5146来实现D M6437视频采集接口的方法。

2 DM6437视频端口T M S 320D M 6437提供了V P S S 视频处理子系统,方便与各种视频格式接口。

可实现P A L /N T S C 标准模拟视频输入,本系统采用的TVP5146是由TI公司推出的一款低功耗,超小封装的高性能视频解码器。

该芯片内核电源电压为1.8V,输入输出电压为3.3V,采用外部独立的14.318MHz的晶振为其提供时钟频率,它支持两路CVBS (复合视频信号)输入和一路超级视频信号Y/C ,模拟摄像头输出的模拟视频信号在T VP 5146内部经过钳位、抗混叠滤波、A D 转换、Y U V 分离电路之后,在Y U V 到Y C r C b 的转换电路中转换成8位的I T U -RBT.656格式的视频数据。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

TI达芬奇系列DM6437核心板中文资料整理Revision History

Draft Date Revision No. Description 2016/10/17 V1.0 1.初始版本。

目录

1 核心板简介 (3)

2 典型运用领域 (4)

3 软硬件参数 (4)

4 开发资料 (7)

5 电气特性 (7)

6 机械尺寸图 (8)

7 核心板订购型号 (8)

1核心板简介

基于TI TMS320DM6437的32位定点多媒体DSP处理器,适合高性能、低成本视频应用开发,最高主频为700MHz;

支持8个8bit或4个16bit并行MAC运算,峰值处理能力高达5600MIPS,可实时处理8路CIF或3路D1格式的H.264编码算法;

2级Cache体系结构:32KB可配置L1P、80KB可配置L1D和128KB可配置L2;

64通道增强型DMA控制器EDMA3,支持复杂的数据类型的传输,利于图像数据高效传输和格式变换;

视频处理子系统(VPSS):具有1个VPFE视频输入接口,支持BT.656输入,1个VPBE 视频输出接口,支持NTSC/PAL,S-Video,RGB,YPbPr输出;

集成McASP、McBSP、I2C、UART、PCI、HPI、EMIFA等常见接口;

核心板大小仅63.5mm*38mm;

采用精密工业级B2B连接器,占用空间小,稳定性强,易插拔,防反插。

图1 SOM-TL6437正面

图2 SOM-TL6437背面

由广州创龙自主研发的SOM-TL6437是基于TMS320DM6437定点DSP核心板,大小仅63.5mm*38mm,功耗小、成本低、性价比高。

采用沉金无铅工艺的六层板设计,专业的PCB Layout保证信号完整性的同时,经过严格的质量控制,满足工业环境应用。

SOM-TL6437引出CPU全部资源信号引脚,二次开发极其容易,用户只需要专注上层运用,降低了开发难度和时间成本,让产品快速上市,及时抢占市场先机。

不仅提供丰富的Demo程序,还提供全面的技术支持,协助用户进行底板设计和调试以及DSP软件开发。

2典型运用领域

✓机器视觉系统

✓机器人技术

✓视频安全设备和视频电话

✓车用视觉系统

✓内窥镜

✓视频分析服务器

✓运动检测器(PIR和微波等)

3软硬件参数

功能框图

图3 TMS320DM6437功能框图硬件框图

图4 TMS320DM6437硬件框图

硬件参数

表1

CPU TMS320DM6437,32位定点DSP C64x+,主频600MHz

ROM 128MByte NAND FLASH

RAM 256MByte DDR2

1x 供电指示灯

LED

2x 可编程指示灯

连接器2x 50pin公头B2B,2x 50pin母头B2B,间距0.5mm,共200pin,合高3.5mm 111x GPIO

1x EDMA3(含64个独立通道)

1x 10/100M Ethernet

3x Timers(含2个64位通用寄存器和一个64位看门狗)

2x UART

3x PWM

1x EMIFA

1x VLYNQ

1x I2C

1x HPI

1x PCI

2x McBSP

1x McASP

2x Video Ports(1x VPFE +1x VPBE)

1x HECC

1x 8位启动模式选择信号

软件参数

表 2

DSP端软件支持裸机、SYS/BIOS操作系统

CCS版本号CCS5.5

4开发资料

(1)提供核心板引脚定义、可编辑底板原理图、可编辑底板PCB、芯片datasheet,缩短硬件设计周期;

(2)提供丰富的Demo程序;

(3)提供完整的平台开发包、入门教程,节省软件整理时间,上手容易;

基于DSP端的裸机开发例程

基于DSP端的SYS/BIOS开发例程

5电气特性

核心板工作环境

表 3

环境参数最小值典型值最大值

商业级温度0°C / 70°C

工业级温度-40°C / 85°C

工作电压 3.8V 5V 5.5V

6机械尺寸图

表 4

PCB尺寸63.5mm*38mm

安装孔数量4个

图5 SOM-TL6437机械尺寸图

7核心板订购型号

表 5

型号CPU主频NAND FLASH DDR2 温度级别SOM-TL6437-4-1GN2GD-I-A2 600MHz 128MB 256MB 工业级

型号参数解释

图6 命名规范。