allegro16[1].2建立差分对,设置差分规则,差分走线。

allegro差分对和XNET设置

差分线的设置,相对等长线以及xnet的设置不同的信号对走线的要求不同,差分线为了抗干扰能力强,要求两根信号线在一定范围内等长等间距。

而现对等长线要求信号的相对延时在一定的范围内必须比较接近。

这个设置在原理图阶段可以设置,不过现在要讲的主要是在allegro环境下的设置。

一差分线的设置点击logic——》assign differential pair出现以上对话框的时候选择要创立的差分对的两根线。

方法很简单只要点击要选择的线就可以了在net1 和net2 上就可以显示这两个线的名字。

Diff pair name 自己起个记住名字。

一会设置规则的时候还要用到。

点击add 差分对就设定好了。

下面是通过约束管理器来定义差分对的走线规则。

点击set up——》constraints——》electrical选择net ——》differential pair 找到我们刚才设定的差分对名字lwq4 规则设定为5/7 Ok二等长线以及xnet 的设置许多等长线要求的场合往往等长线里还包含电阻,如果不用xnet 就需要画两组等长线,给布线带来很大的工作量。

特别是布线空间有限的时候。

1.设置xnet2.点击analyze——》SI/EMI sim ——》signal model assignment如上图,点击要创建xnet的器件比如说排阻rp4 点击creat model 出现如下对话框点击ok 出现如下对话框这里value 是仿真的时候用的阻值我们可以随便填个值比如说10 不过记住要这组等长线所有value 都要相等。

Single pins 这个非常重要,现在我们用的是排阻他有八个引脚。

就是说有四根线输入输出排阻,那么1 脚和8脚对应第一根线的输入输出,那么 2 脚和7脚对应第二根线的输入输出,那么3 脚和6脚对应第三根线的输入输出,那么4脚和5脚对应第四根线的输入输出,所以single pins 就对应 1 8 2 7 3 6 4 5 。

Cadence_Allegro16.2常用操作方法

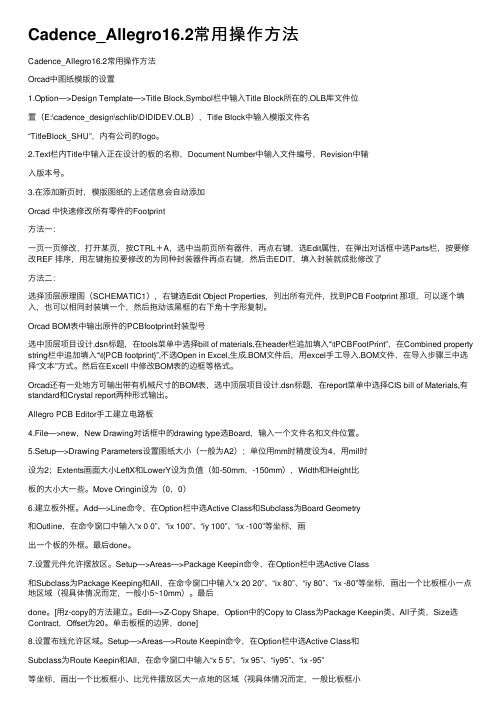

Cadence_Allegro16.2常⽤操作⽅法Cadence_Allegro16.2常⽤操作⽅法Orcad中图纸模版的设置1.Option—>Design Template—>Title Block,Symbol栏中输⼊Title Block所在的.OLB库⽂件位置(E:\cadence_design\schlib\DIDIDEV.OLB),Title Block中输⼊模版⽂件名“TitleBlock_SHU”,内有公司的logo。

2.Text栏内Title中输⼊正在设计的板的名称,Document Number中输⼊⽂件编号,Revision中输⼊版本号。

3.在添加新页时,模版图纸的上述信息会⾃动添加Orcad 中快速修改所有零件的Footprint⽅法⼀:⼀页⼀页修改,打开某页,按CTRL+A,选中当前页所有器件,再点右键,选Edit属性,在弹出对话框中选Parts栏,按要修改REF 排序,⽤左键拖拉要修改的为同种封装器件再点右键,然后击EDIT,填⼊封装就成批修改了⽅法⼆:选择顶层原理图(SCHEMATIC1),右键选Edit Object Properties,列出所有元件,找到PCB Footprint 那项,可以逐个填⼊,也可以相同封装填⼀个,然后拖动该⿊框的右下⾓⼗字形复制。

Orcad BOM表中输出原件的PCBfootprint封装型号选中顶层项⽬设计.dsn标题,在tools菜单中选择bill of materials,在header栏追加填⼊“\tPCBFootPrint”,在Combined property string栏中追加填⼊“\t{PCB footprint}”,不选Open in Excel,⽣成.BOM⽂件后,⽤excel⼿⼯导⼊.BOM⽂件,在导⼊步骤三中选择“⽂本”⽅式。

然后在Excell 中修改BOM表的边框等格式。

Orcad还有⼀处地⽅可输出带有机械尺⼨的BOM表,选中顶层项⽬设计.dsn标题,在report菜单中选择CIS bill of Materials,有standard和Crystal report两种形式输出。

Cadence Allegro 16.2规则设置

Spacing规则(约束)Rexdlutarm@2009-07-02 Allegro 16.0以后版本的约束规则设置较之前有很大改变,对于用惯了15.x的人来说,很多不习惯新的约束管理器。

和在对待女人的态度上,恰相反。

80后说90后脑残,15.7说16.2脑残,Xp说Vista脑残。

Vista确实很脑残。

新事物取代旧事物是自然界发展的客观规律。

说明:1本文只介绍了Spacing约束的设置,因为Physical规则通常来说都设置的非常简单。

掌握了Spacing规则Physical规则对你来说一定是小Case。

另外,Physical 规则的设置也写的话,一定显得都是在重复Spacing的设置;2文中所有的规则(约束),如不特殊说明默认情况下均指Spacing规则(约束);3对于Electrical的约束,是另一种约束,本文不作讨论。

约束的设置方式:1直接的:Net中写数值,2 间接的:创建Constraint Set,然后Assign给Net;这两种都很常用,后者管理方便。

在Physical和Spacing设置中用后者比较好,但是在Electrical中,我看到很多很多的人会混合使用。

使用第二种约束设置方式的约束设置步骤:1约束的对象2约束的内容3给对象分配内容1这3个步骤默默的引导着所有间接约束的设置。

基本约束预备先理解:Net class2Net class-classRegionRegion-classRegion-class-classBus……现在不理解,想跳过去。

没关系,你早晚都要理解的。

最简单和稍微复杂一点的约束:最简单的就是default的约束,稍微复杂一点的就是修改了一点默认的约束。

再复杂一些的约束:你可能会想让不断变化的CLK(我们不考虑是不是差分)和其他的线离的远一些。

在Constraint Set中Create规则并设置规则的内容:Creat & Set之后3给Net分配规则:更高级的约束:What Can U Think?有了一根线的约束,贪婪的本性会使你你很快上升到两根线(通常是Diff)和更多线的约束。

allegro建立差分线规则

allegro建立差分线规则

建立差分线规则的方法如下:

1. 确定差分线的标准:差分线指的是MACD指标中的DIF线

和DEA线之间的差值。

一般情况下,当DIF线由负值变为正

值时,表示买入信号;当DIF线由正值变为负值时,表示卖

出信号。

2. 设定阈值:根据市场经验和个人风险偏好,设定一个合适的阈值来判断买入和卖出信号。

比如,当DIF线大于等于阈值时,触发买入信号;当DIF线小于等于阈值的负值时,触发

卖出信号。

3. 确定持仓策略:根据买入和卖出信号,制定持仓策略。

比如,当触发买入信号时,可以全仓买入;当触发卖出信号时,可以全部卖出或者部分卖出。

4. 设置止损和止盈点:为了控制风险,可以设置一定的止损和止盈点。

比如,当买入后的价格下跌到设定的止损点时,自动卖出;当买入后的价格上涨到设定的止盈点时,自动卖出。

5. 定期回顾和调整规则:市场行情时刻变化,所以需要定期回顾和调整差分线规则。

可以根据历史回测结果和市场环境来优化规则,提高交易效果。

需要注意的是,差分线规则只是一种参考,投资者应根据个人

情况和市场情况综合考虑。

此外,差分线规则也具有一定的局限性,不能完全依赖于它进行投资决策。

allegro建立差分线规则

allegro建立差分线规则

建立差分线规则是在使用Allegro软件进行PCB设计时非常重要的一步。

差分

线是一对相互衔接的信号线,用于传输高速数字信号,如USB、HDMI和以太网等。

通过建立差分线规则,可以确保差分线的质量和稳定性,减少干扰和串扰,从而提高整体电路性能。

首先,在Allegro软件中,打开设计文件并进入布局编辑器。

选择需要添加差

分线规则的信号线对,并右键单击选择“差分对属性”。

在弹出的对话框中,可以设置差分线的物理特性、约束条件和信号完整性要求。

物理特性方面,可以设置差分线的宽度、间距和层堆栈,以满足设计要求。

这

些参数会影响差分线的阻抗和信号传输速率,需要根据具体设计需求进行调整。

约束条件方面,可以设置差分线的最大长度、最小间距和最大串扰限制等。

这

些约束条件会在布线时自动检测和优化差分线,确保其满足电路的可靠性和性能要求。

信号完整性要求方面,可以设置差分线的最大延迟和最小延迟不平衡等。

这些

要求会在信号传输过程中考虑时延和时序要求,确保差分信号的同步性和稳定性。

在建立差分线规则之后,可以进行布线操作。

Allegro软件会根据所设定的差

分线规则自动分配和布线差分线,同时提供实时反馈和报告,以便进行优化和调整。

综上所述,建立差分线规则是使用Allegro软件进行PCB设计中至关重要的一步。

通过准确设置差分线的物理特性、约束条件和信号完整性要求,可以确保差分线的质量和稳定性,提高整体电路性能。

同时,在布线过程中,Allegro软件提供

了自动分配和布线差分线的功能,方便优化和调整设计。

allegro差分线设置规则

allegro差分线设置规则Allegro差分线设置规则引言:Allegro差分线是一种常用的信号传输方式,在电路设计中起到了重要的作用。

本文将探讨Allegro差分线设置规则,从理论和实践角度介绍如何正确地设置Allegro差分线以保证信号传输的准确性和稳定性。

一、什么是Allegro差分线?Allegro差分线是一种差分信号传输方式,通过同时传输正负两个信号来降低干扰和提高信号的抗噪声能力。

差分信号在信号线上的电压差被解读为二进制信号,从而实现数据传输。

Allegro差分线广泛应用于高速数据传输、音频信号传输等领域。

二、设置规则1. 差分线对称布局:为了减小差分信号间的电磁干扰,差分线应该尽量保持对称布局。

在PCB设计中,可以通过布局对称的方式将差分信号线放置在相邻的层上,并且保持相同的长度和宽度,以确保信号的平衡传输。

2. 差分线长度匹配:差分线的长度差异会导致信号的相位差,从而影响信号的准确性和稳定性。

因此,在布线过程中,应尽量使差分线的长度保持一致,以确保信号的同步传输。

3. 差分线与其他信号线的间隔:为了避免干扰,差分线应与其他信号线保持一定的间隔。

特别是与高频信号线、时钟线等应尽量保持一定的距离,以减小相互之间的电磁干扰。

4. 差分线与地线的间隔:差分线与地线之间的间隔也需要特别注意。

过大的间隔会增加信号线的阻抗,影响信号的传输质量;而过小的间隔则容易导致信号与地线之间的串扰干扰。

因此,在实际设计中,应根据具体情况合理设置差分线与地线的间隔。

5. 差分线的屏蔽与接地:为了进一步降低差分线的干扰,可以采用屏蔽措施。

常见的做法是在差分线周围设置屏蔽层,并将屏蔽层接地,以消除外部电磁干扰对信号的影响。

6. 差分线的阻抗匹配:差分线的阻抗匹配是保证信号传输质量的关键。

在设计中,应根据差分线的特性和设计要求,选择合适的阻抗值。

常见的阻抗匹配方式有微带线和差分对线,设计时需要注意保持差分线的阻抗匹配。

Allegro中等长线或差分线设置的一些方法

以千兆以太网为例说明,差分等长设置;

首先,拉好差分线;

打开约束管理器,创建BUS(也可以再拉线之前创建,个人习惯拉线前设好所有的总线BUS);

创建MG;

差分的对内等长设置;

其他信号等长线路(点对点或一组像具有相同模型)可以参照以上做法!

若一组线内有多种模型;一般选择使用相同模型最多的一根做模型创建MG;驱动后不同模型会自动显示红色,把显示红色的clear掉规则,设置点对点的PIN pair ,然后membership到之前创建的MG即可,等长范围手动添加。

创建不同的模型和PIN pair 最后都是要membership到一个每个里面,这样才能一起等长;

Pin pair很费时间,如果拖的器件多了,做起来很费事。

allegro差分线分组约束规则设置

allegro差分线分组约束规则设置摘要:1.Allegro差分线分组约束规则简介2.设置差分线分组约束规则的步骤3.约束规则的应用场景及优势4.总结与建议正文:1.Allegro差分线分组约束规则简介Allegro软件是一款专业的印刷电路板(PCB)设计软件,其差分线分组约束规则是其中一项重要的功能。

通过这项功能,用户可以实现自动化布局,确保PCB上各个元件的正确位置和连接关系,从而提高整体设计的稳定性和可靠性。

2.设置差分线分组约束规则的步骤在Allegro软件中设置差分线分组约束规则,主要可以分为以下几个步骤:步骤一:创建差分线。

首先,在Allegro中创建差分线,它们用于定义分组约束规则。

步骤二:定义约束规则。

在创建差分线后,设置相应的约束规则,如最小间距、最大间距等。

步骤三:应用约束规则。

将设置好的约束规则应用于需要布局的元件,以确保它们在PCB上的位置和连接关系满足设计要求。

步骤四:检查与修复。

在布局过程中,不断检查PCB设计是否符合约束规则,如有问题,及时进行修复。

3.约束规则的应用场景及优势差分线分组约束规则在以下场景中具有显著优势:- 提高设计效率:通过自动化布局,设计者可以更快地完成PCB设计,减少重复性工作。

- 保证连接可靠性:约束规则确保了元件之间的正确连接,降低了故障风险。

- 优化电路性能:合理的布局可以降低信号干扰,提高电路性能。

- 易于维护:约束规则使得设计更加规范,便于后期维护和升级。

4.总结与建议差分线分组约束规则在Allegro软件中发挥着重要作用,能够帮助设计者实现自动化布局,提高PCB设计的质量。

在使用过程中,建议设计者熟练掌握约束规则的设置方法,并根据实际需求进行调整。

allegro 差分对间 控制

allegro 差分对间控制Allegro差分对间控制差分对间控制是一种常见的电路设计技术,在许多电子设备中被广泛应用。

本文将介绍差分对间控制的基本原理和应用场景。

一、差分对间控制的原理差分对间控制是一种基于差分信号的反馈控制技术。

差分信号是由两个输入信号之间的差值构成的。

差分对间控制通过比较差分信号与设定值之间的差异,并根据差异的大小进行相应的调节,以实现对输出信号的控制。

差分对间控制的基本原理是通过放大差分信号并将其与设定值进行比较,然后根据比较结果来调节系统的输出。

常用的差分对间控制器包括比例控制器、积分控制器和微分控制器。

比例控制器根据差分信号与设定值的比例关系进行调节;积分控制器根据差分信号与设定值的积分关系进行调节;微分控制器根据差分信号与设定值的微分关系进行调节。

这些控制器可以单独使用,也可以组合使用,以实现更精确的控制。

二、差分对间控制的应用场景差分对间控制广泛应用于各种电子设备中,特别是在模拟信号处理和通信系统中。

以下是几个常见的应用场景:1. 音频放大器:差分对间控制可以用于音频放大器的电平控制,以实现音频信号的放大和输出控制。

通过差分对间控制,可以使音频信号的输出保持在设定的电平范围内,以避免信号失真或过载。

2. 通信系统:差分对间控制可以应用于通信系统中的信号调节和增益控制。

通过差分对间控制,可以实现对输入信号的动态调节,以适应不同的信号强度和传输距离。

3. 传感器信号处理:差分对间控制可以用于传感器信号的处理和调节。

通过差分对间控制,可以对传感器信号进行放大、滤波和校正,以提高信号的稳定性和精确性。

4. 自动控制系统:差分对间控制在自动控制系统中起着重要作用。

通过差分对间控制,可以对系统的输入和输出进行实时监测和调节,以实现系统的稳定性和性能优化。

三、差分对间控制的优势和挑战差分对间控制具有以下优势:1. 高精度:差分对间控制通过比较差分信号与设定值的差异来进行调节,可以实现对输出信号的高精度控制。

allegro设置差分线和等长的方法

一、设置差分线的方法方法一:1、Logic→Assign Differenttial Pair2、在弹出的对话框里选择需要添加的差分对,点击Add按钮,即可添加方法二:1、Setup→Constraints→Electrical2、选择Net,然后在Objects→Create→Differenttial Pair3、在弹出的对话框里选择需要添加的差分对,点击Create按钮,即可添加设置完差分线对后,需要设置其约束规那么,方法如下:1、初始默认的有一个DEFAULT规那么,右击DEFAUlT,选择Create→Physical CSet2、弹出一下对话框,在Physical CSet栏写上规那么名称,建议根据差分线的阻抗描写,点击OK,这里已经写好,规那么名称为:DIFF100,就可以看到多了一行PCS3、设立好规那么后就可以在这项规那么里设置线宽间距等参数了4、在Net一栏看到有已经设好的差分线,在Referenced physical C Set选项下选择刚刚设好的规那么DIFF100*规那么设置中各个工程的含义*Line Width〔设置根本走线宽度〕Min:最小线宽Max:最大线宽,写0相当于无限大Neck〔neck模式,一般在间距很小的时候用到〕Min Width:最小线宽Max Length:最大线长Differential Pair〔差分线设置,单端线可不写〕Min Line Spacing:差分对的最小线间距Primary Gap:差分对理想线间距Neck Gap:差分对最小允许线间距(+)Tolerance:差分线允许的误差+(-)Tolerance:差分线允许的误差-Vias〔过孔选择〕BB Via Stagger〔设置埋/盲孔的过孔间距〕Min:最小间距Max:最大间距AllowPad-Pad Connect:/Etch:/Ts:/示意图:二、设置等长1、进入规那么设置页面Electrical→Net→Routing→Relative Propagation Delay2、选中需要设置等长的网络,右击,选择Create→Match Group3、更改组名称4、设置好后,会显示MGrp,如下列图。