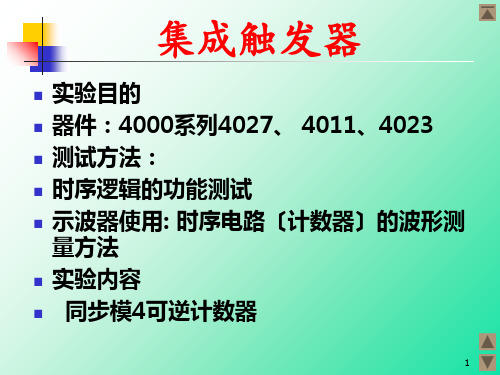

数电实验报告之集成触发器

实验07集成触发器(1)

SD RD Q /Q

00 01 10 11

功能测试 ?

MC14027 CD4027

16 15 14 13 12 11 10 9

VDD 2Q 2Q 2CP 2RD 2K 2J 2SD CC4027 双上升沿J-K触发器

1Q 1Q 1CP 1RD 1K 1J 1SD VSS

3

时序电路〔计数器〕的波形测量方法

1 2 3 45 6 7 8 9

CP

0 1 0 10 1 01 1Q

问题: 0 0 1 1 0 0 1 1 2Q

1. 观测3个以上的波形,应该如何操作? 两两比较… … 与谁比较?

2. CP CH1,1Q CH2。触发信源选谁? 应选择频率低的,即CH2

3. 触发斜率应选上升沿还是下降沿? 加计数器-上升沿;减计数器-下降沿

9

+5V 本卷须知

14 13 12 11 10 9 8 VDD 4B 4A 4Y 3Y 3B 3A

CC4011 四2输入与非门 1A 1B 1Y 2Y 2A 2B VSS 1234567

14 13 12 11 10 9 8 VDD 3C 3B 3A 3Y 1Y 1C

CC4023 三3输入与非门 1A 1B 2A 2B 2C 2Y VSS 1234567

14 13 12 11 10 9 8 VDD 3C 3B 3A 3Y 1Y 1C

CC4023 三3输入与非门 1A 1B 2A 2B 2C 2Y VSS 1234567

MC14023 CD4023

11

验收要求

坐标纸上画出CP,Q0,Q1,Z的加法和减 法时的波形图

在CP利用信号源的同步输出端输入1hz 的脉冲信号,利用Q0,Q1,Z分别连接 三个发光二极管控制发光二极管的亮灭 。

集成触发器实验

数电实验:集成触发器实验一、D触发器1.VHDL编程library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity dff1 isport(-- Input portsclk: in bit;D: in bit;-- Output portsQ: out BIT;Q1:OUT BIT);end dff1;architecture one of dff1 isbeginprocess(clk)beginif(clk'event and clk='1') thenQ<=D;Q1<=NOT D;end if;end process;end one;2.功能仿真:二、JK触发器1.VHDL编程library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all; entity jkff1 isport(-- Input portsCLK: in bit;J,K : in bit;-- Output portsQ : out BIT);end jkff1;architecture one of jkff1 issignal Q:bit;beginprocess(CLK)beginif(CLK'event and CLK='1')thenQ<=(J and not Q)or(not K and Q); end if;Q<=Q;end process;end one2.功能仿真三、广告流水灯时序电路VHDL编程1.电路图2.VHDL语言实现library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all; entity light1 isport(-- Input portsclk1: in bit;D1: in bit;D2: in bit;-- Output portsQ1: inout BIT;Q11:inOUT BIT;Q2:inOUT BIT;Q22:inOUT BIT;L1: OUT bit;L2: OUT bit;L3: OUT bit;L4: OUT bit);end light1;architecture one of light1 is signal clk2:bit;beginprocess(clk1,clk2)beginif(clk1'event and clk1='1') then Q1<=D1;Q11<=NOT D1;end if;clk2<=Q1;if(clk2'event and clk2='1') then Q2<=D2;Q22<=NOT D2;L4<=(Q2 nand Q1);L3<=(Q2 nand Q11);L2<=(Q22 nand Q1);L1<=(Q22 nand Q11);end if;end process;end one;3.功能仿真4.时序仿真。

集成触发器实验报告

电子电路试验报告

姓名:专业:班级:学号:

一、试验名称

集成触发器功能及其应用。

二、试验目的

掌握用与非门组成的基本RS触发器的特征;掌握集成JK触发器、D触发器的逻辑功能和使用方法;熟悉各种触发器的应用。

三、试验任务

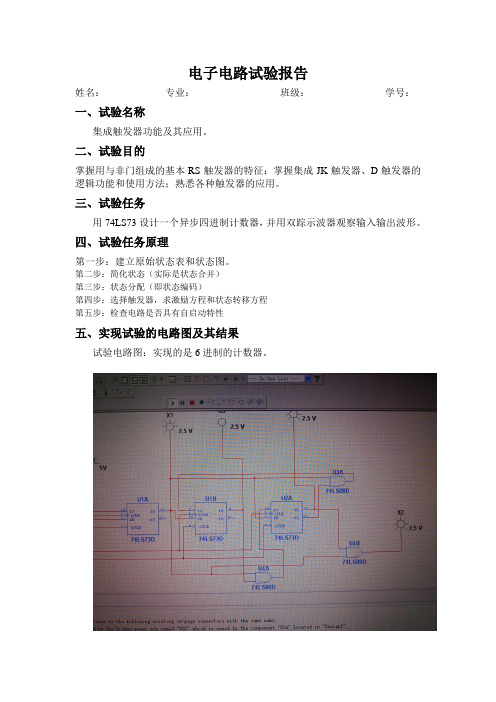

用74LS73设计一个异步四进制计数器,并用双踪示波器观察输入输出波形。

四、试验任务原理

第一步:建立原始状态表和状态图。

第二步:简化状态(实际是状态合并)

第三步:状态分配(即状态编码)

第四步:选择触发器,求激励方程和状态转移方程

第五步:检查电路是否具有自启动特性

五、实现试验的电路图及其结果

试验电路图:实现的是6进制的计数器。

波形图:

六、思考题

(1)为解决主从JK触发器的一次变化问题,对CP脉冲有何要求?

答:对CP的要求是宽度较窄的正脉冲,且在CP=1期间,输入信号J,K不发生变化

七、试验心得与体会

通过这次电子电路试验,我对触发器有了了解,触发器是一种具有记忆功能的电路,可作为二进制存储单元使用。

触发器有置位端和复位端,只有当它们同时为1的时候,触发器才能正常工作,否则进行复位、置位、维持的功能,这些是我在这次试验中所学到的。

实验五集成触发器

Qn=1 说明

且每次测试时都要将

0→1

触发器异步清零或置1。

0 0 1→0

按照右表测试并记录结果。

(c)将J、K触发器

0

接成 T’触发器。

CP接1kHz连续脉冲;

1

通过示波器双踪观察

CP和Q的波形,

1

画图并分析结果。

0→1

1 1→0

0 0→1

1→0

1

0→1

1→0

实验五 触发器

4. 实验内容及要求

(2)测试双D触发器74LS74的逻辑功能。

Q

Q

1J C1 1K J CP K SD

74LSll2双JK触发器引脚排列及逻辑符号

实验五 触发器

实验五 触发器

(3)D触发器

可用作数字信号的寄存、移位寄存、分频和波形发生等。

Q n+1 = D

14 13 12 11 10 9 8

Vcc 2RD 2D CP SD 2Q 2Q

74LS74

Q

Q

C1 1D

(5)单脉冲发生器实验 (选做) 用74LS74双D型触发器,设计一个单发脉冲发生器的实验线路。要

求将频率为1Hz的信号脉冲和手控触发脉冲分别作为两个触发器的CP 脉冲输入。只要手控脉冲送出一个脉冲,该脉冲与手控触发脉冲的时 间长短无关。

实验五 触发器

试问:能实现单发脉冲输出的原理是什么?画出电路的输出时序波形图. 下图是用双JK触发器组成的单发脉冲发生器,以供设计时参考。

实验五 触发器

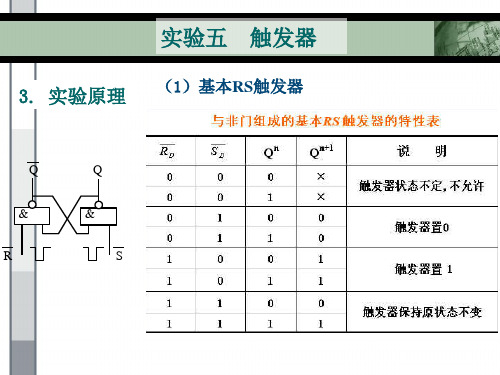

3. 实验原理 (1)基本RS触发器

Q & R

Q &

S

实验五 触发器

(2)JK触发器

常用作缓冲存储器、移位寄存器和计数器。 Qn+1 = JQn + KQn

实验5集成触发器功能测试及应用

实验5 集成触发器功能测试及应用一. 实验目的掌握基本触发器的电路组成及其功能;掌握基本RS、JK、D触发器的逻辑功能;掌握集成触发器的逻辑功能及使用方法。

二三触发器具有两个稳定状态,用以表示逻辑状态“1”和“0”,在一定的外界信号作用下,可以从一个稳定状态翻转到另一个稳定状态,它是一个具有记忆功能的二进制信息存贮器件,是构成各种时序电路最基本的逻辑单元。

RS锁存器(又叫基本RS触发器)是各种触发器构成的基本部件,也是最简单的一种触发器。

它的输入信号直接作用在触发器,无需触发信号。

可以由两个与非门交叉耦合而成。

在输入信号为单端的情况下,D触发器用来最为方便,其状态方程为Q n+1=D,其输出状态的更新发生在CP脉冲边沿,属于边沿触发器,触发器的状态只取决于时钟到来前D端的状态,D 触发器的应用很广,可用作数信号的寄存,位移寄存,分频和波形发生等。

在输入信号为双端的情况下,JK触发器是功能完善.使用灵活和通用性较强的一种触发器。

本实验采用74LS112双JK触发器,是下降边沿触发的边沿触发器。

J-K触发器使用时要查清引线排列,其特征方程为。

四. 实验内容与步骤1.基本RS触发器建立与测试(1)在实验箱上选取一个14P插座,按定位标记插好74LS00集成块,根据右图连接实验线路。

(2)将实验箱上+5V直流电源接74LS00的14脚,地接7脚。

将、接电平开关输出口,输出Q接发光二级管。

(3)按下表在输入端输入相应电平,观察并记录输出逻辑电平显示情况(发光管亮,表示输出高电平“1”,发光管不亮,表示输出低电平“0”)。

2.验证D触发器功能1)在实验箱上选取一个14P插座,按定位标记插好74LS74集成块,将实验箱上+5V直流电源接74LS74的14脚,地接7脚。

将双D 触发器74LS74中的一个触发器的,和D 输入端分别接逻辑开关输出口,CP 端接单次脉冲,输出端和分别接发光二极管。

2)根据输出端状态,填表2。

集成触发器功能测试及转换_实验报告(1)

深圳大学实验报告课程名称:数字电路实验项目名称:集成触发器功能测试及转换学院:专业:指导教师:报告人:学号:班级:实验时间:实验报告提交时间:教务处制一、实验目的:1.熟悉并掌握RS、D、JK触发器的构成,工作原理和功能测试方法;2.掌握不同逻辑功能触发器的相互转换;3.常我三态触发器和锁存器的功能及使用方法;4.学会触发器、三态触发器、锁存器的应用。

二、实验仪器:1.双踪示波器2.RXS-1B数字逻辑电路实验箱3.器件74LS74 双上升沿D触发器74LS76 双下降沿JK触发器三、实验任务:任务一:维持-阻塞型D触发器功能测试双上升沿触发维持-阻塞D触发器74LS74的引脚排列图如图3-19所示。

图中SD,RD端异步置1端,置0端(或称异步位置,复位端)。

CP为时钟脉冲端。

试按下面步骤做实验:1.分别在SD,RD端加低电平,观察并记录Q,Q端的状态。

注意:当SD,RD端同时加低电平时,输出将为高电平,但是此事如果SD,RD端再同时加高电平,对应的输出状态是不确定的。

2.令SD,RD端为高电平,D端分别接入高、低电平,用手动脉冲作为CP,观察并记录当CP为0-1时Q端状态。

3.当SD=RD=1,CP=0(或CP=1),改变D端信号,观察Q端的状态是否变化?整理上述实验室据,将结果填入表3-5中。

4.令SD=RD=1,将D和Q端相恋,CP加入连续脉冲,用双踪示波器观察并记录Q相对于CP的波形。

表3-5D触发器74LS74功能表SD RD CP D Q Q0 1 X X 011 0 X X 011 1 0 011 1 1 01任务二:下降沿J-K触发器功能测试双J-K下降沿触发器74LS76芯片的引脚排列图如图3-20所示。

自拟实验步骤,测试器功能并将结果填入表3-6中。

表3-6 双J-K触发器功能测试SD RD CP J K Q Q0 1 X X X X1 0 X X X X1 1 0 X 01 1 1 X 01 1 X 0 11 1 X 1 1若令J=K=1时,CP端加入连续脉冲,用双踪示波器观察Q-CP波形,并于D触发器D和Q 端相连时观察到的Q端波形相比较,有何异同点?任务三:触发器功能转换1.将D触发器和J-K触发器转换成T触发器,列出表达式,画出实验连接图;2.接入连续脉冲,观察各触发器CP及Q端波形,比较两者关系;3.自拟实验数据表并填写之。

实验三 集成触发器

实验七集成触发器一、实验目的1、掌握基本RS、JK、D等常用触发器的逻辑功能及其测试方法;2、研究时钟脉冲的触发作用。

二、预习要求1、预习教材相关内容,了解触发器功能及时钟边沿。

2、确定实验线路连接,画出接线图,拟定实验必要的表格。

三、实验内容1.基本R-S触发器功能与非门(74LS00)按图连接成基本RS触发器,置位端S和复位端R接0/1开关,输出端Q和Q接LED。

改变输入端R、S的状态,测试并将测试结果填入下表中。

与RS触发器真值表比较。

2. J-K触发器逻辑功能测试:(1)测试异步复位端R D和异步置位端S D的功能。

74LS112触发器的S D、R D、J、K接0/1开关,输出端Q和Q接LED,CP接手动单脉冲源。

按下表要求,在R D、S D作用期间改变J、K、CP的状态,观察LED显示状态,测试并记录R D、S D对输出状态的控制作用。

(2)J-K触发器逻辑功能测试:改变J、K的状态,并用R D、S D端对触发器进行异步置位或复位(即设置现态Q n)。

按下表要求测试其逻辑功能并记录于表中。

(3)观察J-K触发器分频功能74LS112按下图接线,J、K接高电平(1),CP接2KHz连续脉冲源,R D、S D接高电平(1)。

用示波器同时观察并记录CP、Q端波形,验证2分频的功能。

接示波器CH2接示波器CH13. D触发器74LS74逻辑功能测试:(1)测试异步复位端R D和异步置位端S D的功能。

74LS74一个触发器的S D、R D、D接0/1开关,输出端Q和Q接LED,CP接手动单脉冲源。

按下表要求,在R D、S D作用期间改变D、CP的状态,观察LED显示状态,测试并记录R D、S D对输出状态的控制作用。

(2)D触发器逻辑功能测试:改变D的状态,并用R D、S D端对触发器进行异步置位或复位(即设置现态Q n)。

按下表要求测试其逻辑功能并记录于表中。

(3)观察D 触发器分频功能74LS74按下图接线,CP 接2KHz 连续脉冲源,R D 、S D 接高电平(1)。

电工电子实验 集成触发器及应用

若干

1块 1块 1块

9-28

三、实验内容

1.异步二进制加法计数器逻辑功能测试(74LS74) ;

2.异步二进制减法计数器逻辑功能测试(74LS76);

3.二进制计数、译码、显示电路(74LS74、 74LS138) ; 4.十进制计数器及译码显示(74LS90、74LS47); 5 .任意进制计数器逻辑功能测试(74LS90、74LS47)。

10-28

74LS138

11-28

74LS138

12-28

74LS90

13-28

14-28

74LS47

15-28

74LS47

16-28

波形的记录

17-28

2.掌握任意进制计数器的设计方法。

3. 掌握译码和显示电路的工作原理和应用方法。

8-28

二、实验仪器与器件 1.数字试验箱 2.数字万用表 1台 1台

3.示波器

4.JK触发器74LS76

1台

若干

5.D触发器74LS74

6.译码器芯片74LS138 7.七段译码器芯片74LS47 8.集成计数器芯片74LS90

实验3.18 集成触发器及应用一 Nhomakorabea实验目的

1.掌握基本RS,JK,D触发器的逻辑功能。 2.学习触发器逻辑功能的测试、转换及应用。

0-28

二、实验仪器与器件:

1.数字试验箱 2.函数信号发生器 1台 1台

3.示波器

4.集成与非门74LS00

1台

2块

5.JK触发器74LS76

6.D触发器74LS74

1块

1块

1-28

三、实验内容

1. 基本RS触发器功能测试(74LS00) 2. JK触发器逻辑功能测试(74LS76) 3. D触发器逻辑功能测试(74LS74)

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

数字逻辑与数字系统设计实验报告

——D、JK触发器与广告流水灯异步时序电路

VHDL语言仿真

学院电子工程学院

班级卓越001012班

学号00101201

姓名冉艳伟

实验时间2012.4.20

一.实验目的

1.了解集成触发器的工作原理。

2.对Quartus II 软件使用操作有初步的了解,能用该软件进行简单的VHDL语言编程与功能仿真

3、掌握VHDL设计实体的基本结构及文字规则。

二.实验仪器

1.计算机一台

2.万用表一块

3.直流稳压电源一台

4.数字电路实验板一台(含cyclone—II FPGA芯片)

5.数据下载线,JTAG连接线若干

三.实验内容

用VHDL代码输入的方法设计以下三个电路功能,并进行全程编译,执行功能和时序仿真。

1.用VHDL语言描述D触发器功能。

2.用VHDL语言描述JK触发器功能。

3.用VHDL语言描述以下功能:

用双D触发器74LS74和与非门74LS00设计一个广告流水灯同步时序电路,广告流水灯有四个灯,这四个灯始终是一暗三明且暗灯循环右移,其状态图如图5-11所示,图中¤表示灯亮,◎表示灯暗。

四.实验数据记录与处理

1. D触发器

1)VHDL语言

library ieee;

use ieee.std_logic_1164.all;

entity Dflipflop is

port(D,clock :in std_logic;

Q :out std_logic);

end Dflipflop;

architecture behavior of Dflipflop is

begin

Process (clock)

begin

if clock'event and clock='1' then

Q<=D;

end if;

end process;

end behavior;

2)功能仿真

建立波形文件,功能仿真结果如下:

3)时序仿真

建立波形文件,时序仿真结果如下:

2.JK触发器

1)VHDL语言

LIBRARY ieee ;

USE ieee.std_logic_1164.all ;

ENTITY jkflipflop IS

PORT ( Clock : IN STD_LOGIC ;

J,K : IN STD_LOGIC ;

Q : OUT STD_LOGIC) ;

END jkflipflop ;

ARCHITECTURE Behavior OF jkflipflop IS

SIGNAL Q1: STD_LOGIC ;

BEGIN

PROCESS ( Clock )

BEGIN

IF Clock'EVENT AND Clock = '1' THEN

Q1 <= (J AND NOT Q1)OR(NOT K AND Q1);

END IF ;

Q <= Q1;

END PROCESS ;

END Behavior ;

2)功能仿真

建立波形文件,功能仿真结果如下

3)时序仿真

建立波形文件,时序仿真结果如下:

3. 广告流水灯

1)VHDL语言

LIBRARY ieee ;

USE ieee.std_logic_1164.all ;

ENTITY fd2 IS

PORT ( Clock : IN STD_LOGIC ;

Q : OUT STD_LOGIC); END fd2 ;

ARCHITECTURE Behavior OF fd2 IS

SIGNAL D : STD_LOGIC ;

BEGIN

PROCESS ( Clock )

BEGIN

IF Clock'EVENT AND Clock = '1' THEN

D <= NOT D ;

END IF ;

Q <= D;

END PROCESS ;

END Behavior ;

LIBRARY ieee ;

USE ieee.std_logic_1164.all ;

PACKAGE fd2_package IS

COMPONENT fd2

PORT ( Clock : IN STD_LOGIC ;

Q : OUT STD_LOGIC);

END COMPONENT ;

END fd2_package;

LIBRARY ieee ;

USE ieee.std_logic_1164.all ;

LIBRARY work ;

USE work.fd2_package.all;

ENTITY fd4 IS

PORT ( Clock : IN STD_LOGIC ;

Q0,Q1 : OUT STD_LOGIC); END fd4 ;

ARCHITECTURE Structure OF fd4 IS

SIGNAL W : STD_LOGIC ;

BEGIN

S0: fd2 PORT MAP( CLOCK, W );

Q0 <= W;

S1: fd2 PORT MAP( W, Q1 );

END Structure ;

LIBRARY ieee ;

USE ieee.std_logic_1164.all ;

PACKAGE fd4_package IS

COMPONENT fd4

PORT ( Clock : IN STD_LOGIC ;

Q0,Q1 : OUT STD_LOGIC);

END COMPONENT ;

END fd4_package;

LIBRARY ieee ;

USE ieee.std_logic_1164.all ;

LIBRARY work ;

USE work.fd4_package.all;

ENTITY liushuideng IS

PORT ( Clock : IN STD_LOGIC ;

Q0,Q1 : OUT STD_LOGIC ;

L : OUT STD_LOGIC_VECTOR(0 TO 3)); END liushuideng ;

ARCHITECTURE Structure OF liushuideng IS SIGNAL W0,W1 : STD_LOGIC ;

BEGIN

S0: fd4 PORT MAP( CLOCK, W0, W1 );

Q0<= W0;

Q1<= W1;

L(0)<= (NOT W0) OR (NOT W1);

L(1)<= W0 OR (NOT W1);

L(2)<= (NOT W0) OR W1;

L(3)<= W0 OR W1;

END Structure ;

2)功能仿真

建立波形文件,功能仿真结果如下

3)时序仿真

建立波形文件,时序仿真结果如下:。